Intel High-Level Synthesis Compiler Pro Edition

Informace o produktu

| Název produktu | Intel High-Level Synthesis Compiler Pro Edition |

|---|---|

| Verze | 22.4 |

| Datum vydání | 19. prosince 2022 |

| Oznámení o ukončení podpory | V plánu je kompilátor Intel High-Level Synthesis Compiler zastaralé po verzi 23.4. |

Návod k použití produktu

Průvodce Začínáme

- Inicializujte prostředí kompilátoru.

- Review různé provedení napřampsoubory a výukové programy poskytované s kompilátorem Intel HLS.

Uživatelská příručka

- Uživatelská příručka obsahuje pokyny

- Syntetizace, ověřování a simulace duševního vlastnictví (IP) navržené pro produkty Intel FPGA.

- Projděte si celý vývojový tok vaší komponenty od vytvoření komponenty a testovacího stolu až po integraci vaší IP komponenty do většího systému pomocí softwaru Intel Quartus Prime.

Průvodce osvědčenými postupy

Průvodce osvědčenými postupy poskytuje techniky a postupy, které můžete použít ke zlepšení využití oblasti FPGA a výkonu vaší komponenty HLS. Po ověření funkční správnosti vaší součásti použijte tyto osvědčené postupy.

Referenční příručka

Referenční příručka poskytuje referenční informace o funkcích podporovaných kompilátorem Intel HLS. Najděte podrobnosti o možnostech příkazu Intel HLS Compiler, záhlaví files, pragmaty, atributy, makra, deklarace, argumenty a knihovny šablon.

Poznámky k vydání Intel® High Level Synthesis Compiler Pro Edition verze 22.4

- Poznámky k vydání Intel® High Level Synthesis Compiler Pro Edition poskytují nejnovější informace o Intel High Level Synthesis Compiler Pro Edition verze 22.4.

Čeká se na ukončení podpory kompilátoru Intel HLS

- Chcete-li si zachovat přístup k nejnovějším funkcím návrhu, optimalizacím a vývojovým nástrojům na vysoké úrovni FPGA, migrujte své stávající návrhy na sadu Intel oneAPI Base Toolkit.

- Předpokládá se, že po verzi 23.4 bude ukončena podpora kompilátoru Intel High Level Synthesis (HLS).

- Navštivte stránku produktu Intel oneAPI, kde najdete rady ohledně migrace, nebo přejděte na fórum komunity Intel High Level Design, kde máte jakékoli dotazy nebo požadavky.

O knihovně dokumentace Intel HLS Compiler Pro Edition

- Dokumentace k Intel HLS Compiler Pro Edition je rozdělena do několika publikací. V následující tabulce vyhledejte publikaci, která obsahuje informace o Intel HLS Compiler Pro Edition, které hledáte:

Tabulka 1. Knihovna dokumentace Intel High-Level Synthesis Compiler Pro Edition

| Název a popis | |

| Poznámky k vydání

Poskytuje nejnovější informace o kompilátoru Intel HLS. |

Odkaz |

| Průvodce Začínáme

Začněte pracovat s Intel HLS Compiler tím, že se naučíte, jak inicializovat prostředí kompilátoru a znovuviewv různých provedeních napřampsoubory a výukové programy poskytované s kompilátorem Intel HLS. |

Odkaz |

| Uživatelská příručka

Poskytuje pokyny k syntéze, ověřování a simulaci duševního vlastnictví (IP), které navrhnete pro produkty Intel FPGA. Projděte si celý vývojový tok vaší komponenty od vytvoření komponenty a testovacího prostředí až po integraci vaší IP komponenty do většího systému pomocí softwaru Intel Quartus Prime. |

Odkaz |

| Průvodce osvědčenými postupy

Poskytuje techniky a postupy, které můžete použít ke zlepšení využití oblasti FPGA a výkonu vaší komponenty HLS. Tyto doporučené postupy obvykle použijete poté, co ověříte funkční správnost vaší součásti. |

Odkaz |

| Referenční příručka

Poskytuje referenční informace o funkcích podporovaných kompilátorem Intel HLS. Najděte podrobnosti o možnostech příkazu Intel HLS Compiler, záhlaví files, pragmaty, atributy, makra, deklarace, argumenty a knihovny šablon. |

Odkaz |

Intel Corporation. Všechna práva vyhrazena. Intel, logo Intel a další značky Intel jsou ochranné známky společnosti Intel Corporation nebo jejích dceřiných společností. Společnost Intel zaručuje výkon svých FPGA a polovodičových produktů podle aktuálních specifikací v souladu se standardní zárukou společnosti Intel, ale vyhrazuje si právo provádět změny jakýchkoli produktů a služeb kdykoli bez upozornění. Společnost Intel nepřebírá žádnou odpovědnost nebo závazky vyplývající z aplikace nebo použití jakýchkoli informací, produktů nebo služeb zde popsaných, s výjimkou případů, kdy je společnost Intel výslovně písemně odsouhlasena. Zákazníkům společnosti Intel se doporučuje získat nejnovější verzi specifikací zařízení předtím, než se budou spoléhat na jakékoli zveřejněné informace a než zadají objednávky na produkty nebo služby.

*Jiná jména a značky mohou být nárokovány jako vlastnictví jiných.

Čeká se na ukončení podpory kompilátoru Intel HLS

- Chcete-li si zachovat přístup k nejnovějším funkcím návrhu, optimalizacím a vývojovým nástrojům na vysoké úrovni FPGA, migrujte své stávající návrhy na sadu Intel oneAPI Base Toolkit.

- Předpokládá se, že po verzi 23.4 bude ukončena podpora kompilátoru Intel High Level Synthesis (HLS).

- Navštivte stránku produktu Intel oneAPI, kde najdete rady ohledně migrace, nebo přejděte na fórum komunity Intel High Level Design, kde máte jakékoli dotazy nebo požadavky.

Nové funkce a vylepšení

- Intel High Level Synthesis Compiler Pro Edition verze 22.4 obsahuje následující nové funkce:

- Uvolnění údržby.

- Žádné nové funkce nebo vylepšení pro Intel HLS Compiler Pro Edition verze 22.4.

Změny v chování softwaru

- Tato část popisuje případy, kdy se funkce Intel HLS Compiler Pro Edition verze 22.4 oproti dřívějším verzím kompilátoru změnily.

Uvolnění údržby.

- Žádné změny v chování softwaru pro Intel HLS Compiler Pro Edition verze 22.4.

Předpoklady Intel High-Level Synthesis Compiler Pro Edition

- Intel HLS Compiler Pro Edition je součástí Intel Quartus® Prime Pro Edition Design Suite. Kompilátor Intel HLS můžete nainstalovat jako součást instalace softwaru Intel Quartus Prime nebo jej nainstalovat samostatně. K použití vyžaduje Intel Quartus Prime a další software.

- Podrobné pokyny k instalaci softwaru Intel Quartus Prime Pro Edition, včetně systémových požadavků, předpokladů a licenčních požadavků, najdete v tématu Instalace a licencování softwaru Intel FPGA.

- Kompilátor Intel HLS vyžaduje kromě Intel Quartus Prime následující software:

Kompilátor C++

- V Linuxu Intel HLS Compiler vyžaduje GCC 9.3.0 včetně knihovny GNU C++ a binárních utilit (binutils).

- Tato verze GCC je poskytována jako součást instalace kompilátoru Intel HLS. Po instalaci kompilátoru Intel HLS je k dispozici GCC 9.3.0 /gcc.

- Důležité: Kompilátor Intel HLS používá /gcc jako jeho adresář toolchain. Použijte tuto instalaci GCC pro všechny své návrhářské práce související s HLS.

- Pro Windows nainstalujte jednu z následujících verzí Microsoft* Visual Studio* Professional:

- Microsoft Visual Studio 2017 Professional

- Komunita Microsoft Visual Studio 2017

- Chcete-li mít nejaktuálnější podporu C++17, ujistěte se, že používáte nejnovější verzi sady Visual Studio 2017.

- Důležité: Software Intel HLS Compiler nepodporuje jiné verze Microsoft Visual Studio než ty, které jsou uvedeny pro edici softwaru.

Simulační software Siemens* EDA Questa®

- V systémech Windows a RedHat Linux můžete nainstalovat simulační software Questa® z instalačního programu softwaru Intel Quartus Prime. Dostupné možnosti jsou následující:

- Questa Intel FPGA Edition

- Questa Intel FPGA Starter Edition

- Jak Questa Intel FPGA Edition, tak Questa Intel FPGA Starter Edition vyžadují licence. Licence pro Questa Intel FPGA Starter Edition je zdarma. Podrobnosti naleznete v části Instalace a licencování softwaru Intel FPGA.

- Případně můžete použít svou vlastní licencovanou verzi softwaru Siemens* EDA ModelSim* SE nebo Siemens EDA Questa Advanced Simulator.

- Na systémech Linux vyžadují Questa – Intel FPGA Edition a Questa – Intel FPGA Starter Edition balíčky vývojových nástrojů Red Hat*.

- Informace o všech verzích softwaru ModelSim a Questa, které software Intel podporuje, naleznete v části Informace o rozhraní EDA v poznámkách k vydání podpory softwaru a zařízení pro vaši edici Intel Quartus Prime Pro Edition.

Související informace

- Příručka Začínáme s kompilátorem Intel High Level Synthesis Compiler

- Podporované operační systémy

- Softwarové požadavky při instalaci a licencování softwaru Intel FPGA

- Informace o rozhraní EDA (Intel Quartus Prime Pro Edition)

Známé problémy a náhradní řešení

- Tato část poskytuje informace o známých problémech, které ovlivňují Intel HLS Compiler Pro Edition verze 22.4.

| Popis | Řešení |

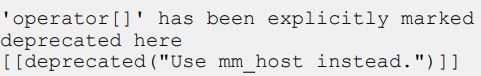

| Když použijete zastaralou třídu mm_master, kompilátor vydá varovnou zprávu, jako je tato:

Tato zpráva neuvádí, kterou část kódu je třeba změnit. |

Vyhněte se této varovné zprávě použitím třídy mm_host, která nahrazuje zastaralou třídu mm_master. |

| (Pouze Windows) Kompilace návrhu v adresáři s dlouhým názvem cesty může vést k selhání kompilace.

Zkontrolujte debug.log file pro „nemohl najít file“chyby. Tyto chyby mohou naznačovat, že vaše cesta je příliš dlouhá. |

Zkompilujte návrh v adresáři s krátkým názvem cesty. |

| (Pouze Windows) Dlouhá cesta k instalačnímu adresáři Intel Quartus Prime vám může bránit v úspěšné kompilaci a spuštění výukových programů Intel HLS Compiler a example designy.

Zkontrolujte debug.log file pro „nemohl najít file“chyby. Tyto chyby mohou naznačovat, že vaše cesta je příliš dlouhá. |

Přesunout tutoriály a examples na krátký název cesty, než se je pokusíte spustit. |

| Popis | Řešení |

| Knihovny, které cílí na OpenCL* a jsou napsány v HLS, nemohou používat proudy nebo kanály jako rozhraní mezi kódem OpenCL a knihovnou napsanou v HLS.

Knihovna v HLS však může používat proudy nebo kanály, pokud jsou oba koncové body v knihovně (napřample, proud, který spojuje dvě funkce úkolu). |

N/A |

| Použití parametru ihc::maxburst na hostitelská rozhraní Avalon® Memory-Mapped může způsobit, že se váš návrh zasekne v simulaci. | N/A |

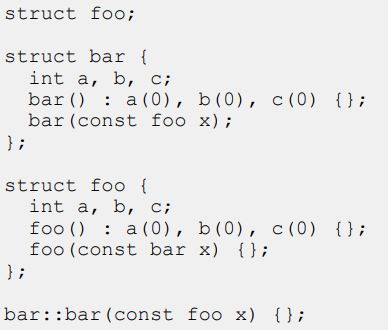

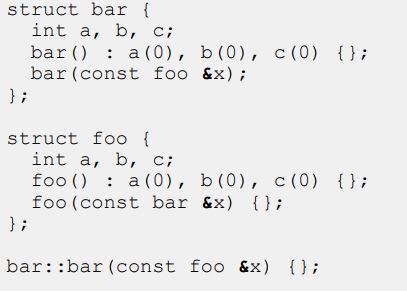

| V některých neobvyklých případech, pokud máte dvě třídy, z nichž každý vyžaduje jako vstup instance druhé třídy, může kompilátor selhat.

Napřample, kompilace následujícího fragmentu kódu způsobí selhání kompilátoru:

|

Vyhněte se vytváření kruhové definice. Místo toho použijte v konstruktoru kopírování ukazatel nebo odkaz.

Napřample, transformujte dřívější fragment kódu na následující kód a předejte strukturu jako odkaz na konstruktor:

|

| Knihovny, které cílí na OpenCL a jsou napsány v HLS, mohou způsobit, že jádra OpenCL, která knihovnu obsahují, budou mít konzervativnější přírůstkovou kompilaci. | N/A |

| Pokud při vývoji knihovny máte #define definující hodnotu, kterou později použijete v #pragma, příkaz fpga_crossgen selže.

Napřample, následující kód nelze zkompilovat

|

Místo #pragma použijte pragma.

Napřample, následující se úspěšně zkompiluje s

|

| Když použijete volbu příkazu -c k samostatné kompilaci a propojení stages ve vašem pracovním postupu, a pokud nezadáte volbu -march v odkazu stage (nebo zadejte jinou hodnotu volby -march), vaše propojení stage může selhat s chybovými zprávami nebo bez nich. | Ujistěte se, že používáte stejnou hodnotu volby -march pro obě kompilace s volbou příkazu -c stage a spojovací stage. |

| Popis | Řešení |

| Použití paměťového atributu hls_merge na pole deklarované v rozvinuté nebo částečně rozvinuté smyčce způsobí, že kopie pole budou sloučeny v rámci iterací rozvinuté smyčky.

|

Vyhněte se použití atributu paměti hls_merge v rozvinutých smyčkách.

Pokud potřebujete sloučit paměti v rozvinuté smyčce, explicitně deklarujte pole typu struct pro sloučení šířky nebo deklarujte hlubší pole pro sloučení hloubky.

|

| V paměti funkcí ViewVe zprávě o návrhu na vysoké úrovni se mohou některé paměti s rozsahem funkcí jevit jako „optimalizované“. | Žádný.

Když a file obsahuje funkce, které jsou součástmi, a funkce, které nejsou součástmi, všechny proměnné s rozsahem funkcí jsou uvedeny v podokně Seznam paměti funkcí, ale pouze proměnné z komponent mají informace o nich, které se mají zobrazit v paměti funkcí View podokno. |

| Některé sestavy návrhu na vysoké úrovni selžou v aplikaci Microsoft Internet Explorer*. | K tomu použijte jeden z následujících prohlížečů view zprávy:

• Google Chrome* • Microsoft Edge* • Mozilla Firefox* |

| Smyčka Viewer v High-Level Design Reports má následující omezení:

• Chování clusterů bez zastavení není modelováno ve smyčce Viewehm. Konečná latence zobrazená ve smyčce Viewer pro cluster bez blokování je obvykle pesimističtější (tj. vyšší) než skutečná latence vašeho návrhu. Popis klastrování a klastrů bez blokování viz Shlukování datové cesty v Intel na vysoké úrovni Synthesis Compiler Pro Edition Průvodce doporučenými postupy. • Zablokování při čtení a zápisu z paměti nebo tiskových příkazů nejsou modelována. • Vysoké počty iterací (>1000) způsobují pomalý výkon smyčky Viewehm. • Ve smyčce nemůžete zadat počet iterací nula (0). Viewehm. |

Žádný. |

| Odkazy v některých sestavách v sestavách návrhu na vysoké úrovni generovaných v systémech Windows nefungují. | Vygenerujte sestavy návrhu na vysoké úrovni (tj. zkompilujte svůj kód) v systému Linux. |

| Použití struktury jednoho datového typu ac_int v rozhraní steaming, které používá pakety (ihc::usesPackets ) nefunguje.

Napřample, následující fragment kódu nefunguje:

|

Chcete-li ve svém návrhu použít tuto kombinaci, dodržujte následující omezení:

• Vnitřní velikost dat ac_int musí být násobkem 8 • Musí být uvedena deklarace typu rozhraní toku ihc::bitsPerSymbol<8> Napřample, funguje následující fragment kódu:

|

| Popis | Řešení | |

| Pokud při spouštění vysoce propustné simulace vaší komponenty pomocí volání funkcí zařazování do fronty nepoužijete funkci ihc_hls_component_run_all ke spuštění volání komponenty zařazené do fronty po všech voláních ihc_hls_enqueue pro tuto komponentu, dojde k následujícímu chování:

• V emulaci jsou spuštěny funkce zařazené do fronty. • V simulaci nejsou spuštěny funkce zařazené do fronty bez chybových nebo varovných zpráv. |

Ujistěte se, že používáte funkci ihc_hls_component_run_all po všech voláních ihc_hls_enqueue pro tuto komponentu ke spuštění volání funkcí komponenty zařazených do fronty. | |

| Spuštění funkce úlohy pomocí ihc::launch_always_run | Chcete-li se vyhnout odstranění optimalizace, přidejte chvíli (1) | |

| odstraní atributy optimalizace aplikované na úlohu | smyčky na postiženou funkci použijte odpovídající ovládací prvek | |

| funkce. | pragma do cyklu while(1) místo funkce. | |

| V následujícím kódu example, atribut použitý na funkci je ignorován. Zprávy o návrhu na vysoké úrovni ukazují pro tento úkol II 1 místo požadované II 4. | Následující kód exampukažte, jak můžete implementovat tuto změnu pro dřívější kód exampten: | |

|

|

|

| U projektů Cyclone® V, které obsahují více komponent HLS, se při použití příkazu i++ ke kompilaci projektu na hardware (i++ -march=CycloneV) může zobrazit chyba.

I když se text chyby liší v závislosti na vašem projektu, podpisem chyby je selhání kompilace Intel Quartus Prime kvůli špatné syntaxi Verilog. Modul se pokouší použít funkci, kterou kompilátor Intel Quartus Prime nemůže najít. |

Pokud se setkáte s tímto problémem, umístěte každou komponentu HLS do samostatného projektu. | |

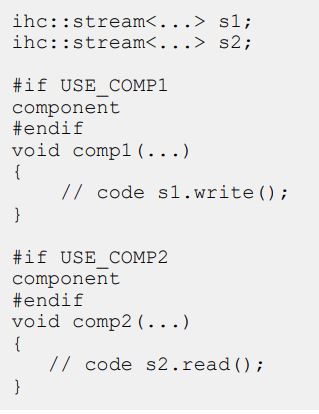

| Kompilace některých návrhů, které obsahují více komponent, generuje chybu o opětovném použití streamu. | Pokud se setkáte s tímto problémem, zkompilujte každou komponentu v návrhu samostatně. Možná budete muset do kódu přidat makra, abyste umožnili kompilaci každé komponenty samostatně. | |

| Zvažte následující příkladampten: | ||

|

||

Archiv poznámek k vydání Intel High-Level Synthesis Compiler Pro Edition

Nejnovější a předchozí verze této uživatelské příručky naleznete v poznámkách k vydání Intel HLS Compiler Pro Edition. Pokud verze softwaru není uvedena, platí poznámky k verzi pro předchozí verzi softwaru.

Historie revizí dokumentu pro Intel HLS Compiler Pro Edition verze 22.4 Poznámky k vydání

| Verze dokumentu | Verze Intel Quartus Prime | Změny |

| 2022.12.19 | 22.4 | • První vydání. |

Dokumenty / zdroje

|

Intel High Level Synthesis Compiler Pro Edition [pdfPokyny Verze 22.4, Verze 23.4, High Level Synthesis Compiler Pro Edition, High Level Synthesis Compiler, Pro Edition |