## Wiznet W5100 Ethernet Design Guide User Guide

Home » WIZnet » Wiznet W5100 Ethernet Design Guide User Guide 12

#### **Contents**

- 1 Wiznet W5100 Ethernet Design Guide

- 2 Description

- **3 Product Usage Instructions**

- **4 Description**

- **5 SCH Design Guide**

- **6 Using RJ-45 without Transformer**

- 7 PCB Design Guide

- **8 TEST Compliance**

- 9 Documents / Resources

## Wiznet W5100 Ethernet Design Guide

This document is a WIZnet Ethernet Chip design reference. It contains PCB design references using W5100, W5300, W5500, W7500, and W7500P. The references include information about the Medium Dependent Interface (MDI), power supply, parts placement, and Media Independent Interface (MII). It is important to follow the instructions provided in this document to ensure optimal Ethernet performance.

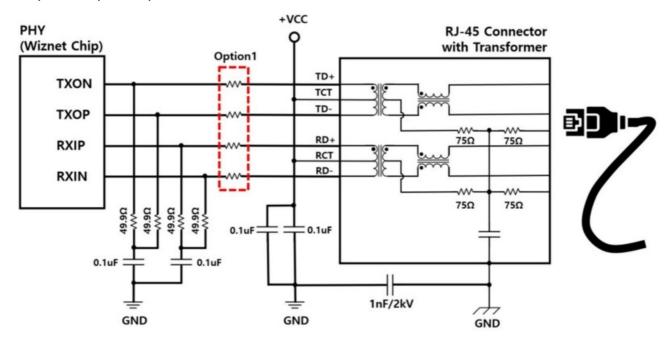

#### SCH Design Guide – W5100, W5100S, W5300, W6100:

The circuit configuration may vary depending on the internal circuit of the Ethernet socket. Therefore, it is crucial to refer to the respective datasheets and design the circuit accordingly. If you are using an Ethernet socket without a transformer, you need to design the transformer part of the circuit as well. The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal resistance of the TX and RX can be designed as AGND instead of the normal GND. This design choice helps separate the MDI signal from system GND noise. In suchcases, it is important to ensure that the AGND area is sufficiently large. Alternatively, integrating AGND and system GND can be more advantageous. Option1 refers to a damping resistance against electromagnetic compatibility (EMC). This resistance helps prevent common mode noise and differential mode noise interference. It is important to choose an appropriate resistance value because if it is too large, it may cause a decrease in the voltage level of the differential line, leading to Ethernet communication problems.

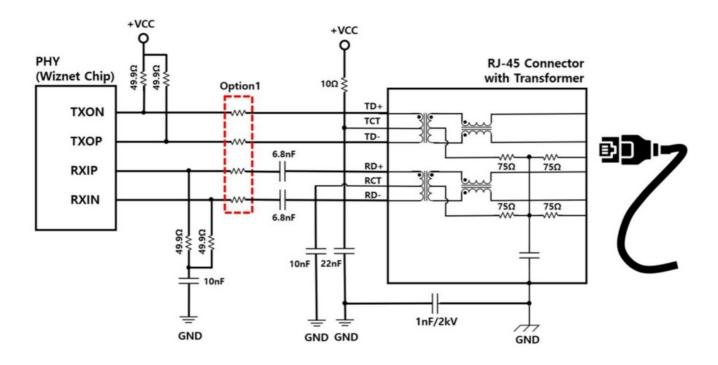

#### SCH Design Guide - W5500:

The circuit configuration may vary depending on the internal circuit of the Ethernet socket. Therefore, it is crucial to refer to the respective datasheets and design the circuit accordingly. If you are using an Ethernet socket without a transformer, you need to design the transformer part of the circuit as well. The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal resistance of the TX and RX can be designed as AGND instead of the normal GND. This design choice helps separate the MDI signal from system GND noise. In such cases, it is important to ensure that the AGND area is sufficiently large. Alternatively, integrating AGND and system GND can be more advantageous. Option1 refers to a damping resistance against electromagnetic compatibility (EMC). This resistance helps prevent common mode noise and differential mode noise interference. It is important to choose an appropriate resistance value because if it is too large, it may cause a decrease in the voltage level of the differential line, leading to Ethernet communication problems.

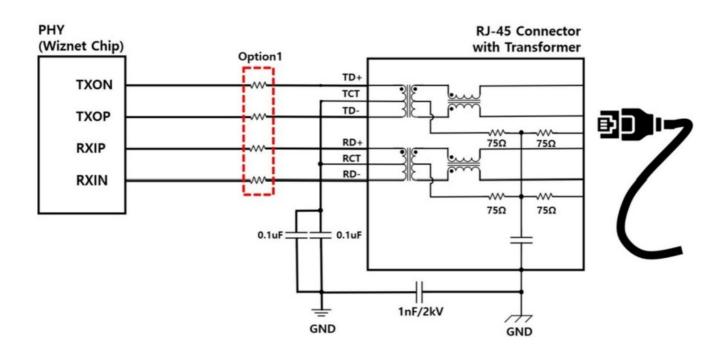

#### SCH Design Guide – W7500, W7500P:

The circuit configuration may vary depending on the internal circuit of the Ethernet socket. Therefore, it is crucial to refer to the respective datasheets and design the circuit accordingly. If you are using an Ethernet socket without a transformer, you need to design the transformer part of the circuit as well. The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal resistance of the TX and RX can be designed as AGND instead of the normal GND. This design choice helps separate the MDI signal from system GND noise. In such cases, it is important to ensure that the AGND area is sufficiently large. Alternatively, integrating AGND and system GND can be more advantageous. Option1 refers to a damping resistance against electromagnetic compatibility (EMC). This resistance helps prevent common mode noise and differential mode noise interference.

#### **Product Usage Instructions**

To use the WIZnet Ethernet Chip, follow the steps below:

- 1. Refer to the respective datasheet for your specific chip model (W5100, W5300, W5500, W7500, or W7500P) to understand the internal circuit configuration.

- 2. Design the circuit according to the information provided in the datasheet. Pay attention to the Medium Dependent Interface (MDI), power supply, parts placement, and Media Independent Interface (MII).

- 3. If you are using an Ethernet socket without a transformer, ensure that you design the transformer part of the circuit as well.

- 4. Consider designing the TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal resistance of the TX and RX as AGND instead of the normal GND. This helps in separating the MDI signal from system GND noise. Ensure that the AGND area is large enough or integrate AGND and system GND if more advantageous.

5. Choose an appropriate value for Option1, the damping resistance against electromagnetic compatibility (EMC). This resistance should prevent common mode noise and differential mode noise interference. Avoid using a resistance value that is too large as it may cause a decrease in voltage level and Ethernet communication problems.

By following these instructions, you can ensure optimal performance and functionality of the WIZnet Ethernet Chip.

## **Description**

This document is a WIZnet Ethernet Chip design reference. It contains PCB design references using W5100, W5300, W5500, W7500, and W7500P. Includes Medium dependent interface (MDI), power supply, parts placement, Media Independent Interface (MII), etc. You must follow the instructions below. Failure to follow the instructions may result in poor Ethernet performance.

#### **SCH Design Guide**

#### W5100, W5100S, W5300, W6100

- The circuit may change depending on the internal circuit configuration of the Ethernet socket. Make sure to refer to Datasheet and design the circuit in an appropriate way.

- If you use an Ethernet socket that does not include a transformer, you must also design the transformer part of the circuit.

- The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal resistance of the TX and RX can be designed as AGND instead of the normal GND. This is for the separation of the MDI signal from the system GND noise, in which case the area of the AGND should be large enough.

Otherwise, it is more advantageous to integrate AGND and system GND.

- Option1 is a damping resistance against EMC. Resistance to prevent common mode noise and differential mode noise interference; if the resistance value is designed too large, the voltage level of the differential line may decrease, which may cause Ethernet communication problems.

- The circuit may change depending on the internal circuit configuration of the Ethernet socket. Make sure to refer to Datasheet and design the circuit in an appropriate way.

- If you use an Ethernet socket that does not include a transformer, you must also design the transformer part of the circuit.

- The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal

resistance of the TX and RX can be designed as AGND instead of the normal GND. This is for the separation

of the MDI signal from the system GND noise, in which case the area of the AGND should be large enough.

Otherwise, it is more advantageous to integrate AGND and system GND.

- Option1 is a damping resistance against EMC. Resistance to prevent common mode noise and differential mode noise interference; if the resistance value is designed too large, the voltage level of the differential line may decrease, which may cause Ethernet communication problems.

#### W7500, W7500P

- The circuit may change depending on the internal circuit configuration of the Ethernet socket. Make sure to refer to Datasheet and design the circuit in an appropriate way.

- If you use an Ethernet socket that does not include a transformer, you must also design the transformer part of the circuit.

- The TCT of the transformer, the GND connected to the RCT, and the GND connected to the longitudinal

resistance of the TX and RX can be designed as AGND instead of the normal GND. This is for the separation

of the MDI signal from the system GND noise, in which case the area of the AGND should be large enough.

Otherwise, it is more advantageous to integrate AGND and system GND.

- Option1 is a damping resistance against EMC. Resistance to prevent common mode noise and differential mode noise interference; if the resistance value is designed too large, the voltage level of the differential line may decrease, which may cause Ethernet communication problems.

- The Current Mode PHY has a termination resistor circuit inside, eliminating the need to design an external termination resistor.

- Since the W7500 does not have PHY, additional PHY circuits must be designed.

#### **Using RJ-45 without Transformer**

- If you use an Ethernet socket without Transformer, you must design an additional Transformer circuit.

- The above circuit is a typical circuit configuration and corresponds to W5100, W5100S, W5300, and W6100 on the WIZnet Ethernet Chip.

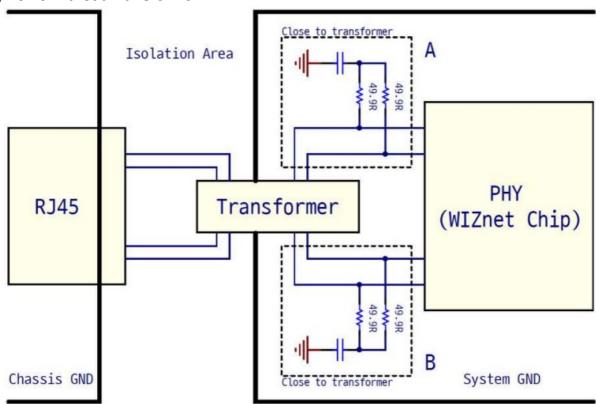

- Based on Transformer, PHY to Transformer is the System GND area.

- It is recommended that the termination resistance be placed closest to the end of the signal. (Receiving side)

#### **PCB Design Guide**

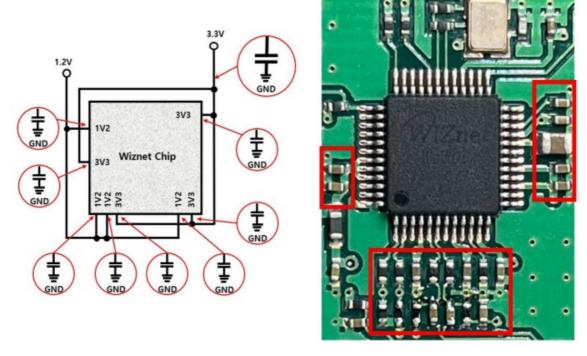

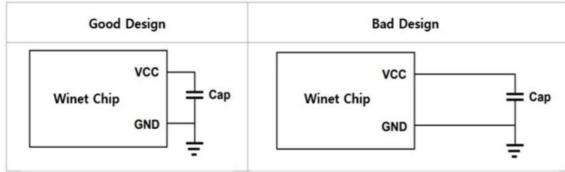

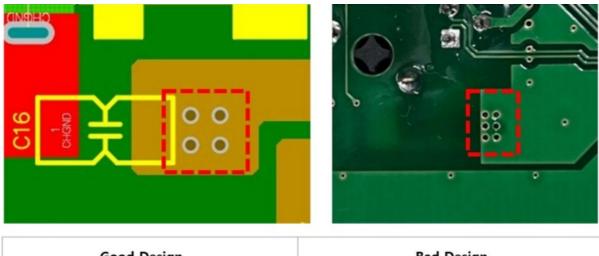

#### **Decoupling Capacitor**

- The Decoupling Capacitor is used to remove noise from the power line.

- As filtering is the purpose, it is recommended to place it as close as possible to the chip.

- It is recommended that at least one Capacitor be designed for each power line.

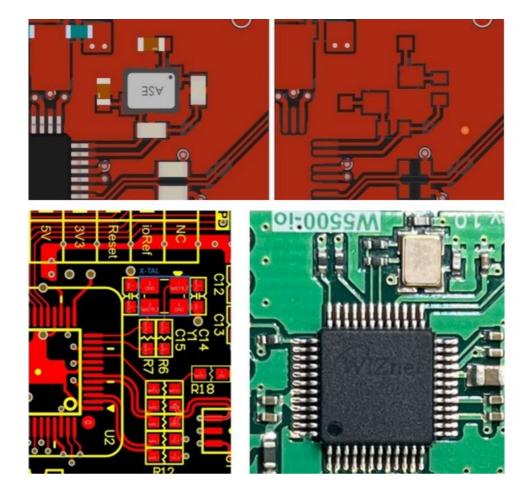

#### **Oscillator**

- Because it is a high-frequency signal, it is recommended to design without Via in layers such as Chip during Artwork.

- It is recommended that only one chip be connected to one oscillating element. (current problem, interference

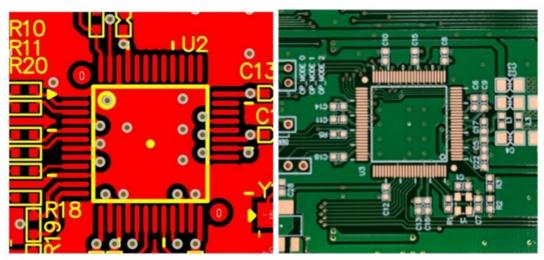

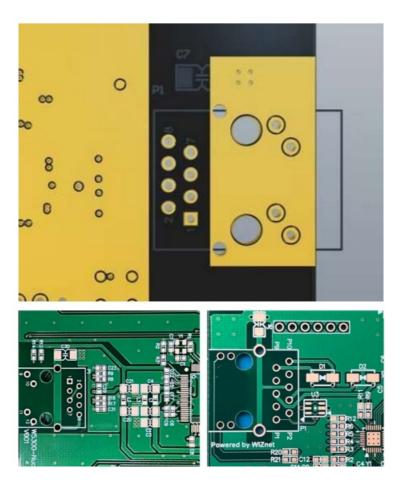

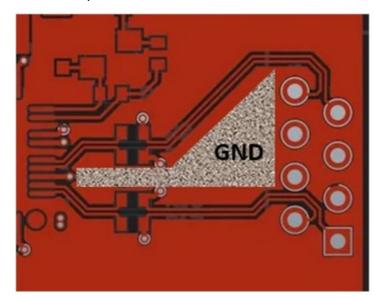

#### **GND Plane**

- It is also recommended to put GND Copper powder on the inside of the chip.

- It is recommended that no other digital lines pass across the chip.

- It is recommended that you place multiple Via's to maintain good GND connectivity.

- It is recommended to distinguish between AGND and DGND.

- If you separate AGND and DGND, it is not functionally good if it is located on the same coordinate even if it is a different layer.

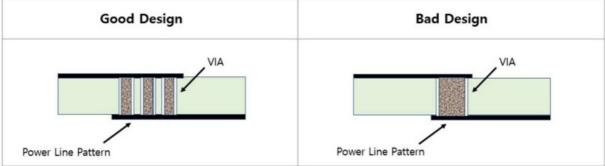

## **Power Pattern**

- The Power Plane should also consider Pattern and Via. The current capacity of the pattern depends on the width, thickness, OZ, and temperature.

- If possible, it is better to design with several smaller Via rather than one larger Via. (Current capacity is greater)

#### **Ethernet Socket**

- If you use an RJ-45 socket without Transformer, you must design the Transformer circuit additionally.

- The above circuit is a typical circuit configuration and corresponds to W5100S, W6100, and W5300 on the WIZnet Ethernet Chip.

- Based on Transformer, PHY to Transformer is the System GND area.

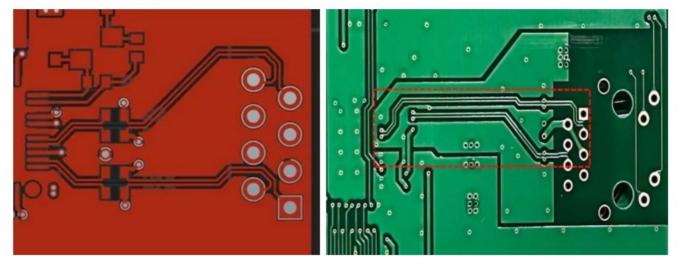

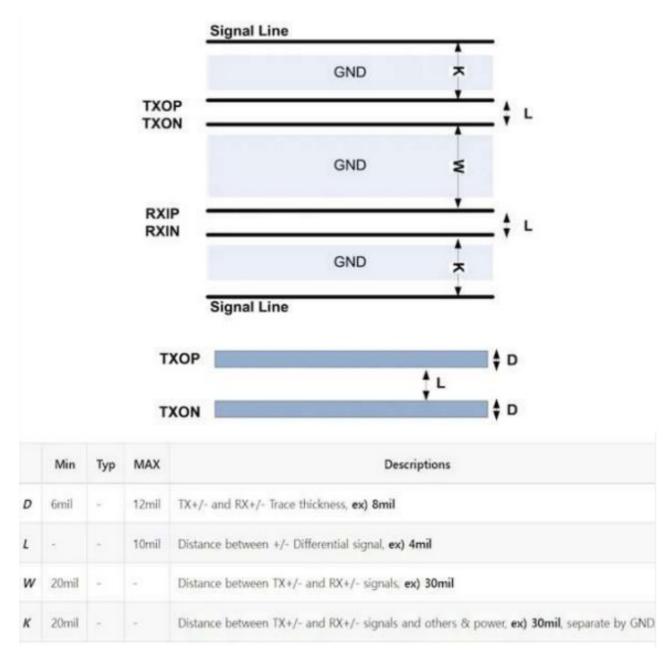

## MDI

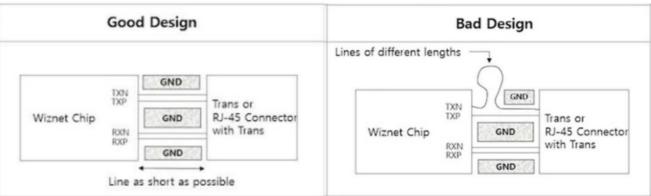

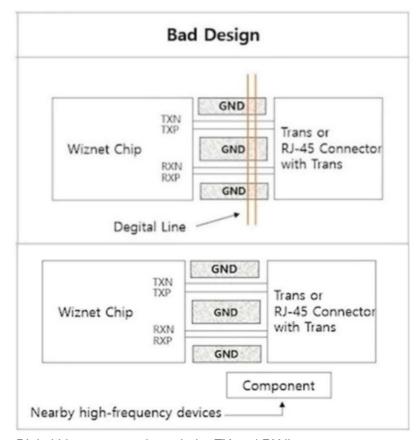

- The distance between RJ-45 and Chip should be as close as possible.

- Because the Tx, Rx signals are differential signals, each line must be of the same length. If the lines are formed differently, the differential mode signal can switch to common mode noise, affecting EMI, and causing Ethernet communication to become a problem.

- It is recommended that a GND pattern be placed between TX and RX so that there is no influence between the two lines.

- If the distance between the two lines is wide enough not to affect each other, there isno need for GND Copper.

- The Impedance of the Line depends on the GND processing. When designing this part, Impedance Matching is possible with line thickness and Clearance.

- It is not good for other Digital Lines to pass through the TX and RX lines.

- It is not good to have a high frequency device around (OCS, etc.)

- Minimum condition for Ethernet Impedance Line design.

- The impedance of Ethernet is 100 ohms.

- In order to design an accurate Impedance 100 ohm, you should ask the PCB manufacturer to design it. (Impedance changes depending on Solder Mask, Oz, and process method.)

#### **TEST Compliance**

# **Test Report**

## Pass

|                         | Test Configuration Details                                                                                                                                |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Application                                                                                                                                               |

| Nane                    | D9010ETHC Ethernet                                                                                                                                        |

| Version                 | 2.72.0.0                                                                                                                                                  |

|                         | Device Description                                                                                                                                        |

| Tests100T               | No.                                                                                                                                                       |

| Tests1008T              | Ves                                                                                                                                                       |

| Tests10008T             | No.                                                                                                                                                       |

| Tests100T_EEE           | No.                                                                                                                                                       |

| Tests1000T_EEE          | No.                                                                                                                                                       |

| Tests1000BT EEE         | No.                                                                                                                                                       |

| DisturbingSignal        | Yes                                                                                                                                                       |

| TxTclk                  | Yes                                                                                                                                                       |

| DisturberSource         | Use Keysight 13250A                                                                                                                                       |

| ReturnLossTest          | Use Vector Network Analyzer                                                                                                                               |

|                         | Test Session Details                                                                                                                                      |

| Infiniium SW Version    | 86,48,00714                                                                                                                                               |

| Infiniium Model Number  | PS05104A                                                                                                                                                  |

| Infiniium Serial Number | WY55160128                                                                                                                                                |

| Debug Mode Used         | No.                                                                                                                                                       |

| Compliance Limits       | IEEE Std. 802.3 Specification (official)                                                                                                                  |

| Probe (Channel 2)       | Model: N2750A<br>Serial: U553331201<br>Atten: Calibrated (18 NOV 2022 15:23:49), Using Cal Atten (9.9742E+00)<br>Skew: Not Calibrated, Using Default Skew |

| Probe (Channel 3)       | Model: User Defined Probe Serial: No Serial Num  Atten: Not Calibrated, Using Default Atten (1.00006+00) Skew: Not Calibrated, Using Default Skew         |

| Probe (Channel 4)       | Model: User Defined Probe Serial: No Serial Num  Atten: Not Calibrated, Using Default Atten (1.000000+00) Skew: Not Calibrated, Using Default Skew        |

| Last Test Date          | 2022-11-18 15:37:29 UTC +08:60                                                                                                                            |

#### Summary of Results

|                 |                   | The state of the s | 1 |

|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Test Statistics | Margin Thresholds |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 |

| Falled 0        | Warning < 2 %     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Passed 15       | Critical < 0 %    | The state of the s |   |

| Total 15        |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Pass | # Failed | # Trials | Test Name (click to jump)                          | Actual Value | Margin  | Pass Limits                   |

|------|----------|----------|----------------------------------------------------|--------------|---------|-------------------------------|

| 8    | 0        | 1        | 100 Base-TX, UTP +Vout Differential Output Voltage | 955.4 mV     | 5.4 %   | 950.0 mV < VALUE < 1.0500 V   |

| 0    | 0        | 1        | 100 Base-TX, UTP -Vout Differential Output Voltage | -950.7 mV    | 0.7%    | 950.0 MV <  VALUE  < 1.0500 V |

| 0    | ė .      | 1        | 100 Base-TX, UTP Signal Amplitude Symmetry         | -1.005       | 37.5 %  | 980 m < [VALUE] < 1.020       |

| 0    | 0        | 1        | 100 Base-TX, *Vout Overshoot                       | -1.2 %       | 124.0 % | VALUE < 5.0 %                 |

| 0    | 0        | 1        | 100 Base-TX, -Yout Overshoot                       | -1.1 %       | 122.0%  | VALUE < 5.0 %                 |

| 0    | 0        | 1        | 100 Base-TX, UTP AGI Template                      | 0.000        | 100.0 X | No Mask Failures              |

| 0    | 0        | 1        | 100 Base-TX, AOI +Vout Rise Time                   | 3.809 ns     | 40.5 %  | 3.000 ns < VALUE < 5.000 ns   |

| 0    | 0        | 1        | 100 Base-TX, AOI +Vout Fall Time                   | 3.836 ns     | 41.8 %  | 3.000 ns < VALUE < 5.000 ns   |

| 0    | 0        | 1        | 100 Base-TX, AOI +Vout Rise/Fall Symmetry          | 80.89 ps     | 83.8 %  | VALUE < 500.00 ps             |

| 0    | 0        | 1        | 100 Base-TX, AOI -Vout Rise Time                   | 3.700 ns     | 35.0 %  | 3.000 ns < VALUE < 5.000 ns   |

| 0    | 0        | 1        | 100 Base-TX, AOI -Yout Fall Time                   | 3.692 ns     | 34.6 %  | 3.000 ns < VALUE < 5.000 ns   |

| 0    | 0        | 1        | 100 Base-TX, AOI -Vout Rise/Fall Symmetry          | 135.00 ps    | 73.0 %  | VALUE < 500.00 ps             |

| 0    | 0        | 1        | 100 Base-TX, AOI Overall Rise/Fall Symmetry        | 198.10 ps    | 60.4%   | VALUE < 500.00 ps             |

| 0    | 0        | 1        | 100 Base-TX, Transmit litter                       | 374 ps       | 73.3 %  | VALUE < 1.400 ns              |

| 0    | 0        | 1        | 100 Base-TX, Duty Cycle Distortion                 | 54.890 ps    | 89.0 %  | VALUE <= 500.000 ps           |

- Test conducted at 10/100M

- Power USB Micro B Type

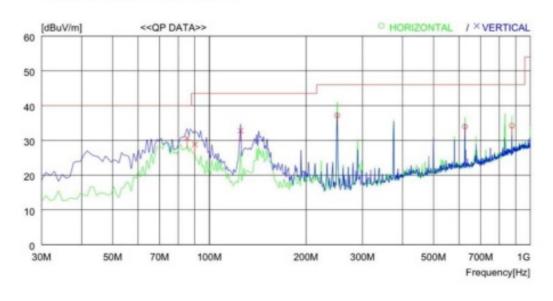

### **EMI-RE**

## RADIATED EMISSION

2022. 11. 23

Trade Name Model Name Serial No. Mode

W5100S\_MAG\_C

AGR No. Power Supply Temp / Humi Operator

220 V~, 60 Hz 23.8 °C, 45.8 % R.H. OH SUN EAK

LIMIT: FCC Part15 Subpart.B Class B (3m)

| No.         | FREQ                          | READING<br>QP | ANT<br>FACTOR        | LOSS | GAIN | RESULT   | LIMIT                | MARGIN              | ANTENNA           | TABLE             |

|-------------|-------------------------------|---------------|----------------------|------|------|----------|----------------------|---------------------|-------------------|-------------------|

|             | [MHz]                         | [dBuV]        | [dB]                 | [dB] | [dB] | [dBuV/m] | dBuV/m]              | [dB]                | [cm]              | [DEG]             |

|             | Horizo                        | ntal          |                      |      |      |          |                      |                     |                   |                   |

| 1<br>2<br>3 | 250.190<br>625.577<br>875.830 | 33.4          | 12.7<br>19.2<br>21.7 | 10.5 | 29.1 | 34.0     | 46.0<br>46.0<br>46.0 | 8.8<br>12.0<br>11.8 | 200<br>200<br>200 | 297<br>359<br>174 |

|             | Vertic                        | al            |                      |      |      |          |                      |                     |                   |                   |

| 4<br>5<br>6 | 85.290<br>90.140<br>125.060   | 43.0          | 9.1<br>10.5<br>9.6   |      | 28.2 | 28.9     | 40.0<br>43.5<br>43.5 | 9.3<br>14.6<br>10.7 | 100<br>100<br>100 | 0 0               |

- Source Power 5 Volt Adapter Power

- Test running with maximum Dummy Data transmission and reception

#### **Documents / Resources**

<u>Wiznet W5100 Ethernet Design Guide</u> [pdf] User Guide W5100 Ethernet Design Guide, W5100, Ethernet Design Guide, Design Guide

Manuals+,