# NXP UM12181 FRDM-IMX93 Board User Manual

Home » NXP » NXP UM12181 FRDM-IMX93 Board User Manual

#### **Contents**

- 1 NXP UM12181 FRDM-IMX93 Board

- **2 Product Usage Instructions**

- 3 FRDM-IMX93 overview

- 4 FRDM-IMX93 functional description

- 5 Working with accessories

- **6 PCB information**

- 7 Acronyms

- 8 Related documentation

- 9 Note about the source code in the document

- 10 Legal information

- 11 Documents / Resources

- 11.1 References

- **12 Related Posts**

NXP UM12181 FRDM-IMX93 Board

#### **Specifications**

- Processor: i.MX 93 applications processor with dual Arm Cortex-A55 + Arm Cortex-M33 core

- Memory: 2 GB LPDDR4X

- Storage: 32 GB eMMC 5.1, uSDHC support

- Interfaces: USB 2.0, USB Type-C, USB Type-A, MIPI CSI, MIPI DSI, HDMI, Ethernet, CAN, I2C/I3C, ADC, Wi-Fi

SDIO, UART, SPI, SAI

# **Product Usage Instructions**

# Setting Up the FRDM-IMX93 Board

Before starting with the board, ensure you have all the necessary components including power supply and cables.

#### **Connecting the Board**

Connect the FRDM-IMX93 board to your computer using the provided USB Type-C cable.

#### **Powering On the Board**

Use the power button on the board to turn it on. The board should boot up and be ready for use.

# **Accessing Features**

Explore the various features of the board such as camera interface, display interface, and connectivity options like Wi-Fi and Ethernet.

## **Development**

If you are a developer, refer to the user manual for detailed information on setting up configurations for development purposes.

# Frequently Asked Questions (FAQ)

- Q: Can I expand the memory on the FRDM-IMX93 board?

- A: The board supports uSDHC for additional storage expansion.

- Q: What is the processor speed of the i.MX 93 applications processor?

- A: The processor can speed up to 1.7 GHz with a dual Arm Cortex-A55 + Arm Cortex-M33 core configuration.

- Q: How can I connect to Wi-Fi on the FRDM-IMX93 board?

A: The board has onboard Wi-Fi support through SDIO interface. Refer to the user manual for detailed instructions on connecting to Wi-Fi.

#### **Document information**

| Information | Content                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | i.MX 93, FRDM-IMX93, UM12181                                                                                                                                                                          |

| Abstract    | The FRDM i.MX 93 development board (FRDM-IMX93 board) is a low-cost platform designed to show the most commonly used features of the i.MX 93 applications processor in a small and low- cost package. |

#### FRDM-IMX93 overview

The FRDM i.MX 93 development board (FRDM-IMX93 board) is a low-cost platform designed to show the most commonly used features of the i.MX 93 Applications Processor in a small and low-cost package. The FRDM-IMX93 board is an entry-level development board, which helps developers to get familiar with the processor before investing a large amount of resources in more specific designs.

This document includes system setup and configurations, and provides detailed information on the overall design and usage of the FRDM board from a hardware system perspective.

#### **Block diagram**

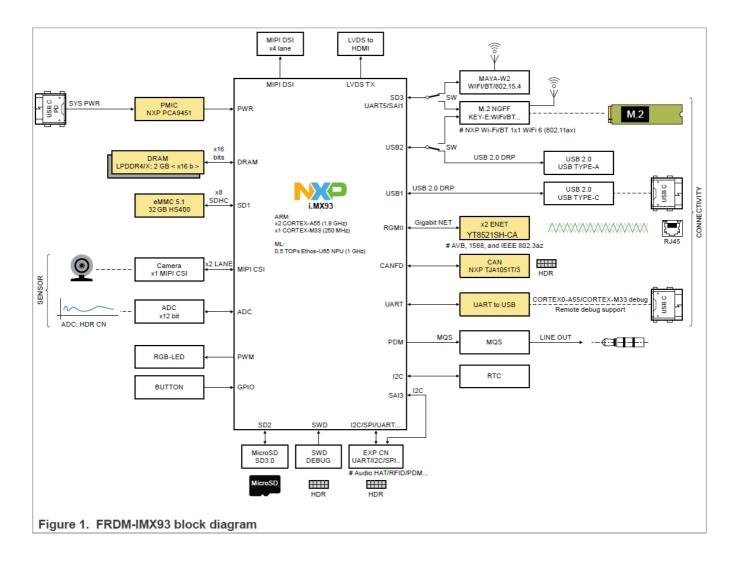

Figure 1 shows the FRDM-IMX93 block diagram.

# **Board features**

Table 1 lists the features of FRDM-IMX93.

Table 1. FRDM-IMX93 features

| Board feature          | Target processor feature used                 | Description                                                                                                                                                                                                                                                           |

|------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications processor |                                               | The i.MX 93 applications processor features a dual Arm Cortex-A 55 + Arm Cortex-M33 core speeding up to 1.7 GHz, a neural processing unit (NPU) of 0.5 TOPS  Note: For more detail on the i.MX 93 processor, see the i.MX 93 Applications Processor Reference Manual. |

| USB interface          | USB 2.0 high-speed host and device controller | <ul> <li>x1 USB 2.0 Type C connector</li> <li>x1 USB 2.0 Type A connector</li> </ul>                                                                                                                                                                                  |

| DRAM memory            | DRAM controller and PHY                       | 2 GB LPDDR4X (Micron MT53E1G16D1FW-046 AAT:A)                                                                                                                                                                                                                         |

| Mass storage           | uSDHC                                         | 32 GB eMMC5.1 (FEMDRM032G-A3A55)     MicroSD card connector (SD3.0 supported)                                                                                                                                                                                         |

| Boot configuration        |                                                     | <ul> <li>Default boot mode is single boot from the eMMC device</li> <li>Board also supports SD card boot</li> </ul>                                                                                                                                                                                                      |  |

|---------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Camera interfa            | MIPI CSI                                            | One CSI (x2 data lane) interface, FPC cable connector (P6)                                                                                                                                                                                                                                                               |  |

| Disabouistada             | MIPI DSI                                            | x4 data lane MIPI DSI interface, FPC cable connector (P7)                                                                                                                                                                                                                                                                |  |

| Display interfac<br>e     | HDMI                                                | x4 data lane LVDS to HDMI converter chip (IT6263) connected to HDMI connector, P5                                                                                                                                                                                                                                        |  |

| Ethernet interfa<br>ce    | Two ENET controllers                                | <ul> <li>10/100/1000 Mbit/s RGMII Ethernet with one RJ45 connector with TSN support (P3) connected with external PHY, YT8521</li> <li>10/100/1000 Mbit/s RGMII Ethernet with one RJ45 connector (P4) connected with external PHY, YT8521</li> </ul>                                                                      |  |

| I/O expanders             | CAN, I2C/I3C, analog-to-<br>digital converter (ADC) | One 10-pin 2×5 2.54 mm connector P12 provides:  • One high-speed CAN transceiver TJA1051GT/3 connection  • 3-pin header for I2C/I3C expansion  • Two-channel ADC support                                                                                                                                                 |  |

| Onboard Wi-Fi             | SDIO, UART, SPI, SAI                                | Onboard Wi-Fi 6 / Bluetooth 5.4 module                                                                                                                                                                                                                                                                                   |  |

| Wi-Fi/Bluetooth interface | USB, SDIO, SAI, UART, I2<br>C, and GPIO             | One M.2/NGFF Key E mini card 75-pin connector, P8, supporting USB, SDIO, SAI, UART, I2C, and Vendor-defined SPI interfaces <b>Note:</b> By default, these signals are connected with the onboard Wi-Fi module, however, to use this M.2 slot, you must rework resi stors (see Table 15).                                 |  |

| Audio                     | MQS                                                 | MQS support                                                                                                                                                                                                                                                                                                              |  |

| Debug interfac<br>e       |                                                     | <ul> <li>USB-to-UART device, CH342F</li> <li>One USB 2.0 Type-C connector (P16) of CH342F provides tw o COM ports:         <ul> <li>The first COM port is used for Cortex A55 system debug</li> <li>The second COM port is used for Cortex M33 system debug</li> </ul> </li> <li>Serial Wire Debug (SWD), P14</li> </ul> |  |

| Expansion port            |                                                     | One 40-pin dual-row pin header for I2S, UART, I2C, and GPIO ex pansion                                                                                                                                                                                                                                                   |  |

| Power                     |                                                     | <ul> <li>One USB 2.0 Type-C connector for power delivery only</li> <li>PCA9451AHNY PMIC</li> <li>Discrete DCDC/LDO</li> </ul>                                                                                                                                                                                            |  |

| PCB FRDM-IMX93: 105 mm × 65 mm, 10-layer |

|------------------------------------------|

|------------------------------------------|

#### Table 1. FRDM-IMX93 features...continued

| Board feature         | Target processor feature used | Description |

|-----------------------|-------------------------------|-------------|

| Orderable part number |                               | FRDM-IMX93  |

# **Board kit contents**

Table 2 lists the items included in the FRDM-IMX93 board kit.

# Table 2. Board kit contents

| Item description                                  | Quantity |

|---------------------------------------------------|----------|

| FRDM-IMX93 board                                  | 1        |

| USB 2.0 Type-C Male to Type-A Male assembly cable | 2        |

| FRDM-IMX93 Quick Start Guide                      | 1        |

# **Board pictures**

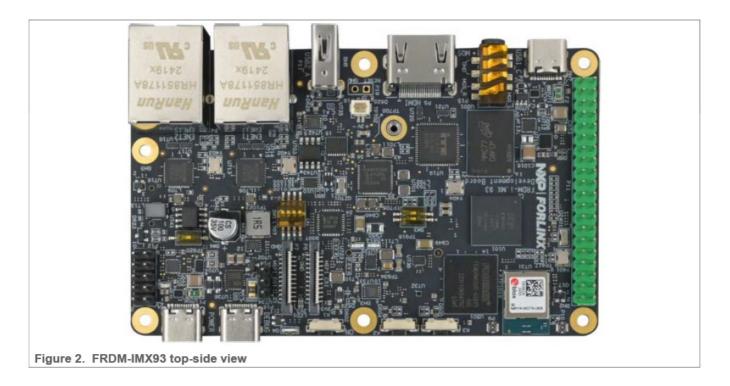

Figure 2 shows the top-side view of the FRDM-IMX93 board.

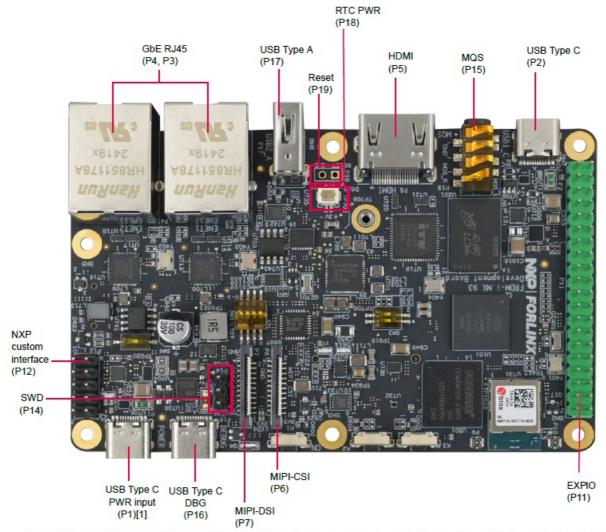

Figure 3 shows the connectors available on the top side of the FRDM-IMX93 board.

[1] - USB Type C PWR input (P1) shown in the figure is the only power supply port, and must always be supplied for system running.

Figure 3. FRDM-IMX93 connectors

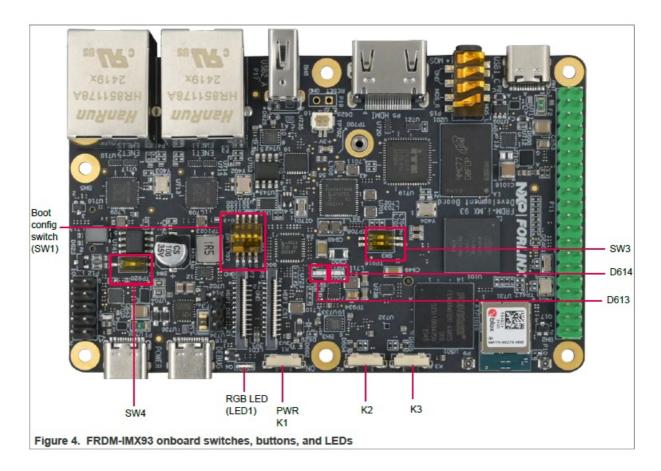

Figure 4 shows the onboard switches, buttons, and LEDs available on the FRDM-IMX93 board.

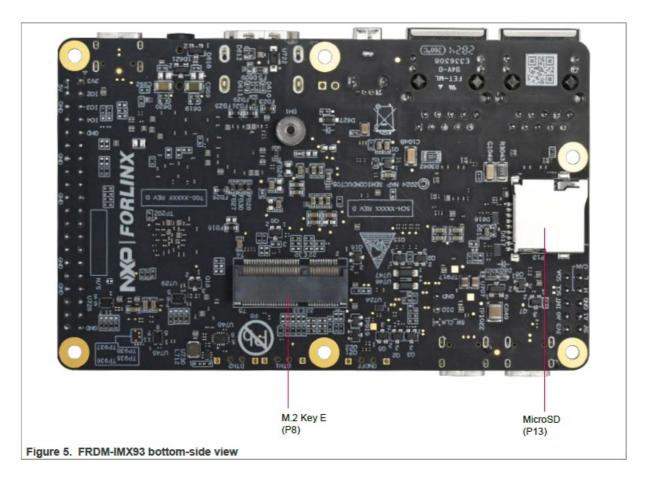

Figure 5 shows the bottom-side view, and also highlights the connectors available at the bottom side of the FRDM-IMX93 board.

# **Connectors**

See Figure 3 and Figure 5 for connectors position on the board. Table 3 describes the FRDM-IMX93 board connectors.

Table 3. FRDM-IMX93 connectors

| Part identifi<br>er | Connector type       | Description            | Reference section |

|---------------------|----------------------|------------------------|-------------------|

| P1, P2, P16         | USB 2.0 Type C       | USB connector          | Section 2.19.2    |

| P3, P4              | RJ45 jack            | Ethernet connectors    | Section 2.17      |

| P5                  | HDMI A connector     | HDMI connector         | Section 2.16      |

| P6                  | 22-pin FPC connector | MIPI CSI FPC connector | Section 2.14      |

| P7                  | 22-pin FPC connector | MIPI DSI FPC connector | Section 2.15      |

| P9 (DNP)            | U.FL connector       | RF antenna connector   | Section 2.11      |

| P10 (DNP)           | U.FL connector       | RF connector           | Section 2.11      |

| P8                  | 75-pin connector     | M.2 socket KEY-E       | Section 2.10      |

| P11                 | 2×20-pin connector   | GPIO expansion         | Section 2.18      |

| P12                 | 2×5-pin connector    | I/O connector          | Section 2.4       |

| Part identifi<br>er | Connector type                | Description           | Reference section                    |

|---------------------|-------------------------------|-----------------------|--------------------------------------|

| P13                 | MicroSD push- push conn ector | MicroSD 3.0           | Section 2.8                          |

| P14                 | 1×3-pin 2.54 mm connect or    | SWD connector         | Section 2.19.1                       |

| P15                 | 3.5 mm headphone jack         | MQS connector         | Section 2.6                          |

| P17                 | USB 2.0 Type A                | USB connector         | Section 2.13                         |

| P18                 | JST_SH_2P                     | RTC battery connector | For detail, see the board schem atic |

| P19                 | 1×2-pin connector             | SYS_nRST connector    | For detail, see the board schem atic |

# **Push buttons**

Figure 4 shows the push buttons available on the board. Table 4 describes the push buttons available on FRDM-IMX93.

Table 4. FRDM-IMX93 push buttons

| Part identifier     | Switch name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part identifier  K1 | Power button | Description  The i.MX 93 applications processor supports the use of a button input signal to request main SoC power state changes (that is, ON or OFF) from the PMIC. The ON/OFF button is connected to the ONOFF pin of the i.MX 93 processor.  In the ON state:  If the ON/OFF button is held longer than the debounce time, the power off interrupt is gener ated  If the button is held longer than the defined max timeout (approx. 5 s), the state will transit from ON to OFF, and send PMIC_ON_REQ signal to turn off the powers of PMIC  In the OFF state: |

|                     |              | If the ON/OFF button is held longer than the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |              | OFF-to- ON time, the state will transit from OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                     |              | F to ON, and send PMIC_ON_REQ signal to t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     |              | urn on the powers of PMIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| K2, K3              | User button  | The User buttons are kept for customized use cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

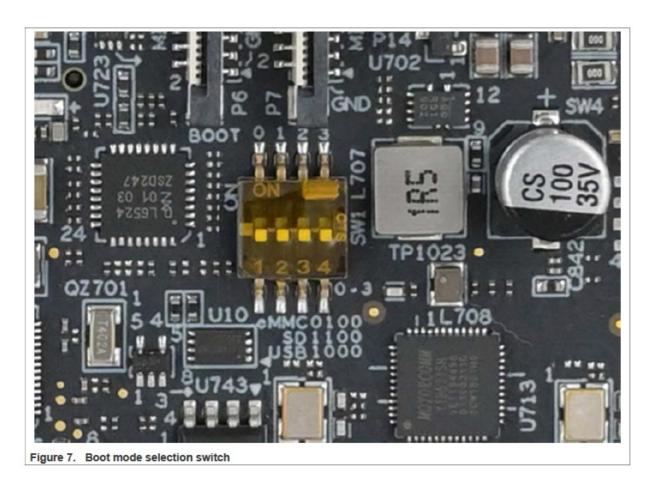

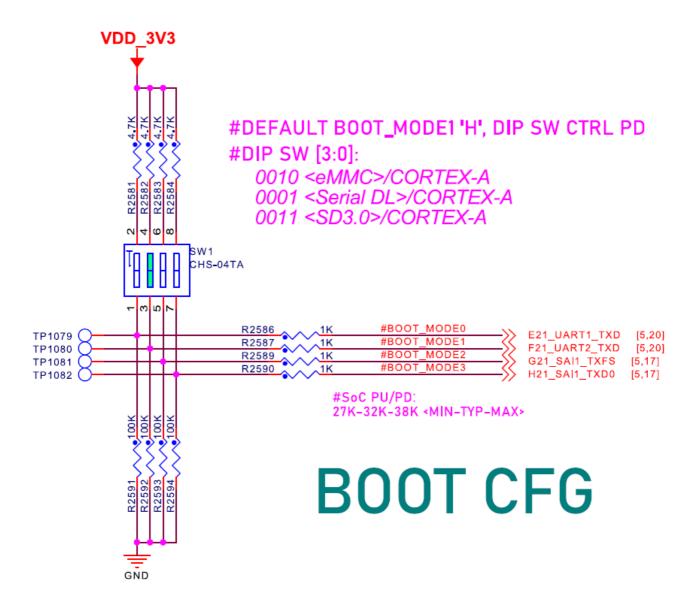

#### **DIP** switch

The following DIP switches are used on the FRDM-IMX93 board.

- 4-bit DIP switch SW1

- 2-bit DIP switch SW3

- 1-bit DIP switch SW4

# If a DIP switch pin is:

- OFF pin value is 0

- ON pin value is 1

The following list describes the description and configuration of the DIP switches available on the board.

- SW1 Provides control for boot mode configuration. For detail, see Section 2.5.

- SW3 Provides control for enabling or disabling the CAN interface signals, CAN\_TXD (GPIO\_IO25) and CAN\_RXD (GPIO\_IO27), on the board.

Table 5. SW3 configuration

| Switch | Signal              | Description                                                                                            |

|--------|---------------------|--------------------------------------------------------------------------------------------------------|

| SW3[1] | CAN_TXD (GPIO_IO25) | <ul> <li>ON (default setting): Enables CAN_TXD signal</li> <li>OFF: Disables CAN_TXD signal</li> </ul> |

| SW3[2] | CAN_RXD (GPIO_IO27) | <ul> <li>ON (default setting): Enables CAN_RXD signal</li> <li>OFF: Disables CAN_RXD signal</li> </ul> |

• SW4 – Provides control for enabling or disabling the CAN split termination RC

# Table 6. SW3 configuration

| Switch | Signal | Description                                                                                                                                                                                      |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW4[1] |        | <ul> <li>ON (default setting): Enables RC termination filter (62 Ω + 56 pF) and configures CAN bus for normal operatio n.</li> <li>OFF: Disables RC termination filter for test mode.</li> </ul> |

# **LEDs**

The FRDM-IMX93 board has light-emitting diodes (LEDs) to monitor system functions, such as power-on and board faults. The information collected from LEDs can be used for debugging purposes.

Figure 4 shows the LEDs available on the board.

Table 7 describes the FRDM-IMX93 LEDs.

Table 7. FRDM-IMX93 LEDs

| Part identifier | LED color              | LED name   | Description (When LED in ON)                                                                                                                                                                                                            |

|-----------------|------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D601            | Red                    | PWR LED    | Indicates 3.3 V power-on status. When 3.3 V is avail able on board, the D601 LED turns ON.                                                                                                                                              |

| LED1            | Red / Green / Blu<br>e | RGB_LED    | User application LEDs. Each of these LEDs can be c ontrolled through a user application.  Red LED connects to target MPU pin GPIO_IO13  Green LED connects to target MPU pin GPIO_IO0  4  Blue LED connects to target MPU pin GPIO_IO12 |

| D613            | GREEN                  | LED_GREEN  | D613 ON – WLAN status indicator. When ON, ind                                                                                                                                                                                           |

| D614            | ORANGE                 | LED_ORANGE | <ul> <li>icates that the WLAN connection is established.</li> <li>D614 ON – Bluetooth status indicator. When ON, i ndicates that the Bluetooth connection is established.</li> </ul>                                                    |

# FRDM-IMX93 functional description

This chapter describes the features and functions of the FRDM-IMX93 board.

**Note:** For details of the i.MX93 MPU features, see i.MX 93 Applications Processor Reference Manual.

# The chapter is divided into the following sections:

- · Section "Processor"

- Section "Power supply"

- · Section "Clocks"

- Section "I2C interface"

- · Section "Boot mode and boot device configuration"

- · Section "PDM interface"

- Section "LPDDR4x DRAM memory"

- Section "SD card interface"

- Section "eMMC memory"

- Section "M.2 connector and Wi-Fi/Bluetooth module"

- Section "CAN interface"

- · Section "USB interface"

- Section "Camera interface"

- Section "MIPI DSI"

- · Section "HDMI interface"

- · Section "Ethernet"

- Section "Expansion connector"

- · Section "Debug interface"

· Section "Board errata"

#### **Processor**

The i.MX 93 applications processor includes dual Arm Cortex-A55 processors with speeds up to 1.7 GHz integrated with an NPU that accelerates machine learning inference. The general-purpose Arm Cortex-M33 running up to 250 MHz is for real-time and low-power processing. Robust control networks are possible via the CAN-FD interface. Also, dual 1 Gbit/s Ethernet controllers, one supporting time sensitive networking (TSN), drive gateway applications with low latency.

# The i.MX 93 is useful for applications such as:

- Smart home

- Building control

- · Contactless HMI

- Commercial

- Healthcare

- Media IoT

Each processor provides a 16-bit LPDDR4/LPDDR4X memory interface and other interfaces for connecting peripherals, such as MIPI LCD, MIPI Camera, LVDS, WLAN, Bluetooth, USB2.0, uSDHC, Ethernet, FlexCAN, and multisensors. For more detailed information about the processor, see the i.MX93 data sheet and i.MX 93 Applications Processor Reference Manual at <a href="https://www.nxp.com/imx93">https://www.nxp.com/imx93</a>.

#### **Power supply**

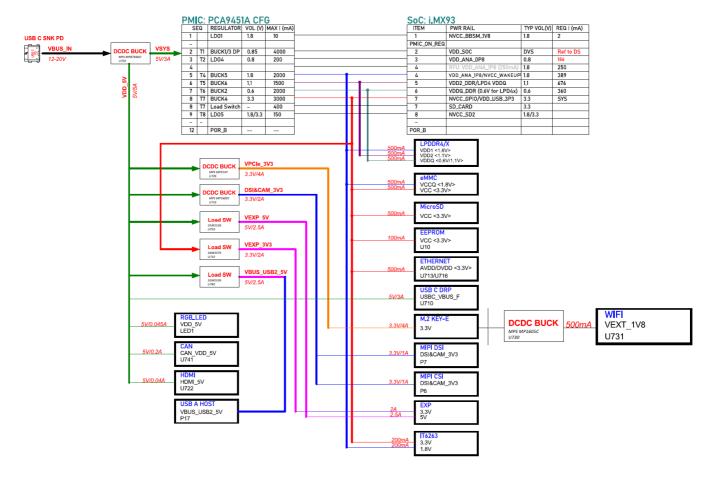

The primary power supply to the FRDM-IMX93 board is VBUS\_IN (12 V - 20 V) through USB Type-C PD connector (P1).

# Four DC buck switching regulators are used:

- MP8759GD (U702) switches VBUS\_IN supply to SYS\_5V (5 V) power supply, which is input power supply for PCA9451AHNY PMIC (U701) and other discrete devices on the board.

- MP1605C (U723) switches VDD\_5V supply to DSI&CAM\_3V3 (3.3 V / 2 A) for MIPI CSI and MIPI DSI.

- MP2147GD (U726) switches VDD 5V supply to VPCIe 3V3 (3.3 V / 4 A) for M.2 / NGFF module (P8).

- MP1605C (U730) switches VPCIe\_3V3 supply to VEXT\_1V8 (3.3 V / 500 mA) for on-board Wi-Fi module MAYA-W27x (U731).

Figure 6 shows the FRDM-IMX93 power supply block diagram.

Figure 6. FRDM-IMX93 power supply

Table 8 describes different power sources available on the board.

Table 8. FRDM-IMX93 power supply devices

| Part<br>identifier<br>designator | Manufacturing part number | Part<br>manufacturer             | Power supply           | Specifications | Description                                                                                                                                                                                                                                                   |

|----------------------------------|---------------------------|----------------------------------|------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U702                             | MP8759GD                  | Monolithic Power<br>Systems Inc. | • DCDC_5V<br>• VSYS_5V | • 5 V at 8 A   | Supplies power to: PMIC PCA9451AHNY (U701)  NX20P3483UK USB PD and Type-C switches (U710)  DC buck MP2147GD (U726) for VPCIe_3V3  DC buck MP1605C (U723) for DSI&CAM_3V3  Load switch SGM2526 (U733) for VRPi_5V  Load switch SGM2526 (U742) for VBUS_USB2_5V |

| U726                             | MP2147GD                  | Monolithic Power Systems Inc.    | VPCIe_3V3              | 3.3 ∨ at 3 A   | Input supply for switch-mode<br>converter MP1605C (U730)                                                                                                                                                                                                      |

|  | Manufacturing p<br>art number | Part manufac<br>turer | Power supply | Specification<br>s | Description |

|--|-------------------------------|-----------------------|--------------|--------------------|-------------|

|--|-------------------------------|-----------------------|--------------|--------------------|-------------|

|      |         |                                       |                                       |                                                                                                | <ul> <li>Supply for WLAN and Blue tooth status indicating LED s (D613 and D614)</li> <li>Supply for onboard Wi-Fi module u-blox MAYA-W27x (U731)</li> </ul> |

|------|---------|---------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U723 | MP1605C | Monolithic Po<br>wer Systems I<br>nc. | DSI&CAM_3V                            | 3.3 V at 2 A                                                                                   | Supplies power to MIPI CSI (P6) and MIPI DSI (P7) interface                                                                                                 |

| U730 | MP1605C | Monolithic Po<br>wer Systems I<br>nc. | VEXT_1V8                              | 1.8 V at 500<br>mA                                                                             | Supplies power to onboard W i-Fi u-blox MAYA-W27x modul e                                                                                                   |

|      |         |                                       | BUCK2: LPD4<br>/x_VDDQ_0V<br>6        | • 0.6 V at 20<br>00<br>mA                                                                      | Supplies power to VDDQ_DD<br>R power supply for CPU DRA<br>M PHY I/O (LPDDR4/X)                                                                             |

|      |         |                                       | BUCK1/3: VD<br>D_SOC_0V8 <sup>[</sup> | VOL (V): 0 .8  Typ VOL ( V):  Dynamic volt age scaling ( DVS) Note: R efer to SoC d ata sheet. | VDD_SOC, power supply for<br>SoC logic and Arm core                                                                                                         |

|      |         |                                       |                                       |                                                                                                |                                                                                                                                                             |

|      |         | NXP                                   |                                       |                                                                                                |                                                                                                                                                             |

| U701 | PCA9451AHNY | Semiconductors | BUCK4: • VDD_3V3 | 3.3 V at 3000<br>mA | Supplies power to:  MIPI DSI/LVDS  NVCC_GPIO, power supply for GPIO when it is in 3.3 V mode  VDD_USB_3P3 pin for USBPHY power  MicroSD  EEPROM  Ethernet ports (P3 and P4)  LVDS to HDMI converter  I2C IO expander PCAL652  4 HEAZ (U725, I2C address: 0x22)  Power source for:  ENET1_DVDD3 and ENET1  AVDD3 supplies  OVDD_3V3 for AVCC_3V3  supplies |

|------|-------------|----------------|------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |             |                | BUCK5: • VDD_1V8 | 1.8 V at 2000<br>mA | Supplies to:  • LPD4/x_VDD1  • eMMC 5.1 device  • LVDS to HDMI converter  • VDD_ANA_1P8, analog co re supply voltage  • NVCC_WAKEUP, digital I/O supply                                                                                                                                                                                                   |

| Part ide<br>ntifier d<br>esignato<br>r | Manufacturing p art number | Part manufac<br>turer | Power supply              | Specification s     | Description                                       |

|----------------------------------------|----------------------------|-----------------------|---------------------------|---------------------|---------------------------------------------------|

|                                        |                            |                       | BUCK6: • LPD4/x_V DD2_1V1 | 1.1 V at 2000<br>mA | Supplies to:  • VDD2_DDR, DDR  PHY supply voltage |

|                                        |                            |                       |                           |                     |                                                   |

| I    | I                                       | I                     |                          |                    |                                                                                                                                                                                       |

|------|-----------------------------------------|-----------------------|--------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                         |                       | LDO1: NVCC_<br>BBSM_ 1V8 | 1.8 V at 10 m      | NVCC BBSM I/O supply                                                                                                                                                                  |

|      |                                         |                       | LDO4: VDD_<br>ANA_0 P8   | 0.8 V at 200<br>mA | Analog core supply voltage                                                                                                                                                            |

|      |                                         |                       | LDO5: NVCC_<br>SD        | 1.8 V / 3.3 V      | MicroSD card                                                                                                                                                                          |

|      |                                         |                       | Load Switch:<br>VSDs_3V3 | 3.3 V              | MicroSD card                                                                                                                                                                          |

| U703 | FDS4435 (Power<br>Trench MOSFET)        | SG MICRO C<br>ORP     | VDD_5V                   | 5 V / 2.5 A        | Supplies to:  • 10-pin dual-row header (P1 2)  • CAN transceiver through C AN_ VDD_5V  • RGB LED  Power source for:  • HDMI_5V  • DSI&CAM_3V3  • VPCIe_3V3  • VRPi_5V  • VBUS_USB2_5V |

| U732 | SGM2525 (Load switch)                   | SG MICRO C<br>ORP     | VRPi_3V3                 | 3.3 V at 2.5 A     | • 40-pin dual-row pin header (P11)                                                                                                                                                    |

| U733 | SGM2525 (Load switch)                   | SG MICRO C<br>ORP     | VRPi_5V                  | 5 V at 2.5 A       | 40-pin dual-row pin header (P11)                                                                                                                                                      |

| U737 | TLV76033DBZR<br>(Voltage regulato<br>r) | Texas Instrum<br>ents | VCC_3V3_ D<br>EBUG       | 3.3 V              | Supplies to 4-bit voltage-level translator used for USB-to-du al UART debug interface                                                                                                 |

| U742 | SGM2526 (Load switch)                   | SG MICRO C<br>ORP     | VBUS_USB2_<br>5 V        | 5 V / 2.5 A        | Supplies to USB2.0 Type-A H ost                                                                                                                                                       |

- 1. BUCK1 and BUCK3 are configured as dual phase mode.

- 2. PCA9451 BUCK1/3 dual phase default output voltage is 0.8 V. Software changes it to 0.95 V for overdrive mode.

For further details on the power sequence needed by the i.MX 93, refer to section "Power sequence" in the i.MX 93 Reference Manual.

#### **Clocks**

FRDM-IMX93 provides all the clocks required for the processor and peripheral interfaces. Table 9 summarizes the specifications of each clock and the component that provides it.

Table 9. FRDM-IMX93 clocks

| Part identifi<br>er | Clock generator    | Clock     | Specifications    | Destination      |

|---------------------|--------------------|-----------|-------------------|------------------|

| Y401                | Crystal oscillator | XTALI_24M | Frequency: 24 MHz | Target processor |

| Part identifi<br>er | Clock generator    | Clock                        | Specifications            | Destination                                                 |

|---------------------|--------------------|------------------------------|---------------------------|-------------------------------------------------------------|

|                     |                    | XTALO_24M                    |                           |                                                             |

| QZ401               | Crystal oscillator | XTALI_32K XTALO_<br>32K      | Frequency: 32.768 k<br>Hz | NVCC_BBSM block of tar get processor                        |

| QZ701               | Crystal oscillator | XIN_32K XOUT_32K             | Frequency: 32.768 k<br>Hz | PCA9451AHNY PMIC                                            |

| Y402                | Crystal oscillator | PHY1_XTAL_I PHY1<br>_XTAL_O  | Frequency: 25 MHz         | Ethernet RMII PHY1                                          |

| Y403                | Crystal oscillator | PHY2_XTAL_I PHY2<br>_XTAL_O  | Frequency: 25 MHz         | Ethernet RMII PHY2                                          |

| Y404                | Crystal oscillator | HDMI_XTALIN HDMI<br>_XTALOUT | Frequency: 27 MHz         | Onboard LVDS to HDMI c<br>onverter module IT6263 (<br>U719) |

# **I2C** interface

The i.MX 93 processor supports a low-power inter-integrated circuit (I2C) module that supports an efficient interface to an I2C-bus as a master. The I2C provides a method of communication between a number of devices available on the FRDM-IMX93 board.

One 10-pin  $2\times5$  2.54 mm connector P12 is provided on the board to support I2C, CAN, and ADC connections. The developers can use the port for some specific application development.

Table 10 explains the I2C, CAN, and ADC header, P12, pinout.

Table 10. 10-pin 2×5 2.54mm I2C, CAN, and ADC header (P12) pinout

| Pin | Signal name | Description                 |

|-----|-------------|-----------------------------|

| 1   | VDD_3V3     | 3.3 V power supply          |

| 2   | VDD_5V      | 5 V power supply            |

| 3   | ADC_IN0     | ADC input channel 0         |

| 4   | ADC_IN1     | ADC input channel 1         |

| 5   | I3C_INT     | I2C/I3C interrupt signal    |

| 6   | GND         | Ground                      |

| 7   | I3C_SCL     | I2C/I3C SCL signal          |

| 8   | CAN_H       | CAN transceiver high signal |

| 9   | I3C_SDA     | I2C/I3C SDA signal          |

| 10  | CAN_L       | CAN transceiver low signal  |

Table 11 describes the I2C devices and their I2C addresses (7-bit) on the board.

Table 11. I2C devices

| Part ident ifier | Device      | I2C address (7-b it)   | Port    | Speed     | Voltag<br>e | Description                      |

|------------------|-------------|------------------------|---------|-----------|-------------|----------------------------------|

| U719             | IT6263      | 0x4C (0b'100110<br>0x) | MX-I2C1 | 1 MHz Fm+ | 3.3 V       | LVDS to HDMI converter           |

| U748             | PCAL6408AHK | 0x20 (0b'010000<br>0x) | MX-I2C1 | 1 MHz Fm+ | 3.3 V       | I/O expander for IRQ<br>/ OUTPUT |

| Part ident ifier | Device       | I2C address (7-b it)      | Port    | Speed     | Voltag<br>e | Description                    |

|------------------|--------------|---------------------------|---------|-----------|-------------|--------------------------------|

| U701             | PCA9451AHNY  | 0x25 (0b'010010<br>1x)    | MX-I2C2 | 1 MHz Fm+ | 3.3 V       | PMIC                           |

| U725             | PCAL6524HEAZ | 0x22 (0b'01000[1<br>0]x)  | MX-I2C2 | 1 MHz Fm+ | 3.3 V       | IO expander for IRQ/<br>OUTPUT |

| U10              | AT24C256D    | 0x50 (0b'101000<br>0x)    | MX-I2C2 | 1 MHz Fm+ | 3.3 V       | EEPROM                         |

| U705             | PTN5110NHQZ  | 0x52 (0b'10100[1<br>0]x)  | MX-I2C3 | 1 MHz Fm+ | 3.3 V       | USB Type-C Power D elivery PHY |

| U712             | PTN5110NHQZ  | 0x50 (0b'10100[0<br>0]x)  | MX-I2C3 | 1 MHz Fm+ | 3.3 V       | USB Type-C Power D elivery PHY |

| U710             | NX20P3483UK  | 0x71 (0b'11100[0<br>1]x)  | MX-I2C3 | 1 MHz Fm+ | 3.3 V       | USB load switch                |

| U740             | PCF2131      | 0x 53 (0b'110101<br>[0]x) | MX-I2C3 | 1 MHz Fm+ | 3.3 V       | External RTC                   |

#### Boot mode and boot device configuration

The i.MX 93 processor offers multiple boot configurations, which can be selected by SW1 on the FRDM-IMX93 board or from the boot configuration stored on the internal eFUSE of the processor. In addition, the i.MX 93 can download a program image from a USB connection when configured in serial download mode. The four dedicated BOOT MODE pins are used to select the various boot modes.

Figure 7 shows the boot mode selection switch.

Table 12 describes the SW1 values used in different boot modes.

Table 12. Boot mode settings

| SW1 [3:0] | BOOT_MODE[3:0] | Boot core | Boot device             |

|-----------|----------------|-----------|-------------------------|

| 0001      | 0001           |           | Serial downloader (USB) |

| 0010      | 0010           | Cortex-A  | uSDHC1 8-bit eMMC 5.1   |

| 0011      | 0011           |           | uSDHC2 4-bit SD3.0      |

On the FRDM-IMX93 board, the default boot mode is from the eMMC device. The other boot device is the microSD connector. Set SW1[3:0] as 0010 to choose uSDHC1 (eMMC) as boot device, set 0011 to choose uSDHC2 (SD), and set 0001 to enter USB serial download.

**Note:** For more information about the boot modes and boot device configuration, see chapter "System Boot" in the i.MX 93 Applications Processor Reference Manual.

Figure 8 shows the connection of SW1 and i.MX 93 boot mode signals.

Figure 8. Boot configuration schematic

#### **PDM** interface

The pulse density modulated (PDM) microphone interface of the processor provides PDM/MQS support on the FRDM-IMX93, and it connects to a 3.5 mm audio jack (P15).

Table 13. Audio jack

| Part identifier | Manufacturing part number | Description                                              |

|-----------------|---------------------------|----------------------------------------------------------|

| P15             | PJ_3536X                  | 3.5 mm audio jack for onboard MQS analog input / out put |

# LPDDR4x DRAM memory

The FRDM-IMX93 board features one 1 Gig  $\times$  16 (1 channel  $\times$ 16 I/O  $\times$  1 rank) LPDDR4X SDRAM chip (MT53E1G16D1FW-046 AAT:A) for a total of 2 GB of RAM memory. The LPDDR4x DRAM memory is connected to the i.MX 93 DRAM controller. The ZQ calibration resistors (R209 and R2941) used by the LPDDR4x chip are 240  $\Omega$  1% to LPD4/x\_VDDQ and the ZQ calibration resistor DRAM\_ZQ used at i.MX93 SoC side is 120  $\Omega$  1% to GND. In the physical layout, the LPDDR4X chip is placed at the top side of the board. The data traces are not necessarily connected to the LPDDR4x chips in sequential order. Instead, the data traces are connected as best determined by the layout and other critical traces for the ease of routing.

The FRDM-IMX93 DRAM part is MT53E1G16D1FW-046 AAT:A that supports both LPDDR4X and LPDDR4 modes, however, LPDDR4X has been selected as the default option on the board.

#### To verify LPDDR4, the two ways are as follows:

- Rework DRAM VDDQ power to 1.1 V to support LPDDR4 by performing the following steps:

- 1. Remove R704

- 2. Install R702

- 3. Make sure that the DRAM parameters meet the LPDDR4 requirement

Figure 9. LPDDR4 rework

No hardware rework is required. Change the DRAM VDDQ power to 1.1 V by software to configure the PMIC by I2C after system power on.

#### SD card interface

The target processor has three ultra secured digital host controller (uSDHC) modules for SD/eMMC interface support. The uSDHC2 interface of the i.MX 93 processor connects to the MicroSD card slot (P13) on the FRDM-IMX93 board. This connector supports one 4-bit SD3.0 MicroSD card. To select it as the boot device of the board, see Section 2.5.

#### eMMC memory

The eMMC memory (at the SOM board) is connected to the uSDHC1 interface of the i.MX 93 processor, which can support eMMC 5.1 devices. It is the default boot device of the board. Table 12 describes the boot settings. Table 14 describes the eMMC memory device that is supported by the uSDHC1 interface.

Table 14. Supported eMMC device

| Part identifie r | Part number      | Configuration | FBGA      | Manufacturer | Memory siz<br>e |

|------------------|------------------|---------------|-----------|--------------|-----------------|

| U501             | FEMDRM032G-A3A55 | 256 Gb x1     | TFBGA-153 | FORESEE      | 32 GB           |

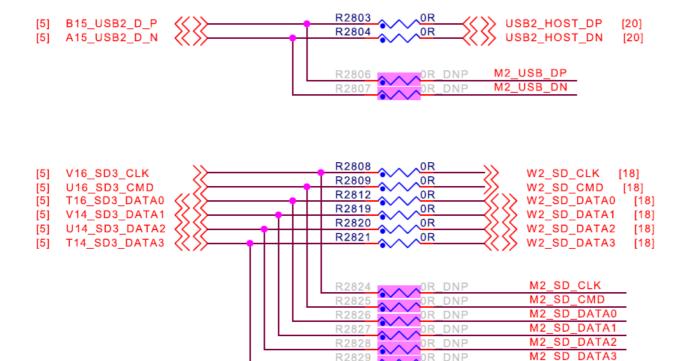

#### M.2 connector and Wi-Fi/Bluetooth module

The FRDM-IMX93 board supports the M.2/NGFF Key E mini card 75-pin connector, P8. The M.2 mini card connector supports USB, SDIO, SAI, UART, I2C, and GPIO connection. By default, these signals are connected with the onboard Wi-Fi module, however, to use this M.2 slot, the following resistors must be reworked.

Table 15. Resistors rework for M.2 slot usage

| Resistors DNP                            | Resistors install                        |  |

|------------------------------------------|------------------------------------------|--|

| R2808, R2809, R2812, R2819, R2820, R2821 | R2824, R2825, R2826, R2827, R2828, R2829 |  |

| R3023, R3024, R2958, R3028               | R2960, R2860                             |  |

| R2854, R2855                             | R2851, R2853                             |  |

| R3038, R2870, R2871                      | R3037, R2866, R2867                      |  |

| R2796, R2798, R2800, R2802               | R2788, R2791, R2792, R2794               |  |

| R2797, R2799, R2801, R2805               | R2789, R2790, R2793, R2795               |  |

| R2832, R2834, R2836, R2838               | R2833, R2835, R2837, R2839               |  |

The M.2 connector can be used for Wi-Fi / Bluetooth card, IEEE802.15.4 Radio, or 3G / 4G cards. Table 16 describes the pinout of the M.2 mini card connector (P8).

Table 16. M.2 mini card connector (P8) pinout

| Pin nu<br>mber | M.2 mini card connector pin    | Connection details                                                                                 |  |

|----------------|--------------------------------|----------------------------------------------------------------------------------------------------|--|

| 2, 4, 72       | 3V3_1, 3V3_2, 3V3_3, 3V<br>3_4 | Connected to VPCIe_3V3 power supply                                                                |  |

| 6              | LED1                           | Connected to M.2 Green LED, D613                                                                   |  |

| 8              | I2S_SCK                        | Connected to SAI1_TXC processor pin if R2788 is populated                                          |  |

| 10             | 12S_WS                         | Connected to SAI1_TXFS processor pin if R2791 is populated                                         |  |

| 12             | I2S_SD_IN                      | Connected to SAI1_RXD processor pin if R2794 is populated                                          |  |

| 14             | I2S_SD_OUT                     | Connected to SAI1_TXD processor pin if R2792 is populated                                          |  |

| 16             | LED2                           | Connected to M.2 Orange LED, D614                                                                  |  |

| 20             | UART_WAKE                      | M2_UART_nWAKE input for I/O expander (PCAL6524HEAZ, P0_3, I2C address: 0x22) if R2853 is populated |  |

| 22             | UART_RXD                       | Connected to UART5_RXD if R2835 is populated                                                       |  |

| 32             | UART_TXD                       | Connected to UART5_TXD if R2833 is populated                                                       |  |

| 34             | UART_CTS                       | Connected to UART5_CTSI if R2839 is populated                                                      |  |

| 36             | UART_RTS                       | Connected to UART5_RTSO if R2837 is populated                                                      |  |

| 38             | VEN_DEF1                       | Connected to SPI3_MOSI if R2790 is populated                                                       |  |

| 40             | VEN_DEF2                       | Connected to SPI3_MISO if R2795 is populated                                                       |  |

| 42             | VEN_DEF3                       | Connected to SPI3_CLK if R2793 is populated                                                        |  |

| Pin nu<br>mber | M.2 mini card connector pin | Connection details                                                                              |  |

|----------------|-----------------------------|-------------------------------------------------------------------------------------------------|--|

| 50             | SUSCLK                      | Connected to PMIC_32K_OUT, generated by PCA9451AHNY PMIC                                        |  |

| 52             | PERST0                      | M2_nRST input for I/O expander (PCAL6524HEAZ, P2_2, I2C address: 0x22)                          |  |

| 54             | W_DISABLE2                  | M2_nDIS2 input for I/O expander (PCAL6524HEAZ, P2_3, I2C address: 0x22) if R2867 is populated   |  |

| 56             | W_DISABLE1                  | M2_nDIS1 input for I/O expander (PCAL6524HEAZ, P2_4, I2C address: 0x22) if R2866 is populated   |  |

| 58             | I2C_DATA                    | Connected to SDAL pin of PCA9451AHNY PMIC                                                       |  |

| 60             | I2C_CLK                     | Connected to SCLL pin of PCA9451AHNY PMIC                                                       |  |

| 62             | ALERT                       | M2_nALERT input for I/O expander (PCAL6524HEAZ, P1_2, I2C addres s: 0x22) if R2860 is populated |  |

| 3              | USB_D+                      | Connected to USB2_D_P processor pin if R2806 is populated                                       |  |

| 5              | USB_D-                      | Connected to USB2_D_N if R2807 is populated                                                     |  |

| 9              | SDIO_CLK                    | Connected to the SD3_CLK processor pin and processor interface SDH C3 if R2824 is populated     |  |

| 11             | SDIO_CMD                    | Connected to the SD3_CMD processor pin and processor interface SDH C3 if R2825 is populated     |  |

| 13             | SDIO_DATA0                  | Connected to the SD3_DATA0 processor pin and processor interface SD HC3 if R2826 is populated   |  |

| 15             | SDIO_DATA1                  | Connected to the SD3_DATA1 processor pin and processor interface SD HC3 if R2827 is populated   |  |

| 17             | SDIO_DATA2                  | Connected to the SD3_DATA2 processor pin and processor interface SD HC3 if R2828 is populated   |  |

| 19             | SDIO_DATA3                  | Connected to the SD3_DATA3 processor pin and processor interface SD HC3 if R2829 is populated   |  |

| 21             | SDIO_WAKE                   | Connected to the CCM_CLKO1 processor pin of NVCC_WAKEUP modul e if R2851 is populated           |  |

| 23             | SDIO_RST                    | SD3_nRST output from I/O expander (PCAL6524HEAZ, P1_4, I2C address: 0x22) if R3037 is populated |  |

| 55             | PEWAKE0                     | PCIE_nWAKE input for I/O expander (PCAL6524HEAZ, P0_2, I2C address: 0x22) if R2868 is populated |  |

For further details about i.MX 93 interfaces, see i.MX 93 Applications Processor Reference Manual.

The FRDM-IMX93 board features a Tri-radio (Wi-Fi 6, Bluetooth 5.4, and 802.15.4) module that interfaces with the SD2, UART5, SAI1, and SPI3 controller of the target processor.

Table 17. Tri-radio module

| Part identifier | Manufacturing part number | Description                                                                       |

|-----------------|---------------------------|-----------------------------------------------------------------------------------|

| U731            | MAYA-W27x (u-blox)        | Host-based Wi-Fi 6, Bluetooth 5.4, and 802.15.4 mod ules for the IoT applications |

The two antenna pins (RF\_ANT0 and RF\_ANT1) of the module connects to U.FL connectors P9 and P10 (DNP by default). The module is supplied with VPCIe 3V3, VEXT 1V8, and VDD 1V8.

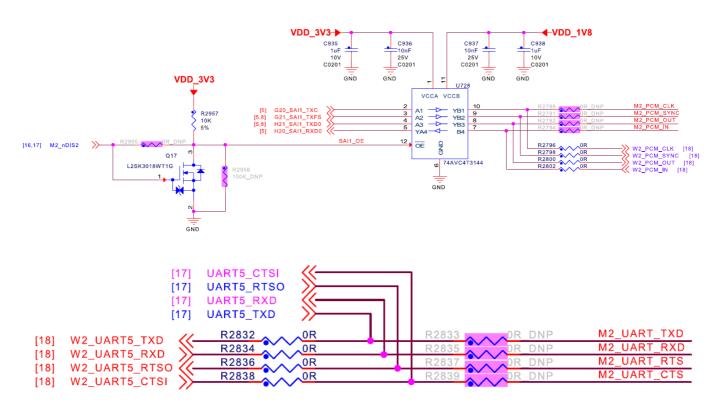

The MAYA-W27x module and M.2 connector share several interface lines on the FRDM-IMX93 board. Zero-ohm resistors enable signal selection between these components.

#### **SD3 Interface**

The SD3 interface lines are shared between the MAYA-W27x module and the M.2 connector. Zero-ohm resistors select either the MAYA-W27x module (default setting) or the M.2 connector.

#### **UART5** Interface

Similarly, the UART5 interface lines are shared between the MAYA-W27x module and the M.2 connector. Zero-ohm resistors select either the MAYA-W27x module (default setting) or the M.2 connector.

#### **SAI1 Interface**

The SAI1 interface lines are shared between the MAYA-W27x module and the M.2 connector. Zero-ohm resistors select either the MAYA-W27x module (default setting) or the M.2 connector for 1.8 V translated signals, generated using the 74AVC4T3144 bidirectional voltage translator (U728).

#### **SPI3 Interface**

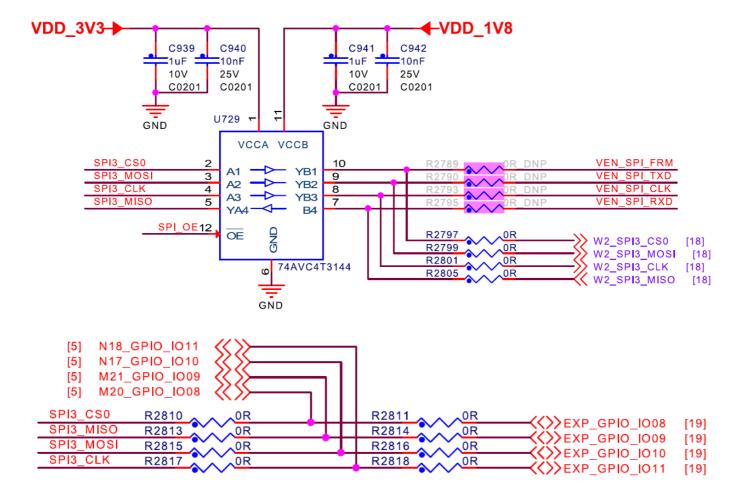

The SPI3 signals (CLK, MOSI, MISO, and CS0) are multiplexed with GPIO\_IO[08, 09, 10, 11] signals, respectively. These SPI3 signals are shared between the MAYA-W27x module and the M.2 connector. Zero-ohm resistors select either the MAYA-W27x module (default setting) or the M.2 connector for 1.8 V translated signals, generated using the 74AVC4T3144 bidirectional voltage translator (U729).

```

R2830

Y2_JTAG_TDO

W1_JTAG_TDI

UART5_TXD [17]

UART5_RXD

R3017

[6,19] W2_JTAG_TMS > [6,19] Y1_JTAG_TCK

->> UART5_RTSO [17]

R3018

UART5_CTSI [17]

M2 SD nWAKE

[6] A22_SD3_nWAKE

M2_UART_nWAKE

[16] UART_nWAKE

[16,19] PCIE_nWAKE

0R

WL_WAKE_HOST [18]

R2855

0R

W2_BT_154_WAKE_HOST

10K 5%

R2862

R2859

M2_SD_nRST

OR DNP

[16]

SD3_nRST

M2 DIS1

R2866

[16,17]

M2_nDIS1

M2_DIS2

[16,17]

M2 nDIS2

```

0R

0R

W2\_WL\_RST [18]

W2\_nDIS1 [18]

W2\_BT\_154\_RST

R3038

R2870

R2871

Figure 10. Resistors configuration for SD3

Figure 11. Resistors configuration for SAI1, UART5, and SPI3

#### **CAN** interface

The i.MX93 processor supports a controller area network (CAN) module that is a communication controller implementing the CAN protocol according to the CAN with flexible data rate (CAN FD) protocol and the CAN 2.0B protocol specification. The processor supports two CAN FD controllers. On the FRDM-IMX93 board, one of the controllers is connected to the high-speed CAN transceiver TJA1051T/3. The high-speed CAN transceiver drives CAN signals between the target processor and a 10-pin  $2\times5$  2.54 mm header (P12) to its physical two-wire CAN bus. The CAN\_TXD and CAN\_RXD signals are multiplexed on GPIO\_IO25 and GPIO\_IO27, respectively. On the board, a 2-bit DIP switch (SW3) is used to control the CAN signals. For SW3 detail, see Section 1.7. The CAN\_STBY signal from the IO expander PCAL6524HEAZ (U725, P2\_7, I2C address: 22) enables / disables CAN standby mode. The CAN interface circuit includes the split termination RC filter ( $62\Omega + 56pF$ ) for noise rejection and signal integrity. The switch SW4 is provided for enabling/disabling the RC filter. For SW4 detail, see Section 1.7. The HS-CAN transceiver and header are described in Table 18.

Table 18. High-speed CAN transceiver and header

| Part identifier | Manufacturing part number | Description                                                                                                                                                                                |

|-----------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U741            | TJA1051T/3                | High-speed CAN transceiver. Provides an interface between a CA N protocol controller and the physical two-wire CAN bus.                                                                    |

| P12             | Not applicable            | 10-pin 2×5 2.54 mm connector (P12). It is connected to the CAN b us and allows external connection with the bus.  Note: Table 10 explains pinout for the 10-pin 2×5 2.54 mm connector P12. |

Note: For details about TJA1051, see TJA1051 data sheet at <a href="nxp.com">nxp.com</a>.

#### **USB** interface

The i.MX 93 applications processor features two USB 2.0 controllers, with two integrated USB PHYs. On the FRDM-IMX93 board, one is used for the USB2.0 Type-C Port (P2) and the other is used for USB2.0 Type-A Port (P17).

Table 19 describes the USB ports available on the board.

Table 19. USB ports

| Part identifi<br>er | USB Port Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2                  | USB2.0 Type-C | Connects to full-speed USB host and device controller (USB 1) of targ et processor. It can operate as a device or host. The USBC_VBUS sig nal controls the VBUS drive for the USB port.                                                                                                                                                                                                                                     |

| P17                 | USB2.0 Type-A | Connects to full-speed USB host and device controller (USB 2) of targ et processor. It can operate as a device or host. The USB2_VBUS sig nal controls the VBUS drive for the USB port. The USB2_DP and US B2_DN signals from the USB2 controller of the target processor connect to USB2 Type A port (P17) by default. These signals can be connected to M.2 card connecter (P6) by solder/DNP R2803, R2804, R2806, R2807. |

| P1                  | USB Type-C PD | It is used for power only. It does not support USB data transfer. It is the only power supply port therefore it must always be supplied for system power.                                                                                                                                                                                                                                                                   |

| P16                 | USB Type-C    | It is used for system debug purpose. For detail, see the system debug section.                                                                                                                                                                                                                                                                                                                                              |

#### Camera interface

The i.MX 93 processor includes a mobile industry processor interface (MIPI) camera serial interface 2 (CSI-2) receiver that handles image sensor data from camera modules and supports up to 2 data lanes. The MIPI CSI-2 signals are connected to an FPC connector to which the RPI-CAM-MIPI (Agile Number: 53206) accessory card can be plugged in.

# The description of the FPC connector is as below:

• Part identifier: P6

• Table 20 describes FPC connector pinout

# Table 20. MIPI CSI connector (P6) pinout

| Pin number              | Signal          | Description                                                                           |

|-------------------------|-----------------|---------------------------------------------------------------------------------------|

| 1, 4, 7, 10, 13, 16, 19 | GND             | Ground                                                                                |

| 2                       | MIPI_CSI1_D0_N  | MIPI CSI data channel 0                                                               |

| 3                       | MIPI_CSI1_D0_P  | Will I OSI data Chamber 0                                                             |

| 5                       | MIPI_CSI1_D1_N  | MIPI CSI data channel 1                                                               |

| 6                       | MIPI_CSI1_D1_P  | Will I OSI data Chamber I                                                             |

| 8                       | MIPI_CSI1_CLK_N | MIPI CSI clock signal                                                                 |

| 9                       | MIPI_CSI1_CLK_P | Will I Got clock signal                                                               |

| 17                      | CSI_nRST        | Reset signal from I/O expander U725 (PCAL6524 HEAZ, P2_6, I2C address: 0x22)          |

| 18                      | CAM_MCLK        | 3.3 V voltage translated input from CCM_CLKO3 p in (CSI_MCLK) of the target processor |

| 20                      | USB_I2C_SCL     | 3.3 V I2C3 SCL signal                                                                 |

| 21                      | USB_I2C_SDA     | 3.3 V I2C3 SDA signal                                                                 |

| 22                      | DSI&CAM_3V3     | 3.3 V power supply                                                                    |

# MIPI DSI

The i.MX 93 processor supports MIPI display serial interface (DSI) that supports up to four lanes and the resolution can be up to 1080p60 or 1920x1200p60.

The MIPI DSI data and clock signals from the target processor are connected to one 22-pin FPC connector (P7). Table 21 describes DSI connector pinout.

Table 21. MIPI DSI connector (P7) pinout

| Pin number              | Signal       | Description                                                                    |

|-------------------------|--------------|--------------------------------------------------------------------------------|

| 1, 4, 7, 10, 13, 16, 19 | GND          | Ground                                                                         |

| 2                       | DSI_DN0      | MIPI DSI data channel 0                                                        |

| 3                       | DSI_DP0      | Will I DOI data Chamber 0                                                      |

| 5                       | DSI_DN1      | MIPI DSI data channel 1                                                        |

| 6                       | DSI_DP1      | - WIII I DOI GATA CHAIINEL I                                                   |

| 8                       | DSI_CN       | MIPI DSI clock signal                                                          |

| 9                       | DSI_CP       | Will I DOI Clock signal                                                        |

| 11                      | DSI_DN2      | MIPI DSI data channel 2                                                        |

| 12                      | DSI_DP2      | - WIII I DOI GATA CHAIINEI Z                                                   |

| 14                      | DSI_DN3      | MIPI DSI data channel 3                                                        |

| 15                      | DSI_DP3      | - WIFT DOI GATA CHAIINELS                                                      |

| 17                      | CTP_RST      | Reset signal from I/O expander U725 (PCAL6524HE AZ, P2_1, I2C address: 0x22)   |

| 18                      | DSI_CTP_nINT | Interrupt signal to I/O expander U725 (PCAL6524HE AZ, P0_7, I2C address: 0x22) |

| Pin number | Signal      | Description           |  |

|------------|-------------|-----------------------|--|

| 20         | USB_I2C_SCL | 3.3 V I2C3 SCL signal |  |

| 21         | USB_I2C_SDA | 3.3 V I2C3 SDA signal |  |

| 22         | DSI&CAM_3V3 | 3.3 V power supply    |  |

#### **HDMI** interface

The i.MX 93 processor supports a four data lane LVDS TX display, the resolution can be up to 1366x768p60 or 1280x800p60. These signals are connected to one high-performance single-chip De-SSC LVDS to HDMI converter IT6263. The output of the IT6263 connects to the HDMI connector P5. The connector is as shown in Figure 3.

#### **Ethernet**

The i.MX 93 processor supports two Gigabit Ethernet controllers (capable of simultaneous operation) with support for Energy-Efficient Ethernet (EEE), Ethernet AVB, and IEEE 1588. The Ethernet subsystem of the board is provided by the Motorcomm YT8521SH-CA Ethernet transceivers (U713, U716) which support RGMII and connect to RJ45 connectors (P3, P4). The Ethernet transceivers (or PHYs) receive standard RGMII Ethernet signals from i.MX 93. The RJ45 connectors integrate Magnetic transformer inside, so they can be directly connected to Ethernet transceivers (or PHYs).

Each Ethernet port has a unique MAC address, which is fused into i.MX 93. The Ethernet connectors are labeled clearly on the board.

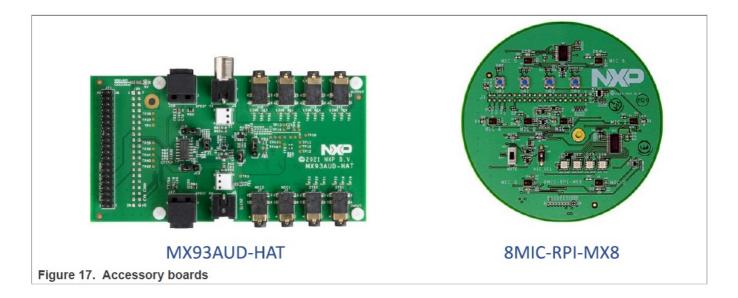

#### **Expansion connector**

One 40-pin dual-row pin connector (P11) is provided on the FRDM-IMX93 board to support I2S, UART, I2C, and

GPIO connections. The header can be used to access various pins or to plug in accessory cards, such as the LCD display TM050RDH03, 8MIC-RPI-MX8 card, MX93AUD-HAT. The connector is shown in Figure 3.

Table 22. P11 pin definition

| Pin number | Net name  | Pin number | Net name  |

|------------|-----------|------------|-----------|

| 1          | VRPi_3V3  | 2          | VRPi_5V   |

| 3          | GPIO_IO02 | 4          | VRPi_5V   |

| 5          | GPIO_IO03 | 6          | GND       |

| 7          | GPIO_IO04 | 8          | GPIO_IO14 |

| 9          | GND       | 10         | GPIO_IO15 |

| 11         | GPIO_IO17 | 12         | GPIO_IO18 |

| 13         | GPIO_IO27 | 14         | GND       |

| 15         | GPIO_IO22 | 16         | GPIO_IO23 |

| 17         | VRPi_3V3  | 18         | GPIO_IO24 |

| 19         | GPIO_IO10 | 20         | GND       |

| 21         | GPIO_IO09 | 22         | GPIO_IO25 |

| 23         | GPIO_IO11 | 24         | GPIO_IO08 |

| Pin number | Net name  | Pin number | Net name  |

|------------|-----------|------------|-----------|

| 25         | GND       | 26         | GPIO_IO07 |

| 27         | GPIO_IO00 | 28         | GPIO_IO01 |

| 29         | GPIO_IO05 | 30         | GND       |

| 31         | GPIO_IO06 | 32         | GPIO_IO12 |

| 33         | GPIO_IO13 | 34         | GND       |

| 35         | GPIO_IO19 | 36         | GPIO_IO16 |

| 37         | GPIO_IO26 | 38         | GPIO_IO20 |

| 39         | GND       | 40         | GPIO_IO21 |

# **Debug interface**

The FRDM-IMX93 board features two independent debug interfaces.

- Serial wire debug (SWD) header (Section 2.19.1)

- USB-to-Dual UART debug port (Section 2.19.2)

## **SWD** interface

The i.MX 93 applications processor has two serial wire debug (SWD) signals on dedicated pins, and those signals are directly connected to the standard 3-pin 2.54 mm connector P14.

## The two SWD signals used by the processor are:

- SWCLK (Serial wire clock)

- SWDIO (Serial wire data input / output)

The SWD connector P14 is shown in Figure 3.

#### **USB** debug interface

The i.MX 93 applications processor has six independent UART ports (UART1 – UART6). On the FRDM-IMX93 board, UART1 is used for Cortex-A55 core, and UART2 is used for Cortex-M33 core. A single chip USB to dual UART is used for the debug purpose. The part number is CH342F. You can download the driver from WCH Website.

After installing the CH342F driver, the PC / USB host enumerates two COM ports connected to the P16 connector through a USB cable:

• COM Port 1: Cortex-A55 system debugging

COM Port 2: Cortex-M33 system debugging

#### You can use the following terminal tools for debugging purposes:

- Putty

- · Tera Term

- Xshell

- Minicom>=2.9

To debug under Linux, make sure CH342F Linux driver is installed. Table 23 describes the required settings.

# Table 23. Terminal setting parameters

| Data rate | 115,200 Baud |

|-----------|--------------|

| Data bits | 8            |

| Parity    | None         |

| Stop bits | 1            |

The USB debug connector P16 is shown in Figure 3.

#### **Board errata**

No board errata.

# Working with accessories

This section describes how a connection can be established between with the FRDM-IMX93 board and

compatible accessory boards.

#### 7-inch Wave share LCD

This section describes how to connect the FRDM-IMX93 board with a 7-inch Wave share LCD using MIPI DSI interface and I2C. It also specifies the changes required in the software configuration to support Wave share LCD.

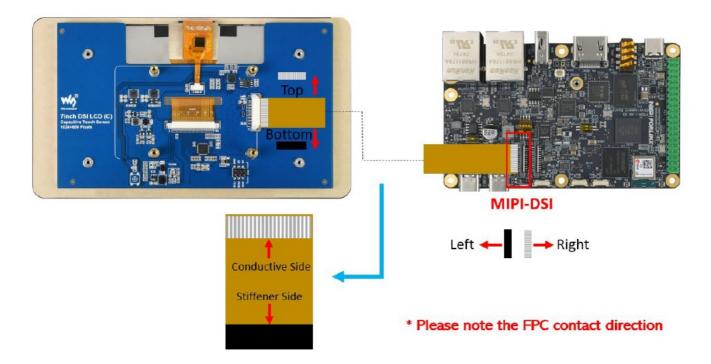

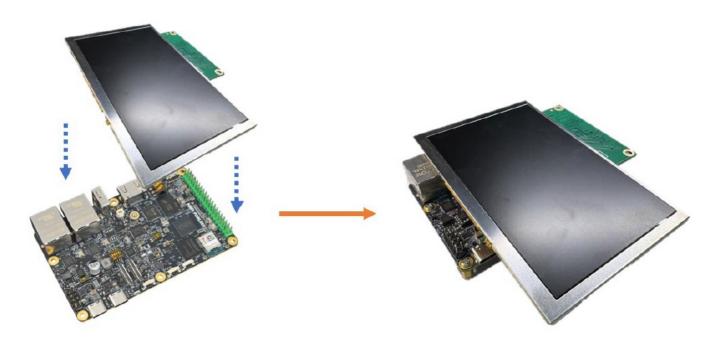

#### Connection of the MIPI DSI interface

To make a connection between a 7-inch Wave share LCD and the FRDM-IMX93 board through the MIPI DSI interface, ensure the following:

#### At LCD side:

- FPC cable orientation: Conductive side up and stiffener side down

- Insert the FPC cable into LCD's FPC connector

#### At FRDM-IMX93 board side:

- FPC cable orientation: Conductive side right and stiffener side left

- Insert FPC cable into the board's FPC connector (P7)

Figure 12. FPC cable connection between 7-Inch Wave share LCD and FRDM-IMX93

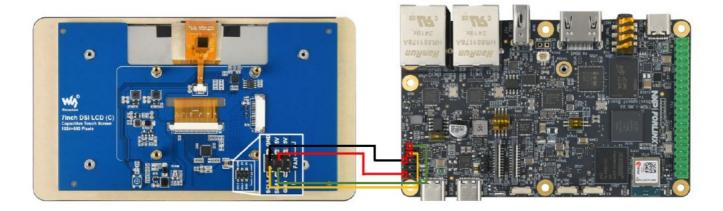

## **Connection of I2C**

Figure 13 shows the I2C signal wires connection between 7-Inch Wave share LCD and FRDM-IMX93.

Figure 13. I2C connection between 7-Inch Wave share LCD and FRDM-IMX93

# Software configuration update

The following steps specify how to replace the default dtb with the custom dtb (imx93-11×11-frdm-dsi.dtb) that supports Wave share LCD.

- 1. Stop at U-Boot

- 2. Use the below commands to replace the default dtb:

\$setenv fdtfile imx93-11×11-frdm-dsi.dtb \$saveenv \$boot

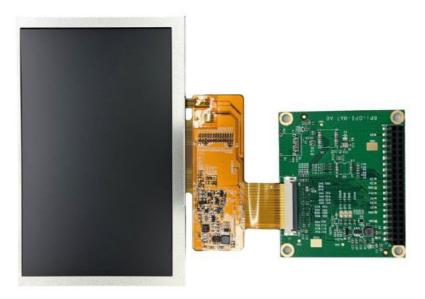

#### 5-inch Tianma LCD

TM050RDH03-41 is a 5" TFT LCD display with 800×480 resolution. This industrial-grade display uses an RGB interface without a touch panel. This display module connects to the FRDM-IMX93 through the EXPI 40-pin connector (P11).

# Connection between Tianma panel and adapter board

Figure 14 shows the FPC connection between the 5-inch Tianma LCD panel and adapter board. Insert the FPC connector with the conductive side up (stiffener side down).

Figure 14. FPC connection between 5-inch Tianma LCD panel and adapter board

#### Connection between adapter board and FRDM-IMX93

Plug 5" Tianma LCD to FRDM-MIX93 through the EXPI 40-pin connector (P11) as shown in Figure 15

Figure 15. 5-inch Tianma LCD connection with FRDM-MIX93 through 40-pin connector

#### Software configuration update

The following steps specify how to replace the default dtb with the custom dtb (imx93-11×11-frdm-tianma-wvga-panel.dtb) that supports Tianma LCD.

- 1. Stop at U-Boot

- 2. Use the below commands to replace the default dtb:

\$setenv fdtfile imx93-11×11-frdm-tianma-wvga-panel. dtb \$saveenv \$boot

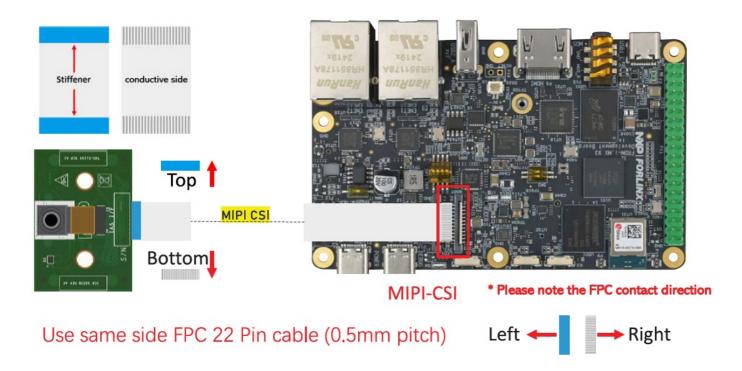

# Camera module (RPI-CAM-MIPI)

The RPI-CAM-MIPI accessory board is a MIPI-CSI camera module adapter. The adapter is based on the AR0144 CMOS image sensor with ONSEMI IAS interface by default, which features a 1/4-inch 1.0 Mp with an active-pixel array of 1280 (H) x 800 (V). The by passable onboard ISP chip allows it to be used with a wide range of SoCs. This accessory board connects to the FRDM-IMX93 board through the 22-pin / 0.5 mm pitch FPC cable.

# Connection between RPI-CAM-MIPI and FRDM-IMX93

Figure 16 shows the FPC cable connection between RPI-CAM-MIPI and FRDM-IMX93.

# At the RPI-CAM-MIPI side:

- FPC cable orientation: Stiffener side up and conductive side down

- Insert FPC cable into RPI-CAM-MIPI FPC connector

#### At FRDM-IMX93 board side:

• FPC cable orientation: Conductive side right and stiffener side left

• Insert the FPC cable into the FPC connector (P7) of the board

Figure 16. FPC connection between RPI-CAM-MIPI and FRDM-IMX93

# Software configuration update

In default BSP, FRDM-IMX93 supports ap1302 + ar0144.

# For the first time use, follow the below steps:

- Download ap1302 firmware from ONSEMI github, and rename it as ap1302.fw

- Copy ap1302.fw to the target board under path /lib/firmware/imx/camera/ (if the folder does not exist, create it)

- Reboot the board as FRDM dtb supports the camera

- Check whether the camera is probed:

root@imx93frdm: ~# dmesg | grep ap1302

[2.565423]ap1302 mipi2-003c:AP1302 Chip ID is 0x265

[2.577072]ap1302 mipi 2-003c: AP1302 is found

[7.477363]mx8-img-md: Registered sensor sub device: ap1302 mipi 2-003c (1)

[7.513503]mx8-img-md: created link

[ap1302 mipi 2-003c]=> [mxc-mipi-csi2.0]7.988932]ap1302 mipi 2-003c: Load firmware successfully.

#### Other accessory boards

There are other accessory boards also that can work with FRDM-IMX93 through EXPI 40-pin interface, such as MX93AUD-HAT and 8MIC-RPI-MX8. To use any such board, check the schematic and layout to determine the direction of the connection between FRDM-IMX93 and the accessory board in advance. Also, choose the right dtb file in the U-Boot stage.

# Software configuration update

• To use the MX93AUD-HAT and 8MIC-RPI-MX8 boards together or use the MX93AUD-HAT board alone, run the following commands at U-Boot to replace the default dtb:

\$setenv fdtfile imx93-11×11-frdm-aud-hat.dtb \$saveenv \$boot

• To use the 8MIC-RPI-MX8 board alone, run the following commands at U-Boot to replace the default dtb:

\$setenv fdtfile imx93-11×11-frdm-8mic.dtb saveenv

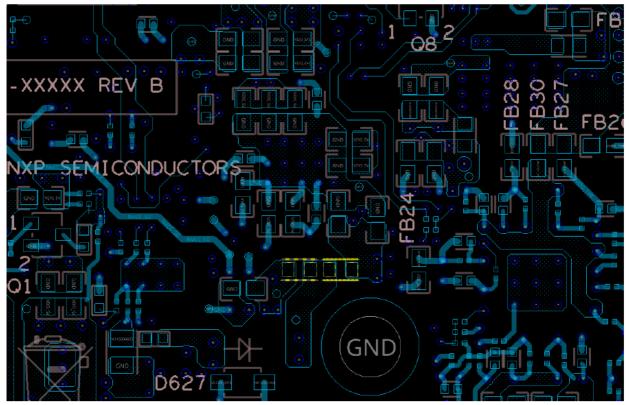

# **PCB** information

The FRDM-IMX93 is made with standard 10-layer technology. The material is FR-4, and the PCB stack-up information is described in Table 24.

Table 24. FRDM-IMX93 board stack up information

| Layer         | Description | Copper (mil) | Generic | Er       | Dielectric thickness (mil) |

|---------------|-------------|--------------|---------|----------|----------------------------|

| 1             | ТОР         | 0.7+Plating  | _       | _        | 1.3                        |

| _             | Dielectric  | _            |         |          | 2.61                       |

| 2             | GND02       | 1.4          | _       | _        | _                          |

| _             | Dielectric  | _            |         |          | 3                          |

| 3             | ART03       | 1.4          | _       | _        | _                          |

| _             | Dielectric  | _            |         |          | 8.8                        |