# NXP FS23 Fail Safe System Basis Chips User Guide

Home » NXP » NXP FS23 Fail Safe System Basis Chips User Guide 🖔

## **Contents**

- 1 NXP FS23 Fail Safe System Basis Chips

- 2 Specifications

- 3 FAQs

- 4 Introduction

- 5 FS23 initialization flow chart example

- 6 Register mapping of fail-safe logic

- 7 Readable registers

- 8 Writable registers

- 9 FS0B and or LIMP0 release calculation procedure

- 10 Watchdog answer procedure

- 11 INIT CRC calculation procedure

- 12 Legal information

- **13 CONTACT INFORMATION**

- 14 Documents / Resources

- 14.1 References

# **NXP FS23 Fail Safe System Basis Chips**

- Product Name: FS23 Fail-Safe System Basis Chip (SBC)

- Manufacturer: NXP Semiconductors

- Compatibility: Suitable for S32K processor-based applications and multivendor processors

- Features: CAN and LIN transceivers, system and safety features, pin-to-pin and software compatibility

- Variants: LDO version to DC-DC version, QM to ASIL B

- Output Voltage Settings: Multiple options are available

- Operating Frequency: Configurable

Powerup Sequencing: Customizable

#### **FAQs**

- Q: What are the key features of the FS23 SBC?

- A: The FS23 SBC features CAN and LIN transceivers, scalability options, system and safety features, and compatibility with various processors.

- Q: Where can I find more detailed information about the FS23 device?

- A: Detailed information, including the datasheet, design guidelines, and software drivers, is available on the FS23 device webpage.

#### Introduction

- This application note is meant to be used as a launching point for software engineers, as a complement, or as a substitute for NXP's software drivers.

- This document gives guidance on the implementation of SPI or I<sup>2</sup>C communication protocol between the MCU and the FS23.

- This document explains the initialization procedure of the FS23 device and provides an example of a start-up sequence.

### **General description**

- The FS23 SBC offers an expandable family of devices that is pin-to-pin and software-compatible. The devices

are scalable from the LDO version to the DC-DC version, as well as from QM to ASIL B. The FS23 SBC

includes CAN and LIN transceivers, along with several system and safety features for the latest generation of

automotive electronic control units (ECUs).

- The flexibility of the FS23 SBC makes it suitable for S32K processor-based applications, as well as multivendor processors.

- Several device versions are available, offering a choice of output voltage settings, operating frequency, powerup sequencing, and input/output configuration to address multiple applications.

#### **Reference documents**

- Reference documents and various materials are available on the <u>FS23 device webpage</u>. The webpage provides more detailed information about specific topics:

- <u>FS23 data sheet</u>: Information, such as features, functional description, parametric description, register mapping.

- FS23 Design Guidelines application note: Information such as application schematics, bill of materials, placement and layout guidelines, application validation data including ISO/non-ISO pulses, and Electromagnetic Compatibility (EMC).

- The low-level software driver components are provided as part of the basic enablement for the device, and do not incur an additional charge:

<u>FS23 AUTOSAR software drivers</u>: AUTOSAR and ISO 26262-compliant basic start-up drivers for low-level interfaces. Technical documentation is available as part of the software driver package, detailing supported features such as:

- SPI access register function and events handling (SBC\_FS23)

- CAN/LIN function (CANTRCV\_FS23 and LINTRCV\_FS23)

- Watchdog function (WDG\_FS23)

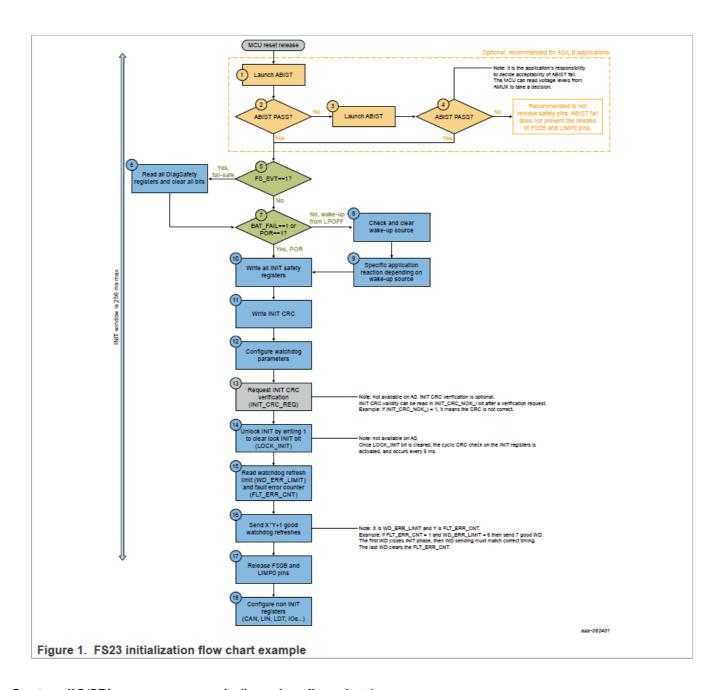

# FS23 initialization flow chart example

- Figure 1 gives an example of FS23 software initialization. After MCU reset is released (RSTB state is high), the MCU can start FS23 initialization. The initialization must be done within the dedicated 256 ms INIT window.

- Running the ABIST is optional, though it is recommended for ASIL B applications. ABIST can be run multiple

times in a row. In this example, the MCU checks the cause of the MCU reset (POR, LPOFF, fail-safe) and takes

action accordingly. Then the MCU writes INIT safety registers, ending with INIT cyclic redundancy check

(CRC).

- The next step is watchdog configuration, and unlocking the INIT CRC cyclic check, followed by watchdog refreshes to clear the fault error counter. The first watchdog refresh closes the INIT phase.

- Therefore, the subsequent watchdog refreshes must be sent according to watchdog timing configuration. Once the fault error counter is cleared, safety pins FS0B and LIMP0 can be released.

# Start-up I<sup>2</sup>C/SPI sequence example (based on flow chart)

Table 1. Start-up I<sup>2</sup>C/SPI sequence example

|     |                                              | Register                 | Read   | Write  | Comment                                                                                                                                              |

|-----|----------------------------------------------|--------------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Launch ABIST                                 | FS_ABIST (0x3D)          |        | 0x4000 | Optional: recommended for ASIL B applications. Full ABIST launch by writing LAUNCH_ABIST bit. Specific ABIST can be launched using appropriate bits. |

| 2   | Check ABIST                                  | FS_ABIST (0x3D)          | 0x07C0 |        | Optional: recommended for ASIL B applications. Check ABIST diagnostic bits.                                                                          |

| 3   | Launch ABIST                                 | FS_ABIST (0x3D)          |        | 0x4000 | Optional: recommended for ASIL B applications. Full ABIST launch by writing LAUNCH_ABIST bit. Specific ABIST can be launched using appropriate bits. |

| 4   | Check ABIST                                  | FS_ABIST (0x3D)          | 0x07C0 |        | Optional: recommended for ASIL B applications. Check ABIST diagnostic bits.                                                                          |

| 5   | MCU reset from FS?                           | M_WU1_FLG (0x17)         | 0x0200 |        | Check FS_EVT bit: 0x0200 if wake-up from fail-safe.                                                                                                  |

|     | Read diagnostic                              | FS_SAFETY_OUTPUTS (0x3F) | 0x3804 |        | Default value: RSTB released, FS0B asserted, LIMP0 released                                                                                          |

| 6   | registers and clear                          | FS_SAFETY_FLG (0x40)     | 0x0002 |        | Default value: FCCU1 sensed high                                                                                                                     |

|     | all bits                                     | M_REG_FLG (0x0A)         | 0x0000 |        | Default value                                                                                                                                        |

| 7   | MCU reset from POR/LPOFF?                    | M_SYS_CONFIG (0x05)      | 0x5000 |        | Check BAT_FAIL and POR bits: 0x5000 if wake-up from POR                                                                                              |

| 8   | Check WU source                              | M_WU1_FLG (0x17)         | 0x0000 |        | Check wake-up sources if wake-up from LPOFF: 0x0000 if wake-up from                                                                                  |

|     | Check Wo Source                              | M_IOWU_FLG (0x15)        | 0x0000 |        | POR                                                                                                                                                  |

|     |                                              | FS_I_OVUV_CFG1 (0x32)    |        | 0x1F98 | Default value                                                                                                                                        |

|     |                                              | FS_I_OVUV_CFG2 (0x33)    |        | 0x0C18 | Default value                                                                                                                                        |

| 10  | INIT                                         | FS_I_FCCU_CFG (0x34)     |        | 0x103F | Default value                                                                                                                                        |

|     |                                              | FS_I_FSSM_CFG (0x36)     |        | 0x0AF1 | Default value, FLT_ERR_CNT = 1 and FLT_ERR_LIMIT = 6                                                                                                 |

|     |                                              | FS_I_WD_CFG (0x37)       |        | 0x7080 | Default value                                                                                                                                        |

| 11  | Send INIT CRC                                | FS_CRC (0x41)            |        | 0x06B4 | INIT CRC to be computed to match INIT registers content                                                                                              |

| 12  | Configure Watchdog                           | FS_WDW_CFG (0x38)        |        | 0x01AB | Default value                                                                                                                                        |

| 13  | Request INIT<br>CRC verification             | FS_CRC (0x41)            |        | 0x46B4 | Optional: INIT CRC to be computed to match INIT registers content                                                                                    |

| 14  | Unlock INIT CRC cyclic check                 | M_SYS_CONFIG (0x05)      |        | 0x0400 | Clearing LOCK_INIT bit unlocks INIT CRC cyclic check                                                                                                 |

| 15  | Read watchdog                                | FS_I_WD_CFG (0x37)       | 0x7080 |        | Default value, with watchdog error limit = 6                                                                                                         |

| 15  | current counter value                        | FS_I_FSSM_CFG (0x36)     | 0x0AF1 |        | Default value, with fault error counter = 1                                                                                                          |

|     |                                              | FS_WD_TOKEN (0x39)       | 0x5AB2 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0x5AB2 | Watchdog answer is 0x5A2B (default value)                                                                                                            |

|     |                                              | FS_WD_TOKEN (0x39)       | 0xD564 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0xD564 | Watchdog answer is 0xD564                                                                                                                            |

|     |                                              | FS_WD_TOKEN (0x39)       | 0x5AB2 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0x5AB2 | Watchdog answer is 0x5A2B                                                                                                                            |

| 16  | Send 7x good WD refresh                      | FS_WD_TOKEN (0x39)       | 0xD564 |        | Read watchdog token                                                                                                                                  |

| 16  | (if WD_ERR_LIMIT = 6<br>and FLT_ERR_CNT = 1) | FS_WD_ANSWER (0x3A)      |        | 0xD564 | Watchdog answer is 0xD564                                                                                                                            |

|     |                                              | FS_WD_TOKEN (0x39)       | 0x5AB2 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0x5AB2 | Watchdog answer is 0x5A2B                                                                                                                            |

|     |                                              | FS_WD_TOKEN (0x39)       | 0xD564 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0xD564 | Watchdog answer is 0xD564                                                                                                                            |

|     |                                              | FS_WD_TOKEN (0x39)       | 0x5AB2 |        | Read watchdog token                                                                                                                                  |

|     |                                              | FS_WD_ANSWER (0x3A)      |        | 0x5AB2 | Watchdog answer is 0x5A2B                                                                                                                            |

| 4-7 | Delegas FOOD                                 | FS_WD_TOKEN (0x39)       | 0xD564 |        | Read watchdog token                                                                                                                                  |

| 17  | Release FS0B                                 | FS_FS0B_LIMP0_REL        |        | 0x7B2A | Compute FS0B and LIMP0 release register value                                                                                                        |

| 4.5 | Configure CAN,                               | M_CAN (0x2A)             |        | 0x02A0 | CAN in Normal operation mode                                                                                                                         |

| 18  | LIN, LDT, I/Os                               | M_LIN (0x2B)             |        | 0x4400 | LIN in Normal operation mode                                                                                                                         |

|     |                                              |                          | 1      |        |                                                                                                                                                      |

# I<sup>2</sup>C/SPI register mapping of main logic

# Table 2. Main register mapping

Refer to Table 70 from the **FS23 data sheet**.

|           |   | Addre     | ess       |           |           |           |           |           |         |                      |            |

|-----------|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---------|----------------------|------------|

| Register  | # | Adr_<br>6 | Adr_<br>5 | Adr_<br>4 | Adr_<br>3 | Adr_<br>2 | Adr_<br>1 | Adr_<br>0 | R/W SPI | R/W I <sup>2</sup> C | Read/Write |

| M_DEV_CFG | 0 | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0/1     | 1/0                  | Read only  |

| M_DEV_PROG_ID      | 1      | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0/1 | 1/0 | Read only  |

|--------------------|--------|---|---|---|---|---|---|---|-----|-----|------------|

| M_GEN_FLAG         | 2      | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0/1 | 1/0 | Read only  |

| M_STATUS           | 3      | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0/1 | 1/0 | Read only  |

| Reserved           | 4      | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0/1 | 1/0 | Reserved   |

| M_SYS_CFG          | 5      | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_SYS1_CFG         | 6      | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_REG_CTRL         | 7      | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| Reserved           | 8      | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0/1 | 1/0 | Reserved   |

| Reserved           | 9      | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0/1 | 1/0 | Reserved   |

| M_REG_FLG          | 1<br>0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_REG_MSK          | 1      | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_REG1_FLG         | 1 2    | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_REG1_MSK         | 1<br>3 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_IO_CTRL          | 1 4    | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0/1 | 1/0 | Write      |

| M_IO_TIMER_FLG     | 1<br>5 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_IO_TIMER_MS<br>K | 1<br>6 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_VSUP_COM_F<br>LG | 1<br>7 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_VSUP_COM_M<br>SK | 1<br>8 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_IOWU_CFG         | 1<br>9 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_IOWU_EN          | 2      | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_IOWU_FLG         | 2      | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_WU1_EN           | 2      | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_WU1_FLG          | 2      | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_TIMER1_CFG       | 2<br>4 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_TIMER2_CFG         | 2<br>5 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0/1 | 1/0 | Read/Write |

|----------------------|--------|---|---|---|---|---|---|---|-----|-----|------------|

| M_TIMER3_CFG         | 2      | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_PWM1_CFG           | 2<br>7 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_PWM2_CFG           | 2      | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_PWM3_CFG           | 2<br>9 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_TIMER_PWM_<br>CTRL | 3<br>0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_CS_CFG             | 3      | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_CS_FLG_MSK         | 3<br>2 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_HSx_SRC_CFG        | 3      | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_HSx_CTRL           | 3<br>4 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_HSx_FLG            | 3<br>5 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_HSx_MSK            | 3<br>6 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_AMUX_CTRL          | 3<br>7 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_LDT_CFG1           | 3<br>8 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_LDT_CFG2           | 3<br>9 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_LDT_CFG3           | 4<br>0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_LDT_CTRL           | 4      | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_CAN                | 4<br>2 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0/1 | 1/0 | Read/Write |

| M_LIN                | 4 3    | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0/1 | 1/0 | Read/Write |

| M_CAN_LIN_MSK        | 4      | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0/1 | 1/0 | Read/Write |

| M_MEMORY0            | 4<br>5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0/1 | 1/0 | Read/Write |

| M_MEMORY1 | 6 0 | ) 1 | 0 1 | 1 | 1 | 0 | 0/1 | 1/0 | Read/Write |

|-----------|-----|-----|-----|---|---|---|-----|-----|------------|

|-----------|-----|-----|-----|---|---|---|-----|-----|------------|

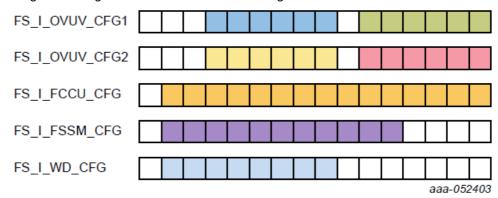

# Register mapping of fail-safe logic

**Table 3.** Safety-related register mapping Refer to Table 71 from the **FS23 data sheet**.

|                       |        | Addre     | ess       |           |           |           |           |           |         |                      |                                     |

|-----------------------|--------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---------|----------------------|-------------------------------------|

| Register              | #      | Adr<br>_6 | Adr<br>_5 | Adr_<br>4 | Adr<br>_3 | Adr_<br>2 | Adr_<br>1 | Adr_<br>0 | R/W SPI | R/W I <sup>2</sup> C | Read/Write                          |

| FS_I_OVUV_CFG1        | 5      | 0         | 1         | 1         | 0         | 0         | 1         | 0         | 0/1     | 1/0                  | Write during IN IT, then read only  |

| FS_I_OVUV_CFG2        | 5<br>1 | 0         | 1         | 1         | 0         | 0         | 1         | 1         | 0/1     | 1/0                  | Write during IN IT, then read o nly |

| FS_I_FCCU_CFG         | 5<br>2 | 0         | 1         | 1         | 0         | 1         | 0         | 0         | 0/1     | 1/0                  | Write during IN IT, then read only  |

| Reserved              | 5<br>3 | 0         | 1         | 1         | 0         | 1         | 0         | 1         | 0/1     | 1/0                  | Reserved                            |

| FS_I_FSSM_CFG         | 5<br>4 | 0         | 1         | 1         | 0         | 1         | 1         | 0         | 0/1     | 1/0                  | Write during IN IT, thenr ead only  |

| FS_I_WD_CFG           | 5<br>5 | 0         | 1         | 1         | 0         | 1         | 1         | 1         | 0/1     | 1/0                  | Write during IN IT, then read only  |

| FS_WDW_CFG            | 5<br>6 | 0         | 1         | 1         | 1         | 0         | 0         | 0         | 0/1     | 1/0                  | Read/Write                          |

| FS_WD_TOKEN           | 5<br>7 | 0         | 1         | 1         | 1         | 0         | 0         | 1         | 0/1     | 1/0                  | Read only                           |

| FS_WD_ANSWER          | 5<br>8 | 0         | 1         | 1         | 1         | 0         | 1         | 0         | 0/1     | 1/0                  | Write only                          |

| FS_LIMP12_CFG         | 5<br>9 | 0         | 1         | 1         | 1         | 0         | 1         | 1         | 0/1     | 1/0                  | Read/Write                          |

| FS_FS0B_LIMP0_<br>REL | 6<br>0 | 0         | 1         | 1         | 1         | 1         | 0         | 0         | 0/1     | 1/0                  | Read/Write                          |

| FS_ABIST              | 6<br>1 | 0         | 1         | 1         | 1         | 1         | 0         | 1         | 0/1     | 1/0                  | Read/Write                          |

| Reserved              | 6<br>2 | 0         | 1         | 1         | 1         | 1         | 1         | 0         | 0/1     | 1/0                  | Reserved                            |

| FS_SAFETY_OUT<br>PUTS | 6<br>3 | 0         | 1         | 1         | 1         | 1         | 1         | 1         | 0/1     | 1/0                  | Read/Write                          |

| FS_SAFETY_FLG         | 6<br>4 | 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0/1     | 1/0                  | Read/Write                          |

| FS_CRC                | 6<br>5 | 1         | 0         | 0         | 0         | 0         | 0         | 1         | 0/1     | 1/0                  | Read/Write                          |

# Readable registers

| L<br>o<br>g<br>ic | Regi<br>ster<br>name      | Bit<br>15             | Bit<br>14        | Bit<br>13            | Bit<br>12                                        | Bit 1<br>1<br>B<br>it 10                 | B<br>it<br>9                    | Bit<br>8                           | Bit<br>7          | Bit<br>6         | Bit<br>5                | Bit<br>4        | Bit<br>3             | Bit<br>2              | Bit<br>1         | Bit<br>0             |

|-------------------|---------------------------|-----------------------|------------------|----------------------|--------------------------------------------------|------------------------------------------|---------------------------------|------------------------------------|-------------------|------------------|-------------------------|-----------------|----------------------|-----------------------|------------------|----------------------|

|                   | M_D<br>EV_C<br>FG         | 0                     | 0                | CAN<br>_EN           | LIN_<br>EN                                       | LDTI<br>M_E<br>N<br>H<br>SD1<br>3_E<br>N | H<br>S<br>D<br>2<br>4<br>E<br>N | V2_<br>EN                          | V1_<br>PNP<br>_EN | ABI<br>ST_<br>EN | FCC<br>U_E<br>N         | FS0<br>B_E<br>N | LIM<br>PO_<br>EN     | V0M<br>ON_<br>EN      | 0                | 0                    |

|                   | M_D<br>EV_P<br>ROG<br>_ID | FULL                  | _LAYE            | R_REV                | ,                                                | META<br>L_LA\<br>ER_R<br>EV              | <b>′</b>                        |                                    |                   | PROC             | G_IDH                   |                 | PROC                 | G_IDL                 |                  |                      |

|                   | M_G<br>EN_F<br>LAG        | 0                     | 0                | 0                    | 0                                                | 0                                        | 0                               | 0                                  | HSx<br>G          | SAF<br>ETY<br>G  | PHY<br>G                | WU<br>G         | IOTI<br>MG           | CO<br>MG              | VSU<br>PG        | VxG                  |

|                   | M_ST<br>ATUS              | V1T<br>WA<br>RN_<br>S | LPO<br>N_S       | NO<br>RM<br>AL_<br>S | INIT<br>_S                                       | 0<br>WK2<br>_S                           | W<br>K<br>1                     | HVI<br>O2_<br>S                    | HVI<br>O1_<br>S   | LVI5<br>_S       | LVI<br>O4_<br>S         | LVI<br>O3_<br>S | V1_<br>MO<br>DE      | V1_<br>S              | V2_<br>S         | V3_<br>S             |

|                   | M_S<br>YS_C<br>FG         | 0                     | BAT<br>_FAI<br>L | 0                    | PO<br>R                                          | 0<br>L<br>OCK<br>_INI<br>T               | 0                               | 0                                  | 0                 | 0                | INT<br>_TO<br>_W<br>UEN | 0               | INT<br>B_D<br>UR     | 0                     | MO<br>D_C<br>ONF | MO<br>D_E<br>N       |

|                   | M_S<br>YS1_<br>CFG        | 0                     | 0                | 0                    | VBO<br>S2<br>V1_<br>SW<br>_AL<br>WA<br>YS_<br>EN | O LO AD_ OTP _BY P                       | S<br>L<br>O<br>T<br>B<br>Y<br>P | TSL<br>OT_<br>DO<br>WN<br>_CF<br>G | 0                 | 0                | 0                       | 0               | DB<br>G_<br>MO<br>DE | 0                     | 0                | OTP<br>_M<br>OD<br>E |

|                   | M_R<br>EG_<br>CTRL        | 0                     | 0                | 0                    | BUC<br>K_S<br>RHS<br>OFF                         | BUC<br>N                                 | L_SF                            | RHSO                               | 0                 | 0                | V2O<br>N_L<br>PO<br>N   | 0               | 0                    | V3O<br>N_L<br>PO<br>N | 0                | 0                    |

| M_R<br>EG_F<br>LG           | VOU<br>V_I | V0O<br>V_I | V1T<br>WA<br>RN_<br>I | V1T<br>SD_<br>I             | V2T<br>SD_<br>I<br>V3T<br>SD_<br>I | V<br>2<br>0<br>L<br>_I     | V1U<br>V_I        | V2U<br>V_I        | V3U<br>V_I        | V10<br>V_I        | V2O<br>V_I      | V3O<br>V_I        | V10<br>C_I        | V2O<br>C_I       | V3          |

|-----------------------------|------------|------------|-----------------------|-----------------------------|------------------------------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-----------------|-------------------|-------------------|------------------|-------------|

| M_R<br>EG_<br>MSK           | VOU<br>V_M | V0O<br>V_M | V1T<br>WA<br>RN_<br>M | V1T<br>SD_<br>M             | V2T<br>SD_<br>M<br>V3T<br>SD_<br>M | V<br>2<br>O<br>L<br>-<br>M | V1U<br>V_M        | V2U<br>V_M        | V3U<br>V_M        | V1O<br>V_M        | V2O<br>V_M      | V3O<br>V_M        | V1O<br>C_M        | V2O<br>C_M       | V3<br>C_    |

| M_R<br>EG1_<br>FLG          | 0          | 0          | 0                     | 0                           | 0                                  | 0                          | 0                 | 0                 | 0                 | 0                 | 0               | 0                 | 0                 | 0                | V<br>O<br>S |

| M_R<br>EG1_<br>MSK          | 0          | 0          | 0                     | 0                           | 0                                  | 0                          | 0                 | 0                 | 0                 | 0                 | 0               | 0                 | 0                 | 0                | V<br>O<br>S |

| M_IO<br>_TIM<br>ER_F<br>LG  | 0          | 0          | 0                     | 0                           | 0                                  | 0                          | LDT<br>_I         | LVI5<br>_I        | LVI<br>O4_<br>I   | LVI<br>O3_<br>I   | HVI<br>O2_<br>I | HVI<br>O1_<br>I   | 0                 | WK<br>2_I        | W<br>1_     |

| M_IO<br>_ TIM<br>ER_<br>MSK | 0          | 0          | 0                     | 0                           | 0                                  | 0                          | LDT<br>_M         | LVI5<br>_M        | LVI<br>O4_<br>M   | LVI<br>O3_<br>M   | HVI<br>O2_<br>M | HVI<br>O1_<br>M   | 0                 | WK<br>2_M        | W<br>1_     |

| M_V<br>SUP_<br>COM<br>_FLG  | 0          | 0          | 0                     | VBO<br>S2<br>V1S<br>W_<br>S | VBO<br>S_U<br>V                    | 12<br>C<br>C<br>R<br>C _   | I2C_<br>RE<br>Q_I | SPI<br>_CR<br>C_I | SPI<br>_CL<br>K_I | SPI<br>_RE<br>Q_I | 0               | VSH<br>S_O<br>V_I | VSH<br>S_U<br>V_I | VSU<br>POV<br>_I | V:<br>Pi    |

|              | M_V<br>SUP_<br>COM<br>_MS<br>K | 0                      | 0                       | 0                       | 0   | 0                                                              | 12<br>C<br>C<br>R<br>C          | I2C_<br>RE<br>Q_<br>M       | SPI<br>_CR<br>C_M      | SPI<br>_CL<br>K_M      | SPI<br>_RE<br>Q_<br>M       | 0                            | VSH<br>S_O<br>V_M     | VSH<br>S_U<br>V_M     | VSU<br>POV<br>_M | VSU<br>PUV<br>_M |

|--------------|--------------------------------|------------------------|-------------------------|-------------------------|-----|----------------------------------------------------------------|---------------------------------|-----------------------------|------------------------|------------------------|-----------------------------|------------------------------|-----------------------|-----------------------|------------------|------------------|

|              | M_IO<br>WU_<br>CFG             | LVI5<br>_W<br>UCF<br>G | LVI<br>O4_<br>WU<br>CFG | LVI<br>O3_<br>WU<br>CFG | 0   | HVI<br>O2_<br>DGL<br>T H<br>VIO<br>1_D<br>GLT                  | W<br>K<br>2<br>D<br>G<br>L<br>T | WK<br>1_D<br>GLT            | HVIO<br>CFG            | 2_WU                   | HVIO<br>CFG                 | 1_WU                         | WK2_<br>FG            | _WUC                  | WK1_<br>FG       | _WUC             |

|              | M_IO<br>WU_<br>EN              | 0                      | 0                       | LVI5_<br>N              | WUE | LVIO4<br>LV<br>N                                               |                                 | JEN<br>WUE                  | HVIO<br>EN             | 2_WU                   | HVIO<br>EN                  | 1_WU                         | WK2_<br>N             | _WUE                  | WK1_<br>N        | _WUE             |

|              | M_IO<br>WU_<br>FLG             | LVI5<br>_W<br>U_I      | LVI<br>O4_<br>WU<br>_I  | LVI<br>O3_<br>WU<br>_I  | 0   | HVI<br>O2_<br>HVI<br>O1_<br>CYS<br>_RD<br>Y<br>C<br>YS_<br>RDY | H VI O 2 C Y C S                | HVI<br>O1_<br>CYC<br>_S     | HVI<br>O2_<br>WU<br>_I | HVI<br>O1_<br>WU<br>_I | WK<br>2_<br>CYS<br>_RD<br>Y | WK<br>1_<br>CYS<br>_RD<br>Y  | WK<br>2_C<br>YC_<br>S | WK<br>1_C<br>YC_<br>S | WK<br>2_W<br>U_I | WK<br>1_W<br>U_I |

| M<br>ai<br>n | M_W<br>U1_E<br>N               | 0                      | 0                       | 0                       | 0   | 0                                                              | 0                               | 0                           | 0                      | 0                      | LDT_'                       | WUE                          | LIN_V                 | VUEN                  | CAN_<br>N        | WUE              |

|              | M_W<br>U1_F<br>LG              | 0                      | 0                       | 0                       | 0   | 0                                                              | F<br>S<br>-<br>E<br>V<br>T      | EXT<br>_R<br>STB<br>_W<br>U | WD<br>_OF<br>L_W<br>U  | V1_<br>UVL<br>P_<br>WU | INT<br>_TO<br>_W<br>U       | GO2<br>NO<br>RM<br>AL_<br>WU | 0                     | LDT<br>_W<br>U_I      | LIN_<br>WU<br>_I | CAN<br>_W<br>U_I |

| M_TI<br>MER<br>1_CF<br>G          | 0 | 0 | 0 | 0                | 0              | 0               | TIME<br>LY             | R1_D                   | TIME                   | R1_ON                  | I               |                        | TIME                   | R1_PE                  | R                      |

|-----------------------------------|---|---|---|------------------|----------------|-----------------|------------------------|------------------------|------------------------|------------------------|-----------------|------------------------|------------------------|------------------------|------------------------|

| M_TI<br>MER<br>2_CF<br>G          | 0 | 0 | 0 | 0                | 0              | 0               | TIME<br>LY             | R2_D                   | TIME                   | R2_ON                  | I               |                        | TIME                   | R2_PE                  | R                      |

| M_TI<br>MER<br>3_CF<br>G          | 0 | 0 | 0 | 0                | 0              | 0               | TIME<br>LY             | R3_D                   | TIME                   | R3_ON                  | I               |                        | TIME                   | R3_PE                  | R                      |

| M_P<br>WM1<br>_CFG                | 0 | 0 | 0 | PW<br>M1_<br>DLY | PW<br>M1_<br>F | PW              | /M1_D                  | С                      |                        |                        |                 |                        | -                      |                        |                        |

| M_P<br>WM2<br>_CFG                | 0 | 0 | 0 | PW<br>M2_<br>DLY | PW<br>M2_<br>F | PW              | /M2_D                  | С                      |                        |                        |                 |                        |                        |                        |                        |

| M_P<br>WM3<br>_CFG                | 0 | 0 | 0 | PW<br>M3_<br>DLY | PW<br>M3_<br>F | PW              | /M3_D                  | С                      |                        |                        |                 |                        |                        |                        |                        |

| M_TI<br>MER<br>_ PW<br>M_C<br>TRL | 0 | 0 | 0 | 0                | 0              | 0               | 0                      | 0                      | TIM<br>1_E<br>N        | TIM<br>2_E<br>N        | TIM<br>3_E<br>N | 0                      | PW<br>M1_<br>EN        | PW<br>M2_<br>EN        | PW<br>M3_<br>EN        |

| M_C<br>S_CF<br>G                  | 0 | 0 | 0 | 0                | 0              | HS FLT WU FORCE | 0                      | HVIO<br>_SEL           |                        | HVIO<br>_SEL           | 1_HS            | WK2_<br>SEL            | HS_                    | WK1_<br>SEL            | HS_                    |

| M_C<br>S_FL<br>G_M<br>SK          | 0 | 0 | 0 | 0                | 0              | 0               | HVI<br>O2_<br>OL_<br>M | HVI<br>O1_<br>OL_<br>M | WA<br>KE2<br>_OL<br>_M | WA<br>KE1<br>_OL<br>_M | 0               | HVI<br>O2_<br>OL_<br>I | HVI<br>O1_<br>OL_<br>I | WA<br>KE2<br>_OL<br>_I | WA<br>KE1<br>_OL<br>_I |

| M_H<br>Sx_S<br>RC_<br>CFG | HS4_ | SRC_S                           | SEL                           |                               | HS3_<br>RC_S<br>EL |                       |                  |                        | HS2_<br>SEL | SRC_             |                  | HS1_ | SRC_S            | SEL              |                        |

|---------------------------|------|---------------------------------|-------------------------------|-------------------------------|--------------------|-----------------------|------------------|------------------------|-------------|------------------|------------------|------|------------------|------------------|------------------------|

| M_H<br>Sx_C<br>TRL        | 0    | HS_<br>VSH<br>SUV<br>OV_<br>REC | HS_<br>VSH<br>SUV<br>_DI<br>S | HS_<br>VSH<br>SOV<br>_DI<br>S | 0                  | 0                     | 0                | 0                      | HS4<br>_EN  | 0                | HS3<br>_EN       | 0    | HS2<br>_EN       | 0                | HS1<br>_EN             |

| M_H<br>Sx_F<br>LG         | 0    | 0                               | 0                             | HS4<br>_OL<br>_I              | HS4<br>_OC<br>_I   | H<br>S<br>3<br>O<br>L | HS3<br>_OC<br>_I | HS3<br>4_T<br>SD_<br>I | 0           | HS2<br>_OL<br>_I | HS2<br>_OC<br>_I | 0    | HS1<br>_OL<br>_I | HS1<br>_OC<br>_I | HS1<br>2_T<br>SD_<br>I |

| L D | Regi<br>ster<br>nam<br>e | Bit<br>15 | Bit<br>14   | Bit<br>13 | Bit<br>12        | Bit<br>11            | Bit<br>10 | Bit<br>9         | Bit<br>8             | Bit<br>7                   | Bit<br>6 | Bit<br>5             | Bit<br>4             | Bit<br>3        | Bit<br>2             | Bit<br>1             | Bit<br>0                   |

|-----|--------------------------|-----------|-------------|-----------|------------------|----------------------|-----------|------------------|----------------------|----------------------------|----------|----------------------|----------------------|-----------------|----------------------|----------------------|----------------------------|

|     | M_H<br>Sx_<br>MSK        | 0         | 0           | 0         | HS4<br>_OL<br>_M | HS4<br>_O<br>C_<br>M | 0         | HS3<br>_OL<br>_M | HS<br>3_O<br>C_<br>M | HS<br>34_<br>TS<br>D_<br>M | 0        | HS<br>2_O<br>L_<br>M | HS<br>2_O<br>C_<br>M | 0               | HS<br>1_O<br>L_<br>M | HS<br>1_O<br>C_<br>M | HS<br>12_<br>TS<br>D_<br>M |

| -   | M_A<br>MUX<br>_CT<br>RL  | 0         | 0           | 0         | 0                | 0                    | 0         | AM<br>UX_<br>EN  | AM<br>UX<br>_DI<br>V | 0                          | 0        | 0                    | AMU                  | X               |                      |                      | ı                          |

| -   | M_L<br>DT_<br>CFG<br>1   | LDT_      | Γ_AFTER_RUN |           |                  |                      |           |                  |                      |                            |          |                      |                      |                 |                      |                      |                            |

| •   | M_L<br>DT_<br>CFG<br>2   | LDT_      | _WUP_       | <u>L</u>  |                  |                      |           |                  |                      |                            |          |                      |                      |                 |                      |                      |                            |

|     | M_L<br>DT_<br>CFG<br>3   | 0         | 0           | 0         | 0                | 0                    | 0         | 0                | 0                    | LDT_                       | _WUP_    | _H                   |                      |                 |                      |                      |                            |

|     | M_L<br>DT_<br>CTR<br>L   | 0         | 0           | 0         | 0                | 0                    | 0         | 0                | 0                    | LDT<br>2LP                 | LDT_     | FNCT                 |                      | LDT<br>_SE<br>L | LDT<br>_M<br>OD<br>E | LDT<br>_E<br>N       | LDT<br>_R<br>UN            |

| M_C<br>AN                      | 0                           | 0                           | 0                           | 0                                                | 0                                                    | 0                                                     | CAN_<br>DE                                       | _MO                                                      | CA N_ AC TIV E_ MO DE _S                                  | 0                      | CA<br>N_F<br>S_<br>DIS                                   | 0                                                    | 0                                                         | 0                                                        | CA<br>N_<br>TX<br>D_T<br>O_I                         | CA<br>N_T<br>SD<br>_I                                     |

|--------------------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| M_LI<br>N                      | 0                           | LIN_I<br>E                  | MOD                         | LIN_S<br>E                                       | SLOP                                                 | LIN<br>_FS<br>_DI<br>S                                | LIN<br>_ V<br>SH<br>SU<br>V_D<br>IS              | LIN<br>_S<br>C                                           | LIN<br>_TX<br>D_T<br>O                                    | 0                      | 0                                                        | 0                                                    | 0                                                         | LIN<br>_S<br>C_I                                         | LIN<br>_TX<br>D_T<br>O_I                             | LIN<br>_TS<br>D_I                                         |

| M_C<br>AN_<br>LIN_<br>MSK      | 0                           | 0                           | LIN_                        | FSM_S                                            | STATE_                                               | _S                                                    |                                                  | LIN<br>_S<br>C_<br>M                                     | LIN<br>_TX<br>D_<br>TO<br>_M                              | LIN<br>_TS<br>D_<br>M  | 0                                                        | CAN_<br>TE_S                                         | _FSM_                                                     | _STA                                                     | CA<br>N_T<br>XD<br>_T<br>O_<br>M                     | CA<br>N_T<br>SD<br>_M                                     |

| M_M<br>EMO<br>RY0              | ME<br>MO<br>RY<br>0[1<br>5] | ME<br>MO<br>RY<br>0[1<br>4] | ME<br>MO<br>RY<br>0[1<br>3] | ME<br>MO<br>RY0<br>[12]                          | ME<br>MO<br>RY0<br>[11]                              | ME<br>MO<br>RY0<br>[10]                               | ME<br>MO<br>RY0<br>[9]                           | ME<br>MO<br>RY<br>0[8]                                   | ME<br>MO<br>RY<br>0[7]                                    | ME<br>MO<br>RY<br>0[6] | ME<br>MO<br>RY<br>0[5]                                   | ME<br>MO<br>RY<br>0[4]                               | ME<br>MO<br>RY<br>0[3]                                    | ME<br>MO<br>RY<br>0[2]                                   | ME<br>MO<br>RY<br>0[1]                               | ME<br>MO<br>RY<br>0[0]                                    |

| M_M<br>EMO<br>RY1              | ME<br>MO<br>RY<br>1[1<br>5] | ME<br>MO<br>RY<br>1[1<br>4] | ME<br>MO<br>RY<br>1[1<br>3] | ME<br>MO<br>RY1<br>[12]                          | ME<br>MO<br>RY1<br>[11]                              | ME<br>MO<br>RY1<br>[10]                               | ME<br>MO<br>RY1<br>[9]                           | ME<br>MO<br>RY<br>1[8]                                   | ME<br>MO<br>RY<br>1[7]                                    | ME<br>MO<br>RY<br>1[6] | ME<br>MO<br>RY<br>1[5]                                   | ME<br>MO<br>RY<br>1[4]                               | ME<br>MO<br>RY<br>1[3]                                    | ME<br>MO<br>RY<br>1[2]                                   | ME<br>MO<br>RY<br>1[1]                               | ME<br>MO<br>RY<br>1[0]                                    |

| FS_I<br>_OV<br>UV_<br>CFG<br>1 | 0                           | 0                           | 0                           | V1<br>MO<br>N_<br>OV<br>_RS<br>TB_<br>IMP<br>ACT | V1<br>MO<br>N_<br>OV<br>_F<br>S0B<br>_I<br>MP<br>ACT | V1<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>ACT | V1<br>MO<br>N_<br>UV_<br>RS<br>TB_<br>IMP<br>ACT | V1<br>MO<br>N_<br>UV<br>_F<br>S0B<br>_I<br>MP<br>AC<br>T | V1<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | 0                      | V2<br>MO<br>N_<br>OV<br>_R<br>ST<br>B_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>OV<br>_F<br>S0B<br>_IM<br>PA<br>CT | V2<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>UV<br>_R<br>ST<br>B_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>UV<br>_F<br>S0B<br>_IM<br>PA<br>CT | V2<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T |

| FS_I<br>_OV<br>UV_<br>CFG<br>2 | 0   | 0                                      | 0                                   | V3<br>MO<br>N_<br>OV<br>_RS<br>TB_<br>IMP<br>ACT | V3<br>MO<br>N_<br>OV<br>_F<br>S0B<br>_IM<br>PA<br>CT | V3<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>ACT | V3<br>MO<br>N_<br>UV_<br>RS<br>TB_<br>IMP<br>ACT | V3<br>MO<br>N_<br>UV<br>_F<br>S0B<br>_I<br>MP<br>AC<br>T | V3<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | 0                                               | V0<br>MO<br>N_<br>OV<br>_R<br>ST<br>B_I<br>MP<br>AC<br>T | V0<br>MO<br>N_<br>OV<br>_F<br>S0B<br>_IM<br>PA<br>CT | V0<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | V0<br>MO<br>N_<br>UV<br>_R<br>ST<br>B_I<br>MP<br>AC<br>T | V0<br>MO<br>N_<br>UV<br>_F<br>S0B<br>_IM<br>PA<br>CT | V0<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T |  |  |

|--------------------------------|-----|----------------------------------------|-------------------------------------|--------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|--|--|

| FS_I<br>_FC<br>CU_<br>CFG      | 0   | FCCI                                   | J_CF0                               | à                                                |                                                      | FCCI<br>SSIG                                          | _                                                | FC<br>CU<br>12_<br>FLT<br>_P<br>OL                       | FC<br>CU<br>2_<br>FLT<br>_P<br>OL                         | FC<br>CU<br>1_<br>FLT<br>_P<br>OL               | FC<br>CU<br>2_<br>RS<br>TB_<br>IMP<br>AC<br>T            | FC<br>CU<br>2_F<br>S0<br>B_I<br>MP<br>AC<br>T        | FC<br>CU<br>2_<br>LIM<br>P0_<br>IMP<br>AC<br>T            | FC<br>CU<br>1_<br>RS<br>TB_<br>IMP<br>AC<br>T            | FC<br>CU<br>1_F<br>S0<br>B_I<br>MP<br>AC<br>T        | FC<br>CU<br>1_<br>LIM<br>P0_<br>IMP<br>AC<br>T            |  |  |

| FS_I<br>_FS<br>SM_<br>CFG      | 0   | EX<br>T_<br>RS<br>TB_<br>DIS           | RS<br>TB8<br>S_<br>DIS              | RS<br>TB_<br>DU<br>R                             | LIM<br>P0_<br>SC_<br>RS<br>TB_<br>IMP<br>ACT         | EXT<br>RS<br>TB_<br>FS0<br>B_I<br>MP<br>ACT           | FS0<br>B_S<br>C_<br>RS<br>TB_<br>IMP<br>ACT      | FLT_<br>_LIM                                             |                                                           | FLT<br>_MI<br>D_<br>RS<br>TB_<br>IMP<br>AC<br>T | FLT<br>_MI<br>D_F<br>S0<br>B_I<br>MP<br>AC<br>T          | FLT<br>_MI<br>D_<br>LIM<br>PO_<br>IMP<br>AC<br>T     | FLT_                                                      | ERR_(                                                    | CNT                                                  |                                                           |  |  |

| FS_I<br>_WD<br>_CF<br>G        | 0   | WD<br>_R<br>ST<br>B_I<br>MP<br>AC<br>T | WD<br>_FS<br>0 B<br>_IM<br>PA<br>CT | WD<br>_LI<br>MP<br>0_ I<br>MP<br>ACT             | WD<br>_DI<br>S_<br>LP<br>ON                          | WD_I                                                  | RFR_                                             | WD_<br>_LIM                                              |                                                           | WD_                                             | RFR_(                                                    | CNT                                                  | WD_                                                       | ERR_0                                                    | CNT                                                  |                                                           |  |  |

| FS_<br>WD<br>W_C<br>FG         | 0   | 0                                      | 0                                   | 0                                                | WD<br>W_<br>RE<br>C_E<br>N                           | WD<br>W_<br>EN                                        | 0                                                | WDV                                                      | V_PER                                                     | lIOD                                            |                                                          | 0                                                    | WDW_RECOVERY                                              |                                                          |                                                      |                                                           |  |  |

| FS_<br>WD_<br>TOK<br>EN        | WD_ | TOKEI                                  | N                                   |                                                  | ı                                                    | ı                                                     | ı                                                | ı                                                        |                                                           |                                                 |                                                          | ı                                                    | ı                                                         |                                                          |                                                      |                                                           |  |  |

F a il - s a

| f<br>e | FS_<br>LIM<br>P12_<br>CFG             | 0                                | 0                               | 0                               | 0                                  | 0                                  | 0                                                  | 0                                                 | LIMP<br>C_CF                             |                                          | LIMP<br>G                                | 2_CF                | 0                           | 0                            | LIMP<br>G                   | 1_CF                        | 0                           |

|--------|---------------------------------------|----------------------------------|---------------------------------|---------------------------------|------------------------------------|------------------------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|---------------------|-----------------------------|------------------------------|-----------------------------|-----------------------------|-----------------------------|

|        | FS_<br>FS0<br>B_L<br>IMP<br>0_R<br>EL | 0                                | 0                               | 0                               | 0                                  | 0                                  | 0                                                  | 0                                                 | 0                                        | 0                                        | 0                                        | 0                   | 0                           | 0                            | 0                           | 0                           | 0                           |

|        | FS_<br>ABIS<br>T                      | ABI<br>ST_<br>RE<br>AD<br>Y      | 0                               | 0                               | ABI<br>ST_<br>DO<br>NE             | ABI<br>ST_<br>ON<br>GOI<br>NG      | ABI<br>ST_<br>V0<br>MO<br>N_<br>DIA<br>G           | ABI<br>ST_<br>V1<br>UVL<br>P_D<br>IAG             | ABI<br>ST_<br>V1<br>MO<br>N_<br>DIA<br>G | ABI<br>ST_<br>V2<br>MO<br>N_<br>DIA<br>G | ABI<br>ST_<br>V3<br>MO<br>N_<br>DIA<br>G | 0                   | ABI<br>ST_<br>V0<br>MO<br>N | ABI<br>ST_<br>V1<br>UV<br>LP | ABI<br>ST_<br>V1<br>MO<br>N | ABI<br>ST_<br>V2<br>MO<br>N | ABI<br>ST_<br>V3<br>MO<br>N |

|        | FS_<br>SAF<br>ETY<br>_O<br>UTP<br>UTS | 0                                | RS<br>TB_<br>EX<br>T            | RS<br>TB_<br>EV<br>T            | RS<br>TB_<br>DR<br>V               | RS<br>TB_<br>SN<br>S               | RS<br>TB_<br>DIA<br>G                              | 0                                                 | FS0<br>B_<br>DR<br>V                     | FS0<br>B_S<br>NS                         | FS0<br>B_<br>DIA<br>G                    | 0                   | 0                           | LIM<br>P0_<br>DR<br>V        | LIM<br>P0_<br>SN<br>S       | LIM<br>PO_<br>DIA<br>G      | 0                           |

|        | FS_<br>SAF<br>ETY<br>_FL<br>G         | FC<br>CU<br>12_<br>ER<br>R_<br>S | FC<br>CU<br>1_<br>ER<br>R_<br>S | FC<br>CU<br>2_<br>ER<br>R_<br>S | INIT<br>_C<br>RC<br>_N<br>OK<br>_M | INIT<br>_C<br>RC<br>_N<br>OK<br>_I | WD<br>_N<br>OK<br>_M                               | WD<br>_N<br>OK<br>_I                              | 0                                        | FC<br>CU<br>12_<br>M                     | FC<br>CU<br>1_<br>M                      | FC<br>CU<br>2_<br>M | FC<br>CU<br>12_<br>I        | FC<br>CU<br>1_I              | FC<br>CU<br>2_I             | FC<br>CU<br>1_S             | FC<br>CU<br>2_S             |

|        | FS_<br>CRC                            | 0                                | 0                               | 0                               | 0                                  | 0                                  | INIT<br>_C<br>_RC<br>_FS<br>0 B<br>_I<br>MP<br>ACT | INIT<br>_C<br>RC<br>_LI<br>MP<br>0_I<br>MP<br>ACT | 0                                        | CRC.                                     | _VALU                                    | ΙE                  |                             |                              |                             |                             |                             |

# Writable registers

Table 5. Writable registers

|   | Regi<br>ster<br>name       | Bit<br>15      | Bit<br>14      | Bit<br>13                 | Bit<br>12                                                    | Bit<br>11           | Bit<br>10                      | Bit<br>9             | Bit<br>8                               | Bit<br>7            | Bit<br>6                        | Bit<br>5                    | Bit<br>4             | Bit<br>3             | Bit<br>2                  | Bit<br>1             | Bit<br>0                  | De<br>au<br>t v<br>alu<br>e |

|---|----------------------------|----------------|----------------|---------------------------|--------------------------------------------------------------|---------------------|--------------------------------|----------------------|----------------------------------------|---------------------|---------------------------------|-----------------------------|----------------------|----------------------|---------------------------|----------------------|---------------------------|-----------------------------|

|   | M_S<br>YS_C<br>FG          | _              | _              | _                         | _                                                            | _                   | LO<br>CK<br>_IN<br>IT          | GO<br>2IN<br>IT      | GO<br>2N<br>OR<br>MA<br>L              | GO<br>2L<br>PO<br>N | GO<br>2L<br>PO<br>FF            | INT<br>_T<br>O_<br>WU<br>EN | INT<br>B_<br>RE<br>Q | INT<br>B_<br>DU<br>R | _                         | MO<br>D_<br>CO<br>NF | MO<br>D_<br>EN            | O <sup>T</sup> P            |

|   | M_S<br>YS1_<br>CFG         | _              | _              | _                         | VB<br>OS<br>2<br>V1<br>_S<br>W_<br>AL<br>WA<br>YS<br>_E<br>N | _                   | LO<br>AD<br>O<br>TP<br>B<br>YP | SL<br>OT<br>_B<br>YP | TS<br>LO<br>T_<br>DO<br>WN<br>_C<br>FG | _                   | SO<br>FT<br>PO<br>R_<br>RE<br>Q | _                           | DB<br>G_<br>EXI<br>T | _                    | _                         | OT<br>P_<br>EXI<br>T | _                         | O P us                      |

|   | M_R<br>EG_<br>CTRL         | _              | _              | _                         | BUC<br>RHS                                                   |                     | BUC<br>N                       | K_SR                 | HSO                                    | _                   | _                               | V2<br>ON<br>_L<br>PO<br>N   | V2<br>EN             | V2<br>DIS            | V3<br>ON<br>_L<br>PO<br>N | V3<br>EN             | V3<br>DIS                 | O <sup>T</sup><br>P<br>us   |

|   | M_R<br>EG_<br>MSK          | V0<br>UV<br>_M | V0<br>OV<br>_M | V1<br>TW<br>AR<br>N_<br>M | V1<br>TS<br>D_<br>M                                          | V2<br>TS<br>D_<br>M | V3<br>TS<br>D_<br>M            | V2<br>OL<br>_M       | V1<br>UV<br>_M                         | V2<br>UV<br>_M      | V3<br>UV<br>_M                  | V1<br>OV<br>_M              | V2<br>OV<br>_M       | V3<br>OV<br>_M       | V1<br>OC<br>_M            | V2<br>OC<br>_M       | V3<br>OC<br>_M            | 0x                          |

|   | M_R<br>EG1_<br>CTRL        | _              | _              | _                         | _                                                            | _                   | _                              | _                    | _                                      | _                   | _                               | _                           | _                    | _                    | _                         | _                    | V1<br>_O<br>CL<br>S_I     | 0x                          |

|   | M_R<br>EG1_<br>MSK         | _              | _              | _                         | _                                                            | _                   | _                              | _                    | _                                      | _                   | _                               | _                           | _                    | _                    | _                         | _                    | V1<br>_O<br>CL<br>S_<br>M | 0x<br>00                    |

|   | M_IO<br>_CTR<br>L          | _              | _              | _                         | _                                                            | _                   | _                              | HVI<br>O1<br>HI      | HVI<br>O1<br>LO                        | HV<br>IO2<br>HI     | HVI<br>O2<br>LO                 | LVI<br>O3<br>HI             | LVI<br>O3<br>LO      | LVI<br>O4<br>HI      | LVI<br>O4<br>LO           | LV<br>O6<br>HI       | LV<br>O6<br>LO            | 0x                          |

| 1 | M_IO<br>_TIM<br>ER_<br>MSK | _              | _              | _                         | _                                                            | _                   | _                              | _                    | LD<br>T_<br>M                          | LVI<br>5_<br>M      | LVI<br>O4<br>_M                 | LVI<br>O3<br>_M             | HVI<br>O2<br>_M      | HVI<br>O1<br>_M      | _                         | WK<br>2_<br>M        | WK<br>1_<br>M             | 0x                          |

| M_V<br>SUP_<br>COM<br>_MS<br>K    | _                          | _                               | _                               | _                | _                          | _                          | I2C<br>_C<br>RC<br>_M | I2C<br>_R<br>EQ<br>_M | SPI<br>_C<br>RC<br>_M | SPI<br>_C<br>LK<br>_M | SPI<br>_R<br>EQ<br>_M | _                   | VS<br>HS<br>_O<br>V_<br>M | VS<br>HS<br>_U<br>V_<br>M | VS<br>UP<br>OV<br>_M | VS<br>UP<br>UV<br>_M | 0x0<br>000     |

|-----------------------------------|----------------------------|---------------------------------|---------------------------------|------------------|----------------------------|----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------|---------------------------|---------------------------|----------------------|----------------------|----------------|

| M_IO<br>WU_<br>CFG                | LVI<br>5_<br>W<br>UC<br>FG | LVI<br>O4<br>—<br>WU<br>CF<br>G | LVI<br>O3<br>_<br>WU<br>CF<br>G | Re<br>ser<br>ved | HV<br>IO2<br>_D<br>GL<br>T | HVI<br>O1<br>_D<br>GL<br>T | WK<br>2_<br>DG<br>LT  | WK<br>1_<br>DG<br>LT  | HVIO                  |                       | HVIC                  |                     | WK2<br>CFG                | e_WU                      | WK1<br>CFG           | _WU                  | 0x0<br>005     |

| M_IO<br>WU_<br>EN                 | _                          | _                               | LVI5                            | _WU              | LVIC                       | )4_W                       | LVIO                  | _                     | HVIC                  |                       | HVIC                  | _                   | WK2<br>EN                 | WU                        | WK1<br>EN            | _WU                  | 0x0<br>0F<br>F |

| M_W<br>U1_E<br>N                  | _                          | _                               | _                               | _                | _                          | _                          | _                     | _                     | _                     | _                     | LDT_<br>EN            | _WU                 | LIN_<br>EN                | WU                        | CAN<br>EN            | _WU                  | 0x0<br>00<br>F |

| M_TI<br>MER<br>1_CF<br>G          | _                          | _                               | _                               | _                | _                          | _                          | _                     | TIME                  | ER1_                  | TIME                  | ER1_C                 | DN                  |                           | TIME                      | ER1_F                | PER                  | 0x0<br>000     |

| M_TI<br>MER<br>2_CF<br>G          | _                          | _                               | _                               | _                | _                          | _                          | _                     | TIME                  | ER2_                  | TIME                  | ER2_C                 | DN                  |                           | TIME                      | ER2_F                | PER                  | 0x0<br>000     |

| M_TI<br>MER<br>3_CF<br>G          | _                          | _                               | _                               | _                | _                          | _                          | _                     | TIME                  | ER3_                  | TIME                  | ER3_C                 | DΝ                  |                           | TIME                      | ER3_F                | PER                  | 0x0<br>000     |

| M_P<br>WM1<br>_CF<br>G            | _                          | _                               | _                               | PWN<br>LY        | /1_D                       | PW<br>M1<br>_F             | PWN                   | /1_DC                 |                       |                       |                       |                     |                           |                           |                      |                      | 0x0<br>000     |

| M_P<br>WM2<br>_CF<br>G            | _                          | _                               | _                               | PWN<br>LY        | /12_D                      | PW<br>M2<br>_F             | PWN                   | /12_DC                |                       |                       |                       |                     |                           |                           |                      |                      | 0x0<br>000     |

| M_P<br>WM3<br>_CF<br>G            | _                          | _                               | _                               | PWN<br>LY        | //3_D                      | PW<br>M3<br>_F             | PWN                   | //3_DC                | )                     |                       |                       |                     |                           |                           |                      |                      | 0x0<br>000     |

| M_TI<br>MER<br>_ PW<br>M_C<br>TRL | _                          | _                               | _                               | _                | _                          | _                          | _                     | _                     | _                     | TI<br>M1<br>_E<br>N   | TI<br>M2<br>_E<br>N   | TI<br>M3<br>_E<br>N | _                         | PW<br>M1<br>_E<br>N       | PW<br>M2<br>_E<br>N  | PW<br>M3<br>_E<br>N  | 0x0<br>000     |

HS FL T\_  $M_C$ WK1\_HS WU HVIO2\_H HVIO1\_H WK2\_HS 0x0 S CF F S SEL S SEL SEL SEL 000 G OR CE WA WA HVI HV ΚE ΚE M C Ο2 101 S\_FL 2\_ 0x0 1\_ \_0 \_0 OL 000  $G_M$ OL  $L_{\_}$  $L_{\perp}$ SK  $_{\mathsf{M}}$  $_{\mathsf{M}}$ Μ Μ M ai n  $M_H$  $Sx_S$ 0x0 HS4\_SRC\_SEL HS3\_SRC\_SEL HS2\_SRC\_SEL HS1\_SRC\_SEL RC 000 **CFG** HS \_ V HS HS SH ٧ V  $M_H$ SU HS HS HS HS SH SH 0x0 Sx\_C VO 2\_ 4\_ 3 1\_ SU SO 000 **TRL** ٧\_ ΕN ΕN ΕN ΕN ٧ V RE DIS DIS С HS HS HS HS HS HS HS HS HS 12 34 HS  $M_H$ TS 2\_ TS 0x0 4\_ 4\_ 3\_ 2\_ 3\_ 1\_ 1\_ Sx M  $\mathsf{OL}$ OC OL OC  $D_{-}$ OL OC OL OC  $\mathsf{D}_{-}$ 000 SK  $_{\mathsf{M}}$ \_M Μ M  $_{\mathsf{M}}$ М \_M \_M \_M \_M МА AM AM UX MUX UX 0x0 **AMUX** \_CTR \_E \_DI 000 ٧  $M_L$ 0x0 DT C LDT AFTER RUN 000 FG1  $M_L$ 0x0 LDT\_WUP\_L DT\_C 000 FG2 M L 0x0 DT\_C LDT\_WUP\_H 000 FG3 LD LD LD LD MLT\_ T\_ 0x0 DT\_C T2 LDT\_FNCT  $\mathsf{T}_{-}$ SE 000 MO LP ΕN **TRL** DE

| M_C<br>AN                 | _ | _          | _    | _          | _     | _                      | CAN<br>DE                          | _MO                  | _                                | _                     | CA<br>N_<br>FS<br>_DI<br>S | _           | _                    | _                | CA<br>N_<br>TX<br>D_<br>TO       | CA<br>N_<br>TS<br>D_I     | 0x0<br>000 |

|---------------------------|---|------------|------|------------|-------|------------------------|------------------------------------|----------------------|----------------------------------|-----------------------|----------------------------|-------------|----------------------|------------------|----------------------------------|---------------------------|------------|

| M_LI<br>N                 | _ | LIN_<br>DE | MO   | LIN_<br>PE | SLO   | LIN<br>_F<br>S_<br>DIS | LIN<br>_V<br>SH<br>SU<br>V_<br>DIS | LIN<br>_S<br>C       | LIN<br>_T<br>XD<br>_T<br>O       | _                     | _                          | _           | _                    | LIN<br>_S<br>C_I | LIN<br>_T<br>XD<br>_T<br>O_I     | LIN<br>_T<br>SD<br>_I     | 0x0<br>000 |

| M_C<br>AN_L<br>IN_M<br>SK | - | _          | LIN_ | FSM_       | STATE | <b>Ξ_S</b>             |                                    | LIN<br>_S<br>C_<br>M | LIN<br>_T<br>XD<br>_T<br>O_<br>M | LIN<br>_T<br>SD<br>_M | _                          | CAN<br>ATE_ | _FSM <sub>.</sub> _S | _ST              | CA<br>N_<br>TX<br>D_<br>TO<br>_M | CA<br>N_<br>TS<br>D_<br>M | 0x0<br>000 |

| L<br>o<br>gi<br>c | Regi<br>ster<br>name           | Bit<br>15 | Bit<br>14 | Bit<br>13 | Bit<br>12                                                | Bit<br>11                                                | Bit<br>10                                                 | Bit<br>9                                                 | Bit<br>8                                                 | Bit<br>7                                                  | Bit<br>6 | Bit<br>5                                                 | Bit<br>4                                                 | Bit<br>3                                                  | Bit<br>2                                                 | Bit<br>1                                                 | Bit<br>0                                                  | Def<br>aul<br>t<br>val<br>ue |

|-------------------|--------------------------------|-----------|-----------|-----------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|------------------------------|

|                   | M_M<br>EMO<br>RY0              | MEN       | MORY(     | 0         |                                                          |                                                          |                                                           |                                                          |                                                          |                                                           |          |                                                          |                                                          |                                                           |                                                          |                                                          |                                                           | 0x0<br>000                   |

|                   | M_M<br>EMO<br>RY1              | MEN       | MORY.     | 1         |                                                          |                                                          |                                                           |                                                          |                                                          |                                                           |          |                                                          |                                                          |                                                           |                                                          |                                                          |                                                           | 0x0<br>000                   |

|                   | FS_I<br>_OV<br>UV_<br>CFG<br>1 | _         | _         | _         | V1<br>MO<br>N_<br>OV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | V1<br>MO<br>N_<br>OV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T | V1<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | V1<br>MO<br>N_<br>UV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | V1<br>MO<br>N_<br>UV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T | V1<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | -        | V2<br>MO<br>N_<br>OV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | V2<br>MO<br>N_<br>OV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>UV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | V2<br>MO<br>N_<br>UV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T | V2<br>MO<br>N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | OT<br>P f<br>use             |

|                                |   |                                        |                                        | V3<br>MO                                     | V3<br>MO                                                 | V3<br>MO                                                | V3<br>MO                                     | V3<br>MO                                     | V3<br>MO                                      |                                                     | V0<br>MO                                            | V0<br>MO                                             | V0<br>MO                                           | V0<br>MO                                          | V0<br>MO                                      | V0<br>MO                                           |                  |

|--------------------------------|---|----------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|----------------------------------------------------|---------------------------------------------------|-----------------------------------------------|----------------------------------------------------|------------------|

| FS_I<br>_OV<br>UV_<br>CFG<br>2 | - | -                                      | _                                      | N_<br>OV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | N_<br>OV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T             | N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T           | N_<br>UV<br>_R<br>ST<br>B_<br>IM<br>PA<br>CT | N_<br>UV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T | N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T | -                                                   | N_<br>OV<br>_R<br>ST<br>B_<br>IM<br>PA              | N_<br>OV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T         | N_<br>OV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T      | N_<br>UV<br>_R<br>ST<br>B_<br>IM<br>PA            | N_<br>UV<br>_F<br>S0<br>B_I<br>MP<br>AC<br>T  | N_<br>UV<br>_LI<br>MP<br>0_I<br>MP<br>AC<br>T      | OT<br>P f<br>use |