# **NXP AN14179 Based Micro Controllers User Guide**

Home » NXP » NXP AN14179 Based Micro Controllers User Guide 🖫

## **Contents**

- 1 NXP AN14179 Based Micro

- **Controllers**

- **2 Product Usage Instructions**

- 3 Document information

- 4 Introduction

- **5 Memory**

- 6 Clock system

- 7 Pinout

- 8 Peripherals

- 9 Miscellaneous

- 10 Software

- 11 Acronyms and abbreviations

- 12 Revision history

- 13 Legal information

- 14 Documents / Resources

- 14.1 References

- **15 Related Posts**

**NXP AN14179 Based Micro Controllers**

# **Specifications**

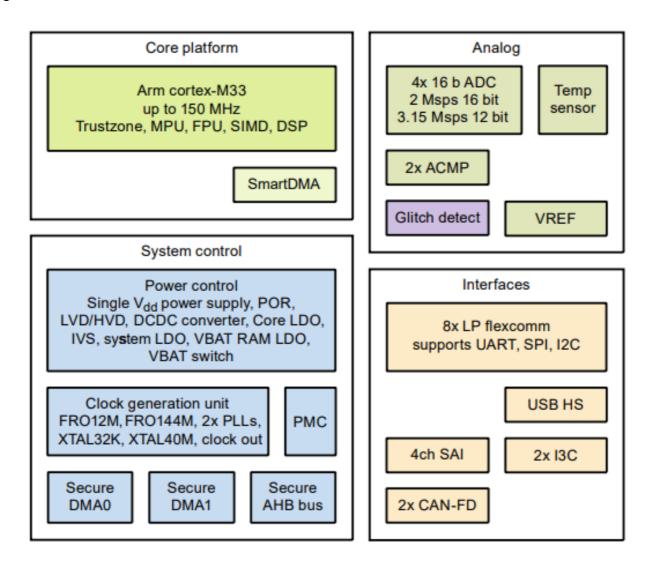

- Core Platform: Arm Cortex-M33 up to 150 MHz with TrustZone, MPU, FPU, SIMD, DSP SmartDMA

- System Control: Power control, Clock generation unit, PMC, Secure DMA0, Secure DMA1, Secure AHB bus

- Analog: 4x 16 b ADC, Temp sensor, 2x ACMP, Glitch detect, VREF

- Interfaces: 8x LP flexcomm supporting UART, SPI, I2C, 4ch SAI, 2x CAN-FD, USB HS, 2x I3C

- Memory: Flash up to 512 kB, RAM up to 320 kB, ECC RAM 32 kB

- HMI: FlexIO, DMIC

- Security: PKC, ECC-256, SHA-512, RNG AES-256, Multi-Rate Timer, Windowed WDT, Debug auth., PRINCE, RTC with anti-tamper pins

- General Purpose Timers: 5x 32 b Timers

- Other Features: Micro-Tick Timer, DICE + UUID, PFR, SRAM PUF, 2x FlexPWM with 2 QDC module, OS

Event Timer, 2x Code WDG, OTP, Tamper detect

# **Product Usage Instructions**

- Step 1: Understanding the Migration Guide

Read through the migration guide provided from MCXNx4x to MCXN23x to understand the differences and changes in the platforms.

- Step 2: Assessing Application Compatibility

Check if your current applications on MCXNx4x are compatible with the MCXN23x platform. Identify any specific features or peripherals that may need modification.

- Step 3: Porting Applications

Follow the guidelines in the migration guide to port your applications from MCXNx4x to MCXN23x. Make necessary code changes based on the platform variations.

- Step 4: Testing and Validation

After porting the applications, thoroughly test them on the MCXN23x platform to ensure proper functionality and performance.

# Frequently Asked Questions (FAQ)

# • Q: What are the key differences between MCXNx4x and MCXN23x?

A: MCXN23x is a cropped version of MCXNx4x with some co-processors and peripherals removed. The MCX series MCU is divided into subseries N, A, L, and W.

# • Q: How can I migrate my applications from MCXNx4x to MCXN23x?

A: Refer to the migration guide provided by NXP that outlines the steps to migrate applications between the two platforms. Ensure compatibility and make necessary adjustments in the code.

#### AN14179

Migration Guide from MCXNx4x to MCXN23x Rev. 1 — 6 May 2024

## **Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14179, MCXNx4x, MCXN23x, migration guide                                                                                                                                                  |

| Abstract    | This application note describes the differences between MCXNx4x and MCXN23x and g uides customers on how to quickly migrate applications from the MCXNx4x platform to the MCXN23x platform. |

#### Introduction

The MCXNx4x is a new-generation MCU launched by NXP after Kinetis and LPC. It integrates excellent IP from both Kinetis and LPC platforms, such as CMC, FlexCAN, FlexIO, and SPC from the Kinetis platform and PowerQuad, SmartDMA, PINT, RTC, and MRT from the LPC platform. The MCX series MCU is divided into four subseries: N, A, L, and W.

## • MCX N (Neural):

- 150 MHz, 512KB-2MB

- On-chip accelerators, enhanced peripherals, and advanced security

# • MCX A (All-purpose):

- Up to 96 MHz, 32KB-1MB

- Intelligent peripherals and various device options for a wide range of applications

# • • MCX W (Wireless):

- Up to 96 MHz

- Low-power Bluetooth LE, Thread, and Zigbee radio optimized for IIoT and Matter applications and advanced security

# • MCX L (Low-power):

- Below 50 MHz, up to 1 MB

- Optimized for always on battery operated applications with the lowest active power and leakage

The MCXNx4x series microcontrollers combine the Arm Cortex-M33 TrustZone core with a CoolFlux BSP32, a PowerQuad DSP Co-processor, and multiple high-speed connectivity options running at 150 MHz. To support a wide variety of applications, the MCX N series includes advanced serial peripherals, timers, high-precision analog, and state-of-the-art security features like secure user code, data, and communications. All MCXNx4x products

include dual-bank flash, which supports read-while-write operation from internal flash. The MCXNx4x series also supports large external serial memory configurations.

#### The MCXNx4x MCU families are as follows:

- N54x: Mainstream MCU with a second M33 core, advanced timers, analog and high-speed connectivity, including high-speed USB, 10/100 Ethernet, and FlexIO, which can be programmed as an LCD controller.

- N94x: Integration of CPU and DSP serial connectivity, advanced timers, high precision analog, and high-speed connectivity, including high-speed USB, CAN 2.0, 10/100 Ethernet, and FlexIO, which can be programmed as an LCD controller.

- MCXN23x is the second product in the MCX N series. It can be regarded as a cropped version of MCXNx4x.

Almost all IPs are reused from MCXNx4x, and some co-processors and peripherals are removed. These removed modules are as follows:

- Co-processor: Secondary Cortex-M33 Core, PowerQuad, NPU, CoolFlux BSP32, and so on.

- Peripherals: FlexSPI, uSDHC, EMVSIM, Ethernet, 12-bit DAC, 14-bit DAC, and so on.

This document describes how to migrate applications from the MCXNx4x platform to the MCXN23x platform.

The system block diagram of MCXN23x is shown in Figure 1.

# Migration Guide from MCXNx4x to MCXN23x

Figure 1. MCXN23x system block diagram

Table 1 lists the comparison of system resources between the MCXNx4x and MCXN23x.

Table 1. Comparison of MCXNx4x and MCXN23x

| MCU series             | MCXNx4x              |                      |                      |                      | MCXN23x               |                      |

|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|----------------------|

| Part                   | MCXN947              | MCXN946              | MCXN547              | MCXN546              | MCXN236               | MCXN235              |

| Package                | VFBGA184<br>HLQFP100 | VFBGA184<br>HLQFP100 | VFBGA184<br>HLQFP100 | VFBGA184<br>HLQFP100 | VFBGA184 H<br>LQFP100 | VFBGA184<br>HLQFP100 |

| Temp range (jun ction) | -40 °C to 125 °C      | -40 °C to 125 °C     |

| MCU series             | MCXNx4x                     |                             |                             |                             | MCXN23x                     |                             |

|------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Part                   | MCXN947                     | MCXN946                     | MCXN547                     | MCXN546                     | MCXN236                     | MCXN235                     |

| Core #1 Cortex-<br>M33 | 150 MHz TZ<br>M<br>+FPU+ETM |

| Core #1 Cache                                   | 16 K     | 16 K     | 16 K     | 16 K     | 16 K    | 16 K    |

|-------------------------------------------------|----------|----------|----------|----------|---------|---------|

| Core #2 Cortex-<br>M33                          | 150 MHz  | 150 MHz  | 150 MHz  | 150 MHz  | _       | _       |

| PowerQuad (DS<br>P and Cordic)                  | Υ        | Υ        | Υ        | Υ        | _       | -       |

| NPU                                             | Υ        | Υ        | Υ        | Υ        | _       | _       |

| SmartDMA                                        | Υ        | Υ        | Υ        | Υ        | Υ       | Υ       |

| CoolFlux BSP32                                  | Υ        | Υ        | -        | -        | _       | _       |

| Total flash                                     | 2 MB     | 1 MB     | 2 MB     | 1 MB     | 1 MB    | 512 kB  |

| Dual bank flash                                 | Υ        | Υ        | Υ        | Υ        | Υ       | Υ       |

| Flash ECC and CRC                               | Υ        | Υ        | Υ        | Υ        | Υ       | Y       |

| Flash encrypt (P rince)                         | Υ        | Υ        | Υ        | Υ        | Υ       | Y       |

| SRAM (ECC use r configurable)                   | 480 K    | 320 K    | 480 K    | 320 K    | 320 K   | 160 K   |

| SRAM with ECC<br>(in addition to m<br>ain SRAM) | 32 K     | 32 K     | 32 K     | 32 K     | 32 K    | 32 K    |

| FlexSPI with 16 k cache                         | 1x, 2 ch | 1x, 2 ch | 1x, 2 ch | 1x, 2 ch | _       | -       |

| uSDHC                                           | Y[1]     | _        | Υ        | Υ        | _       | _       |

| EMVSIM                                          | Y[1]     | _        | Υ        | Y        | _       | _       |

| Secure key man agement                          | PUF/UDF  | PUF/UDF  | PUF/UDF  | PUF/UDF  | PUF/UDF | PUF/UDF |

| Secure subsyste m                               | Υ        | Υ        | Y        | Y        | Y       | Y       |

| Anti-tamper pin <sup>[2</sup>                   | 8        | 8        | 8        | 8        | 6       | 6       |

| Display controlle r (FlexIO)                    | 1        | 1        | 1        | 1        | 1       | 1       |

| TSI                                             | 1[1]     | N        | 1        | 1        | _       | _       |

| DMIC                                            | 4 ch[1]  | _        | 4 ch     | 4 ch     | 4 ch    | 4 ch    |

| SAI                                             | 4 ch     | 4 ch     | 4 ch     | 4 ch     | 4 ch    | 4 ch    |

| LP_FLEXCOMM                                     | 10       | 10       | 10       | 10       | 8       | 8       |

| I3C                                             | 2        | 2        | 2        | 2        | 2       | 2       |

| USB HS                                          | 1        | _        | 1        | 1        | 1       | 1       |

| USB FS                                          | 1        | 1        | 1        | 1        | _       | _       |

| MCU series             | MCXNx4x  |          |          |          | MCXN23x |         |

|------------------------|----------|----------|----------|----------|---------|---------|

| Part                   | MCXN947  | MCXN946  | MCXN547  | MCXN546  | MCXN236 | MCXN235 |

| 10/100 Ethernet<br>MAC | MII/RMII | MII/RMII | MII/RMII | MII/RMII | _       | _       |

| FlexCAN (FD)           | 2        | 2        | 1        | 1        | 2       | 2       |

| DAC 12b, 1 Msp<br>s    | 2        | 2        | 1        | 1        | _       | _       |

| DAC 14b, 5 Msp<br>s    | 1        | 1        | _        | _        | _       | _       |

| Comparator             | 3        | 3        | 2        | 2        | 2       | 2       |

| Opamp                  | 3        | 3        | _        | _        | _       | _       |

| ADC                    | 2        | 2        | 2        | 2        | 2       | 2       |

| VREF                   | Υ        | Υ        | Υ        | Υ        | Υ       | Υ       |

| FlexPWM                | 2        | 2        | 1        | 1        | 2       | 2       |

| Quadrature Dec oder    | 2        | 2        | 1        | 1        | 2       | 2       |

| SINC filter            | Y        | Υ        | _        | _        | _       | _       |

| RTC                    | 1        | 1        | 1        | 1        | 1       | 1       |

| 32b timer              | 5        | 5        | 5        | 5        | 5       | 5       |

| SCTimer                | 1        | 1        | 1        | 1        | _       | _       |

| MRT 24b                | 1        | 1        | 1        | 1        | 1       | 1       |

| uTick timer            | 1        | 1        | 1        | 1        | 1       | 1       |

| WWDT                   | 1        | 1        | 1        | 1        | 1       | 1       |

| OS timer               | 1        | 1        | 1        | 1        | 1       | 1       |

- 1. This feature is only supported on the MCXN947 VFBGA184 package.

- 2. The 100HLQFP supports two Anti-tamper pins.

The following section compares the MCXNx4x and MCXN23x in terms of memory, clock, pinout, and peripherals.

# Memory

This section provides details about flash memory and SRAM memory.

# Flash memory

The MCXNx4x has a flash size of up to 2 MB, while the MCXN23x has a flash size of up to 1 MB, both support dual bank flash and dual image boot. The configuration of flash size for each part is listed in Table 2 and Table 3. Table 2. MCXNx4x part list

|                | Embedded<br>y  | d memor      | Features              |                |              | Package       |       |

|----------------|----------------|--------------|-----------------------|----------------|--------------|---------------|-------|

| Part Number    | Flash (M<br>B) | SRAM<br>(kB) | Tamper pin<br>s (max) | GPIOs<br>(max) | SRAM P<br>UF | Pin co<br>unt | Туре  |

| (P)MCXN547VNLT | 2              | 512          | 2                     | 74             | Υ            | 100           | HLQFP |

|                | Embedde<br>y   | d memor      | Features              |                |              | Package       | •     |

|----------------|----------------|--------------|-----------------------|----------------|--------------|---------------|-------|

| Part Number    | Flash (M<br>B) | SRAM<br>(kB) | Tamper pin<br>s (max) | GPIOs<br>(max) | SRAM P<br>UF | Pin co<br>unt | Туре  |

| (P)MCXN546VNLT | 1              | 352          | 2                     | 74             | Υ            | 100           | HLQFP |

| (P)MCXN547VDFT | 2              | 512          | 8                     | 124            | Υ            | 184           | VFBGA |

| (P)MCXN546VDFT | 1              | 352          | 8                     | 124            | Υ            | 184           | VFBGA |

| (P)MCXN947VDFT | 2              | 512          | 8                     | 124            | Υ            | 184           | VFBGA |

| (P)MCXN947VNLT | 2              | 512          | 2                     | 78             | Υ            | 100           | HLQFP |

| (P)MCXN946VNLT | 1              | 352          | 2                     | 78             | Υ            | 100           | HLQFP |

| (P)MCXN946VDFT | 1              | 352          | 8                     | 124            | Υ            | 184           | VFBGA |

Table 3. MCXN23x part list

|                | Embedde<br>y   | ed Memor      | Features                 |                 |              | Package  |       |

|----------------|----------------|---------------|--------------------------|-----------------|--------------|----------|-------|

| Part Number    | Flash (<br>MB) | SRAM (k<br>B) | Tamper<br>pins (ma<br>x) | GPIOs (<br>max) | SRAM P<br>UF | Pin coun | Туре  |

| (P)MCXN236VNLT | 1              | 352           | 6                        | 74              | Υ            | 100      | HLQFP |

| (P)MCXN236VDFT | 1              | 352           | 6                        | 108             | Υ            | 184      | VFBGA |

| (P)MCXN235VNLT | 0.512          | 192           | 6                        | 74              | Υ            | 100      | HLQFP |

| (P)MCXN235VDFT | 0.512          | 192           | 6                        | 108             | Υ            | 184      | VFBGA |

# **SRAM** memory

The RAM size of the MCXNx4x is up to 512 kB, and the RAM size of the MCXN23x is up to 352 kB. The size of flash and RAM for each part of the MCXNx4x and MCXN23x is listed in Table 4.

Table 4. Flash and RAM size of different parts

| Parts     |            | MCXNx47                        | MCXNx46                        | MCXN236                        | MCXN235                          |

|-----------|------------|--------------------------------|--------------------------------|--------------------------------|----------------------------------|

| Flash     |            | 2M                             | 1M                             | 1M                             | 512 kB                           |

|           | Total size | 512                            | 352                            | 352                            | 192                              |

|           | SRAMX      | 96 (0x04000000-<br>0x04017FFF) | 96 (0x04000000-<br>0x04017FFF) | 96 (0x04000000-<br>0x04017FFF) | 32 (0x04000000- 0<br>x04007FFF)  |

|           | SRAMA      | 32 (0x20000000-<br>0x20007FFF) | 32 (0x20000000-<br>0x20007FFF) | 32 (0x20000000-<br>0x20007FFF) | 32 (0x20000000- 0<br>x20007FFF)  |

| SRAM (kB) | SRAMB      | 32 (0x20008000-<br>0x2000FFFF) | 32 (0x20008000-<br>0x2000FFFF) | 32 (0x20008000-<br>0x2000FFFF) | 32 (0x20008000- 0<br>x2000FFFF)  |

|           | SRAMC      | 64 (0x20010000-<br>0x2001FFFF) | 64 (0x20010000-<br>0x2001FFFF) | 64 (0x20010000-<br>0x2001FFFF) | 64 (0x20010000- 0<br>x2001FFFF)  |

|           | SRAMD      | 64 (0x20020000-<br>0x2002FFFF) | 64 (0x20020000-<br>0x2002FFFF) | 64 (0x20020000-<br>0x2002FFFF) | 64 (0x20020000- 0<br>x2002FFFFF) |

|           | SRAME      | 64 (0x20030000-<br>0x2003FFFF) | 64 (0x20030000-<br>0x2003FFFF) | 64 (0x20030000-<br>0x2003FFFF) | 64 (0x20030000- 0<br>x2003FFFF)  |

| Parts |       | MCXNx47                        | MCXNx46 | MCXN236 | MCXN235 |

|-------|-------|--------------------------------|---------|---------|---------|

|       | SRAMF | 64 (0x20040000-<br>0x2004FFFF) | -       | -       | -       |

|       | SRAMG | 64 (0x20050000-<br>0x2005FFFF) | -       | -       | -       |

|       | SRAMH | 32 (0x20060000-<br>0x20067FFF) | -       | _       | _       |

# **Clock system**

The MCXN23x and MCXNx4x use almost the same clock system, with a few differences.

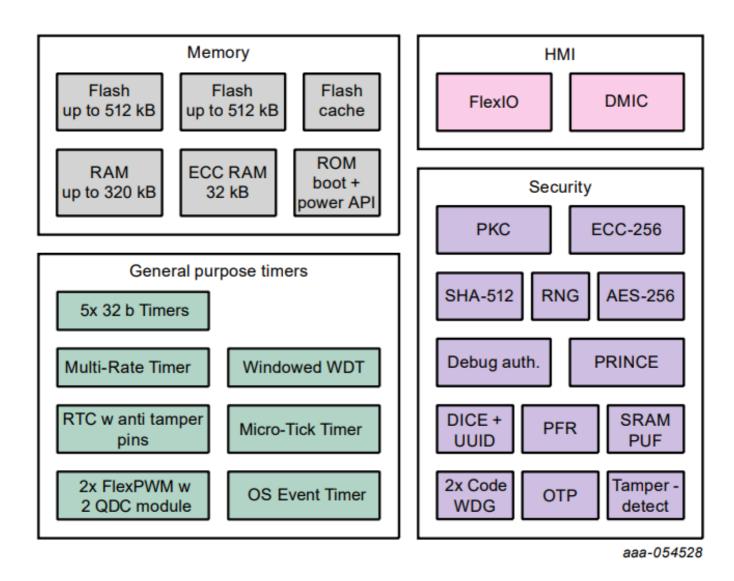

## **FRG**

A Fractional Rate Generator (FRG) is added to the MCXN23x to generate a more accurate clock for the CLKOUT divider. The FRG output is used as the input of the CLKOUT divider, see Figure 2. It can be used to obtain more precise baud rates when the function clock is not a multiple of standard baud rates. This can be primarily used to create a base baud rate clock for USART functions, and can be used for other purposes, such as metering applications.

Figure 2. MCXN23x CLKOUT diagram

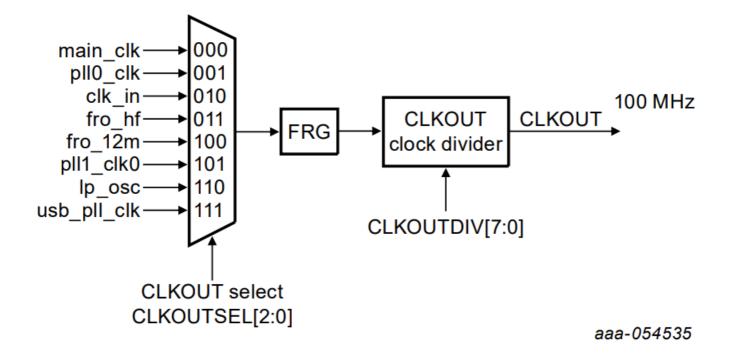

For the CLKOUT diagram of the MCXNx4x, see Figure 3.

Figure 3. MCXNx4x CLKOUT diagram

The CLKOUT\_FRGCTRL register has been added to the SYSCON module of MCXN23x and used to configure numerator and denominator values.

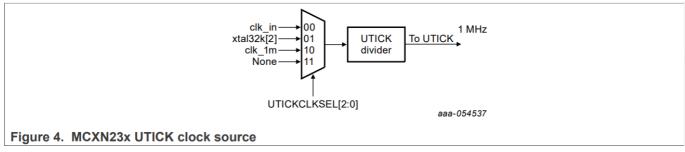

#### UTICK

The clock sources of UTICK (Micro-Tick) on the MCNX23x have been expanded from 1 to 3, and xtal32k[2] and clk\_in have been added as clock sources of UTICK. The clock source of UTICK on the MCXN23x is shown in Figure 4.

In the metering application, UTICK is used to measure power line frequency. To support metering applications, clk in and xtal32k[2] are added to the MCXN23x for high-accuracy clock source.

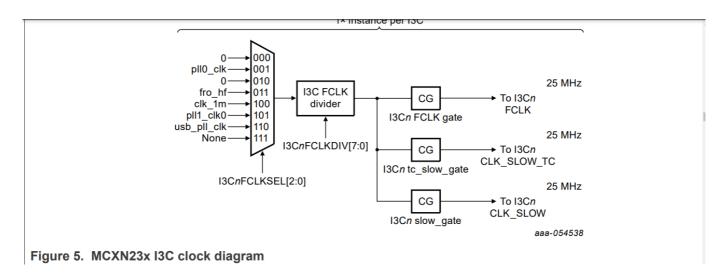

# I3C The clock diagram of I3C on the MCXN23x is shown in Figure 5.

Add clk\_1m as the clock source to the I3C\_FCLK divider, and keep CLK\_SLOW and CLK\_SLOW\_TC synchronized with FCLK.

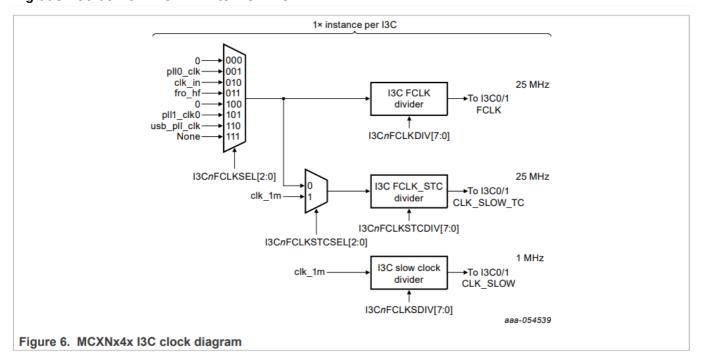

The I3C clock diagram of MCXNx4x is shown in Figure 6.

# Migration Guide from MCXNx4x to MCXN23x

#### **Pinout**

This section compares the pinout differences between MCXNx4x and MCXN23x, including 184VFBGA and 100HLQFP packages.

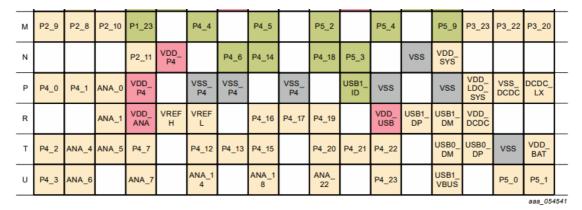

#### 184VFBGA

For the 184VFBGA package, the MCXN23x is pin-to-pin compatible with the MCXNx4x. However, there are some differences between the two. In MCXN23x, 28 pins are removed, including 18 GPIO pins, eight analog pins, and two USB pins. The pinout of the MCXN23x 184VFBGA package is illustrated in Figure 7.

| _  | 1     | 2     | 3           | 4           | 5          | 6                    | 7          | 8          | 9          | 10           | 11           | 12          | 13          | 14            | 15                  | 16           | 17          | _   |

|----|-------|-------|-------------|-------------|------------|----------------------|------------|------------|------------|--------------|--------------|-------------|-------------|---------------|---------------------|--------------|-------------|-----|

| _A | P1_8  | P1_7  |             | P1_4        |            | P0_25                |            | P0_21      |            | P0_17        |              | NC          |             | P0_5          |                     | P0_1         | P0_0        | _   |

| В  | P1_9  | P1_6  | P1_5        | P1_3        |            | P0_24                | P0_23      | P0_22      |            | P0_16        | NC           | NC          |             | P0_4          | P0_3                | P0_2         | P3_0        |     |

| С  |       |       | P1_10       | P1_2        | P1_1       | P1_0                 |            | P0_20      | P0_19      | P0_18        |              | NC          | P0_7        | P0_6          | P3_1                |              |             |     |

| D  | P1_13 | P1_12 | P1_11       | P1_14       |            | vss                  | NC         |            | VSS        |              | NC           | vss         |             | P3_7          | P3_2                | NC           | P3_6        |     |

| Е  |       |       |             | P1_15       | VSS        |                      | NC         | P0_28      |            | P0_27        | P0_14        |             | vss         | P3_8          |                     |              |             |     |

| F  | P1_30 | P1_31 | RESE<br>T_B | P1_17       |            | P1_16                |            | P0_29      |            | P0_26        |              | NC          |             | NC            | P3_9                | P3_11        | P3_10       |     |

| G  |       | vss   |             | P1_18       | P1_19      |                      | VDD        |            |            |              | VDD_<br>P3   |             | P0_15       | NC            |                     | P3_12        |             |     |

| н  | P2_1  | P2_0  | P2_2        |             | VSS        | VDD                  |            | VDD        | VSS        | VDD_<br>P3   |              | VDD_<br>P3  | VSS         |               | P3_15               | P3_13        | P3_14       |     |

| J  |       |       | P2_3        | vss         |            |                      |            | vss        |            | VSS          |              |             |             | VSS           | P3_16               |              |             |     |

| K  | P2_5  | P2_6  | P2_4        |             | NC         | VDD_L<br>DO_<br>CORE |            | VDD_<br>P2 | VSS        | VDD_<br>CORE |              | P5_5        | P5_6        |               | P3_17               | P3_18        | NC          |     |

| L  |       | P2_7  |             | NC          | NC         |                      | VDD_<br>P2 |            |            |              | VDD_<br>CORE |             | P5_7        | NC            |                     | P3_21        |             |     |

| М  | P2_9  | P2_8  | P2_10       | NC          |            | P4_4                 |            | P4_5       |            | P5_2         |              | P5_4        |             | NC            | P3_23               | P3_22        | P3_20       |     |

| N  |       |       |             | P2_11       | VDD_<br>P4 |                      | P4_6       | P4_14      |            | P4_18        | P5_3         |             | VSS         | VDD_<br>SYS   |                     |              |             |     |

| Р  | P4_0  | P4_1  | NC          | VDD_<br>P4  |            | VSS_<br>P4           | VSS_<br>P4 |            | VSS_<br>P4 |              | USB1_<br>ID  | VSS         |             | VSS           | VDD_<br>LDO_<br>SYS | VSS_<br>DCDC | DCDC_<br>LX |     |

| R  |       |       | NC          | VDD_<br>ANA | VREF<br>H  | VREF<br>L            |            | P4_16      | P4_17      | P4_19        |              | VDD_<br>USB | USB1_<br>DP | USB1_<br>DM   | VDD_<br>DCDC        |              |             | _   |

| т  | P4_2  | NC    | NC          | P4_7        |            | P4_12                | P4_13      | P4_15      |            | P4_20        | P4_21        | P4_22       |             | NC            | NC                  | VSS          | VDD_<br>BAT |     |

| U  | P4_3  | NC    |             | ANA_7       |            | NC                   |            | NC         |            | NC           |              | P4_23       |             | USB1_<br>VBUS |                     | P5_0         | P5_1        |     |

|    |       |       |             |             |            |                      |            |            |            |              |              |             |             |               |                     |              | aaa-054     | 540 |

Figure 7. MCXN23x 184VFBGA pinout

In Figure 7, the removed pins are labeled "NC" and are highlighted in yellow. The removed pins on the MCXN23x 184VFBGA are as follows:

# **GPIO** pins:

- P0\_8

- P0\_9

- P0\_10

- P0\_11

- P0\_12

- P0\_13

- P0\_30

- P0\_31

- P1\_20

- P1\_21

- P1\_22

- P1\_23

- P3\_3

- P3\_4

- P3\_5

- P3\_19

- P5\_8

- P5\_9

# Analog pins:

- ANA\_0

- ANA\_1

- ANA\_4

- ANA\_5

- ANA\_6

- ANA\_14

- ANA\_18

- ANA\_22

# **USB** pins:

- USB0\_DM

- USB0\_DP

The pinout of the MCXNx4x 184VFBGA package is shown in Figure 8.

|   | 1     | 2     | 3           | 4     | 5     | 6                    | 7          | 8          | 9     | 10           | 11           | 12         | 13    | 14   | 15    | 16    | 17    |

|---|-------|-------|-------------|-------|-------|----------------------|------------|------------|-------|--------------|--------------|------------|-------|------|-------|-------|-------|

| Α | P1_8  | P1_7  |             | P1_4  |       | P0_25                |            | P0_21      |       | P0_17        |              | P0_9       |       | P0_5 |       | P0_1  | P0_0  |

| В | P1_9  | P1_6  | P1_5        | P1_3  |       | P0_24                | P0_23      | P0_22      |       | P0_16        | P0_11        | P0_10      |       | P0_4 | P0_3  | P0_2  | P3_0  |

| С |       |       | P1_10       | P1_2  | P1_1  | P1_0                 |            | P0_20      | P0_19 | P0_18        |              | P0_8       | P0_7  | P0_6 | P3_1  |       |       |

| D | P1_13 | P1_12 | P1_11       | P1_14 |       | VSS                  | P0_31      |            | VSS   |              | P0_12        | VSS        |       | P3_7 | P3_2  | P3_3  | P3_6  |

| E |       |       |             | P1_15 | vss   |                      | P0_30      | P0_28      |       | P0_27        | P0_14        |            | VSS   | P3_8 |       |       |       |

| F | P1_30 | P1_31 | RESE<br>T_B | P1_17 |       | P1_16                |            | P0_29      |       | P0_26        |              | P0_13      |       | P3_4 | P3_9  | P3_11 | P3_10 |

| G |       | VSS   |             | P1_18 | P1_19 |                      | VDD        |            |       |              | VDD_<br>P3   |            | P0_15 | P3_5 |       | P3_12 |       |

| н | P2_1  | P2_0  | P2_2        |       | VSS   | VDD                  |            | VDD        | VSS   | VDD_<br>P3   |              | VDD_<br>P3 | VSS   |      | P3_15 | P3_13 | P3_14 |

| J |       |       | P2_3        | VSS   |       |                      |            | vss        |       | VSS          |              |            |       | VSS  | P3_16 |       |       |

| к | P2_5  | P2_6  | P2_4        |       | P1_20 | VDD_L<br>DO_<br>CORE |            | VDD_<br>P2 | VSS   | VDD_<br>CORE |              | P5_5       | P5_6  |      | P3_17 | P3_18 | P3_19 |

| L |       | P2_7  |             | P1_22 | P1_21 |                      | VDD_<br>P2 |            |       |              | VDD_<br>CORE |            | P5_7  | P5_8 |       | P3_21 |       |

Figure 8. MCXNx4x 184VFBGA pinout

## 100HLQFP

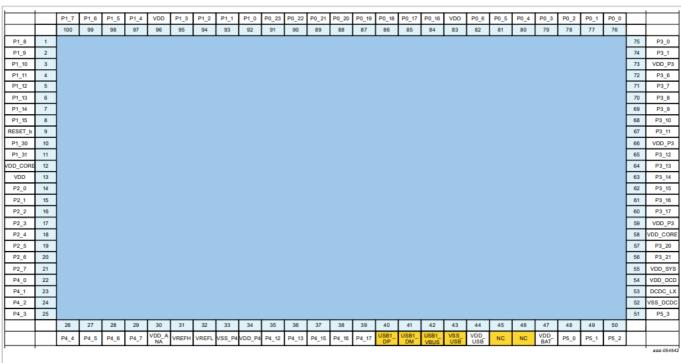

For the 100HLQFP package, MCXN23x is almost pin-to-pin compatible with MCXN54x. The only difference is the USB pin. The MCXN54x supports full-speed USB (USB0) and high-speed USB (USB1), but the MCXN23x only supports USB1, so the MCXN23x does not have USB0\_DM and USB0\_DP pins. The pinout of the MCXN23x 100HLQFP package is as shown in Figure 9.

# Migration Guide from MCXNx4x to MCXN23x

Figure 9. MCXN23x 100HLQFP pinout

The pinout of the MCXN54x and MCXN94x 100HLQFP package is shown in Figure 10.

| N54x     |          |      | P1_7 | P1_6 | P1_5 | P1_4 | VDD         | P1_3  | P1_2  | P1_1   | P1_0   | P0_23 | P0_22 | P0_21 | P0_20 | P0_19 | P0_18       | P0_17       | P0_16         | VDD         | P0_6        | P0_5        | P0_4        | P0_3        | P0_2 | P0_1 | P0_0 |    |          | N54x       |

|----------|----------|------|------|------|------|------|-------------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------------|-------------|---------------|-------------|-------------|-------------|-------------|-------------|------|------|------|----|----------|------------|

|          | N94x     |      | P1_7 | P1_6 | P1_5 | P1_4 | VDD         | P1_3  | P1_2  | P1_1   | P1_0   | _     | P0_22 | P0_21 | P0_20 | P0_19 | P0_18       | P0_17       | P0_16         | VDD         | P0_6        | P0_5        | P0_4        | P0_3        | P0_2 | P0_1 | P0_0 |    | N94x     |            |

|          |          |      | 100  | 99   | 98   | 97   | 96          | 95    | 94    | 93     | 92     | 91    | 90    | 89    | 88    | 87    | 86          | 85          | 84            | 83          | 82          | 81          | 80          | 79          | 78   | 77   | 76   |    |          |            |

| P1_8     | P1_8     | 1    |      |      |      |      |             |       |       |        |        | _     |       |       |       |       |             |             |               |             |             |             |             |             |      | _    |      | 75 | P3_0     | P3_0       |

| P1_9     | P1_9     | 2    | 1    |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 74 | P3_1     | P3_1       |

| P1_10    | P1_10    | 3    | 1    |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 73 | VDD_P3   | VDD_P3     |

| P1_11    | P1_11    | 4    |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 72 | P3_6     | P3_6       |

| P1_12    | P1_12    | 5    | 1    |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 71 | P3_7     | P3_7       |

| P1_13    | P1_13    | 6    |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 70 | P3_8     | P3_8       |

| P1_14    | P1_14    | 7    |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 69 | P3_9     | P3_9       |

| P1_15    | P1_15    | 8    |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 68 | P3_10    | P3_10      |

| RESET_b  | RESET_b  | 9    |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 67 | P3_11    | P3_11      |

| P1_30    | P1_30    | 10   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 66 | VDD_P3   | VDD_P3     |

| P1_31    | P1_31    | -11  |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 65 | P3_12    | P3_12      |

| VDD_CORE | VDD_CORE | 12   | 1    |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 64 | P3_13    | P3_13      |

| VDD      | VDD      | 13   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 63 | P3_14    | P3_14      |

| P2_0     | P2_0     | 14   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 62 | P3_15    | P3_15      |

| P2_1     | P2_1     | 15   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 61 | P3_16    | P3_16      |

| P2_2     | P2_2     | 16   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 60 | P3_17    | P3_17      |

| P2_3     | P2_3     | 17   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 59 | VDD_P3   | VDD_P3     |

| P2_4     | P2_4     | 18   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 58 | VDD_CORE | VDD_CORE   |

| P2_5     | P2_5     | 19   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 57 | P3_20    | P3_20      |

| P2_6     | P2_6     | 20   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 56 | P3_21    | P3_21      |

| P2_7     | P2_7     | 21   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 55 | VDD_SYS  | VDD_SYS    |

| P4_0     | P4_0     | 22   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 54 | VDD_DCDC | VDD_DCDC   |

| P4_1     | P4_1     | 23   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 53 | DCDC_LX  | DCDC_LX    |

| P4_2     | P4_2     | 24   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 52 | VSS_DCDC | VSS_DCDC   |

| P4_3     | P4_3     | 25   |      |      |      |      |             |       |       |        |        |       |       |       |       |       |             |             |               |             |             |             |             |             |      |      |      | 51 | P5_3     | P5_3       |

|          |          |      | 26   | 27   | 28   | 29   | 30          | 31    | 32    | 33     | 34     | 35    | 36    | 37    | 38    | 39    | 40          | 41          | 42            | 43          | 44          | 45          | 46          | 47          | 48   | 49   | 50   |    |          |            |

|          | N94x     |      | P4_4 | P4_5 | P4_6 | P4_7 | VDD_A<br>NA | VREFH | VREFL | VSS_P4 | VDD_P4 | P4_12 | P4_13 | P4_15 | P4_16 | P4_17 | P4_19       | P4_20       | P4_21         | P4_23       | VDD_<br>USB | USB0_<br>DM | USB0_<br>DP | VDD_<br>BAT | P5_0 | P5_1 | P5_2 |    | N94x     |            |

| N54x     |          |      | P4_4 | P4_5 | P4_6 | P4_7 | VDD_A<br>NA | VREFH | VREFL | VSS_P4 | VDD_P4 | P4_12 | P4_13 | P4_15 | P4_16 | P4_17 | USB1_<br>DP | USB1_<br>DS | USB1_<br>VBUS | VSS_<br>USB | VDD_<br>USB | USB0_<br>DM | USB0_<br>DP | VDD_<br>BAT | P5_0 | P5_1 | P5_2 |    |          | N54x       |

|          |          |      |      |      |      |      | Jan         |       |       |        |        |       |       |       |       |       |             |             | .200          |             |             |             |             | 2741        |      |      |      |    |          | asa-054529 |

| Figu     | re 10    | ). N | ΙСΧ  | N94  | x a  | nd I | МСХ         | (N5   | 4x 1  | 00H    | ILQ    | FP p  | oinc  | out   |       |       |             |             |               |             |             |             |             |             |      |      |      |    |          |            |

MCXN94x has six pins P4\_19, P4\_20, P4\_21, P4\_23, USB0\_DM, and USB0\_DP. However, MCXN23x does not have these six pins but instead has four different pins USB1\_DP, USB1\_DM, USB1\_VBUS, and VSS\_USB. For more detailed information about the pinouts, refer to the pinout table in the attachments of MCX Nx4x Reference Manual (document MCXNX4XRM) and MCXN23x Reference Manual (document MCXN23XRM).

# **Peripherals**

In Table 1, we have compared the differences between MCNX23x and MCXNx4x. The MCXN23x does not have various modules such as FlexSPI, PowerQuad, NPU, CoolFlux BSP32, uSDHC, EMVSIM, TSI, USB FS, Ethernet, 12-bit DAC, 14-bit DAC, Opamp, SINC Filter, and SCTimer. The following section describes the differences between the common peripherals between the MCXN23x and MCXNx4x.

#### **GPIO**

As described in Section 4.1, the MCXNx4x supports up to 124 GPlOs, and the MCXN23x supports up to 106 GPlOs. However, in the case of MCXN23x, 18 GPlO pins are not supported. Apart from being used as GPlOs, these 16 pins also support the functions listed in Table 5.

Table 5. Removed GPIOs on the MCXN23x 184VFBGA package

| 184B<br>GA A<br>LL | 184B<br>GA<br>ALL<br>Pin N<br>ame | Analo<br>g                    | ALT<br>0  | ALT1          | ALT2       | ALT3       | ALT4         | ALT5              | ALT6                 | ALT7                   | ALT1<br>0     | ALT1         |

|--------------------|-----------------------------------|-------------------------------|-----------|---------------|------------|------------|--------------|-------------------|----------------------|------------------------|---------------|--------------|

| K5                 | P1_20                             | ADC1<br>_A20/<br>CMP1<br>_IN3 | P1_<br>20 | TRIG_I<br>N2  | FC5_<br>P4 | FC4_<br>P0 | CT3_<br>MAT2 | SCT0<br>-<br>OUT8 | FLEXI<br>O0_ D<br>28 | Smart<br>DMA_<br>PIO16 | _             | CAN1<br>_TXD |

| L5                 | P1_21                             | ADC1<br>_A21/<br>CMP2<br>_IN3 | P1_<br>21 | TRIG_<br>OUT2 | FC5_<br>P5 | FC4_<br>P1 | CT3_<br>MAT3 | SCT0<br>OUT9      | FLEXI<br>O0_ D<br>29 | Smart<br>DMA_<br>PIO17 | SAI1_<br>MCLK | CAN1<br>_RXD |

| L4  | P1_22 | ADC1<br>_A22 | P1_<br>22 | TRIG_I<br>N3  | FC5_<br>P6 | FC4_<br>P2  | CT_IN<br>P14 | SCT0<br>-<br>OUT4 | FLEXI<br>O0_ D<br>30 | Smart<br>DMA_<br>PIO18 | _                  | _ |

|-----|-------|--------------|-----------|---------------|------------|-------------|--------------|-------------------|----------------------|------------------------|--------------------|---|

| M4  | P1_23 | ADC1<br>_A23 | P1_<br>23 | _             | _          | FC4_<br>P3  | CT_IN<br>P15 | SCT0<br>OUT5      | FLEXI<br>O0_ D<br>31 | Smart<br>DMA_<br>PIO19 | _                  | _ |

| L14 | P5_8  | ADC1<br>_B16 | P5_<br>8  | TRIG_<br>OUT7 | _          | TAMP<br>ER6 | _            | _                 | _                    | _                      | _                  | _ |

| M14 | P5_9  | ADC1<br>_B17 | P5_<br>9  |               | _          | TAMP<br>ER7 | _            | _                 | _                    | _                      | _                  | _ |

| K17 | P3_19 | _            | P3_<br>19 | _             | FC7_<br>P6 | _           | CT2_<br>MAT1 | PWM<br>1_X1       | FLEXI<br>O0_ D<br>27 | Smart<br>DMA_<br>PIO19 | SAI1_<br>RX_F<br>S | _ |

| G14 | P3_5  | _            | P3_<br>5  | _             | FC7_<br>P3 | _           | CT_IN<br>P19 | PWM<br>0_X3       | FLEXI<br>O0_ D<br>13 | Smart<br>DMA_<br>PIO5  | _                  | _ |

| F14 | P3_4  | _            | P3_<br>4  | _             | FC7_<br>P2 | _           | CT_IN<br>P18 | PWM<br>0_X2       | FLEXI<br>00_ D<br>12 | Smart<br>DMA_<br>PIO4  | _                  | _ |

| D16 | P3_3  | _            | P3_<br>3  | _             | FC7_<br>P1 | _           | CT4_<br>MAT1 | PWM<br>0_X1       | FLEXI<br>O0_ D<br>11 | Smart<br>DMA_<br>PIO3  | _                  | _ |

| C12 | P0_8  | ADC0<br>_B8  | P0_<br>8  | _             | FC0_<br>P4 | _           | CT_IN<br>P0  | _                 | FLEXI<br>O0_ D<br>0  | _                      | _                  | _ |

| A12 | P0_9  | ADC0<br>_B9  | P0_<br>9  | _             | FC0_<br>P5 | _           | CT_IN<br>P1  | _                 | FLEXI<br>O0_ D<br>1  | _                      | _                  | _ |

| B12 | P0_10 | ADC0<br>_B10 | P0_<br>10 | _             | FC0_<br>P6 | _           | CT0_<br>MAT0 | _                 | FLEXI<br>O0_ D<br>2  | _                      | _                  | _ |

| B11 | P0_11 | ADC0<br>_B11 | P0_<br>11 | _             | _          | _           | CT0_<br>MAT1 | _                 | FLEXI<br>O0_ D<br>3  | _                      | _                  | _ |

| D11 | P0_12 | ADC0<br>_B12 | P0_<br>12 | _             | FC1_<br>P4 | FC0_<br>P0  | CT0_<br>MAT2 | _                 | FLEXI<br>O0_ D<br>4  | _                      | _                  | _ |

| F12 | P0_13 | ADC0<br>_B13 | P0_<br>13 | _             | FC1_<br>P5 | FC0_<br>P1  | CT0_<br>MAT3 | _                 | FLEXI<br>O0_ D<br>5  | _                      | _                  | _ |

| E7  | P0_30 | ADC0<br>_B22 | P0_<br>30 | _             | FC1_<br>P6 | FC0_<br>P6  | CT_IN<br>P2  | _                 | _                    | _                      | _                  | _ |

| D7  | P0_31 | ADC0<br>_B23 | P0_<br>31 | _             | _          | _           | CT_IN<br>P3  | _                 | _                    | _                      | _                  | _ |

and SAI1 are involved. However, the other pins on the MCX23x can also implement the same functions as these pins. Before migrating from the MCXNx4x to MCXN23x, it is important to check if your design on the MCXNx4x uses these pins. If it does, you must reassign the pins to meet your requirements.

## • USB

All the MCXN54x parts and the MCXN94x 184VFBGA packages support FS USB (USB0) and HS USB (USB1). Whereas the MCXN94x 100HLQFP package only supports HS USB. All the MCXN23x parts only support HS USB.

#### DMIC

All parts of the MCXN23x and MCXN54x have a DMIC module and support up to four digital microphone channels. However, for the MCXN94x series, the MCXN946 does not support the DMIC module, and the MCXN947 only supports the DMIC module on the 184VFBGA package.

# LP FLEXCOMM

The MCXNx4x series supports 10 LP\_FLEXCOMM modules. Each LP\_FLEXCOMM can be configured as UART, I2C, and SPI. Among them, the IO of LP\_FLEXCOMM6/7/8/9 is high-speed IO, and the highest clock that can be configured is 150 MHz. The MCXN23x only supports eight LP\_FLEXCOMM modules and does not support LP\_FLEXCOMM8 and LP\_FLEXCOMM9, only LP\_FLEXCOMM6 and LP\_FLEXCOMM7 can use high-speed IOs.

## Comparator

The MCXN94x series supports three Comparator (CMP) modules, while the MCXN54x and MCXN23x series only support two CMP modules.

#### ADC

The MCXNx4x and MCXN23x series have two 16-bit ADC modules but differ in the number of ADC channels they support. The MCXNx4x can support up to 75 ADC channels, while the MCXN23x can support up to 63 ADC channels. For the 184VFBGA package, the MCXN23x cannot support the 12 ADC channels listed in Table 6 because the 16 pins mentioned in Table 6 are removed.

Table 6. Removed ADC channels on MCXN23x

| 184BGA ALL Pin Name | Analog            |

|---------------------|-------------------|

| P1_20               | ADC1_A20/CMP1_IN3 |

| P1_21               | ADC1_A21/CMP2_IN3 |

| P1_22               | ADC1_A22          |

| P1_23               | ADC1_A23          |

| P5_8                | ADC1_B16          |

| P5_9                | ADC1_B17          |

| P3_19               | _                 |

| P3_5                | _                 |

| P3_4                | _                 |

| P3_3                | _                 |

| P0_8                | ADC0_B8           |

| P0_9                | ADC0_B9           |

| P0_10               | ADC0_B10          |

| P0_11               | ADC0_B11          |

| 184BGA ALL Pin Name | Analog   |

|---------------------|----------|

| P0_12               | ADC0_B12 |

| P0_13               | ADC0_B13 |

| P0_30               | ADC0_B22 |

| P0_31               | ADC0_B23 |

**Note:** The term ADC channels refer to the external ADC input channels.

## FlexPWM and Quadrature Decoder (QDC)

The MCXN94x and MCXN23x are compatible with dual-motor applications as they support two FlexPWM modules and two QDC modules. But, the MCXN54x supports only one FlexPWM module and one QDC module, making it suitable for single-motor solutions only.

# **DMA**

The MCXNx4X has two eDMA modules, eDMA0 and eDMA1. Each module supports 16 DMA channels. The MCXN23x also has 2 eDMA modules, but eDMA1 only supports eight channels.

# Anti-tamper pin

The tamper pins for MCXNx4x are listed in Table 7 and Table 8. The MCXNx4x has eight tamper pins, and the MCXN23x has six tamper pins. Pin P5\_8 and P5\_9 are removed on MCXN23x.

Note: The 100HLQFP packaged parts of MCXN4x and MCXN23x only support two tamper pins.

# Table 7. Tamper pins on MCXNx4x

| 184BGA<br>all | 184VFBG<br>A<br>pin name | 100HLQFP<br>N94x | 100HLQFP<br>N94x pin na<br>me | 100HLQFP<br>N54x | 100HLQFP<br>N54x pin na<br>me | ALT0 | ALT3    |

|---------------|--------------------------|------------------|-------------------------------|------------------|-------------------------------|------|---------|

| M10           | P5_2                     | 50               | P5_2                          | 50               | P5_2                          | P5_2 | TAMPER0 |

| N11           | P5_3                     | 51               | P5_3                          | 51               | P5_3                          | P5_3 | TAMPER1 |

| M12           | P5_4                     | _                | _                             | _                | _                             | P5_4 | TAMPER2 |

| K12           | P5_5                     | _                | _                             | _                | _                             | P5_5 | TAMPER3 |

| K13           | P5_6                     | _                | _                             | _                | _                             | P5_6 | TAMPER4 |

| L13           | P5_7                     | _                | _                             | _                | _                             | P5_7 | TAMPER5 |

| L14           | P5_8                     | _                | _                             | _                | _                             | P5_8 | TAMPER6 |

| M14           | P5_9                     | _                | _                             | _                | _                             | P5_9 | TAMPER7 |

Table 8. Tamper pins on MCXN23x

| 184BGA ball | 184VFBGA pin | 100HLQFP | 100HLQFP pin | ALT0 | ALT3    |

|-------------|--------------|----------|--------------|------|---------|

| M10         | P5_2         | 50       | P5_2         | P5_2 | TAMPER0 |

| N11         | P5_3         | 51       | P5_3         | P5_3 | TAMPER1 |

| M12         | P5_4         | _        | _            | P5_4 | TAMPER2 |

| 184BGA ball | 184VFBGA pin | 100HLQFP | 100HLQFP pin | ALT0 | ALT3    |

|-------------|--------------|----------|--------------|------|---------|

| K12         | P5_5         | _        | _            | P5_5 | TAMPER3 |

| K13         | P5_6         | _        | _            | P5_6 | TAMPER4 |

| L13         | P5_7         | _        | _            | P5_7 | TAMPER5 |

# **Miscellaneous**

This section provides details about the boot source and debugging.

# 1. Boot source

The MCXN23x does not have the FlexSPI module and does not support external flash boot, but the MCXNx4x supports external flash boot, which can be configured with the BOOT\_CFG field in the Customer Manufacturing/Factory Configuration Area (CMPA) to implement this function.

# 2. Debug

The MCXNx4x debug module supports ITM, DWT, ETM, ETB W/2KB RAM, and TPIU function, but the ETM

and ETB W/2KB functions are removed on the MCXN23x.

# 3. Power management

Power management The power management of MCXN23x and MCXNx4x is identical, so they can use the same power supply circuit.

#### Software

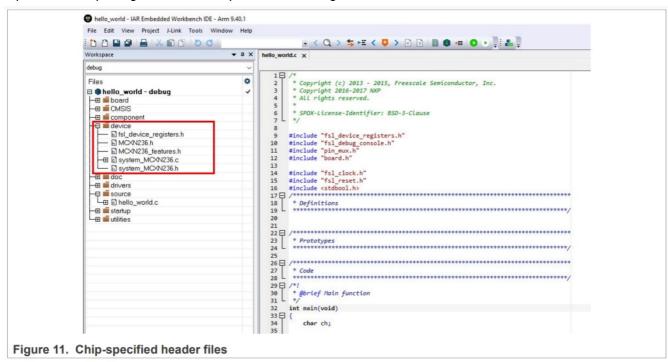

This chapter describes some software considerations when porting the code from the MCXNx4x platform to the MCXN23x platform. In this section, take the hello\_world project from the FRDM-MCXN236 SDK as an example, and the IDE is IAR 9.40.1.

# 1. Chip-specified header files

Each SDK project has a device directory containing chip-specific header files. These header files must be replaced when porting code between platforms, see Figure 11.

# 2. SDK driver

Ensure that the SDK driver directory does not include unsupported modules such as FlexSPI and uSDHC for MCXN23x.

#### 3. Start up file

Replace the start\_up file of MCXNx4x with MCXN23x start\_up file, as some modules are removed, and the interrupt vector table is different.

#### 4. Linker file

The MCXN23x and MCXNx4x can have different Flash and RAM sizes, so the customer must replace the linker file to ensure the Flash and RAM range used in the linker file is suitable.

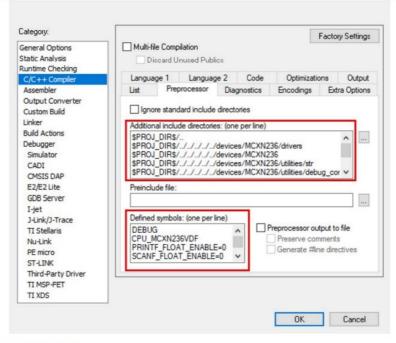

# 5. IDE-related configuration update

When porting code from the MCXNx4x to MCXN23x, update IDE-related configurations such as path and macro definition, see Figure 12.

Figure 12. Path and macro definition

.Note: If the customer does not use the removed pins and peripherals on the MCXN23x, then the customer can directly solder the MCXN23x chip to the MCXNx4x board and can directly use the MCXNx4x software, but the linker file must be updated to match the flash and RAM size of MCXN23x. Currently, this method has only been verified on IAR IDE.

#### Conclusion

This document compares system resources and software differences between the MCXNx4x and MCXN23x, making project migration quick and easy.

#### Related documentation/resources

Table 9 lists additional documents and resources that can be referred to for more information. Some of the documents listed below may be available only under a non-disclosure agreement (NDA). To request access to these documents, contact local field applications engineer (FAE) or sales representative.

Table 9. Related documentation/resources

| Document                                                            | Link/how to access |

|---------------------------------------------------------------------|--------------------|

| MCX Nx4x Reference Manual (document MCXNX4XR M)                     | MCXNX4XRM          |

| MCXN23x Reference Manual (document MCXN23XR M) (document MCXN23XRM) | MCXN23XRM          |

# Acronyms and abbreviations

Table 10 defines the acronyms and abbreviations used in this document.

Table 10. Acronyms and abbreviations

| Acronym | Definition |

|---------|------------|

|         |            |

| ADC     | Analog-to-Digital Converter                       |

|---------|---------------------------------------------------|

| CAN     | Controller Area Network                           |

| СМР     | Comparator                                        |

| СМРА    | Customer Manufacturing/Factory Configuration Area |

| CPU     | Central Processing Unit                           |

| CRC     | Cyclic Redundancy Check                           |

| DAC     | Digital-to-Analog Converter                       |

| DMA     | Direct Memory Access                              |

| DSP     | Digital Signal Processor                          |

| DWT     | Drop-Weight Tear                                  |

| ECC     | Error Correcting Code                             |

| eDMA    | Enhanced Direct Memory Access                     |

| ETM     | Embedded Trace Macrocell                          |

| ЕТВ     | Embedded Trace Buffer                             |

| FlexCAN | Flexible Controller Area Network Interface        |

| FlexIO  | Flexible Input/Output                             |

| GPIO    | General-Purpose Input/Output                      |

| HS USB  | High-Speed USB                                    |

| I2C     | Inter-Integrated Circuit                          |

| ITM     | Instrumentation Trace Macrocell                   |

| IP      | Internet Protocol                                 |

| LDO     | Liquid Crystal Display                            |

| LPC     | Low Pin Count                                     |

| MAC     | Media Access Control                              |

| MCU     | Microcontroller Unit                              |

| MII     | Media-Independent Interface                       |

| NDA     | Non-Disclosure Agreement                          |

| OS      | Operating System                                  |

| QDC     | Quadrature Decoder                                |

| RTC     | Real-Time Clock                                   |

| TPIU    | Trace Port Interface Unit                         |

| TSI     | Touch System Interface                            |

| SAI     | Serial Audio Interface                            |

| SDK  | Software Development Kit    |

|------|-----------------------------|

| SPI  | Serial Peripheral Interface |

| SRAM | Static Random-Access Memory |

| Acronym | Definition                                  |  |

|---------|---------------------------------------------|--|

| RAM     | Random-Access Memory                        |  |

| RMII    | Reduced Media Independent Interface         |  |

| TPIU    | Trace Port Interface Unit                   |  |

| UART    | Universal Asynchronous Receiver Transmitter |  |

| USB     | Universal Serial Bus                        |  |

| VREF    | Voltage Reference                           |  |

#### Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license: Copyright 2024 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## **Revision history**

Table 11 summarizes the revisions to this document.

Table 11. Revision history

| Document ID   | Release date | Description            |

|---------------|--------------|------------------------|

| AN14179 v.1.0 | 06 May 2024  | Initial public version |

# Legal information

#### **Definitions**

Draft — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result

in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including – without limitation -lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default

in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications

and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Terms and conditions of commercial sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="https://www.nxp.com/profile/terms">https://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless

this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles

to reduce the effect of these vulnerabilities on customer's applications

and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP B.V. — NXP B.V. is not an operating company and it does not distribute or sell products.

# **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile — are trademarks and/or registered trademarks of Arm Limited (or its subsidiaries or affiliates) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

Bluetooth — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

- CoolFlux is a trademark of NXP B.V.

- CoolFlux DSP is a trademark of NXP B.V.

- EdgeLock is a trademark of NXP B.V.

- IAR is a trademark of IAR Systems AB.

- Kinetis is a trademark of NXP B.V.

- Matter, Zigbee are developed by the Connectivity Standards Alliance. The Alliance's Brands and all goodwill

associated therewith, are the exclusive property of the Alliance.

• MCX — is a trademark of NXP B.V.

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

- © 2024 NXP B.V.

- For more information, please visit: <a href="https://www.nxp.com">https://www.nxp.com</a>

- · All rights reserved.

- Date of release: 6 May 2024 Document identifier: AN14179

## **Documents / Resources**

## References

• User Manual

Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.