# multiLane AT4079B GUI Bit Error Ratio Tester User Manual

Home » multiLane » multiLane AT4079B GUI Bit Error Ratio Tester User Manual

#### **Contents**

- 1 multiLane AT4079B GUI Bit Error Ratio

- 2 To Avoid Fire or Personal Injury

- **3 INTRODUCTION**

- **4 Product Software**

- 5 Installation

- 6 Pre-Channel Settings

- 7 Log file System

- 8 Documents / Resources

- 8.1 References

- 9 Related Posts

# multiLane AT4079B GUI Bit Error Ratio Tester

#### **Product Information**

The AT4079B GUI User Manual is a user guide for the AT4079B Bit Error Ratio Tester. It is designed for testing and analyzing high-speed data transmission systems. The tester supports 8-lane operation with a baud rate

ranging from 1.25 to 30 GBaud. It is capable of testing both NRZ and PAM4 signaling formats. The manual provides detailed instructions on how to use the tester's graphical user interface (GUI) to perform various tests and measurements. The AT4079B GUI User Manual is the revised version 0.4, dated March 2021. It contains important notices regarding government restrictions on the use, duplication, or disclosure of the product by the Government. The manual also mentions that MultiLane Inc. products are protected by U.S. and foreign patents.

#### **Product Usage Instructions**

General Safety Precautions Before using the AT4079B Bit Error Ratio Tester, review the following safety precautions to ensure safe operation:

- Use the specified power cord certified for the country of use.

- Observe all terminal ratings and markings on the product.

- Do not operate the tester without covers or panels.

- Avoid touching exposed connections and components when power is present.

- If there is suspected damage to the product, have it inspected by qualified service personnel?

- Avoid operating the tester in wet/damp conditions or in an explosive atmosphere.

- · Keep the product surfaces clean and dry.

#### Installation

Follow these steps to install the AT4079B Bit Error Ratio Tester:

- 1. Ensure the minimum PC requirements are met. (Refer to the manual for details on minimum PC requirements.)

- 2. Connect the tester to the PC using an Ethernet connection.

# First Steps

To begin using the AT4079B Bit Error Ratio Tester, follow these

# steps

1. Connect the tester to the PC through Ethernet.

# AT4079B GUI User Manual

8-Lane | 1.25-30 GBaud | Bit Error Ratio Tester 400G | NRZ & PAM4 AT4079B GUI User Manual-rev0.4 (GB 20210310a) March 2021

#### **Notices**

Copyright get © MultiLane Inc. All rights reserved. Licensed software products are owned by MultiLane Inc. or its suppliers and are protected by United States copyright laws and international treaty provisions. Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software — Restricted Rights clause at FAR 52.227-19, as applicable. MultiLane Inc. products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges are reserved.

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified. Only qualified personnel should perform service procedures. While using this product, you may need to access other parts of the system. Read the General Safety Summary in other system manuals for warnings and cautions related to operating the system.

# To Avoid Fire or Personal Injury

Use the Proper Power Cord. Only use the power cord specified for this product and certified for the country of use. Observe All Terminal Ratings. To avoid fire or shock hazards, observe all ratings and markings on the product. Consult the product manual for further rating information before making connections to the product.

- Do not apply a potential to any terminal, including the common terminal that exceeds the maximum rating of that terminal.

- · Do Not Operate Without Covers.

- Do not operate this product with covers or panels removed.

- Avoid Exposed Circuitry. Do not touch exposed connections and components when power is present.

- Do Not Operate with Suspected Failures.

- If you suspect there is damage to this product, have it inspected by qualified service personnel.

- Do Not Operate in Wet/Damp Conditions. Do Not Operate in an Explosive Atmosphere. Keep Product Surfaces Clean and Dry

- Caution statements identify conditions or practices that could result in damage to this product or other property.

#### INTRODUCTION

This is the user operation manual for the AT4079B. It covers the installation of its software package and explains how to operate the instrument for pattern generation and error detection; how to control the clocking system, inputs/outputs and all the available measurements.

| Acronym    | Definition                        |  |  |  |  |  |

|------------|-----------------------------------|--|--|--|--|--|

| BERT       | Bit Error Rate Tester             |  |  |  |  |  |

| API        | Application Programming Interface |  |  |  |  |  |

| NRZ        | Non-Return to Zero                |  |  |  |  |  |

| GBd        | Gigabaud                          |  |  |  |  |  |

| PLL        | Phase-Locked Loop                 |  |  |  |  |  |

| PPG        | Pulse Pattern Generator           |  |  |  |  |  |

| GHz        | Gigahertz                         |  |  |  |  |  |

| PRD        | Product Requirements Document     |  |  |  |  |  |

| I/O        | Input/Output                      |  |  |  |  |  |

| R&D        | Research & Development            |  |  |  |  |  |

| HW, FW, SW | Hardware, Firmware, Software      |  |  |  |  |  |

| GUI        | Graphical User Interface          |  |  |  |  |  |

| ATE        | Automatic Test Equipment          |  |  |  |  |  |

| HSIO       | High-Speed I/O                    |  |  |  |  |  |

- This manual supports the instrument AT4079B and it is compatible with the Advantest V93000 HSIO test head extender frame/twinning.

- All APIs are available for Linux and tested under Smartest 7. For the list of APIs and how to use them please refer to the "API" folder on the AT4079B webpage.

- This manual does not explain how to operate the instrument using the SmarTest environment. Refer to Advantest's website below for the SmarTest document noting that it may change without notice and also require login privileges provided through Advantest.

- https://www.advantest.com/service-support/ic-test-systems/software-information-and-download/v93000-software-information-and-download

#### **Product Software**

The instrument includes the following software: AT4079B GUI. Instrument GUI runs on Windows XP (32/64 bit), Windows 7.8, and 10.

**NOTE.** These applications require the Microsoft .NET Framework 3.5.

If the Microsoft.NET Framework 3.5 is needed, it can be downloaded through this link:

$\underline{http://download.microsoft.com/download/2/0/e/20e90413-712f-438c-988e-fdaa79a8ac3d/dotnetfx35.exe.}$

For more products updates, check the following webpage: <a href="https://multilaneinc.com/products/at4079b/">https://multilaneinc.com/products/at4079b/</a>

### **Minimum PC Requirements**

The Windows PC properties for the AT4079B GUI application should meet the following specifications:

- · Windows 7 or greater

- · Minimum 1 GB RAM

- 1 Ethernet card to establish a connection with the device

- USB connector

- · Pentium 4 processor 2.0 GHz or greater

- NET Framework 3.5 sp1

**NOTE**: It is recommended to connect the BERT via Ethernet to one PC only to prevent conflict from multiple user commands.

NOTE: It is not recommended to hook up the instrument to a slow network or to connect to it through WiFi

#### Installation

This section addresses the installation and bring-up of the instrument. It is divided in two main sections:

- System start-up

- · How to connect to the instrument

#### **First Steps**

When you first receive the instrument, it has a pre-configured IP address from the factory. This IP address is printed on a label on the instrument. You may choose to keep this IP or to change it. If you need to change the IP address refer to the "How to change IP and update firmware" section.

#### **Connect through Ethernet**

Connect the PC to the backplane via the RJ45 connector through an Ethernet cable to be able to control it. To connect via Ethernet, the IP address of the board is required. To learn more options on how to connect the

Ethernet cable go to the section Connect through an Ethernet Cable. Note that no drivers are required; you simply should know the current board IP address, you need to enter it in the text box next to the IP label shown in the below picture, then click on the connect button.

Figure 1: Connect Via Ethernet

Figure 1: Connect Via Ethernet You are now connected.

- Once connected, the Connect button turns into Disconnect.

- To make sure that you are connected, you can also ping your device.

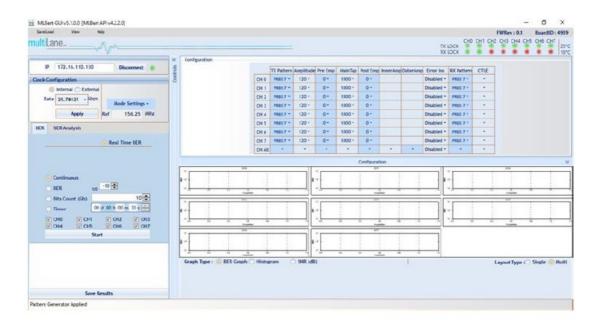

The instrument is now powered up and connected through the right IP address. Next, you need to configure the signal generated. Although the AT4079B is an ATE type of instrument, it can be used as any other Multilane BERT and can be controlled from the general BERT GUI for Windows. This is for instance useful when troubleshooting a setup. The general BERT GUI can be downloaded from the company website, under the download section of the AT4079B. Figure 2: AT4079B GUI In your instrument's GUI, there are several control fields that are each explained below.

Figure 2: AT4079B GUI

# **Instrument Connect Field**

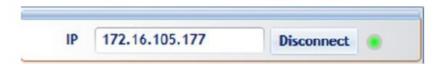

Figure 3: Instrument Connect Field

The first thing you want to do is to make sure you are connected to the instrument. If you are, the connect button will read Disconnect, and the green LED lights up.

Figure 3: Instrument Connect Field

#### **PLL Lock and Temperature Status Field**

Figure 4: PLL Lock and Temperature Status

Keep an eye on the LEDs and temperature readings in this field. TX Lock means that the PLL of the PPG is locked. RX lock goes green only if a signal of correct polarity and PRBS kind is detected on the error detector. If the temperature reaches 65°C, the electronics will auto shut off.

# Reading the installed Firmware Revision

The installed firmware version is displayed in the upper right corner of the GUI. Figure 5: Reading the installed Firmware Revision

FWRev: 0.1 BoardID: 4939

Figure 5: Reading the installed Firmware Revision

#### Line Rate Configuration (Applies to all channels at once)

Figure 6: Line Rate Configuration

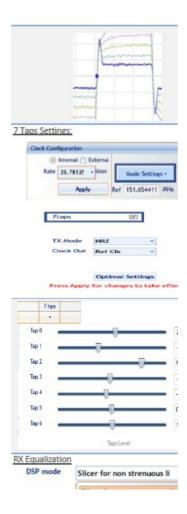

Figure 6: Line Rate Configuration This is where you set the bitrate for all 8 channels by typing in the desired rate. The drop-down menu lists a shortcut to the most widely used bitrates, however, you are not limited only to that list. You can also select the clock input. The clock is internal by default. You should only change to external clock feed-in when you need to synchronize two or more AT4079Bs to each other in a slave-master fashion; In that case, you connect the clocks in a daisy chain. After changing from internal to external clock and vice versa, you have to click apply for changes to take effect (this takes a few seconds).

| Мо                   | de Settings +    |    |   |

|----------------------|------------------|----|---|

| Ref 20               | 1.416015 MHz     |    |   |

| Gray Mappi           | ng 🔳             |    |   |

|                      |                  |    |   |

|                      |                  |    |   |

|                      |                  |    |   |

| TX Mode              | PAM4             | *  |   |

| TX Mode<br>Clock Out | PAM4 Monitor Clk | ¥. | , |

|                      | 5.5.022.3        | *  |   |

|                      | Monitor Clk      | *  | • |

|                      | Monitor Clk      | •  | , |

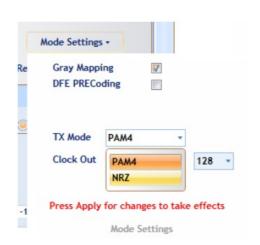

# Mode & Clock Out Settings (Apply to all channels at once)

Description Screenshot The "Ref" denotes the frequency of the clock output. This is a function of the bitrate and will vary according to your clock-out settings under the "Mode" menu. Knowing the clock frequency being output by the BERT is helpful when you want to trigger an oscilloscope. Some oscilloscopes require a clock frequency above 2 GHz. To get the AT4079B to output that, go under mode settings and select the Clock out to be "Monitor". Choose the denominator so that the result is within the scope range. To switch between NRZ and PAM-4 codings, use the TX Mode setting, then click Apply. The options Gray Mapping and DFE pre-coding are only available in PAM4 mode. DFE Pre-coding sends a pre-amble for a DFE receiver to sync to before the actual PRBS pattern is transmitted, to avoid DFE error propagation. Does the decoder implement a 1+D scheme in response to an ?=?? +? encoding. Currently, the DFE precoding is automatic and not user selectable. Gray Mapping enables use of PRBSxxQ defined in IEEE802.3bs. When Gray mapping is enabled, the PRBS13 and PRBS31 under the pattern select menu turn into PRBS13Q and PRBS31Q respectively. Gray mapping basically re-arranges the symbol mapping to the following:  $00 \rightarrow 0.01 \rightarrow 1.01 \rightarrow 0.01 \rightarrow$

# **Pre-Channel Settings**

|        | TX Pattern | Amplitude | Pre Emp | MainTap | Post Emp | InnerAmp | OuterAmp | Error Ins  | RX Pattern | CTLE |

|--------|------------|-----------|---------|---------|----------|----------|----------|------------|------------|------|

| CH 0   | PRBS 7 *   | 120 •     | 0 -     | 1000 -  | 0 +      | 1000 *   | 2000 *   | Disabled * | PRBS 7 *   | *    |

| CH 1   | PRBS 7 *   | 120 -     | 0 -     | 1000 -  | 0 -      | 1000 -   | 2000 -   | Disabled • | PRBS 7 *   | *    |

| CH 2   | PRBS 7 *   | 120 •     | 0 -     | 1000 -  | 0 -      | 1000 -   | 2000 -   | Disabled • | PRBS 7 *   | *    |

| CH 3   | PRBS 7 *   | 120 -     | 0 +     | 1000 -  | 0 -      | 1000 -   | 2000 -   | Disabled * | PR8S 7 *   | *    |

| CH 4   | PRBS 7 *   | 120 *     | 0 +     | 1000 *  | 0 +      | 1000 *   | 2000 *   | Disabled * | PRBS 7 *   | *    |

| CH 5   | PRBS 7 *   | 120 -     | 0 -     | 1000 -  | 0 -      | 1000 -   | 2000 -   | Disabled • | PRBS 7 *   | •    |

| CH 6   | PRBS 7 *   | 120 -     | 0 +     | 1000 -  | 0 -      | 500 -    | 2000 +   | Disabled • | PRBS 7 *   | *    |

| CH 7   | PRBS 7 *   | 120 -     | 0 -     | 1000 -  | 0 -      | 1000 *   | 2000 -   | Disabled * | PR8S 7 *   | *    |

| CH AII |            | -         | -       |         |          | 1500 -   |          | Disabled * |            |      |

You can adjust these settings on a per-channel basis. These are:

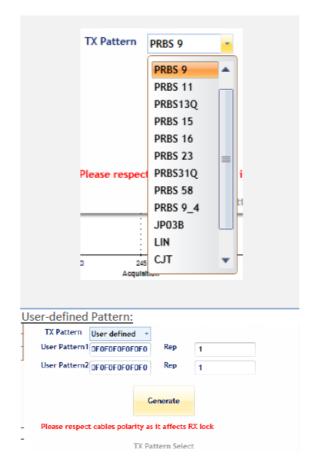

Description Screenshot The AT4079B can output a wide range of pre-defined patterns. In addition to the PRBS patterns, there are linearity and jitter test patterns. Also, on top of the pre-defined patterns, the user has the possibility of defining his/her own pattern – more on this further below. Note: error detection only works on the PRBS patterns existing in the RX pattern drop-down list. It isn't possible to do error detection on custom-defined patterns. The custom pattern is made up of 2 fields with 16 hexadecimal characters each. One must fill out both fields with all 32 hex characters. Every hex character is 4 bits wide, making up 2 PAM4 symbols; example 0xF is 1111 so in the Gray-coded PAM domain this results in 22, assuming the PAM levels are denoted 0, 1, 2, and 3 Example 2: to transmit a stair signal 0123, fill out the fields with repetitions of 1E

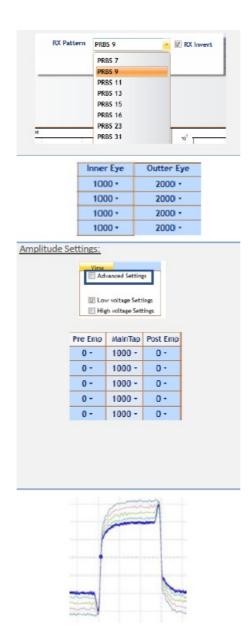

In the RX Pattern menu, one can browse all the patterns with which error detection is possible. Note that TX and RX patterns must be the same to acquire RX lock and consequently be able to do measurements. Also, the pattern polarity is very important and makes all the difference between having an RX PLL lock or no lock at all. You can ensure correct polarity by connecting the TX-P side of the cable to the RX-P and the TX-N to the RX-N. if you do not respect this rule, you can still invert polarity from the GUI on the RX side only. Inner and Outer eye level controls trim the high and low values of the middle PAM eye. Possible control values range from 500 to 1500 for the inner eye control and from 1500 to 2000 for the outer eye. Optimal values are typically in the middle of the range. An example of tweaking the Outer eye settings is shown below The default amplitude control is calibrated in millivolt values but does not allow you to change the equalizer settings. If you need to change the FFE tap settings, please go to then enable 'Advanced Settings'. This enables you to control pre- and post-emphasis values

for each channel, but amplitude values will not be shown in millivolt. By default, three taps are shown and can be edited. Think of the amplitude as a digital equalizer with a main tap, pre-cursor (pre-emphasis), and post-cursor (post-emphasis). In the regular case, pre- and post-cursors are set to zero; the amplitude is controlled using the main tap. The main, pre-, and post-taps use digital values ranging between -1000 and +1000. Increasing and decreasing the pre and post-cursors will also affect the amplitude. Please ensure that the sum of pre-, post, and main cursors is  $\leq$  1000 to have optimal performance. If the sum of taps exceeds 1000, the linearity of the TX signal cannot be maintained.

Post-cursor effect on a pulse The user can also edit a 7 taps coefficients instead of just 3 taps by clicking on and then checking the box of Taps Settings: After applying the settings, the seven-tap control will be available for editing under the amplitude menu. Any one of the 7 taps can be defined as the main tap; in this case, taps preceding it will be pre-cursors. Likewise, taps following the main tap will be post-cursors. The slicer is the default mode. The reflection canceller consumes more power but is useful for strenuous channels containing transitions of impedance

# **Example Inner and Outer Settings Effect**

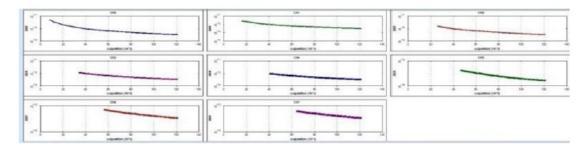

Figure 11: BER Graphs

Taking Measurements Bit Error Ratio Reading To be able to start BER measurements, the instrument ports should be in the loopback mode, which means the TX port should be connected to the RX port and the PPG and ED patterns should match. One does not necessarily need to supply a PRBS from the same physical instrument – the source can be a different instrument and the error-detector of the AT4079B can derive its own clock from the received data (no need for a separate clock link). However, if Gray coding is used in the source, one should tell the receiver to expect Gray coding as well. If there is a match in pattern, polarity, and coding but still no lock, there could be an MSB/LSB swap on one side.

#### **BER Control**

A BER measurement can run in continuous mode and will not stop until the user intervenes and clicks the stop button. BER can also be set to run unit a target value is reached or until a certain number of bits has been transmitted (units of 10 gigabits). The Timer lets the user set a time for the BER to stop.

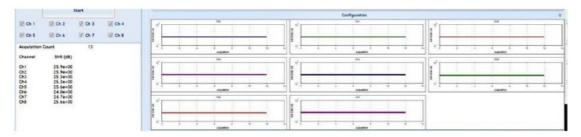

#### **BER Table of Results**

The summary of BER measurements is shown in the following pane:

#### **BER Graph**

Plots BER values collected on the graph

Figure 11: BER Graphs

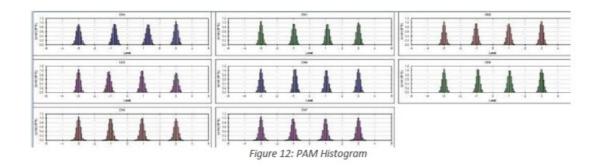

#### **Histogram Analysis**

The histogram is the tool of choice to troubleshoot the link. You can think of it as a scope built into the receiver and it works even if you do not have a pattern lock. For both NRZ and PAM signals, the histogram graph is shown as follows:

Figure 12: PAM Histogram

Figure 13: SNR ratio for PAM signal

- The thinner the peaks the better the performance of the PAM signal and the less the jitter. These peaks can be enhanced using the pre/post-emphasis available.

- The same analogy applies as that of the PAM histogram.

# Signal-to-Noise Ratio Analysis

SNR is a quantitative way to measure the strength of the received signal – it is given in dB.

## Log file System

In the AT4079B BERT, there is a log file system, where every exception handled or unhandled by the GUI will be saved. After the first run, the GUI creates a file in the main directory/exception log and saves all the existing exceptions. In case the user had a problem with the software, he can send the exception file to our team.

Note: the exception file will be deleted automatically after every 1 week of work.

#### Saving and Loading Settings

The instrument always saves the last used settings in non-volatile memory. These settings are automatically restored the next time you connect to the BERT. In addition, you can create and save your own set of setup files and can revert to them when needed. Look for the Save/Load menu in the menu bar of the GUI.

# How to Change IP Address and Update Firmware

For info regarding changing the IP address and updating the firmware of the AT4079B, kindly download the

"Maintenance" folder from <a href="https://multilaneinc.com/products/at4079b/">https://multilaneinc.com/products/at4079b/</a>. The folder consists of the following:

- ML Maintenance GUI

- USB Driver

- User Guide

# **Documents / Resources**

multiLane AT4079B GUI Bit Error Ratio Tester [pdf] User Manual AT4079B, AT4079B GUI Bit Error Ratio Tester, GUI Bit Error Ratio Tester, Bit Error Ratio Tester, Error Ratio Tester, Tester

# References

- Microsoft Cloud, Computers, Apps & Gaming

- Download Drivers & Updates for Microsoft, Windows and more Microsoft Download Center

- MultiLane

- <u>A advantest.com/service-support/ic-test-systems/software-information-and-download/v93000-software-information-and-download</u>

Manuals+,