# Microsemi UG0856 PolarFire FPGA Video Kit User Guide

Home » Microsemi » Microsemi UG0856 PolarFire FPGA Video Kit User Guide 🖫

#### **Contents**

- 1 Microsemi UG0856 PolarFire FPGA Video

- 2 Getting Started

- 2.1 Kit Contents

- 2.2 Block Diagram

- 2.3 Board Overview

- 3 Hardware Settings

- 3.1 Jumper Settings

- **3.2 LEDs**

- 3.3 Power Sources

- **4 Board Components and Operations**

- 4.1 SPI Serial Flash

- 4.2 MIPI- RX Connector (CSI-2 Application)

- 4.3 Transceivers

- 4.4 Programming

- 5 Documents / Resources

- **5.1 References**

- **6 Related Posts**

Microsemi UG0856 PolarFire FPGA Video Kit

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Micro semi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at <a href="https://www.microsemi.com">www.microsemi.com</a>.

Revision History Revision 2.0

Added a footnote in FMC HPC Connector (J14).

**Revision 1.0**

The first publication of this document.

### **Getting Started**

The Microchip PolarFire® FPGA Video Kit (POLARFIRE VIDEO KIT), which is RoHS-compliant, enables you to evaluate the PolarFire MPF300TS-1FCG1152I FPGA for the following interfaces:

- MIPI CSI-2 RX interface

- HDMI2.0

- HDMI1.4

- DDR4 memory

- FMC HPC with 8 Transceiver lanes

- · UART Interface to the FTDI device

- · SPI Interface to the SPI Flash device

#### **Kit Contents**

The following table lists the contents of the PolarFire Video Kit.

| Item                                                                                   | Quantity |

|----------------------------------------------------------------------------------------|----------|

| Dual Camera Sensor Module                                                              | 1        |

| PolarFire Video Board featuring the MPF300TS-1FCG1152I device with 300K logic elements | 1        |

| 12 V, 5 A AC power adapter and cord                                                    | 1        |

| USB 2.0 A-male to mini-B cable programming                                             | 1        |

| Quickstart card                                                                        | 1        |

| Free one-year Libero Gold software license                                             | 1        |

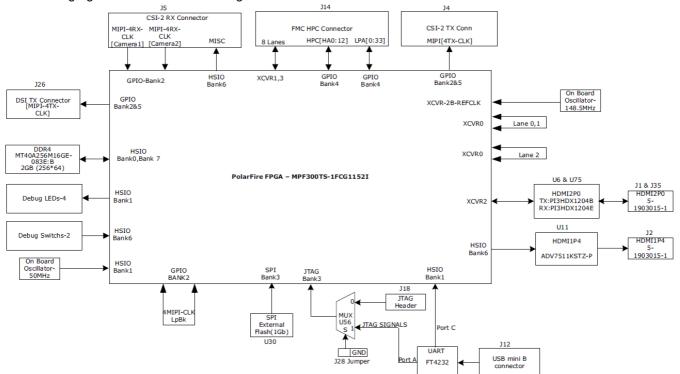

### **Block Diagram**

The following figure shows the block diagram of the video kit.

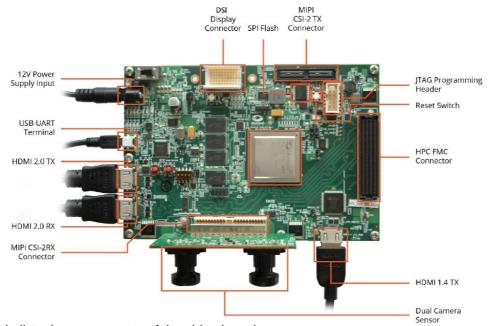

#### **Board Overview**

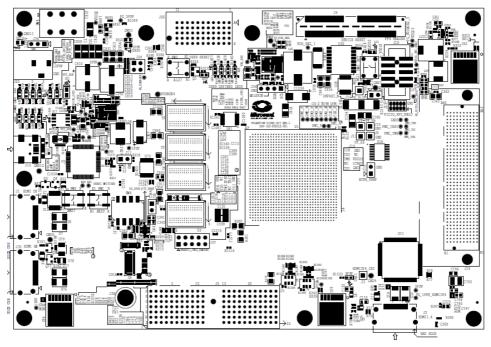

The following figure shows a labeled image of the video board highlighting its components.

# **Board Callout**

The following table lists the components of the video board.

# **Board Components**

| Component                        | Label on        | Board Description                                                                                                                                                    |  |

|----------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                  | Featured Device |                                                                                                                                                                      |  |

| Component                        | Label on Board  | Description                                                                                                                                                          |  |

| PolarFire FPGA                   |                 | MPF300TS-1FCG1152I FPGA with data security feature                                                                                                                   |  |

|                                  | Po              | ower Supply                                                                                                                                                          |  |

| 12 V power supply                | J20             | The board is powered by a 12 V power source using an external +12 V/5 A DC jack                                                                                      |  |

| ON/OFF switch                    | SW4             | Power ON/OFF switch from +12 V external DC jack                                                                                                                      |  |

|                                  |                 | Clocks                                                                                                                                                               |  |

| On-board 50 MHz clock oscillator | X3              | 50 MHz clock oscillator with single-ended output                                                                                                                     |  |

| XCVR reference<br>clock          | Y5              | 148.5 MHz oscillator (differential LVDS output) that provides reference clock (REFCLK) via PolarFire device pins AF29 and AF30. These pins are connected to the XCVR |  |

| Clock Synthesizer                | U15             | CDCEL913PWR Clock Synthesizer for HDMI1.4 clocks and programmable through the I2C                                                                                    |  |

|                            | FPGA Prograi    | mming and Debugging                                                                                                                                                                        |

|----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FT4232H                    | U70             | USB-to-quad serial ports in various configurations                                                                                                                                         |

| JTAG programming<br>header | J18             | This header is used to program and debug the PolarFire device using FlashPro4 or FlashPro5. In the FlashPro software, the appropriate programmer (FlashPro4 orFlashPro5) must be selected. |

| SPI flash                  | U30             | One 1 Gb SPI Flash from Micron<br>MT25QL01GBBB8ESF-0SIT (P/N) connected to<br>SPI pins on bank 3 of the PolarFire device                                                                   |

|                            | Me              | mory Chips                                                                                                                                                                                 |

| DDR4 Memory                | U1,U2,U3 and U4 | Four 4 Gb (MT40A256M16GE-083E:B) chips are connected in Fly-by topology with a 64-bit data bus for storing data bits                                                                       |

| FMC HPC connector          | J14             | FMC connector with eight XCVR lanes and 13 Differential pairs HPC[HA0:12] and LPC[0:33])                                                                                                   |

|                            | Me              | mory Chips                                                                                                                                                                                 |

| DDR4 Memory                | U1,U2,U3 and U4 | Four 4 Gb (MT40A256M16GE-083E:B) chips are connected in Fly-by topology with a 64-bit data bus for storing data bits                                                                       |

| FMC HPC connector          | · J14           | FMC connector with eight XCVR lanes and 13 Differential pairs HPC[HA0:12] and LPC[0:33])                                                                                                   |

|                            | Vide            | eo Interfaces                                                                                                                                                                              |

| CSI-2 RX connector         | J5              | MIPI data and clock signals are received from Camera sensor board                                                                                                                          |

| DSI TX connector           | J26             | MIPI data and clock signals are transmitted to Display daughter board through the connector                                                                                                |

| CS-2 TX connector          | J4              | MIPI data and clock signals are transmitted to Display daughter board through the connector                                                                                                |

|                            | Gener           | ral Purpose I/O                                                                                                                                                                            |

| Switches                   | SW1 and SW2     | Push-button switches for user-interface debugging applications                                                                                                                             |

| DIP Switches               | SW6             | Four DIP switches for testing                                                                                                                                                              |

|                            |                 |                                                                                                                                                                                            |

# **Hardware Settings**

This section provides information about jumper settings, switches, LEDs, and DIP switches on the PolarFire video board.

# **Jumper Settings**

Connect the jumpers according to the settings specified in the following table.

| Jumper | Description                                                                                     | Pin(s)                                                                                    | Default |

|--------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|

| J15    | SPI Slave and Master mode selection. By Default SPI master                                      | 1-2                                                                                       | Closed  |

| J19    | XCVR_VREF is connected to GND                                                                   | 1-2                                                                                       | Closed  |

| J28    | Close pin 1-2 to program through the FTDI<br>Open pin 1-2 to program the external<br>Flash pro5 | 1-2                                                                                       | Closed  |

| J24    | Jumper to select the PolarFire VDDAUX4                                                          | Close pin2-4 for 3V3                                                                      | Closed  |

|        | for Bank4 voltage                                                                               | Close pin2-4 for 2V5                                                                      | Open    |

| J25    | Jumper to select the PolarFire VCCIO                                                            | Close pin 1 and 2 for 3.3 V                                                               | Open    |

|        | voltage (VCCIO_HPC_VADJ)                                                                        | Close pin 3 and 4 for 2.5 V                                                               | Open    |

|        |                                                                                                 | Close pin 5 and 6 for 1.8 V                                                               | Closed  |

|        |                                                                                                 | Close pin 7 and 8 for 1.5 V                                                               | Open    |

|        |                                                                                                 | Close pin 9 and 10 for 1.2 V                                                              | Open    |

| J36    | Jumper to select the SW3 input or the ENABLE_FT4 232 signal from the FT4232H chip               | Close pin 1 and 2 for manual power switching using SW3                                    | Close   |

|        |                                                                                                 | Close pin 2 and 3 for remote power switching using the GPIO capability of the FT4232 chip | Open    |

**LEDs**

The following table lists the power supply LEDs.

| Description             |

|-------------------------|

| 12 V voltage rail       |

| 5 V voltage rail        |

| 3.3V voltage rail       |

| 1.0V voltage rail       |

| 1.8V voltage rail       |

| VDD25 Voltage rail      |

| VDDAUX2_5 Voltage rail  |

| VDDA(1V05) Voltage rail |

| VDDAUX4 Voltage rail    |

|                         |

| LED        | Description                 |

|------------|-----------------------------|

| DS7-Green  | 1.2V voltage rail           |

| DS6-Green  | VCCIO_HPC_VADJ voltage rail |

| DS12-Green | 1.8V HDMI1V4 voltage rail   |

| DS13-Green | 0.6V VTT voltage rail       |

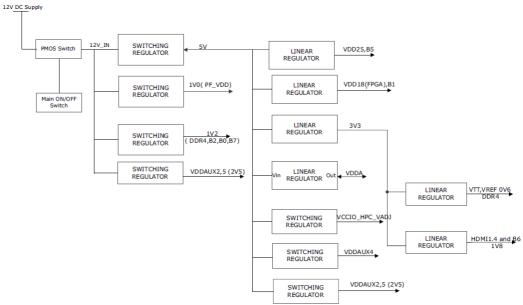

### **Power Sources**

devices, see:

### https://www.microchip.com/design-centers/power-management/dc-dc-converters-regulators.

The following table lists the key power supplies required for normal operation of the PolarFire video board.

| PolarFire Bank | I/O Rail       | Voltage |

|----------------|----------------|---------|

| Bank 0         | 1P2V           | 1.2V    |

| Bank 1         | 1P8V           | 1.8V    |

| Bank 2         | 1P2V_B2        | 1.2V    |

| Bank 3         | VDD25          | 2.5V    |

| Bank 4         | VCCIO_HPC_VADJ | 1.8V    |

| Bank 5         | VDD25          | 2.5V    |

| Bank 6         | 1P8V_HDMI1V4   | 1.8V    |

| Bank 7         | 1P2V           | 1.2V    |

The following figure shows the power supply scheme used in the PolarFire video board. **Power Supply Scheme**

The following table lists the suggested Microchip power regulators for PolarFire FPGA voltage rails. **Power Regulators1**

| Voltage Rail   | Part Number      | Description                     | Current |

|----------------|------------------|---------------------------------|---------|

| 5V             | MIC24055YJL-TR   | IC REG BUCK ADJ 12A SYNC 28QFN  | 12A     |

| 1V             | MIC24055YJL-TR   | IC REG BUCK ADJ 12A SYNC 28QFN  | 12A     |

| 1V2            | MIC24046YFL-TR   | IC REG BUCK PROG 5A SYNC 20VQFN | 5A      |

| VDDAUX2&5      | MIC23303YML-T5   | IC REG BUCK ADJ 3A SYNC 12DFN   | 3A      |

| VDDAUX4        | MIC23303YML-T5   | IC REG BUCK ADJ 3A SYNC 12DFN   | 3A      |

| VCCIO_HPC_VADJ | MIC24046YFL-TR   | IC REG BUCK PROG 5A SYNC 20VQFN | 5A      |

| VREF,VTT       | MIC5166YML-TR    | IC PWR SUP 3A HS DDR TERM 10MLF | 3A      |

| HDMI1.4        | MCP1726T-ADJE/MF | IC REG LINEAR POS ADJ 1A 8DFN   | 1A      |

| VDD25          | MIC69502WR       | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

| 3V3            | MIC69502WR       | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

| VDD18          | MIC69502WR       | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

| 1V05           | MIC69502WR       | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

|                |                  |                                 |         |

1. These regulators are not pin compatible with the existing video kit schematics. Use these regulators for new

board designs.

### **Board Components and Operations**

This section describes the key components of the PolarFire Video board and important board operations. **Memory Interface**

The following figure shows the memory interface scheme.

PolarFire

Data DQ[63:0]

DQS/DQS#[7:0]

DDR4 SDRAM 256×16 (512 MB)

4 memory chips

Control lines

As shown in Figure 4, page 9, Four 4 Gb DDR4 SDRAM chips are used as flexible volatile memory for user applications. The DDR4 interface is implemented in the HSIO Bank 0 and Bank 7. The DDR4 SDRAM specifications are as follows:

- MT40A256M16GE-083E:B

- Quantity: Four chips are connected in Fly-by topology

- · Density: 16 Gb

- Data rate: DDR4 64-bit at 166 MHz clock rate

The PolarFire video board design uses the DDR4 and POD12 standards for the DDR4 interface. The default board assembly for the DDR4 standard uses RC terminations.

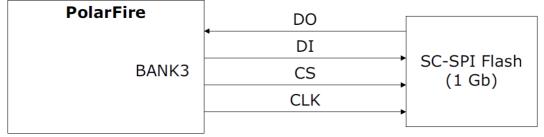

### **SPI Serial Flash**

The following figure shows the SPI Flash and its interface with the PolarFire device.

The SPI flash specifications for the PolarFire device are:

• Density: 1 Gb

• Voltage: 2.7 V to 3.6 V (MT25QL01GBBB8ESF-0SIT)

• Frequency: 90 MHz

• Quantity = 1

• SPI mode support: Modes 0 and 3

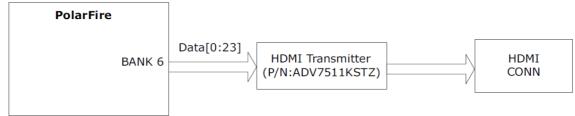

#### **HDMI1.4 Interface**

One HDMI1.4 Transmitter is connected to the PolarFire device to support the HDMI1.4 standard as shown in the following figure.

The HDMI interface is implemented in Bank6.

### The HDMI1.4 transmitter specifications for the PolarFire device are:

Part Number of the HDMI Transmitter: ADV7511KSTZ

• Operating frequency: up to 225 MHz

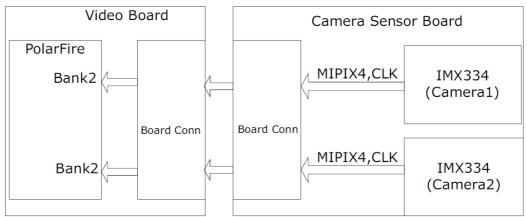

#### MIPI- RX Connector (CSI-2 Application)

The video board supports a dual Camera image sensor daughter card that can be connected using the CSI-2 RX interface (J5) for CSI-2 RX applications. The daughter card includes two IMX334 cameras. Each image sensor supports a four-lane MIPI interface. The daughter card is connected to the video board via the board to board connector as shown in Figure 7, page 10. The MIPI output signals are connected to Bank 2. The image sensor supports maximum 1782 Mbps.

### **MIPI-RX Connection**

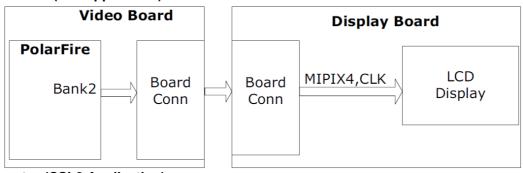

### **MIPI-TX Connector (DSI Application)**

The video board supports the MIPI transmitter X4 lanes and clock for DSI application, as shown in Figure 8, page 11. MIPI TX signals are interfaced to the LCD display. An adaptor board for the LCD display can be connected through the J26 connector on the video board. This adaptor board contains the LCD mating connector and the auxiliary circuit required for the display. For more information, see the video board schematics.

### **MIPI-TX Connection (DSI Application)**

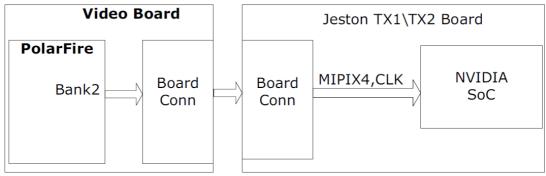

### **MIPI-TX connector (CSI-2 Application)**

The video board supports the MIPI X4 lanes and clock for the CSI-2 transmitter application, . For testing, the video board can be can be interfaced with Nvidia's Jetson TX1\TX2 development board using a mating connector cable.

Note: Jetson board is not part of the kit.

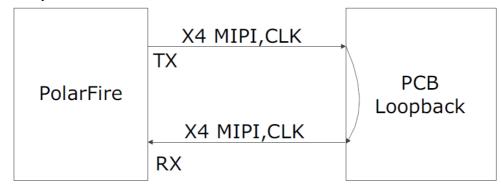

### **MIPI-TX and RX PCB Loopback**

The video board supports the on-board PCB trace loopback of MIPI X4 lanes and clock.

### **MIPI-TX and RX Loopback**

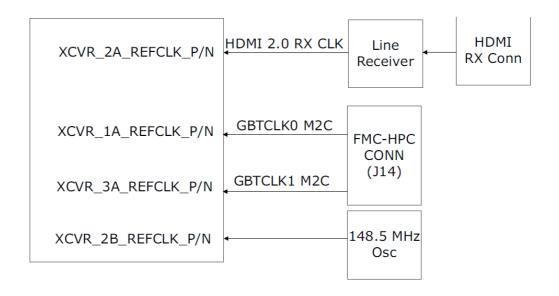

#### **Transceivers**

The PolarFire MPF300TS-1FCG1152I device has 4 XCVR blocks and each block contains 4 transceiver lanes. These lanes can be accessed through the HDMI2.0 and FMC connectors on the board. The following sections describe these blocks and the lanes used.

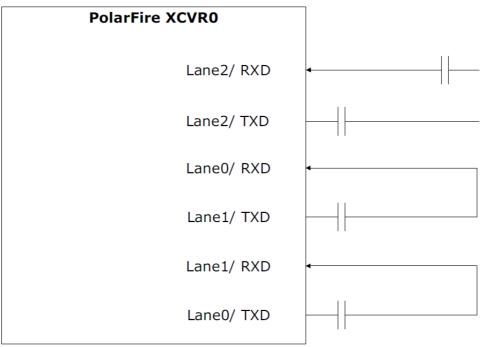

#### XCVR0 Block

Lanes 0, 1, and 2 of the XCVR0 block are looped back.

### **XCVR0 Interface**

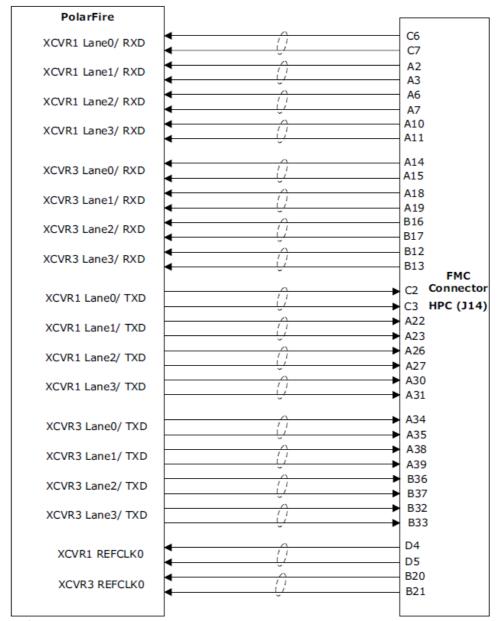

#### XCVR1 and XCVR3 Blocks

XCVR1 and XCVR3 blocks have four lanes each. These lanes are connected to the FMC HPC connector and the signals are routed on the PCB as follows:

• Lanes 0 to 7 are directly routed to the FMC HPC connector.

- TX pad > trace > via (to bottom layer) > trace > FMC HPC connector pad

- RX pad > trace > via (to Top layer) > trace > PolarFire device pad

The XCVR1 and XCVR3 reference clock is routed directly from the HPC connector to the PolarFire device.the XCVR1 and XCVR3 and their interfaces.

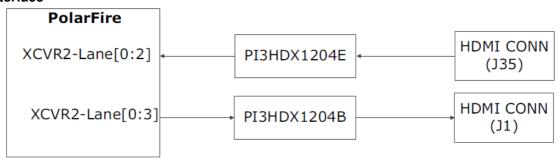

#### XCVR2 BlockXCVR1 and XCVR3 Interface

The lanes of the XCVR2 block are connected to HDMI2.0 TX and RX chips via the line drivers chips. This interface can operate up to 6 Gbps.

### **XCVR2 Interface**

#### **XCVR Reference Clock**

the clock sources for XCVR blocks.

- XCVR 1A, 3A reference clocks are sources from FMC HPC connector(J14).

- XCVR 2B reference clock is sourced from the on-board 148.5 MHz oscillator.

- XCVR 2A reference clock is sourced from the on-board HMDI2.0 TX device.

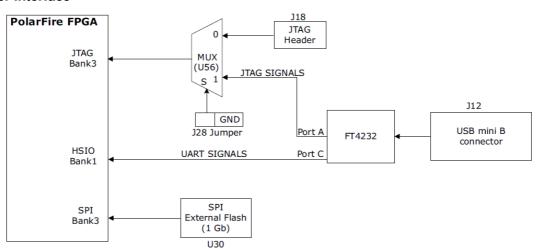

### **Programming**

The PolarFire device is programmed using the on-board FlashPro5 programmer or through the JTAG Header. For more information about programming, see the video board schematics.

The following section describes the FTDI and JTAG Header programming schemes used on the board.

#### **FTDI and JTAG Header Scheme**

The PolarFire device can be programmed using the on-board JTAG Header or FTDI. By default, the FTDI programming mode is enabled. The programming mode can be changed based on the Jumper settings. For more information.

The following figure shows how the JTAG Header interfaces with the PolarFire Device.

#### **JTAG Header Interface**

**Note:** By default, the FTDI programming mode is enabled. Remove J28 jumper to enable programming through JTAG header.

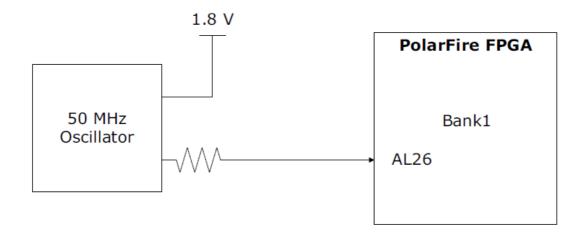

#### 50 MHz Oscillator

A 50 MHz clock oscillator with an accuracy of +/-50 ppm is available on the board. This clock oscillator is connected to the FPGA fabric to provide a system reference clock. An on-chip PolarFire PLL can be configured to generate a wide range of high-precision clock frequencies.

The package and pin details of the 50 MHz oscillator are as follows:

Pin Number: AL26

Pin Name: HSIO72PB1/CCC\_NE\_CLKIN\_N\_11 shows the 50 MHz clock oscillator interface.

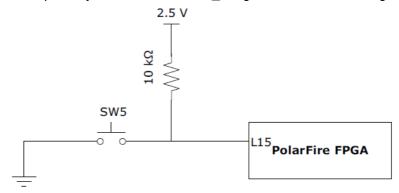

### **Device Reset**

As shown in Figure 17, page 16, DEVRST\_N (SW5 push button) is an input-only reset switch that allows assertion of a full reset of the chip at any time. The DEVRST\_N signal is an active-low signal.

#### **User Reset**

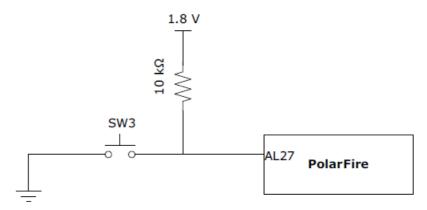

As shown in Figure 18, page 16, the user reset (SW3 push button) is an input-only reset switch that allows assertion of a reset of the fabric logic.

### **User Interface**

LEDs and push-button switches are available on the board for the user interface.

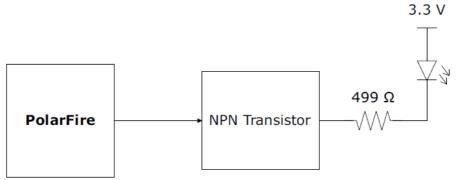

### **User LEDs**

Four active-high LEDs are connected to the PolarFire device. Table 7, page 17 lists the on-board label of these switches, the associated PolarFire pin number, name, and Bank.

| Label On<br>Board | PolarFire Pin<br>Number | PolarFire Pin Name | PolarFire Bank |

|-------------------|-------------------------|--------------------|----------------|

| LED1              | G17                     | HSIO37NB6          | Bank 6         |

| LED2              | K23                     | HSIO54PB6          | Bank 6         |

| LED3              | L23                     | HSIO54NB6          | Bank 6         |

| LED4              | B25                     | HSIO68NB6/DQS      | Bank 6         |

**User LED Interface**

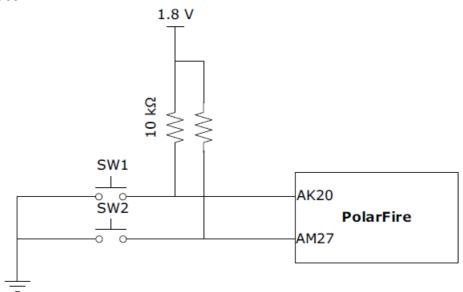

### **Push-Button Switches**

Two push-button tactile switches are connected to the PolarFire device. Table 8, page 17 lists the on-board label of these switches, the associated PolarFire pin number, name, and Bank.

| Label On<br>Board | PolarFire Pin Number | PolarFire Pin Name | PolarFire Bank |

|-------------------|----------------------|--------------------|----------------|

| SW1               | AK20                 | HSIO98NB1          | Bank 1         |

| SW2               | AM27                 | HSIO73NB1          | Bank 1         |

### **Push-Button Interface**

### Slide Switches (DPDT)

The SW4 slide switch powers the device ON or OFF.

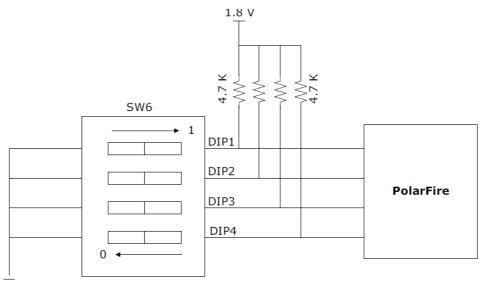

### **DIP Switches (SPST)**

The SW6 DIP switch includes 8 connections to the PolarFire device. Table 9, page 18 lists on-board label of these switches, the associated PolarFire pin number, name, and Bank.

| Label On<br>Board | PolarFire Pin<br>Number | PolarFire Pin Name | PolarFire<br>Bank |

|-------------------|-------------------------|--------------------|-------------------|

| DIP1              | AH22                    | HSIO99PB1/DQS      | Bank1             |

| DIP2              | AJ21                    | HSIO99NB1/DQS      | Bank1             |

| DIP3              | AG21                    | HSIO100PB1         | Bank1             |

| DIP4              | AH21                    | HSIO100NB1         | Bank1             |

shows how the DIP switch interfaces with the PolarFire device.

### **DIP Switch Interface**

### **FMC HPC Connector (J14)**

An HPC (J14) FMC connector is available for future expansion of interfaces. This FMC is partially populated LPC connector1. The PolarFire Bank4, XCVR1, and XCVR3 signals are routed to the FMC connector (J14) for user application development. For more information, see the video board schematics.

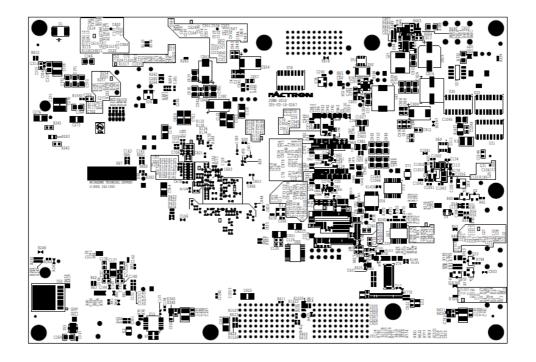

### **Board Components Placement**

Figure 22, page 19 shows the top view of the placement of board components.

### Silkscreen Top View

1. On the FMC, CLK1\_M2C\_P and CLK1\_M2C\_N pins are No Connect (NC). While selecting the LPC base FMC card to connect with MPF300-VIDEO-KIT, ensure that the CLK1\_M2C\_P and CLK1\_M2C\_N pins are not driven or used from the FMC module.

### Silkscreen Bottom View

## **Documents / Resources**

## References

- Microsemi | Semiconductor & System Solutions | Power Matters

- <u>\$\sigma\$ microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=1244033</u>

- ◆ DC-DC Converters and Voltage Regulators | Microchip Technology

Manuals+,