# Microsemi IGLOO2 HPMS DDR Bridge Configuration User Guide

Home » Microsemi » Microsemi IGLOO2 HPMS DDR Bridge Configuration User Guide 🖺

## **Contents**

- 1 Microsemi IGLOO2 HPMS DDR Bridge Configuration

- **2 Configuration Options**

- **3 Product Support**

- **4 Contacting the Customer Technical Support Center**

- **5 Documents / Resources**

- **5.1 References**

- **6 Related Posts**

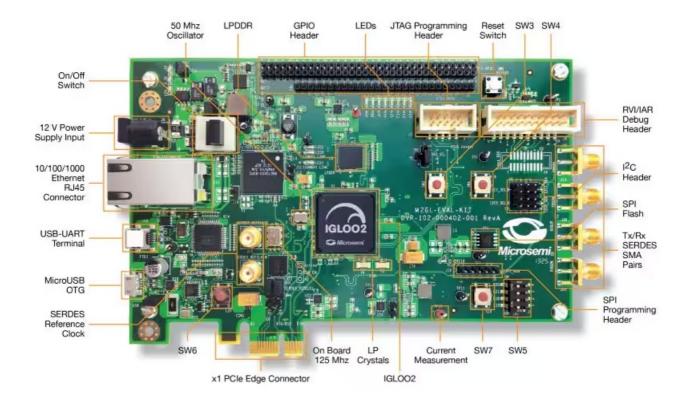

Microsemi IGLOO2 HPMS DDR Bridge Configuration

# **Configuration Options**

The HPMS DDR bridge is a data bridge between four AHB bus masters and a single AXI bus slave. It accumulates AHB writes into write combining buffers prior to bursting out to external DDR memory. It also includes read combining buffers, enabling AHB masters to efficiently read data from the external DDR memory from a local buffer. The DDR bridge optimizes reads and writes from multiple masters to a single external DDR memory. Data coherency rules between the four masters and the external DDR memory are implemented in the hardware.

The DDR bridge contains three write combining / Read buffers and one read buffer. All buffers within the DDR bridge are implemented with latches and are not subject to the single event upsets (SEU's) that SRAM exhibits. For complete details please refer to the Microsemi IGLOO2 User's Guide.

## **Write Buffer Time Out Counter**

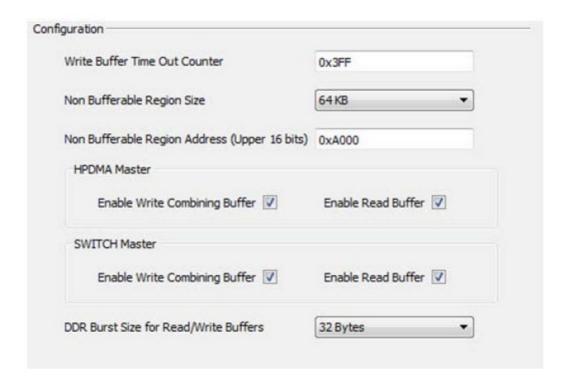

This is a 10-bit timer interface used to configure the timeout register in the write buffer module (Figure 1). Once the timer reaches the timeout value, a flush request is generated by the flush controller and if the response has been received for a previous write request from the write arbiter, this request is posted to the write arbiter. This register is common for all buffers.

- Non-Bufferable Region Size Use this option to set the size of the non-bufferable address region.

- Non-Bufferable Region Address (Upper 16 bits)- Use this option to set the base address of a non-bufferable address region. Bits [15:(N 1)] of this signal are compared with AHB address [31:(N + 15)] to check whether the address is in a non-bufferable region. The value of N depends on the non-bufferable region size, so the base address is defined according to the DDRB\_NB\_SZ register that holds the non-bufferable region size value defined in this configurator.

- Enable Write Combining Buffer Use these options to enable the Write Combining Buffers for the HPDMA and AHB Bus (SWITCH) Masters.

- DDR Burst Size For Read/Write Buffers Use this to configure the write buffer and read buffer size as per DDR burst size. Buffers can be configured to 16-byte or 32-byte size.

## **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

#### **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 408.643.6913

## **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

## **Technical Support**

Visit the Customer Support website (<u>www.microsemi.com/soc/support/search/default.aspx</u>) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

#### Website

You can browse a variety of technical and non-technical information on the SoC home page, at <a href="https://www.microsemi.com/soc">www.microsemi.com/soc</a>.

# **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

## **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request. The technical support email address is <a href="mailto:soc tech@microsemi.com">soc tech@microsemi.com</a>.

# My Cases

Microsemi SoC Products Group customers may submit and track technical cases online by going to My Cases.

### Outside the U.S.

Customers needing assistance outside the US time zones can either contact technical support via email (<a href="mailto:soc\_tech@microsemi.com">soc\_tech@microsemi.com</a>) or contact a local sales office. Sales office listings can be found at <a href="https://www.microsemi.com/soc/company/contact/default.aspx">www.microsemi.com/soc/company/contact/default.aspx</a>.

## **ITAR Technical Support**

For technical support on RH and RT FPGAs that are regulated by International Traffic in Arms Regulations (ITAR), contact us via <a href="mailto:soc\_tech\_itar@microsemi.com">soc\_tech\_itar@microsemi.com</a>. Alternatively, within My Cases, select Yes in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.

Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed-signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at <a href="https://www.microsemi.com">www.microsemi.com</a>.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100

**Sales**: +1 (949) 380-6136 **Fax**: +1 (949) 215-4996

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **Documents / Resources**

Microsemi IGLOO2 HPMS DDR Bridge Configuration [pdf] User Guide IGLOO2 HPMS DDR Bridge Configuration, IGLOO2, HPMS DDR Bridge Configuration, Bridge Configuration, Configuration

# References

- • Microsemi | Semiconductor & System Solutions | Power Matters

- <u>□ Libero® SoC Design Suite Versions 2023.1 to 12.0 | Microchip Technology</u>

- <u>Libero® SoC Design Suite Versions 2022.3 to 12.0 | Microchip Technology</u>

- Libero® SoC Design Suite Versions 2023.1 to 12.0 | Microchip Technology

Manuals+,