# Microsemi HB0794 CoreReset\_PF v2.3 Instructions

Home » Microsemi » Microsemi HB0794 CoreReset\_PF v2.3 Instructions

Microsemi HB0794 CoreReset\_PF v2.3 Instructions

#### **Contents**

- **1 Revision History**

- 2 Introduction

- 3 Design Description

- **4 Tool Flow**

- 5 Documents /

Resources

- **5.1 References**

- **6 Related Posts**

## **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### **Revision 3.0**

Added PolarFire® SoC support.

### **Revision 2.0**

Updated for CoreReset PF v2.2.

## **Revision 1.0**

Revision 1.0 was the first publication of this document. Created for CoreReset\_PF v2.1

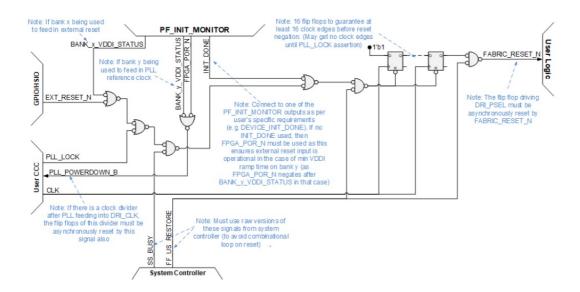

#### Introduction

CoreReset\_PF allows synchronization of the resets to the user-specified clock domain to which each reset is feeded, so that, when assertion is asynchronous, negation is synchronous to the clock. CoreReset\_PF block

diagram is as shown in Figure 1, page 2.

Figure 1 • CoreReset\_PF Block Diagram

## **Key Features**

- Generates a reset, which is asserted asynchronously by one of multiple potential sources and which negates synchronously to a specified clock. This ensures that the recovery time of downstream logic is met and that all flip flops come out of reset in the same clock period.

- Multiple reset can be used such as external gpio, phase lock loop lock or init done in conjunction with the master reset from the system controller (through CORESYSSERVICES\_PF).

#### **Core Version**

This handbook is for CoreReset\_PF version 2.3.

#### **Supported Families**

- PolarFire® SoC

- PolarFire®

#### **Utilization and Performance**

CoreReset\_PF has been implemented for the PolarFire and PolarFire SoC device families. A summary of the implementation data for CoreReset\_PF is listed in Table 1,

## **Design Description**

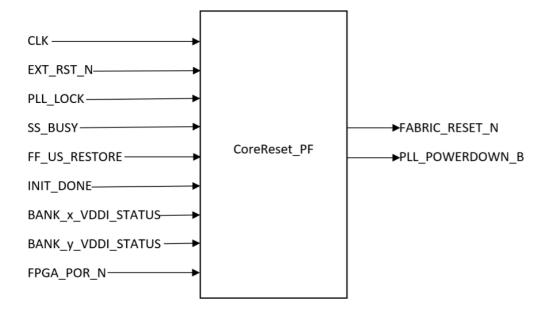

#### I/O Signals

The port signals for the CoreReset PF macro are as shown in Figure 2, page 4 and defined in Table 2,

Figure 2 · CoreReset PF I/O Signal Diagram

#### **Tool Flow**

#### Licensing

CoreReset\_PF is license free.

#### **RTL**

Complete RTL source code is provided for the core and testbenches.

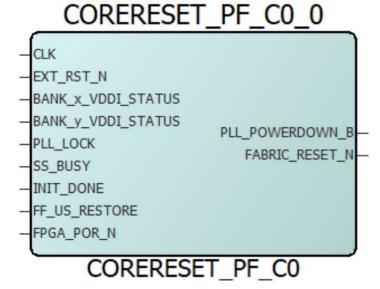

#### **SmartDesign**

CoreReset\_PF is preinstalled in the SmartDesign IP Deployment design environment. The core should be configured using the configuration GUI within SmartDesign, as shown in Figure 3, page 6. To know how to create SmartDesign project using the IP cores, refer to Libero SoC documents page and use the latest SmartDesign user guide.

Figure 3 • CoreReset\_PF Full I/O View

#### **Simulation Flows**

The user testbench for CoreReset\_PF is included in all releases. To run simulations, select the User Testbench flow within the SmartDesign CoreReset\_PF configuration GUI, right-click the canvas, and select Generate Design. When SmartDesign generates the design files, it will install the user testbench files. To run the user testbench, Set the design root to the CoreReset\_PF instantiation in the LiberoSoC design hierarchy pane and click the Simulation icon in the Libero SoC Design Flow window. This will invoke ModelSim® and automatically run the

simulation.

#### Synthesis in Libero SoC

After setting the design root appropriately for your design, click the Synthesis icon in the Libero SoC. The Synthesis window appears, displaying the Synplicity® project. Set Synplicity to use the Verilog 2001 standard if Verilog is being used. To run Synthesis, click the Run icon.

## Place-and-Route in Libero SoC

After setting the design root appropriately for the design, and after running Synthesis, click the Layout icon in the Libero SoC software to invoke Designer. CoreReset\_PF requires no special place-and-route settings.

## **Documents / Resources**

#### References

• Microsemi | Semiconductor & System Solutions | Power Matters

Manuals+,