# **MICROCHIP Synopsys Synplify Pro ME User Manual**

Home » MICROCHIP » MICROCHIP Synopsys Synplify Pro ME User Manual

#### **Contents**

- 1 MICROCHIP Synopsys Synplify Pro ME

- **2 Product Usage Instructions**

- 3 Introduction to Synopsys Synplify (Ask a Question)

- 4 Licensing Download Installation (Ask a Question)

- 5 Warnings/Error Messages (Ask a Question)

- 6 Attributes/Directives (Ask a Question)

- 7 RAM Inference (Ask a Question)

- 8 Area or Quality of Results (Ask a Question)

- 9 Revision History (Ask a Question)

- 10 Documents / Resources

- 10.1 References

- 11 Related Posts

**MICROCHIP Synopsys Synplify Pro ME**

# Introduction to Synopsys Synplify (Ask a Question)

This document provides answers to frequently asked questions (FAQs) related to the Synopsys® Synplify® tool, and its integration with Microchip's Libero® SoC Design Suite. This document covers topics such as licensing, error messages and synthesis optimization. This document is intended to help users to effectively utilize Synplify for FPGA designs. It explains the supported HDL languages, licensing requirements and how to troubleshoot common issues. Additionally, the document addresses specific queries regarding RAM inference, attributes, directives and techniques to improve design area and quality of results.

#### **Specifications**

· Product Name: Synopsys Synplify

Product Type: Logic Synthesis Tool

Supported Devices: FPGA and CPLD

Supported Languages: Verilog and VHDL

• Additional Features: FSM explorer, FSM viewer, Register re-timing, Gated clock conversion

# **Product Usage Instructions**

#### Overview

Synopsys Synplify is a logic synthesis tool designed for FPGA and CPLD devices. It accepts high-level input in Verilog and VHDL languages and converts designs into small and high-performance netlists

#### **Design Input**

Write your design in Verilog or VHDL using industry-standard syntax.

#### **Synthesis Process**

Use Synplify or Synplify Pro to run the synthesis process on your design. The tool will optimize the design for the target FPGA or CPLD device.

#### **Output Verification**

After synthesis, the tool generates VHDL and Verilog netlists.

You can simulate these netlists to verify the functionality of your design.

#### **FAQ**

#### What does Synplify do?

Synplify and Synplify Pro are logic synthesis tools for FPGA and CPLD devices. Synplify Pro offers advanced features for managing and optimizing complex FPGAs.

#### Introduction to Synopsys Synplify (Ask a Question)

This document provides answers to frequently asked questions (FAQs) related to the Synopsys® Synplify® tool, and its integration with Microchip's Libero® SoC Design Suite. This document covers topics such as licensing, error messages and synthesis optimization. This document is intended to help users to effectively utilize Synplify for FPGA designs. It explains the supported HDL languages, licensing requirements and how to troubleshoot

common issues. Additionally, the document addresses specific queries regarding RAM inference, attributes, directives and techniques to improve design area and quality of results.

• What does Synplify do? (Ask a Question)

Synplify and Synplify Pro products are logic synthesis tools for Field Programmable Gate Array (FPGA) and Complex Programmable Logic Device (CPLD). The Synplify Pro tool is an advanced version of the Synplify tool, with many additional features for managing and optimizing complex FPGAs. Some additional features available in Synplify Pro are Finite State Machine (FSM) explorer, FSM viewer, Register re-timing and gated clock conversion.

These tools accept high-level input, written in industry-standard hardware description languages (Verilog and VHDL), and using the Synplicity Behavior Extracting Synthesis Technology (BEST) algorithms. They convert the designs into small and high-performance design netlists for popular technology vendors. The tools write VHDL and Verilog netlists after synthesis, which can be simulated to verify functionality.

- Which HDL language does Synplify support? (Ask a Question)

Verilog 95, Verilog 2001, System Verilog IEEE® (P1800) standard, VHDL 2008, and VHDL 93 are supported in Synplify. For information on different language constructs, see Synplify Pro for Microchip Language Support Reference Manual.

- Will Synplify accept manual instantiations of Microchip macros? (Ask a Question)

Yes, Synplify contains built-in macro libraries for all of Microchip's hard macros including logic gates, counters, flip-flops and I/Os. You can manually instantiate these macros in your Verilog and VHDL designs, and Synplify passes them through to the output netlist.

- How does Synplify work with Microchip tools? (Ask a Question)

The Synopsys Synplify Pro® Microchip Edition (ME) synthesis tool is integrated into Libero, which enables you to target and fully optimize an HDL design for any Microchip device. As with all other Libero tools, you can launch Synplify Pro ME directly from the Libero Project Manager.

Synplify Pro ME is the standard offering in Libero editions. Synplify Pro ME is launched by invoking the executable specific in the Libero tool profile.

# Licensing Download Installation (Ask a Question)

This section answers the queries related to the license installing and download procedure of Synplify in Libero.

- Where can I download the latest Synplify release? (Ask a Question)

Synplify is a part of Libero download and the standalone installation link is Microchip Direct.

- 2. Which version of Synplify is released with the latest Libero? (Ask a Question) For the list of Synplify versions released with Libero, see Synplify Pro® ME.

- 3. How do I upgrade to the latest version of Synplify and use it in the Libero Project Manager? (Ask a Question) Download and install the latest version of Synplify from the Microchip or Synopsys website, and change the synthesis settings in the Libero Project Manager tool profile from the Libero Project > Profiles menu.

- Do I need a separate license to run Synplify in Libero? (Ask a Question)

No, all Libero licenses except for the Libero-Standalone license includes a license for the Synplify software.

- Where and how do I get the license for Synplify? (Ask a Question)

To apply for a free license, see the Licensing Page and click the Software Licenses and Registration System

link. Enter the required information, including the volume ID of your C drive. Make sure to apply with your C drive, even if that is not the drive you intend to install the software on. For paid licenses, contact the local Microchip Sales Office.

- 6. Why can I not run Synplify in batch mode? What license does it require? (Ask a Question)

From command prompt, go to the directory where the project files are located and type the following.

- For Libero IDE: synplify\_pro -batch -licensetype synplifypro\_actel -log synpl.log TopCoreEDAC\_syn.prj

- For Libero SoC: synplify\_pro -batch -licensetype synplifypro\_actel -log synpl.log asdasd\_syn.tcl

Note: You must have a silver license to run Synplify in batch mode. Generate your free silver license at Microchip portal.

#### Why is my Synplify license not working? (Ask a Question)

#### The steps to check the functioning of the license are as follows:

- 1. Check if the license has expired.

- 2. Check if the LM\_LICENSE\_FILE is set correctly as a windows user environment variable, whichpoints to the location of the Libero License.dat file.

- 3. Check whether the Libero IDE tool profile is set to Synplify Pro and the Synplify license feature is enabled in your license file.

- 4. Look for the "synplifypro\_actel" feature line in the license.dat file: INCREMENT synplifypro\_actel snpslmd 2016.09 21-nov-2017 uncounted \ 4E4905A56595B143FFF4 VENDOR\_STRING=^1+S \ HOSTID=DISK\_SERIAL\_NUM=ec4e7c14 ISSUED=21-nov-2016 ck=232 \ SN=TK:4878-0:1009744:181759 START=21-nov-2016

- 5. 5. After locating the feature line, make sure that the HostID is correct for the computer you are using.

# Can I use the Synplify license obtained from Microchip (Ask a Question)

No, if you received a Synplify license from Microchip, you will only be able to run Synplify ME.

Is Synplify Pro Synthesis tool supported in all the Libero licenses? (Ask a Question)

Synplify Pro Synthesis tool is not supported in all the License types. For more information about licensing, see Licensing Page.

# Warnings/Error Messages (Ask a Question)

This section provides information about various error messages that appear during the installation procedure.

1. Warning: Top entity isn't set yet! (Ask a Question)

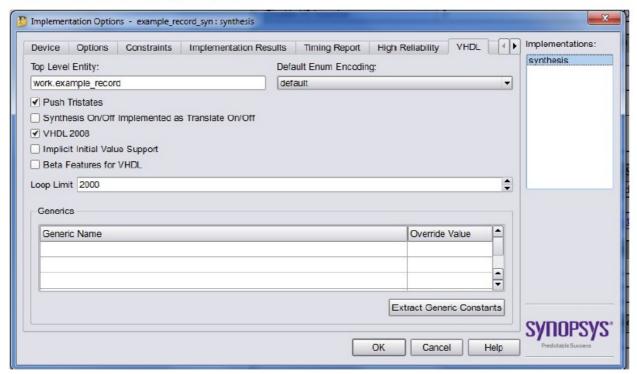

This warning message means that Synplify could not identify the top entity in your design, due to design complexity. You need to manually specify the top entity name in Synplify implementation options. The following figure shows an example. Figure 2-1. Example To Specify Top Entity Name

Figure 2-1. Example To Specify Top Entity Name

- 2. Warnings on Register Pruning (Ask a Question) Synplify optimizes the design by pruning unused, duplicate registers, nets or blocks. You can manually control the amount of auto optimization by applying the following directives:

- \*syn\_keep—ensures that if a wire is kept during synthesis and hat there are no optimizations across the wire. This directive is usually used to break unwanted optimizations and to ensure manually created replications. It works only on nets and combinational logic.

- \*syn\_preserve—ensures that registers are not optimized away.

- \*syn\_noprune—ensures that a black box is not optimized away when its outputs are unused (that is, when its outputs do not drive any logic).

For more information about optimization control and Synplify documents, see Synplify Pro for Microchip User Guide.

- 3. @W: FP101 |The design has eight instantiated global buffers but allowed is only six (Ask a Question) @W: FP103— User can use syn\_global\_buffers to increase the allowed global clock buffers to maximum of 18. The warnings are created because Synplify identified more than six global macros instantiated in the design. The default maximum number of global nets allowed in Synplify is currently set to six.

- So when the tool tries to use more than six for this design, it generates an error. You can manually increase the default limit to eight (up to 18 in IGLOO/e, ProASIC3/E and Fusion, and upto eight and 16 depending on the SmartFusion 2 and IGLOO 2 device) by adding a synthesis attribute called syn\_global\_buffers.

For example:

- module top (clk1, clk2, d1, d2, q1, q2, reset) /\* synthesis syn\_global\_buffers = 8 \*/; ......or architecture behave of top is attribute syn\_global\_buffers : integer; attribute syn\_global\_buffers of behave : architecture is 8; ...... For more information, see Synplify Pro for Microchip User Guide.

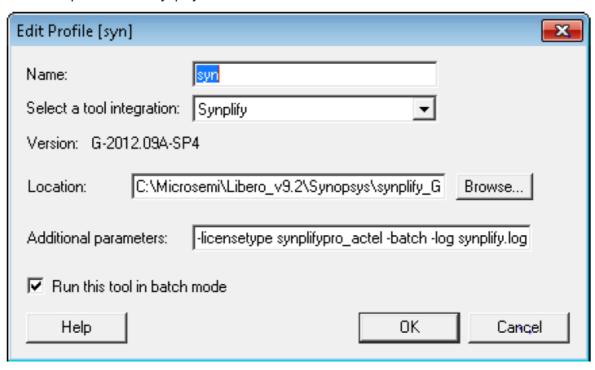

- 4. Error: The profile for tool Synplify is interactive and you are running in batch mode: this tool cannot be invoked (Ask a Question)

- You must have a silver license to run Synplify in batch mode. Contact the local Microchip sales representative to purchase a silver license. You must ensure that the Libero Synthesis tool profile is configured to launch Synplify in batch mode, if you are invoking Synplify from within Libero instead of directly from the command

prompt. The following figure shows how to invoke Synplify from within Libero.

Figure 2-2. Example to Invoke Synplify from Within Libero

- 5. @E: CG103: "C:\PATH\code.vhd":12:13:12:13|Expecting expression (Ask a Question)

- @E: CD488: "C:\PATH\code.vhd":14:11:14:11—EOF in string literal

A comment following anything other than a semicolon or a new line is not allowed in VHDL. Two hyphens mark the start of a comment, which is ignored by the VHDL compiler. A comment can be on a separate line or at the end of the line. The error is due to comments in some other part of the VHDL code.

- 6. @E: Internal Error in m\_proasic.exe (Ask a Question)

This is not an expected tool behavior. For more information, contact Synopsys Synplify support team, or Microchip Technical Support team if you do not have a Synopsys Support Account.

- 7. Why has my logic block disappeared after synthesis? (Ask a Question) Synplify optimizes away any logic block that does not have any external output port.

#### Attributes/Directives (Ask a Question)

This section answers the queries related to attributes and directives.

- 1. How do I turn off automatic clock buffer usage in Synplify? (Ask a Question)

- To turn off automatic clock buffering for nets or specific input ports, use the syn\_noclockbuf attribute. Set the Boolean value to one or true to turn off automatic clock buffering.

- You can attach this attribute to a hard architecture or module whose hierarchy will not be dissolvedduring optimization of a port, or net.

- For more information about usage of the attribute, see the Synplify Pro for Microchip User Guide.

- 2. Which attribute is used for preserving registers? (Ask a Question) syn\_preserve directive is used for preserving registers. For more information about this attribute, see the Synplify Pro for Microchip User Guide.

- 3. Does syn\_radhardlevel attribute support IGLOO and Fusion families? (Ask a Question) No, syn\_radhardlevel attribute is not supported in IGLOO® and Fusion families.

- 4. How do I disable serial optimization in Synplify? (Ask a Question)

Use syn\_preserve directive to disable serial optimization in Synplify.

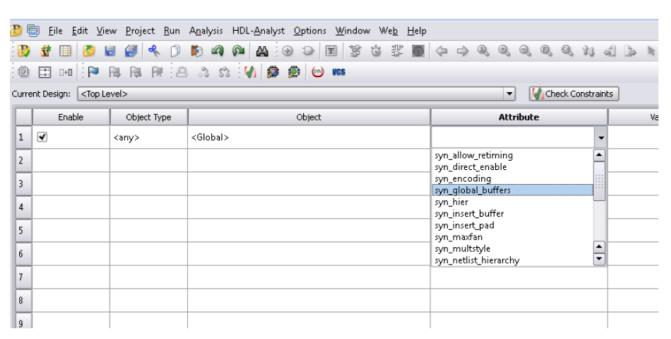

5. How can I add an attribute in Synplify? (Ask a Question)

#### Perform the following steps to add an attribute in Synplify:

- 1. Launch Synplify from the Libero Project Manager.

- 2. Click on File > New > FPGA Design Constraints.

- 3. Click the Attributes tab at the bottom of the spreadsheet.

- 4. Double-click on any of the attribute cells in the spreadsheet. You should see a drop-down menu with many attributes listed. Select any of them, and fill in the required fields accordingly, as shown in the following figure.

5.

Save the files and close the Scope Editor after completing the task.

- How do I insert a clock buffer in my design? (Ask a Question)

Use syn\_insert\_buffer attribute to insert a clock buffer. The synthesis tool inserts a clock buffer according to the vendor-specific values you specify. The attribute can be applied on instances.

For more information about the usage of the attribute, see the Synplify Pro for Microchip User Guide.

- How do I increase the number of global clock buffers used in my design? (Ask a Question)

Use syn\_global\_buffers attribute in the SCOPE to specify the number of global buffers to be used in a design. It is an integer between 0 and 18. For more information about this attribute, seethe Synplify Pro for Microchip User Guide.

- Is there any way to preserve my logic if the output ports are not used in my design? (Ask a Question)

Use syn\_noprune attribute to preserve the logic if the output ports are not used in the design. For example:

module syn\_noprune (a,b,c,d,x,y); /\* synthesis syn\_noprune=1 \*/;

For more information about this attribute, see the Synplify Pro for Microchip User Guide.

- Why is synthesis optimizing my high fanout net to buffered clock? (Ask a Question)

Use syn\_maxfan to override the default (global) fanout guide for an individual input port, net, or register output.

Set the default fanout guide for a design through the device panel on the Implementation Options dialog box, or with the set\_option -fanout\_limit command in the

project file. Use the syn maxfan attribute to specify a different (local) value for individual I/Os.

For more information about this attribute, see the Synplify Pro for Microchip User Guide.

• How do I use the syn\_encoding attribute for an FSM design? (Ask a Question)

The syn\_encoding attribute overrides the default FSM compiler encoding for a state machine.

This attribute takes effect only when FSM compiler is enabled. Use syn\_encoding when you want to disable the FSM compiler globally, but there are a select number of state registers in your design that you want to be extracted. In this case, use this attribute with the syn\_state\_machine directive on for just those specific registers.

For more information about this attribute, see the Synplify Pro for Microchip User Guide.

Why Synplify generates a netlist that exceeds the maximum fanout of device, causing the netlist to fail compile?

(Ask a Question)

A CC macro, available for Antifuse families, is a flip-flop element built using two C-cells. A net driving the CLK or CLR port of a CC macro is driving two cells. The hard fan-out limit on certain nets does not achieve the desired results because it fails to take this net doubling effect into account.

Include the syn\_maxfan attribute in the RTL code to force Synplify to generate a valid netlist.

Reduce the max fanout limit value by one for every CC macro driven by the net. For example, set the syn maxfan limit to 12 for a net that is driving CC macros to keep the fanout at 24 or less.

# **RAM Inference (Ask a Question)**

This section answers the queries related to the RAM inference Synplify support for Microchip product families.

- Which Microchip families do Synplify support for RAM inference? (Ask a Question) Synplify supports the Microchip ProASIC®, ProASIC PLUS®, ProASIC3®,SmartFusion® 2, IGLOO® 2 and RTG4™ families in generating both single and dual-port RAMs.

- 2. Is RAM inference ON by default? (Ask a Question)

Yes, the synthesis tool automatically infers RAM.

3. How can I turn off RAM inference in Symplify? (Ask a Question)

Use syn ramstyle attribute and set its value to registers.

For more information, see the Synopsys Synplify Pro for Microchip Reference Manual.

4. How do I make Synplify infer embedded RAM/ROM? (Ask a Question)

Use syn\_ramstyle attribute and set its value to block\_ram or LSRAM and USRAM for SmartFusion 2 and IGLOO 2 devices.

For more information, see the Synopsys Synplify Pro for Microchip Reference Manual.

5. I cannot compile an existing design in a newer version of designer. (Ask a Question)

There could be possible RAM/PLL configuration change. Regenerate your RAM/PLL by opening the core configuration options from the Catalog in the Libero Project Manager, and resynthesize, compile, or layout.

# Area or Quality of Results (Ask a Question)

This section answers the queries related to the area or quality usage for Synplify.

Why does area usage increase in the new version of Synplify? (Ask a Question)

Synplify is designed to achieve better timing results in every new version. Unfortunately, the tradeoff is often an area increase.

If the timing requirement is achieved for the design, and the remaining task is to fit the design in a specific die, following are the methods:

- 1. Increase Fanout limit to reduce buffer replication.

- 2. Change global frequency settings to relax the timing requirement.

- 3. Turn on resource sharing (design specific) to optimize the design.

# What kind of area improvement technique is available in Synplify? (Ask a Question) Perform the following techniques to improve area in Synplify:

- 1. Increase the fanout limit when you set the implementation options. A higher limit means less replicated logic and fewer buffers inserted during synthesis, and a consequently smaller area. In addition, as place-and-route tools typically buffer high fanout nets, there is no need for excessive buffering during synthesis.

- 2. Check the Resource Sharing option when you set implementation options. With this option checked, the software shares hardware resources like adders, multipliers and counters wherever possible, and minimizes area.

- 3. For designs with large FSMs, use the gray or sequential encoding styles, because they typically use the smallest area.

- 4. If you are mapping into a CPLD and do not meet area requirements, set the default encoding style for FSMs to sequential instead of one hot.

#### How do I disable area optimization? (Ask a Question)

The optimization for timing is often under the expense of area. There is no specific way to disable area optimization. Perform the following to improve timing and thereby increase area utilization:

- 1. Enable re-timing option.

- 2. Enable Pipelining option.

- 3. Use realistic design constraints, about 10 to 15 percent of the real goal.

- 4. Select a balanced fanout constraint.

For more information about the optimization for timing, see Synplify Pro for Microchip User Guide.

#### How do I disable sequential optimization? (Ask a Question)

There is no explicit button or checkbox to disable sequential optimization. This is because there are different types of sequential optimizations that are performed by Synplify.

For more information about the options for disabling optimization, see Synplify Pro for Microchip Reference Manual .

For example, following are some options to disable optimization.

- Disable the FSM compiler.

- Use the syn\_preserve directive to keep registers in certain cases.

Important: The Project Manager overwrites the Synthesis PRJ file every time you invoke synthesis when choosing this option.

- Which family is TMR supported through Synplify? (Ask a Question)

- It is supported on Microchip ProASIC3/E, SmartFusion 2, and IGLOO 2 devices as well as Microchip's

- Radiation Tolerant (RT) and Radiation Hardened (RH) devices. You can also get the Triple Module

- Redundancy (TMR) setting to work for Microchip's older Antifuse device families. However, it is not supported in the commercial AX device family.

- Note: In Microchip's RTAX device family, better TMR support is available through hardware itself.

- For Axcelerator RT devices, the TMR is built into the silicon making soft TMR through the Synthesis tool unnecessary for sequential logic.

- Why is TMR macro working in SX, but not in AX family? (Ask a Question)

- There is no software TMR support in Synplify synthesis for the commercial Axcelerator family, but it is available for the SX family. If you are using RTAXS devices, the TMR is built into the hardware/ device for the sequential flip- flops.

- How can I enable TMR for a SX-A device? (Ask a Question)

- For the SX-A device family, in the Synplify software, you need to manually import the file found in the Libero IDE Installation folder, such as:

- C:\Microsemi\Libero\_v9.2\Synopsys\synplify\_G201209ASP4\lib\actel\tmr.vhd.

- Note: The order of the files in the Synplify project is important and the top-level file must be at the bottom.

- You can click and hold the top-level file in the Synplify project and drag it below the tmr.vhd file.

- Which version of Synplify supports nano products? (Ask a Question)

- All versions of Synplify after Synplify v9.6 A support nano products.

- Which version of Synplify provides RTAX-DSP support? (Ask a Question)

- All versions included with Libero IDE v8.6 and later provide RTAX-DSP support.

- How do I create an IP core with the HDL files I have? (Ask a Question)

- Create an EDIF netlist without I/O buffer insertion. This EDIF netlist is sent to the user as an IP. The user must treat this as a black box and include it in the design.

- Nano devices have only four global clock networks. How do I set this constraint? (Ask a Question)

- Use the attribute /\* synthesis syn\_global\_buffers = 4\*/ to set the constraint.

- Why am I not seeing my new port list even after I updated the netlist?

(Ask a Question)Although the new port was added in the design, the netlist did not add a buffer to the port since there was no logic in the design which involves the port. Ports not associated with any logic in the design are not shown.

- Why is Synplify not using Global for Set/Reset signals? (Ask a Question)

- Synplify treats set/reset signals differently from clocks. Synplify global promotion always gives priority to the clock signals, even if some set/reset signals have higher fanout than clock nets.

- Manually instantiate a clkbuf to ensure that the set/reset signal is global, if you want to use the global network for these signals.

- Why does Synplify write out SDC clock constraints even for autoconstraints? (Ask a Question)

This is the default behavior in Synplify and cannot be changed. However, you can control the SDC autoconstraints by manually modifying or removing the unwanted constraints.

- Why is my internal tristate logic not synthesized correctly? (Ask a Question)

Microchip devices do not support internal tristate buffers. If Synplify does not correctly remap internal tristate signals, all internal tristates must be manually mapped to a MUX.

# **Revision History (Ask a Question)**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revisi<br>on | Date        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α            | 12/20<br>24 | <ul> <li>The following is a summary of the changes in revision A of this document.</li> <li>Migrated the document to the Microchip template.</li> <li>Updated the document number to DS60001871A from 55800015.</li> <li>All Instances of Microsemi were updated to Microchip.</li> <li>Updated sections Why can I not run Synplify in batch mode? What license does it require? a nd Error: The profile for tool Synplify is interactive and you are running in batch mode: this t ool cannot be invoked to indicate that silver license is needed to run Synplify in batch mode. The platinium license was changed to silver license.</li> </ul>                                                                                                                                                      |

| 2.0          |             | <ul> <li>The following is a summary of the changes in revision 2.0 of this document.</li> <li>All the Actel links were updated with the Microsemi links.</li> <li>All instances of IDE are removed from the licensing section. For more information, see Licensing Download Installation.</li> <li>FAQ 3.9 was added. For more information, see Is Synplify Pro Synthesis tool supported in a II the Libero licenses?</li> <li>FAQ 4.1 was updated. For more information, see Warning: Top entity isn't set yet.</li> <li>FAQ 4.4 was updated. For more information, see Error: The profile for tool Synplify is interactive and you are running in batch mode: this tool cannot be invoked.</li> <li>FAQ 5.5 was updated. For more information, see How can I add an attribute in Synplify?</li> </ul> |

| 1.0          |             | This was the first publication of the document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at <a href="www.microchip.com/support">www.microchip.com/support</a> Mention the FPGA Device Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

### **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at

https://www.microchip.com/en-us/about/legal-information/microchip-trademarks

ISBN: 979-8-3371-0303-7

#### **Legal Notice**

- This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>

- THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS

OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED

WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR

PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

- IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code

protection features of Microchip products are strictly prohibited and may violate the Digital Millennium Copyright

Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly

evolving. Microchip is committed to continuously improving the code protection features of our products.

#### **Documents / Resources**

# MICROCHIP Synopsys Synplify Pro ME [pdf] User Manual Synopsys Synplify Pro ME, Synplify Pro ME, Pro ME

#### References

- Design Help and Other Services | Microchip Technology

- Microchip Lightning Support

- W Home Page

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-07570A5F-9154-4DFB-B232-

- 2D078BBD4428&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-0B25A9E6-81F0-4804-8A41-</u>

- 5BEE5E20E2C7&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-11E3A5C9-BA42-4370-BF1E-</u>

- EDFE3AA3C75F&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-129959E1-425C-4882-B2E7-</u>

- 514DC068530F&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-21FCF715-4CC5-4BF4-98DB-</u>

- 697F7078504A&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-2B8EACCB-E1B6-41C4-8DF1-</u>

- 53E8FD928077&cover title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-2F720715-AC58-491C-B8B9-

- 20362967FBB7&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-3880A83F-94FE-4D41-BDAD-

- <u>5C0458821DF2&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo</u>

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-3B8BCCA4-4543-4318-B68B-

- <u>3D07446EECDB&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo</u>

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID4097CE59-0C0E-499D-AC164B47C48B173E&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>Microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-42450640-E515-42DE-998A-</u>

- 13BE1D1F6C12&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-4477E572-5446-4E77-B2DF-

- BEFABD5712F3&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF 39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-48889159-F76A-447C-8BD1-

- D5483AD9C71D&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-</u>

<u>39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-4A0808C4-B6D6-4D58-A340-</u>

- 5009B175D024&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>o microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-4DAC350E-1977-4E57-9D4D-</u>

- F2CA96F9D6CC&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF 39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-4F531B24-D5DA-456B-A144-

- 1422781C4F58&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-56189166-0762-4B12-967C-

- 5113AB60C8F0&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF 39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-619D0890-F157-4B7B-A2A8-

- 76BAC0462918&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID64FFAC68-AEC2-444D-B59E-

- 812A17EC0860&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-6EF5AFC4-5246-4780-9429-

- 1DD55FEFE2B1&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- <u>wmicrochipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-79B9C104-8702-4EE9-AA26-</u>

- F071BC284D02&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF 39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-7EE0324B-442D-403F-9CFC-

- 715DC3A9FE7C&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-8250A2A2-6109-4010-8669-</u>

- 975B55D2784D&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-825529D9-023E-494A-BF91-

- C5C0EEF24C08&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-852C2803-F697-4751-BE4D-

- 68EAE228B996&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF 39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-854CFFB3-AFF4-488B-9697-

- 63D9B13F4A5E&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-8E09A9EA-A9E0-4484-BFF9-</u>

- E2231A6DE854&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- <u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-8E6B4349-8FB9-457A-BD51-</u>

- F5C87F58EAF8&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-9524AA72-FAC3-4F74-95C3-

- AF90583B130E&cover title=%20%20Synopsys%20Synplify%20FAQ&tech suppo

- microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-9F5C61F6-3C79-4DD2-974C-

4AF6C088DC37&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

<u>microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF-</u>

<u>39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUID-A2F1F091-BE78-4F81-B027-</u>

DB6DF9358DF3&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

microchipsupport.force.com/s/newcase?pub\_guid=GUID-A19C4439-6698-4D3A-9DBF39D4919E1D29&pub\_lang=en-US&pub\_ver=1&pub\_type=User%20Guide&bu=fpga&tpc\_guid=GUIDA422264E-48A9-415D-9BE3132E0E1D4991&cover\_title=%20%20Synopsys%20Synplify%20FAQ&tech\_suppo

User Manual

#### Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.