# **MICROCHIP PD77728 Auto Mode Register Map Instruction Manual**

Home » MICROCHIP » MICROCHIP PD77728 Auto Mode Register Map Instruction Manual

### **Contents**

- 1 MICROCHIP PD77728 Auto Mode Register Map

- **2 Product Usage Instructions**

- 3 Introduction

- **4 Register Functionality**

- **5 Revision History**

- **6 Microchip Information**

- 7 Worldwide Sales and Service

- 8 Documents / Resources

- 8.1 References

- 9 Related Posts

**MICROCHIP PD77728 Auto Mode Register Map**

# **Product Specifications**

Model: PD77728

· Mode: Auto

• Register Map: Included

# **Product Usage Instructions**

### **Automode Operational Flowchart**

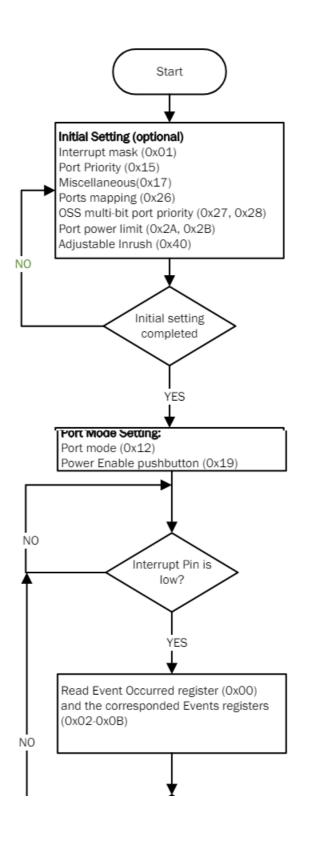

The Automode Operational Flowchart provides a step-by-step guide for utilizing the PD77728 register map:

- 1. Start the process.

- 2. Perform Initial Setting (optional) by configuring Interrupt mask (0x01), Port Priority (0x15), Miscellaneous(0x17), Ports mapping (0x26), OSS multi-bit port priority (0x27, 0x28), Port power limit (0x2A, 0x2B), and Adjustable Inrush (0x40).

- 3. Check if the Initial setting is completed.

- 4. If YES, proceed to Port Mode Setting by configuring Port mode (0x12) and Power Enable pushbutton (0x19).

- 5. If NO, check if Interrupt Pin is low.

- 6. If YES, read Event Occurred register (0x00) and the corresponding Events registers (0x02-0x0B).

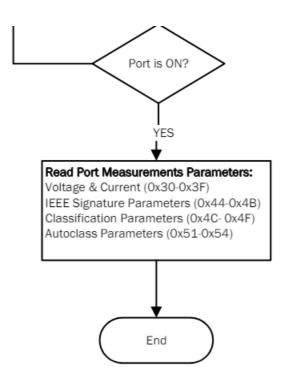

- 7. Check if the Port is ON.

- 8. If YES, read Port Measurements Parameters: Voltage & Current (0x30-0x3F), IEEE Signature Parameters (0x44-0x4B), Classification Parameters (0x4C- 0x4F), and Autoclass Parameters (0x51-0x54)

- 9. End the process.

### **Register Map Details**

The PD77728 device's register map details are listed in various tables:

- 1. Interrupts (Table 2-1)

- 2. Event (Table 2-2)

- 3. Status (Table 2-3)

### Frequently Asked Questions (FAQ)

• Q: What are the main components of the PD77728 Auto Mode Register Map?

A: The main components include Interrupts, Events, and Status registers as detailed in the register map tables.

• Q: How do I configure the Port Mode Setting in the Automode Operational Flowchart?

A: You can configure the Port Mode by setting the Port mode (0x12) and Power Enable pushbutton (0x19) as per the provided instructions.

PD77728 Auto Mode Register Map

### Introduction

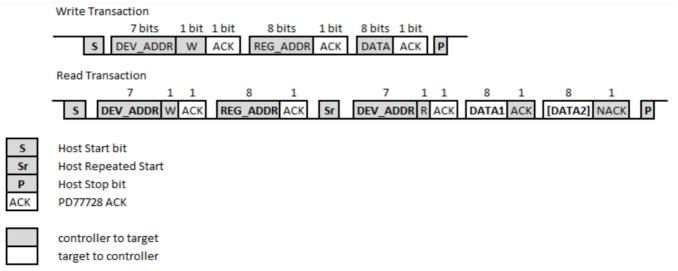

This document describes the PD77728 register map and register functionality. The PD77728 communication method is based on I2C, using register access as shown in Figure 1. Each PD77728 includes two consecutive I2C addresses (a single I2C address controls 4 ports of 2 pairs). The two I2C addresses are set by pins A1–A4, and each address is 7 bits. The PD77728 device does not require clock stretch support from the host. See the I2C section in the PD77728 Datasheet to program the I2C address.

Figure 1. I2C Transactions

1. Automode Operational Flowchart

The following figure shows the Automode Operational Flowchart of the PD77728 register map.

Figure 1-1. Automode Operational Flowchart

# 2. Register Map

The following tables list the register map details of the PD77728 device.

Table 2-1. Interrupts

| Addre<br>ss | Name        | R/W | Туре       | Bit 7                | Bit 6          | Bit 5    | Bit 4         | Bit 3                       | Bit<br>2            | Bit 1                    | Bit 0                   | Reset<br>State |

|-------------|-------------|-----|------------|----------------------|----------------|----------|---------------|-----------------------------|---------------------|--------------------------|-------------------------|----------------|

| 0x00        | Interrupt   | RO  | Syste<br>m | Suppl<br>y Eve<br>nt | Start<br>Fault | Overload | Class<br>Done | I2C<br>SR/ C<br>ap Me<br>as | Disc<br>o nn<br>ect | Pwr<br>Good<br>Even<br>t | Pwr E<br>nable<br>Event | 1000,<br>0000b |

| 0x01        | Int<br>Mask | R/W | Syste<br>m | Mask                 |                |          |               |                             |                     |                          |                         | 1000,<br>0000b |

Table 2-2. Event

| Addres<br>s | Name               | R/W | Туре | Bit 7              | Bit 6           | Bit 5              | Bit 4            | Bit 3      | Bit 2       | Bit 1     | Bit 0        | Rese<br>t Stat<br>e |

|-------------|--------------------|-----|------|--------------------|-----------------|--------------------|------------------|------------|-------------|-----------|--------------|---------------------|

| 0x02        |                    | RO  |      | Power              | Good Cl         | nange              | •                | Power      | Enable      | Change    | )            | 0000,               |

| 0x03        | Power              | CoR | 4321 | Port<br>4          | Port 3          | Port 2             | Port<br>1        | Port<br>4  | Port<br>3   | Port<br>2 | Port<br>1    | 000b                |

| 0x04        | Detection/         | RO  |      | Class              | Done            | ,                  |                  | Detect     | CC Dor      | ne        |              | 0000,               |

| 0x05        | Classificatio<br>n | CoR | 4321 | Port<br>4          | Port 3          | Port 2             | Port<br>1        | Port<br>4  | Port<br>3   | Port<br>2 | Port<br>1    | 000b                |

| 0x06        |                    | RO  |      | Underload Overload |                 |                    |                  |            |             |           | 0000,        |                     |

| 0x07        | Fault              | CoR | 4321 | Port<br>4          | Port 3          | Port 2             | Port<br>1        | Port<br>4  | Port<br>3   | Port<br>2 | Port<br>1    | 000b                |

| 0x08        |                    | RO  |      | Curre              | nt Limit Fa     | ault               |                  | Power      | Up Fau      | lt        |              | 0000,               |

| 0x09        | Start              | CoR | 4321 | Port<br>4          | Port 3          | Port 2             | Port<br>1        | Port<br>4  | Port<br>3   | Port<br>2 | Port<br>1    | 0<br>000b           |

| 0x0A        |                    | RO  |      |                    | VDD             | VDD U              |                  |            |             | oss       | DAM          |                     |

| 0x0B        | Supply             | CoR | 4321 | Over<br>Tem<br>p   | UVLO<br>Failure | VLO<br>Warnin<br>g | Vpwr<br>UVL<br>O | PCU<br>T34 | PCU<br>T1 2 | Even<br>t | RAM<br>Fault | 00xx,<br>0 000<br>b |

Table 2-3. Status

| Addres<br>s | Name                        | R/W | Туре   | Bit 7                                                            | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2        | Bit 1    | Bit 0              | Reset<br>State          |

|-------------|-----------------------------|-----|--------|------------------------------------------------------------------|-------|-------|-------|--------|--------------|----------|--------------------|-------------------------|

| 0x0C        | Detect<br>/ Class<br>Status | RO  | 1      |                                                                  |       |       |       |        |              |          |                    | 0000,<br>00<br>00b      |

| 0x0D        | Detect<br>/ Class<br>Status | RO  | 2      | Detected Class (see Table 3-8)  Detection Status (see Table 3-7) |       |       |       |        |              |          |                    | 0000,<br>00<br>00b      |

| 0x0E        | Detect<br>/ Class<br>Status | RO  | 3      | 3-8)                                                             |       |       |       | non ou | 100 (000 Tax | 3.0 0 1) | 0000,<br>00<br>00b |                         |

| 0x0F        | Detect<br>/ Class<br>Status | RO  | 4      |                                                                  |       |       |       |        |              |          |                    | 0000,<br>00<br>00b      |

|             |                             |     |        | Power                                                            | Good  |       |       | Powe   | r Enabl      | е        |                    | 0000,                   |

| 0x10        | Power                       | RO  | 4321   | Port Port Port Port 4 3 2 1 4                                    |       |       |       |        | Port<br>3    | Port 2   | Port 1             | 00b                     |

| 0x11        | Pin                         | RO  | System | em AUT O Client Address Reserved Reserved                        |       |       |       |        |              |          |                    | 0,SA[<br>4: 0],<br>0,0b |

Table 2-4. Configuration

| Addre<br>ss | Name         | R/W | Туре       | Bit 7                | Bit 6                    | Bit 5                | Bit 4               | Bit 3     | Bit 2             | Bit 1                 | Bit 0        | Reset<br>State      |

|-------------|--------------|-----|------------|----------------------|--------------------------|----------------------|---------------------|-----------|-------------------|-----------------------|--------------|---------------------|

| 0x12        | Port<br>Mode | R/W | 4321       | Port 4 N<br>ee Table | •                        | Port 3 M<br>ee Table | ,                   | Port 2 N  | Mode (s<br>e 3-9) | Port 1 M<br>e Table 3 | •            | 0000,<br>00 00<br>b |

|             |              |     |            | Port Po              | wer Prio                 | rity                 |                     | Disable   | PCUT              |                       |              | 0000,<br>00         |

| 0x15        | PWRP<br>R    | R/W | 4321       | Port 4               | Port 3                   | Port 2               | Port 1              | Port 4    | Port 3            | Port 2                | Port 1       | 00b                 |

|             |              |     |            | Interru              |                          |                      | Multi-              | Change    | 9                 |                       | 0x29         | 1100,               |

| 0x17        | Misc         | R/W | Globa<br>I | pt Pin<br>Enabl<br>e | Port S<br>ig Me<br>asure | Reserv<br>ed         | Bit<br>Priorit<br>y | CLAS<br>S | DETE<br>CT        | Reserv<br>ed          | Behav<br>ior | 00<br>00b           |

|             | Power        |     |            | Power (              | Off                      |                      |                     | Power     | On                |                       |              | 0000,<br>00         |

|             | Enabl<br>e   | wo  | 4321       | Port 4               | Port 3                   | Port 2               | Port 1              | Port 4    | Port 3            | Port 2                | Port 1       | 00b                 |

Table 2-5. General

| Addres<br>s | Name      | R/<br>W | Туре   | Bit 7                | Bit 6                  | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1   | Bit 0 | Reset State             |

|-------------|-----------|---------|--------|----------------------|------------------------|-------|-------|-------|----------|---------|-------|-------------------------|

| 0x1B        | ID        | RO      | System | Manufacture ID IC ID |                        |       |       |       |          |         |       | xxxx,x101b (<br>Note 1) |

| 0x1C        | AC/C<br>C | RO      | 4321   | AutoCl               | ass Dete               | ected |       | Conne | ction Cl | heck Re | sults | 0000,0000b              |

|             |           |         |        | Port<br>4            | Port 3   Port 2   Port |       |       |       | 4        | Port 1, | , 2   |                         |

- Note:

- 1. x = Unknown value

- Table 2-6. Specialized

| Addre<br>ss | Name                                                         | R/<br>W         | Ty<br>pe | Bit<br>7         | Bit 6    | Bit<br>5         | Bit 4  | Bit<br>3     | Bit<br>2 | Bit<br>1       | Bit 0 | Reset Sta<br>te |

|-------------|--------------------------------------------------------------|-----------------|----------|------------------|----------|------------------|--------|--------------|----------|----------------|-------|-----------------|

| 0x24        | Power on Fault                                               | RO              | 432      | Port 4           | 1        | Port :           | 2      | Port 2       | )        | Port 1         |       | 0000,0000<br>b  |

| 0x25        | 1 Ower off aut                                               | CO<br>R         | 1        | T OIL            | <b>T</b> | T OIL            | ,      | 1 Oit 2      | •        | T OIL I        |       | 0000,0000<br>b  |

| 0x26        | Ports Matrix                                                 | R/<br>W         | 432<br>1 | Port 4           | 4 rem    | Port 3           | 3 rem  | Port 2<br>ap | ? rem    | Port 1         | rema  | 1110,0100<br>b  |

| 0x27        | Multi-Bit Power Priori                                       | R/<br>W 21 Resv |          | Port 2           | 2        | Resv             |        | Port 1       |          | 0000,0000<br>b |       |                 |

| 0x28        | ty                                                           | R/<br>W         | 43       | Resv             |          | Port 4           | 4      | Resv         |          | Port 3         | 3     | 0000,0000<br>b  |

| 0x2A        | 4P Police Config                                             | R/<br>W         | 21       | 4P P             | olice Po | ort 1, 2         |        |              |          |                |       | 1111,1111<br>b  |

| 0x2B        | The Folice Corning                                           | R/<br>W         | 43       | 4P P             | olice Po | ort 3, 4         |        |              |          |                |       | 1111,1111<br>b  |

| 0x2C        | Temp. RO 432 Die Temperature 367 – 2 * (re (degrees Celsius) |                 |          |                  |          |                  | (regVa | al_decii     | mal)     |                | _     |                 |

| 0x2E        | VPWR                                                         | RO              | 432      | V <sub>PWR</sub> | LSB      |                  |        |              |          |                |       | _               |

| 0x2F        | 1 VI VVI                                                     | RO              | 1        | Rese             | rved     | V <sub>PWF</sub> | MSB    |              |          |                |       | _               |

Table 2-7. Extended Register Set—Port Parametric Measurement

| Address | Name  | R/W | Туре | Bit 7  | Bit 6   | Bit 5      | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State |

|---------|-------|-----|------|--------|---------|------------|-----------|-------|-------|-------|-------|-------------|

| 0x30    | I-LSB | RO  | 1    | Port 1 | Curren  | t LSB      |           |       |       |       |       | 0000,0000b  |

| 0x31    | I-MSB | RO  | 1    | Reser  | ved     | Port 1     | Curren    | t MSB |       |       |       | 0000,0000b  |

| 0x32    | V-LSB | RO  | 1    | Port 1 | Voltage |            | 0000,000b |       |       |       |       |             |

| 0x33    | V-MSB | RO  | 1    | Reser  | ved     |            | 0000,000b |       |       |       |       |             |

| 0x34    | I-LSB | RO  | 2    | Port 2 | Curren  | t LSB      |           |       |       |       |       | 0000,000b   |

| 0x35    | I-MSB | RO  | 2    | Reser  | ved     | Port 2     | Curren    | t MSB |       |       |       | 0000,000b   |

| 0x36    | V-LSB | RO  | 2    | Port 2 | Voltage | LSB        |           |       |       |       |       | 0000,000b   |

| 0x37    | V-MSB | RO  | 2    | Reser  |         | 0000,0000b |           |       |       |       |       |             |

| 0x38    | I-LSB | RO  | 2    | Port 3 | Curren  |            | 0000,000b |       |       |       |       |             |

| Address | Name  | R/W | Туре | Bit 7                       | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Reset State |

|---------|-------|-----|------|-----------------------------|--------|--------|--------|-------|-------|-------|-----------|-------------|

| 0x39    | I-MSB | RO  | 2    | Reser                       | ved    | Port 3 | Curren | t MSB |       |       |           | 0000,000b   |

| 0x3A    | V-LSB | RO  | 2    | Port 3 Voltage LSB          |        |        |        |       |       |       | 0000,000b |             |

| 0x3B    | V-MSB | RO  | 2    | Reserved Port 3 Voltage MSB |        |        |        |       |       |       | 0000,000b |             |

| 0x3C    | I-LSB | RO  | 2    | Port 4                      | Curren | t LSB  |        |       |       |       |           | 0000,000b   |

| 0x3D    | I-MSB | RO  | 2    | Reser                       | ved    | Port 4 | Curren | t MSB |       |       |           | 0000,0000b  |

| 0x3E    | V-LSB | RO  | 2    | Port 4 Voltage LSB          |        |        |        |       |       |       |           | 0000,000b   |

| 0x3F    | V-MSB | RO  | 2    | Reserved Port 4 Voltage MSB |        |        |        |       |       |       |           | 0000,000b   |

Table 2-8. Extended Register Set—Configuration 1

| Addre<br>ss | Name            | R/<br>W | Туре       | Bit<br>7                   | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3  | Bit<br>2  | Bit<br>1  | Bit<br>0                                           | Reset State |

|-------------|-----------------|---------|------------|----------------------------|----------|----------|----------|-----------|-----------|-----------|----------------------------------------------------|-------------|

|             | Foldback and In | R       |            |                            |          |          |          | Adjus     | table I   | nrush     |                                                    |             |

| 0x40        | rush            | W       | 4321       | Not Used                   |          |          |          | Port<br>4 | Port<br>3 | Port<br>2 | Port<br>1                                          | 0000,0000b  |

| 0x41        | Firmware        | RO      | Syst<br>em | Firmware Revision          |          |          |          |           |           |           | xxxx,xxxxb (Note 1)                                |             |

| 0x43        | Device ID       | RO      | Syst<br>em | Device ID Silicon revision |          |          |          |           |           |           | Contact Microchip for t he most updated firm ware. |             |

- Note:

- 1. x = Unknown variable

- Table 2-9. Port Signature Measurements

| Addres<br>s | Name              | R/<br>W | Typ<br>e | Bit<br>7          | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 | Reset State |

|-------------|-------------------|---------|----------|-------------------|----------|----------|----------|----------|----------|----------|----------|-------------|

| 0x44        | Detect Resistance | RO      | 4        | Port              | 1 Detec  | ction S  | ignatur  | e Resi   | stance   |          |          | 0000,000b   |

| 0x45        | Detect Resistance | RO      | 3        | Port 2            | 2 Detec  | ction S  | ignatur  | e Resi   | stance   |          |          | 0000,000b   |

| 0x46        | Detect Resistance | RO      | 2        | Port 3            | 3 Detec  | ction S  | ignatur  | e Resi   | stance   |          |          | 0000,000b   |

| 0x47        | Detect Resistance | RO      | 1        | Port 4            | 4 Detec  | ction S  | ignatur  | e Resis  | stance   |          |          | 0000,000b   |

| 0x48        | Detect Resistance | RO      | 4        | Port <sup>-</sup> | 1 Detec  | ction S  | ignatur  | e Capa   | citance  | 9        |          | 0000,000b   |

| 0x49        | Detect Resistance | RO      | 3        | Port 2            | 2 Detec  | ction S  | ignatur  | e Capa   | citance  | )        |          | 0000,000b   |

| 0x4A        | Detect Resistance | RO      | 2        | Port 3            | 3 Detec  | ction S  | ignatur  | e Capa   | citance  | )        |          | 0000,000b   |

| 0x4B        | Detect Resistance | RO      | 1        | Port 4            | 4 Detec  | ction S  | ignatur  | e Capa   | citance  | )        |          | 0000,0000b  |

Table 2-10. Assigned Class Status

| Addr<br>ess | Name     | R/<br>W | Ty<br>pe | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit 4                         |                 | Bi<br>t 3 | Bi<br>t 2 | Bi<br>t 1 | Bi<br>t 0 | Reset S<br>tate |

|-------------|----------|---------|----------|----------|----------|----------|-------------------------------|-----------------|-----------|-----------|-----------|-----------|-----------------|

| 0x4C        |          | R<br>O  | 1        | Assi     | gned (   | Class    | Port 1                        | Requested Class | s Por     | t 1       |           |           | 0000,00<br>00b  |

| 0x4D        | Assigned | R<br>O  | 2        | Assi     | gned (   | Class    | Port 2 Requested Class Port 2 |                 |           |           |           |           | 0000,00<br>00b  |

| 0x4E        | Class    | R<br>O  | 3        | Assi     | gned (   | Class    | Port 3                        | Requested Class | s Por     | t 3       |           |           | 0000,00<br>00b  |

| 0x4F        |          | R<br>O  | 4        | Assi     | gned (   | Class    | Port 4                        | Requested Class | s Por     | t 4       |           |           | 0000,00<br>00b  |

Table 2-11. AutoClass Configuration and Status

| Addr<br>ess | Name        | R/<br>W | Ty<br>pe | Bit<br>7 | Bit 6 |                  | Bi<br>t 5 | Bi<br>t 4 | Bi<br>t 3 | Bi<br>t 2 | Bi<br>t 1 | Bi<br>t 0 | Reset S<br>tate |

|-------------|-------------|---------|----------|----------|-------|------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------|

| 0x51        |             | R<br>O  | 1        | Don      | е     | Calculated Auto0 | Class     | Pow       | er Po     | ort 1     |           |           | 0000,00<br>00b  |

| 0x52        | AutoClass P | R<br>O  | 2        | Don      | е     | Calculated Auto0 | Class     | Pow       | er Po     | ort 2     |           |           | 0000,00<br>00b  |

| 0x53        | ower        | R<br>O  | 3        | Don      | е     | Calculated Auto0 | Class     | Pow       | er Po     | ort 3     |           |           | 0000,00<br>00b  |

| 0x54        |             | R<br>O  | 4        | Don      | е     | Calculated Auto0 | Class     | Pow       | er Po     | ort 4     |           |           | 0000,00<br>00b  |

# **Register Functionality**

The address of each register represents a byte of data.

The register has the following modes:

- RO: Read only, this register can be read by the host (this register cannot be set by the host).

- R/W: Read/Write, this register can be read and set by the host.

- COR: Clear On Read, this register can be read only by the host (once it is read, its value is reset).

- Type:

- System: The register represents functionality of the whole I2C address, linked to this register.

- Port: The register represents functionality of a port or a few ports, the related port number is written in the cell.

Event Registers (0x00 to 0x0B) 0x00—Interrupt Event

- Each bit represents a system event. When the bit is equal to 1, it indicates that an event has occurred.

- The following table lists the events associated with the register.

- Table 3-1. System Event

| Bi<br>t | Event Name                                 | Event Description                                                                                                                  |

|---------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Power Enable                               | Port has started power-up cycle.                                                                                                   |

| 1       | Power Good                                 | Port has finished the power-up stage and is delivering power.                                                                      |

| 2       | Disconnect                                 | Port that delivered power has moved from ON to OFF status.                                                                         |

| 3       | I2C Bus Soft Reset/Legacy D etection Ready | I2C bus, 50 ms timeout from Start to Stop condition IEEE <sup>®</sup> detection fail a nd legacy detection reset is ready to read. |

| 4       | Classification Done                        | Classification and AutoClass completed                                                                                             |

| 5       | Overload                                   | Overload or current limit event                                                                                                    |

| 6       | Start Error                                | Inrush current too high or insufficient power allocation                                                                           |

| 7       | Supply                                     | Failure related the system supply                                                                                                  |

- 0x01—Interrupt Mask

- Each bit represents a mask to a system event, described in register 0x00.

- When the bit is set by the host to 1, an event is reported in the relative bit of register 0x00. 0x02/0x03—Power

Events

- These two registers indicate any change in port power good/power enable status.

- Register 0x02 is a read only register.

- Register 0x03 is a COR register; when it is read, both the registers, 0x02 and 0x03, are cleared. Register 0x10 (Power Status) provides the actual power status of the port.

- Bits 0...3 indicate power enable/disable change:

- 0 = No change

- 1 = Change occurred

Bits 4...7 indicate power good change

- 0 = No change

- 1 = Change occurred

0x04/0x05—Detection, Classification, and Connection Check Events

- These two registers indicate changes in Detection, Classification, and Connection Check Events status.

- Register 0x04 is a read only register.

- Register 0x05 is a COR register; when it is read, both the registers, 0x04 and 0x05, are cleared.

- Registers 0x4C to 0x54 provide the full information about the requested class, assigned class, and AutoClass status.

- Bits 0...3 indicate detection and connection check change.

- 0 = Detection and connection check not completed yet

- 1 = Detection and connection check have been completed Bits 4...7 indicate detection and connection check change

- 0 = Classification not completed yet

- 1 = Classification has been completed 0x06/0x07—Underload/Overload Events

- These two registers indicate changes in the port status due to underload/disconnect or overload event.

- Register 0x06 is a read only register.

- Register 0x07 is a COR register; when it is read, both registers 0x06 and 0x07 are cleared.

- The port's power limit value can be set in register 0x29.

- Bits 0...3 indicate an event of overload

- 0 = No change

- 1 = Power was removed from the ports due to overload

- Bits 4...7 indicate an event of underload/PD disconnect/MPS

- 0 = No change

- 1 = Power was removed from the ports due to underload/PD disconnect/MPS 0x08/0x09—Power-up Fault/Current Limit Events

- These two registers indicate changes in the port status due to port power-up fault (that is, high inrush), and when port was disconnected due to current limit event longer then

- TLIM or short circuit.

- Register 0x08 is a read only register.

- Register 0x09 is a COR register; when it is read, both registers 0x06 and 0x07 are cleared.

- Bits 0...3 indicate an event of power-up fault

- $\circ$  0 = No fault

- 1 = Power up fault on the port

- Bits 4...7 indicate an event of underload/PD disconnect/MPS

- 0 = No fault

- □ 1 = Power was removed from the ports due to current limit event/short 0x0A/0x0B—Supply Events

- Register Functionality These two registers indicate failures in the power supply of the system.

- · Each bit reflects a certain failure.

- Register 0x0A is a read only register.

- Register 0x0B is a COR register; when it is read, both the registers, 0x06 and 0x07, are cleared.

The following table describes the failure associated with the two registers.

Table 3-2. Supply Failure Event

| Bi<br>t | Event Name                                   | Event Description                                                                                                                         |

|---------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | NA                                           | Always 0                                                                                                                                  |

| 1       | OSS Event                                    | <ul> <li>0 = No event</li> <li>1 = An event occurred</li> <li>(Reg 0x00, bit 2 is also set due to OSS event)</li> </ul>                   |

| 2       | 4-Pair Port—Over Power Event (Ports 1 and 2) | <ul> <li>0 = No event</li> <li>1 = Over power of event occurred (Reg 0x00, bit 5 is also set)</li> </ul>                                  |

| 3       | 4-Pair Port—Over Power Event (Ports 3 and 4) | <ul> <li>0 = No event</li> <li>1 = Over power of event occurred (Reg 0x00, bit 5 is also set)</li> </ul>                                  |

| 4       | V <sub>MAIN</sub> too low                    | <ul> <li>0 = No event</li> <li>1 = V<sub>MAIN</sub> is below the minimum threshold</li> </ul>                                             |

| 5       | V <sub>DD</sub> too low warning              | <ul> <li>0 = No event</li> <li>1 = V<sub>DD</sub> is below the minimum warning threshold (2.7 V<sub>DC</sub>)</li> </ul>                  |

| 6       | V <sub>DD</sub> too low failure              | <ul> <li>0 = No event</li> <li>1 = V<sub>DD</sub> is below the minimum failure threshold (2.4 V<sub>DC</sub>, PoE is disabled)</li> </ul> |

| 7       | Over Temperature                             | <ul> <li>0 = No event</li> <li>1 = Temperature exceeds the setting</li> </ul>                                                             |

# Status Registers (0x0C to 0x11)

These four registers that provide the port detection status are listed in Table 3-3, and the actual detected classification is listed in Table 3-4. These registers are read only.

- 0x0C: Port 1 Detection Status/Detected Classification

- 0x0D: Port 2 Detection Status/Detected Classification

- 0x0E: Port 3 Detection Status/Detected Classification

- 0x0F: Port 3 Detection Status/Detected Classification

- Each register is divided into bits for detection status and requested class status.

| Value Bin/Hex | Detection Status                     |

|---------------|--------------------------------------|

| 0000b/0x0     | Unknown: POR value                   |

| 0001b/0x1     | Short circuit                        |

| 0010b/0x2     | Port is pre-charged                  |

| 0011b/0x3     | Resistor is too low                  |

| 0100b/0x4     | Valid IEEE® 802.3bt detection        |

| 0101b/0x5     | Resistor is too high                 |

| 0110b/0x6     | Port is open/empty                   |

| 0111b/0x7     | External voltage is detected on port |

| Value Bin/Hex | Detection Status |  |  |

|---------------|------------------|--|--|

| 1110b/0x14    | MOSFET_FAULT     |  |  |

Table 3-4. Requested Class Status (Bits 4...7)

| Value Bin/Hex | Requested Class Status                                 |  |

|---------------|--------------------------------------------------------|--|

| 0000b/0x0     | Unknown: POR value                                     |  |

| 0001b/0x1     | Class 1                                                |  |

| 0010b/0x2     | Class 2                                                |  |

| 0011b/0x3     | Class 3                                                |  |

| 0100b/0x4     | Class 4                                                |  |

| 0101b/0x5     | Reserved: Treated as class 0                           |  |

| 0110b/0x6     | Class 0                                                |  |

| 0111b/0x7     | Over current                                           |  |

| 1000b/0x8     | Class 5 4P SS                                          |  |

| 1001b/0x9     | Class 6 4P SS                                          |  |

| 1010b/0xA     | Class 7 4P SS                                          |  |

| 1011b/0xB     | Class 8 4P SS                                          |  |

| 1100b/0xC     | Class 4 + (PSE port is limited to type 1 power budget) |  |

| 1101b/0xD     | Class 5 4P DS                                          |  |

| 1110b/0xE     | Reserved                                               |  |

| 1111b/0xF     | Classification mismatch                                |  |

# Notes:

- SS = Single Signature

- DS = Dual Signature

#### 0x10—Power Enable/Power Good

- The Power Enable bit (bits 0..3, a bit per port) is set when a port is in powered-up process.

- The Power Good Status bit (bits 4..7, a bit per port) represents a power delivery port, after it is turned on successfully.

- This register is linked to the event registers 0x02/0x03.

- Bits 0...3 Power Enable

- 0 = Port is not in power-up process

- 1 = Port is in powered-up process

- Bits 4...7 Power Good

- 0 = Port is off

- 1 = Port was powered-up successfully

#### 0x11—I2C Status

• Bits 3...6 provide the value of pins A1...A4 (pins 48..51), which set the I2C address of both quads.

# Configuration Registers (0x12 to 0x19 and 0x27/0x28) 0x12—Port Operation Mode Setting

- This register is read/write, to set all 4 ports according to Table 3-5. Each 2 bits set a port according to Table 3-5:

- Bits 0..1 set port 1

- Bits 2..3 set port 2

- Bits 4..5 set port 3

- Bits 6..7 set port 4

Table 3-5. Port Operation Mode

| Port Operation<br>Mode | Description                                                                                                              | Valu<br>e |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|

| Disable                | Any PoE activity is disabled (detection, classification, power).                                                         | 00b       |

| Autonomous             | <ul> <li>PSE is enabled.</li> <li>Detection, classification, power-up, and power are preformed automatically.</li> </ul> | 11b       |

- 0x15—Port Priority

- · This register is read/write.

- Bits 0..3 should be set to 0.

- Bits 4..7 set if the port are effected by the OSS pin:

- Bit 4 sets port 1

- o Bit 5 sets port 2

- Bit 6 sets port 3

- Bit 7 sets port 4

- When the bit is set to 0, the port is not disconnected due to OSS level changes. When the bit is set to 1, the power of that port is removed during OSS changes. 0x17—Misc

- This register is read/write, only bit 4 should be set.

- Bit 4 set the OSS mode:

- 0 = OSS mode is a single bit

- 1 = OSS is multi-bit

- 0x19—Power Pushbutton

- This register is read/write.

- Bits 4..7 are used to disable momentary the PoE activity of the ports, bit per port. After that the port will continue its activity per register 0x14

- 0 = Performs nothing.

- 1 = Port is momentary turned off. After the action, the bit will be internally cleared. After the action, the bit will be internally cleared.

- A bit per port:

- Bit 4 sets port 1

- Bit 5 sets port 2

- Bit 6 sets port 3

- Bit 7 sets port 4

### 0x27/0x28—Multi-Bit Priority

- These 2 registers are read/write, only bit 4 should be set, all other bits should be kept as in the default.

- In each register, the priority of two ports can be set, 8 levels of priority, while priority 7 is the highest priority, and priority 0 is the lowest.

- Register 0x27 sets the priority of ports 1, 2.

- Register 0x28 sets ports 3, 4.

- General Registers (0x1B and 0x1C)

### 0x1B—Manufacture ID and Chip IC

- This register is read only.

- The register value is 0x2D (00101101b).

#### 0x1C—AutoClass and Connection Check Result

- · This register is read only.

- Bits 0...1 provide the result of the connection check of the first 4-pair port (ports 1 and 2), per Table 3-6.

- Bits 2...3 provide the result of the connection check of the second 4-pair port (ports 3 and 4), per Table 3-6.

#### Table 3-6. Connection Check Result

| Value | Connection Check Result                                                         |

|-------|---------------------------------------------------------------------------------|

| 0x0   | Unknown or incomplete.                                                          |

| 0x1   | 4-pair single signature.                                                        |

| 0x2   | 4-pair dual signature.                                                          |

| 0x3   | Faulty connection check, or invalid signature detected on one of the pair sets. |

# Bits 4...7 Indicate if the connected PD supports AutoClass:

- 0 = PD does not support AutoClass

- 1 = PD supports AutoClass

### A bit per port:

- Bit 4 sets port 1

- Bit 5 sets port 2

- Bit 6 sets port 3

- Bit 7 sets port 4

**Note: The** result of the AutoClass measurements is read in registers 0x51 to 0x54.

# Specialized Registers (0x24 to 0x2F) 0x24/0x25—Power on Error

- These two registers indicate an error during power on sequence (detection, classification, or insufficient power).

- Register 0x24 is a read only register.

- Register 0x25 is a COR register; when it is read, both registers 0x24 and 0x25 are cleared.

### Each port is represented by 2 bits, as seen in Table 3-8:

- Bits 0..1 represent port 1

- Bits 2..3 represent port 2

- Bits 4..5 represent port 3

- Bits 6..7 represent port 4

### Table 3-7. Power on Error Result

| Value | Power on Failure Description |  |

|-------|------------------------------|--|

| 0x0   | No failure                   |  |

| 0x1   | Invalid detection            |  |

| 0x2   | Invalid classification       |  |

| 0x3   | Insufficient power           |  |

### 0x26—Ports Matrix (Remap)

- This register is read/write, is intended re-arrange the ports matrix differently than the default matrix (0xE4).

- If the register is not modified by the user, the default port matrix is shown in Table 3-8.

### Each port is represented by 2 bits:

- Bits 0..1 represent logical port 1

- Bits 2..3 represent logical port 2

- Bits 4..5 represent logical port 3

- Bits 6..7 represent logical port 4

Table 3-8. Default Port Matrix

| Bits | Value   | Logical Port | Physical Port |

|------|---------|--------------|---------------|

| 01   | 0 (00b) | 1            | 1             |

| 23   | 1 (01b) | 2            | 2             |

| 45   | 2 (10b) | 3            | 3             |

| 67   | 3 (11b) | 4            | 4             |

### 0x2A/0x2B—4-Pair Police Configuration

- These two registers are read/write, to set the power limit of the ports (PCUT). Register 0x2A sets the 4-pair port based ports 1 and 2.

- Register 0x2B sets the 4-pair port based ports 3 and 4.

- The following table lists the power level of the 4-pair port.

- The power limit is equal to PCUT = 0.5 \* Value

Table 3-9. PCUT Value

| Assigned Class | Value Hex/De | Minimum P <sub>CUT</sub> Setting (0x1 7 Bit 0 = 0) | Minimum P <sub>CUT</sub> Setting (0x1 7 Bit 0 = 1) |

|----------------|--------------|----------------------------------------------------|----------------------------------------------------|

| Class 0        | 0x22 (34d)   | 15.5W                                              | 17W                                                |

| Class 1        | 0x08 (8d)    | 4W                                                 | 17W                                                |

| Class 2        | 0x0E (14d)   | 7W                                                 | 17W                                                |

| Class 3        | 0x22 (34d)   | 15.5W                                              | 17W                                                |

| Class 4        | 0x40 (64d)   | 30W                                                | 32W                                                |

| Assigned Class          | Value Hex/De | Minimum P <sub>CUT</sub> Setting (0x1 7 Bit 0 = 0) | Minimum P <sub>CUT</sub> Setting(0x1 7 Bit 0 = 1) |

|-------------------------|--------------|----------------------------------------------------|---------------------------------------------------|

| Class 5—4P SS           | 0x5A (90d)   | 45W                                                | 45W                                               |

| Class 6—4P SS           | 0x78 (120d)  | 60W                                                | 60W                                               |

| Class 7—4P SS           | 0x96 (150d)  | 75W                                                | 75W                                               |

| Class 8—4P SS           | 0xB4 (180d)  | 90W                                                | 90W                                               |

| Class 4+—Type 1 limited | 0x22 (34d)   | 15.5W                                              | 17W                                               |

| ANY 4P DS PD            | 0xB4 (180d)  | 90W                                                | 90W                                               |

### 0x2C—Chip Temperature

This is a read-only register provide the die temperature, based on the following formula: 367 – {2 \* (regVal\_decimal)} (degrees Celsius)

#### 0x2E/0x2F—VMAIN Measurement

- These two registers are read only, and provide the level of VMAIN by 14 bits, with resolution of 64.4 mV per bit.

- Register 0x2E represents the 8 LSB bits of the measurement.

- Register 0x2F represents the 6 MSB bits, bits 6 and 7 of that register are not used.

- The maximum value can be measured is 61V, VMAIN above 61V is reported as 61V (0x3B3).

- Example: VMAIN of 55V is provided as 0x356 (55V/64.4 mV = 854).

- Port Voltage and Current Measurement Registers (0x30 to 0x3F)

- The voltage and current of each port are provided by four registers (two for port voltage and two for current).

- The two current registers per port provide the current level by 14 bits, with resolution of 1 mA per LSB. The maximum value that can be measured is 1020 mA, current above that level is reported as 1020 mA (0x3FC).

- The two voltage registers per port provide the voltage level by 14 bits, with resolution of 64.4 mV per LSB. The maximum value can be measured is 61V, voltage above that level is reported as 61V (0x3B3).

#### 0x30/0x31—Port 1 Current Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x32/0x33—Port 1 Voltage

Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x34/0x35—Port 2 Current

Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x36/0x37—Port 2 Voltage

Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used.

#### 0x38/0x39—Port 3 Current Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x3A/0x3B—Port 3 Voltage

Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x3C/0x3D—Port 4 Current Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used. 0x3E/0x3F—Port 4 Voltage

Measurement

- Register 0x30 represents the 8 LSB bits of the measurement.

- Register 0x31 represents the 6 MSB bits, bits 6 and 7 of that register are not used.

- Port Inrush Current Control Register (0x40)

### 0x40—Inrush Current Control

Only bits 0-3 are active, bits 4-7 are not used.

#### Each bit sets a port:

- Bit 0 sets port 1

- Bit 1 sets port 2

- Bit 2 sets port 3

- Bit 3 sets port 4

- 0: If in the end of the start-up period inrush current is still high, port is not powered up.

- 1: If in the end of the start-up period inrush current is still high, port is powered up normally.

- Firmware Version and Chip ID Registers (0x41 and 0x43)

### 0x41—Firmware Version

- · This register is read only.

- For the most recent version, contact Microchip.

- 0x43—Silicon Version and Chip ID

- This register is read only.

- Bits 0...4 show the chip ID.

- Bits 5...7 show the silicon version.

- For the most recent version, contact Microchip.

- Port Signature Measurement Registers (0x44 to 0x4B)

### 0x44-0x47—Signature Measured Resistance

- These four registers are read only, and provide the resistance measured during the signature detection.

- Register per port,  $256\Omega$  per bit  $(480\Omega$  for short,  $65280\Omega$  maximum).

- 0x48-0x4B-Signature Measured Capacitance

- Register Functionality These four registers are read only, and provide the capacitance measured during the signature detection.

• Register per port, with a resolution of 64 nF per bit.

# Port Classification Status Registers (0x4C to 0x4F)

These four registers are read only and provide PD's requested class and the port's assigned class. The following table lists both values (requested and assigned).

Table 3-10. Requested and Assigned Values

| Value of Reques | ted and Assigned | Class Status |   |                    |

|-----------------|------------------|--------------|---|--------------------|

| 0               | 0                | 0            | 0 | Unknown            |

| 0               | 0                | 0            | 1 | Class 1            |

| 0               | 0                | 1            | 0 | Class 2            |

| 0               | 0                | 1            | 1 | Class 3            |

| 0               | 1                | 0            | 0 | Class 4            |

| 0               | 1                | 0            | 1 | NA                 |

| 0               | 1                | 1            | 0 | Class 0            |

| 0               | 1                | 1            | 1 | NA                 |

| 1               | 0                | 0            | 0 | Class 5—4-Pair SS  |

| 1               | 0                | 0            | 1 | Class 6—4Pair SS   |

| 1               | 0                | 1            | 0 | Class 7—4-Pair SS  |

| 1               | 0                | 1            | 1 | Class 8 —4-Pair SS |

| 1               | 1                | 0            | 0 | NA                 |

| 1               | 1                | 0            | 1 | Class 5—4-Pair DS  |

| 1               | 1                | 1            | 0 | NA                 |

| 1               | 1                | 1            | 1 | NA                 |

### Notes:

- **SS** = Single Signature; DS = Dual Signature.

- If PSE has limited power budget and cannot deliver the power that the PD asks for, the port's assigned class might be lower than the PD's requested class.

# 0x4C—Port 1 Class Status

- Bits 0...3 provide PD's requested class. Bits 4...7 provide the port's assigned class. 0x4D—Port 2 Class Status

- Bits 0...3 provide PD's requested class. Bits 4...7 provide the port's assigned class. 0x4E—Port 3 Class Status

- Bits 0...3 provide PD's requested class. Bits 4...7 provide the port's assigned class. 0x4F—Port 4 Class Status

- Bits 0...3 provide PD's requested class. Bits 4...7 provide the port's assigned class.

### **AutoClass Status Registers (0x51 to 0x54)**

- These four registers are read only and provide the AutoClass measurement and status.

- Bits 0...6 provide the power measured during the AutoClass stage, with a resolution of 0.5W per LSB. Bit 7 provides the AutoClass status:

- 0 = Measurement was not performed.

- 1 = AutoClass measurement was completed. 0x51—Port 1 AutoClass Status

- Bits 0...6 are PD's requested class.

- Bit 7 is AutoClass status.

#### • 0x52—Port 2 AutoClass Status

- Bits 0...6 are PD's requested class.

- Bit 7 is AutoClass status.

#### • 0x53—Port 3 AutoClass Status

- Bits 0...6 are PD's requested class.

- Bit 7 is AutoClass status.

#### • 0x53—Port 3 AutoClass Status

- Bits 0...6 are PD's requested class.

- Bit 7 is AutoClass status.

### **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description                                                    |

|----------|---------|----------------------------------------------------------------|

| В        | 4/2023  | Added section 1. Automode Operational Flowchart and Figure 1-1 |

| Α        | 04/2023 | Initial Revision                                               |

# **Microchip Information**

• The Microchip Website

Microchip provides online support via our website at <u>www.microchip.com</u>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

- Product Change Notification Service

- Microchip's product change notification service helps keep customers current on Microchip products.

Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

- To register, go to www.microchip.com/pcn and follow the registration instructions.

### Customer Support

- Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

- Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

- Technical support is available through the website at: www.microchip.com/support

- Microchip Devices Code Protection Feature

- Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is

constantly evolving. Microchip is committed to continuously improving the code protection features of our

products.

- · Legal Notice

- This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

- THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS

OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED

WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR

PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

- IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR

- ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

- Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual

#### **Trademarks**

- The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

- AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

- Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM- ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

- SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

- The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

- GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

- All other trademarks mentioned herein are property of their respective companies. © 2023, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

- ISBN: 978-1-6683-2380-9

- Quality Management System

- For information regarding Microchip's Quality Management Systems, please visit <a href="https://www.microchip.com/quality">www.microchip.com/quality</a>.

#### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office

- · 2355 West Chandler Blvd.

- Chandler, AZ 85224-6199

- Tel: 480-792-7200

- Fax: 480-792-7277

- · Technical Support:

- www.microchip.com/support

- · Web Address:

- www.microchip.com

- Atlanta

- · Duluth, GA

- Tel: 678-957-9614

- Fax: <u>678-957-1455</u>

- Austin, TX

- Tel: <u>512-257-3370</u>

- Boston

- · Westborough, MA

- Tel: 774-760-0087

- Fax: 774-760-0088

- Chicago

- Itasca, IL

- Tel: 630-285-0071

- Fax: 630-285-0075

- Dallas

- · Addison, TX

- Tel: 972-818-7423

- Fax: 972-818-2924

- Detroit

- Novi, MI

- Tel: 248-848-4000

- · Houston, TX

- Tel: 281-894-5983

- Indianapolis

- · Noblesville, IN

- Tel: 317-773-8323

- Fax: 317-773-5453

- Tel: 317-536-2380

- · Los Angeles

- Mission Viejo, CA

- Tel: 949-462-9523

- Fax: 949-462-9608

- Tel: 951-273-7800

- · Raleigh, NC

- Tel: 919-844-7510

- · New York, NY

- Tel: 631-435-6000

- · San Jose, CA

- Tel: 408-735-9110

- Tel: 408-436-4270

- Canada Toronto

- Tel: 905-695-1980

- Fax: 905-695-2078

### ASIA/PACIFIC

- Australia Sydney

- Tel: 61-2-9868-6733

- China Beijing

- Tel: 86-10-8569-7000

- China Chengdu

- Tel: 86-28-8665-5511

- China Chongqing

- Tel: 86-23-8980-9588

- China Dongguan

- Tel: 86-769-8702-9880

- China Guangzhou

- Tel: 86-20-8755-8029

- China Hangzhou

- Tel: 86-571-8792-8115

- China Hong Kong SAR

- Tel: 852-2943-5100

- China Nanjing

- Tel: 86-25-8473-2460

- China Qingdao

- Tel: 86-532-8502-7355

- · China Shanghai

- Tel: 86-21-3326-8000

- China Shenyang

- Tel: 86-24-2334-2829

- China Shenzhen

- Tel: 86-755-8864-2200

- China Suzhou

- Tel: 86-186-6233-1526

- China Wuhan

- Tel: 86-27-5980-5300

- China Xian

- Tel: 86-29-8833-7252

- China Xiamen

- Tel: 86-592-2388138

- China Zhuhai

- Tel: 86-756-3210040

- India Bangalore

- Tel: 91-80-3090-4444

- India New Delhi

- Tel: 91-11-4160-8631

- India Pune

- Tel: 91-20-4121-0141

- Japan Osaka

- Tel: 81-6-6152-7160

- Japan Tokyo

- Tel: 81-3-6880- 3770

- Korea Daegu

- Tel: 82-53-744-4301

- Korea Seoul

- Tel: 82-2-554-7200

- Malaysia Kuala Lumpur

- Tel: 60-3-7651-7906

- · Malaysia Penang

- Tel: 60-4-227-8870

- Philippines Manila

- Tel: 63-2-634-9065

- Singapore

- Tel: 65-6334-8870

- Taiwan Hsin Chu

- Tel: 886-3-577-8366

- Taiwan Kaohsiung

- Tel: 886-7-213-7830

- Taiwan Taipei

- Tel: 886-2-2508-8600

- Thailand Bangkok

- Tel: 66-2-694-1351

- Vietnam Ho Chi Minh

- Tel: 84-28-5448-2100

# **EUROPE**

- Austria Wels

- Tel: 43-7242-2244-39

- Fax: 43-7242-2244-393

- Denmark Copenhagen

- Tel: 45-4485-5910

- Fax: 45-4485-2829

- Finland Espoo

- Tel: 358-9-4520-820

- France Paris

- Tel: 33-1-69-53-63-20

- Fax: 33-1-69-30-90-79

- Germany Garching

- Tel: 49-8931-9700

- Germany Haan

- Tel: 49-2129-3766400

- Germany Heilbronn

- Tel: 49-7131-72400

- Germany Karlsruhe

- Tel: 49-721-625370

- Germany Munich

- Tel: 49-89-627-144-0

- Fax: 49-89-627-144-44

- Germany Rosenheim

- Tel: 49-8031-354-560

- Israel Ra'anana

- Tel: 972-9-744-7705

- Italy Milan

- Tel: 39-0331-742611

- Fax: 39-0331-466781

- Italy Padova

- Tel: 39-049-7625286

- Netherlands Drunen

- Tel: 31-416-690399

- Fax: 31-416-690340

- Norway Trondheim

- Tel: 47-72884388

- Poland Warsaw

- Tel: 48-22-3325737

- Romania Bucharest

- Tel: 40-21-407-87-50

- Spain Madrid

- Tel: 34-91-708-08-90

- Fax: 34-91-708-08-91

- Sweden Gothenberg

- Tel: 46-31-704-60-40

- Sweden Stockholm

- Tel: 46-8-5090-4654

- UK Wokingham

• Tel: 44-118-921-5800

• Fax: 44-118-921-5820

#### **User Guide**

© 2023 Microchip Technology Inc. and its subsidiaries

### **Documents / Resources**

MICROCHIP PD77728 Auto Mode Register Map [pdf] Instruction Manual DS00004761B, PD77728 Auto Mode Register Map, PD77728, PD77728 Register Map, Auto Mode Register Map, Register Map, Map

### References

- © <u>, ,337p</u>

- <u>Sempowering Innovation | Microchip Technology</u>

- <u>Sempowering Innovation | Microchip Technology</u>

- Design Help and Other Services | Microchip Technology

- <u>Sempowering Innovation | Microchip Technology</u>

- Microchip Lightning Support

- User Manual

#### Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.