# **MICROCHIP DDR Read IP User Guide**

Home » MICROCHIP » MICROCHIP DDR Read IP User Guide

#### **Contents**

- 1 MICROCHIP DDR Read

- IP

- 2 Specifications

- 3 FAQ

- 4 Introduction

- **5 Key Features**

- 6 Hardware

**Implementation**

- 7 Design Description

- **8 Configuration**

**Parameters**

- 9 CONTACT

- 10 Documents / Resources

- 10.1 References

- 11 Related Posts

**MICROCHIP DDR Read IP**

# **Specifications**

- Product Name: DDR Read IP v2.0

- Compatible with Video Arbiter IP

- Used for reading a burst of continuous data from DDR memory

- Typically used in video applications to read each horizontal line of the video frame stored in DDR memory

#### The DDR Read IP also has input and output ports in Arbiter

Interface bus and AXI4 Stream Interface, are listed in the user manual.

#### **FAQ**

- 1. What is the purpose of DDR Read IP?

- 2. What is the required compatibility for DDR Read IP?

- 3. In which applications are DDR Read IP typically used?

#### Introduction

DDR Read IP reads a burst of continuous data from the DDR memory. The DDR Read IP must be used with the Video Arbiter IP that converts the read requests to AXI4 transactions. The DDR Read IP is typically used in video applications to read each horizontal line of the video frame stored in DDR memory.

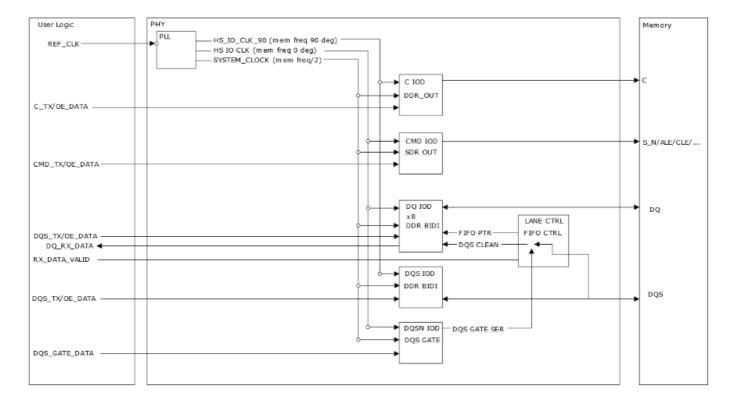

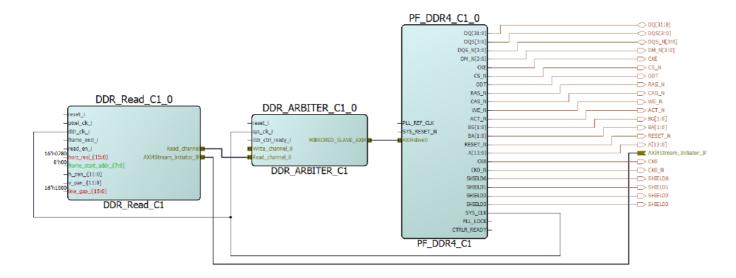

Figure 1. SmartDesign Arbiter Interface

# **Key Features**

- Typically used to Read Video Frame Lines

- Supports Output Video Pixel Width of 8, 16, and 32 bits

- Supports Video Arbiter Interface of 128, 256, and 512 bits

- Supports AXI4 Stream Interface

### **Hardware Implementation**

The IP generates the control signals to the Video arbiter IP based on the user inputs of the horizontal resolution frame start address. The rising edge of read\_en\_i initiates a read transaction. The data from the video umpire is stored in a CDC FIFO that converts the data from the DDR clock domain to the pixel clock domain. The data is read from FIFO at the falling edge of read\_en\_i and unpacked to generate pixel data. The read\_en\_i should be high for sufficient duration to complete the DDR read transaction and the recommended duration is for several clocks equal to horizontal resolution. The first line is read from the address defined by frame\_start\_addr\_i, and after each read transaction, the address is incremented by line\_gap\_i. The read address is reset to the frame\_start\_addr\_i at every frame\_end\_i signal. The output data is high for a horizontal resolution number of clocks.

#### **Design Description**

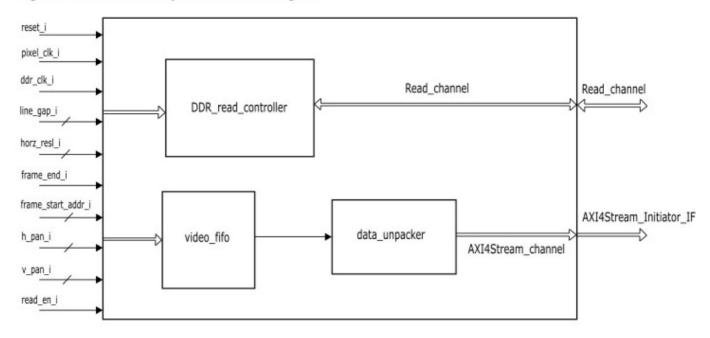

• The following figure shows the top-level pin-out diagram of DDR Read.

Figure 1-1. DDR Read Top-level Pin Out Diagram

# **Input and Output Ports**

The following table lists the input and output ports of the DDR Read IP in the Native Interface. Table 1-1. Input and Output Ports of the DDR Read in Native Interface.

| Port Name   | Туре  | Width   | Description                                    |  |

|-------------|-------|---------|------------------------------------------------|--|

| reset_i     | Input | _       | Active Low asynchronous reset signal to design |  |

| pixel_clk_i | Input | _       | Pixel clock                                    |  |

| ddr_clk_i   | Input | _       | DDR clock from the memory controller           |  |

| frame_end_i | Input | _       | End of frame signal                            |  |

| read_en_i   | Input | _       | Read enable signal for reading                 |  |

| line_gap_i  | Input | 16 bits | Line gap between two lines                     |  |

| horz_resl_i | Input | 16 bits | Horizontal resolution                          |  |

| Port Name         | Туре       | Width             | Description                                                   |  |

|-------------------|------------|-------------------|---------------------------------------------------------------|--|

| h_pan_i           | Input      | 12 bits           | Horizontal offset for each video line for horizontal panning  |  |

| v_pan_i           | Input      | 12 bits           | Vertical offset from frame start address for vertical panning |  |

| read_ackn_i       | Input      | _                 | Acknowledgment for read request from video arbiter            |  |

| read_done_i       | Input      | _                 | Read completion input from the video arbiter                  |  |

| ddr_data_valid_i  | Input      | _                 | Read data valid from Arbiter                                  |  |

| frame_start_addr  | Input      | 8 bits            | Video frame start address                                     |  |

| wdata_i           | Input      | Input Data Width  | Read data from Arbiter                                        |  |

| read_req_o        | Outpu<br>t | _                 | Read the request to the arbiter                               |  |

| read_start_addr_o | Outpu<br>t | 32 bits           | DDR address from where read has to be started                 |  |

| burst_size_o      | Outpu<br>t | 8 bits            | Read burst size                                               |  |

| data_valid_o      | Outpu<br>t | _                 | Data Valid                                                    |  |

| data_o            | Outpu<br>t | Output Data Width | Data for Video Pipelining                                     |  |

The following table lists the input and output ports of the DDR Read IP in the Arbiter Interface bus. Table 1-2. Input and Output Ports of the DDR Read in Arbiter Interface Bus.

| Port Name | Туре   | Width            | Description                                   |  |

|-----------|--------|------------------|-----------------------------------------------|--|

| RDATA_I   | Input  | Input Data Width | Read data from Arbiter                        |  |

| RVALID_I  | Input  | _                | Read data valid from Arbiter                  |  |

| ARREADY_I | Input  | _                | Arbiter acknowledgment from read request      |  |

| BUSER_I   | Input  | _                | Read completion                               |  |

| ARADDR_O  | Output | 32 bits          | DDR address from where read has to be started |  |

| ARVALID_O | Output | _                | Read the request to the arbiter               |  |

| ARSIZE_O  | Output | 8 bits           | Read burst size                               |  |

The following table lists the input and output ports of the DDR Read IP in the AXI4 Stream Interface. Table 1-3. Input and Output Ports of the DDR Read in AXI4 Stream Interface.

| Port Name | Туре   | Width                       | Description                                    |  |

|-----------|--------|-----------------------------|------------------------------------------------|--|

| CLOCK_I   | Input  | _                           | Pixel clock                                    |  |

| RESET_n_I | Input  | _                           | Active Low asynchronous reset signal to design |  |

| TDATA_O   | Output | Output Data Width           | Output Video Data                              |  |

| TSTRB_O   | Output | [Output Data Width/8 - 1:0] | Output Video Data strobe                       |  |

| TKEEP_O   | Output | [Output Data Width/8 – 1:0] | Output Video Data Keep                         |  |

| TVALID_O  | Output | _                           | Output Video data valid                        |  |

|           |        |                             | Output user data 0bit= VSYNC                   |  |

| TUSER_O   | Output | 4 bits                      | 3bit =Frame end                                |  |

| Port Name | ort Name Type Width |  | Description               |  |

|-----------|---------------------|--|---------------------------|--|

| TLAST_O   | AST_O Output —      |  | Output Video End of Frame |  |

# **Configuration Parameters**

The following table lists the configuration parameters used in the DDR Read IP hardware implementation. These are generic parameters and can be varied based on the application requirements.

Table 1-4. Configuration Parameters

| Parameter Name           | Description                                                                                       |  |

|--------------------------|---------------------------------------------------------------------------------------------------|--|

| Horizontal<br>Resolution | Defines horizontal resolution                                                                     |  |

| Input Data Width         | Defines the input data width (128, 256, and 512 bits)                                             |  |

| Output Data Width        | Defines the output data width (8, 16, 24, 32, and 64 bits)                                        |  |

| Arbiter Interface        | Options to select the Arbiter Interface from the drop-down menu as Native or Bus Interfac e       |  |

| Data Interface           | Options to select the Data Interface from the drop-down menu as Native and AXI4 Strea m Interface |  |

#### **Resource Utilization**

The following table lists the resource utilization for DDR Read IP in the Native Interface with the input data width = 256 and output data width = 8.

DDR Read block is implemented on the PolarFire FPGA device, MPF300TS\_ES-1FCG1152E package.

Table 1-5. DDR Read IP in Native Interface

| Resource     | Usage |

|--------------|-------|

| DFFs         | 502   |

| 4 input LUTs | 513   |

| MACC         | 0     |

| LSRAM 18K    | 14    |

| SRAM         | 0     |

The following table lists the resource utilization for DDR Read IP in the Bus Interface and AXI4 stream with input data width = 256 and output data width = 8.

Table 1-6. DDR Read IP in Bus Interface and AXI4 Stream

| Resource     | Usage |

|--------------|-------|

| DFFs         | 512   |

| 4 input LUTs | 514   |

| MACC         | 0     |

| LSRAM 18K    | 14    |

| SRAM         | 0     |

#### **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description       |  |

|----------|---------|-------------------|--|

| 1.0      | 03/2022 | Initial Revision. |  |

#### **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources before contacting support as it is very likely that their queries have been already answered.

Contact the Technical Support Center through the website at <a href="www.microchip.com/support">www.microchip.com/support</a>. Mention the FPGA Device Part number, select the appropriate case category, and upload design files while creating a technical support case. Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

#### The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Datasheets and errata, application notes and sample programs, design resources, user guides and hardware support documents, latest software releases, and archived software.

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing.

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, the listing of seminars and events, listings of Microchip sales offices, distributors, and factory representatives.

#### **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notifications whenever there are changes, updates, revisions, or errata related to a specified product family or development tool of interest.

To register, go to <a href="https://www.microchip.com/pcn">www.microchip.com/pcn</a> and follow the registration instructions.

#### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative, or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document. Technical support is available through the website at: <a href="https://www.microchip.com/support">www.microchip.com/support</a>.

#### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating

specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip products are strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly

evolving. Microchip is committed to continuously improving the code protection features of our products.

#### **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE. IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE NUMBER OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify, and hold harmless Microchip from all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motor bench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, membrane, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAMICE, Serial Quad I/O, simple map, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY,

ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

- SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

- The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

- GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

- All other trademarks mentioned herein are the property of their respective companies.

- © 2022, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved. ISBN: 978-1-6683-0015-

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **CONTACT**

| AMERICAS                                            | ASIA/PACIFIC          | ASIA/PACIFIC         | EUROPE                |

|-----------------------------------------------------|-----------------------|----------------------|-----------------------|

|                                                     |                       |                      | Austria – Wels        |

|                                                     |                       |                      | Tel: 43-7242-2244-39  |

| Corporate Office                                    |                       |                      | Fax: 43-7242-2244-393 |

| -                                                   |                       |                      | Denmark – Copenhagen  |

| 2355 West Chandler Blvd.<br>Chandler, AZ 85224-6199 |                       |                      | Tel: 45-4485-5910     |

| Tel: 480-792-7200                                   |                       |                      | Fax: 45-4485-2829     |

| Fax: 480-792-7277                                   | Australia – Sydney    |                      | Finland – Espoo       |

| Technical Support: www.microchip.com/support        | Tel: 61-2-9868-6733   |                      | Tel: 358-9-4520-820   |

| Web Address: www.micr                               | China – Beijing       |                      | France – Paris        |

| ochip.com Atlanta                                   | , 0                   | India – Bangalore    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                                          | Tel: 86-10-8569-7000  | Tel: 91-80-3090-4444 | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614                                   | China – Chengdu       | India – New Delhi    |                       |

| Fax: 678-957-1455                                   | Tel: 86-28-8665-5511  | Tel: 91-11-4160-8631 | Germany – Garching    |

| Austin, TX                                          | China – Chongqing     | India – Pune         | Tel: 49-8931-9700     |

| •                                                   | Tel: 86-23-8980-9588  |                      | Germany – Haan        |

| Tel: 512-257-3370                                   |                       | Tel: 91-20-4121-0141 | Tel: 49-2129-3766400  |

| Boston Westborough, M                               | China – Dongguan      | Japan – Osaka        | Germany – Heilbronn   |

| A Tel: 774-760-0087                                 | Tel: 86-769-8702-9880 | Tel: 81-6-6152-7160  | Tel: 49-7131-72400    |

| Fax: 774-760-0088                                   | China – Guangzhou     | Japan – Tokyo        |                       |

| Chicago                                             | Tel: 86-20-8755-8029  | Tel: 81-3-6880- 3770 | Germany – Karlsruhe   |

| Itasca, IL                                          | China – Hangzhou      |                      | Tel: 49-721-625370    |

| Tel: 630-285-0071                                   |                       | Korea – Daegu        | Germany – Munich      |

|                                                     | Tel: 86-571-8792-8115 | Tel: 82-53-744-4301  | Tel: 49-89-627-144-0  |

| Fax: 630-285-0075                                   | China – Hong Kong     | Korea – Seoul        |                       |

SAR **Dallas** Tel: 82-2-554-7200 Fax: 49-89-627-144-44 Tel: 852-2943-5100 Addison, TX Malaysia – Kuala Germany – Rosenheim Lumpur China – Nanjing Tel: 972-818-7423 Tel: 49-8031-354-560 Tel: 60-3-7651-7906 Tel: 86-25-8473-2460 Fax: 972-818-2924 Israel - Ra'anana Malaysia - Penang China - Qingdao **Detroit** Tel: 972-9-744-7705 Tel: 60-4-227-8870 Tel: 86-532-8502-7355 Novi, MI Italy - Milan Philippines - Manila China – Shanghai Tel: 248-848-4000 Tel: 39-0331-742611 Tel: 63-2-634-9065 Tel: 86-21-3326-8000 Fax: 39-0331-466781 Houston, TX Singapore China - Shenyang Tel: 281-894-5983 Italy – Padova Tel: 65-6334-8870 Tel: 86-24-2334-2829 Indianapolis Noblesville, Tel: 39-049-7625286 IN Tel: 317-773-8323 Taiwan - Hsin Chu China – Shenzhen Netherlands – Drunen Fax: 317-773-5453 Tel: 886-3-577-8366 Tel: 86-755-8864-2200 Tel: 31-416-690399 Tel: 317-536-2380 Taiwan – Kaohsiung China - Suzhou Fax: 31-416-690340 Los Angeles Mission Viei Tel: 886-7-213-7830 Tel: 86-186-6233-1526 Norway – Trondheim o, CA Tel: 949-462-9523 Taiwan - Taipei China - Wuhan Tel: 47-72884388 Fax: 949-462-9608 Tel: 886-2-2508-8600 Tel: 86-27-5980-5300 Poland - Warsaw Tel: 951-273-7800 Thailand – Bangkok China - Xian Tel: 48-22-3325737 Raleigh, NC Tel: 66-2-694-1351 Tel: 86-29-8833-7252 Romania – Bucharest Tel: 919-844-7510 Vietnam - Ho Chi Minh China - Xiamen Tel: 40-21-407-87-50 **New York, NY** Tel: 84-28-5448-2100 Tel: 86-592-2388138 Spain - Madrid Tel: 631-435-6000 China - Zhuhai Tel: 34-91-708-08-90 San Jose, CA Tel: 86-756-3210040 Fax: 34-91-708-08-91 Tel: 408-735-9110 Sweden – Gothenburg Tel: 408-436-4270 Tel: 46-31-704-60-40 Canada - Toronto Sweden - Stockholm Tel: 905-695-1980 Tel: 46-8-5090-4654 Fax: 905-695-2078 UK - Wokingham Tel: 44-118-921-5800 Fax: 44-118-921-5820

# MICROCHIP DDR Read IP [pdf] User Guide DDR Read IP, DDR, Read IP, IP

# References

- © { 42 ,18 , AV }

- <u>Sempowering Innovation | Microchip Technology</u>

- <u>Sempowering Innovation | Microchip Technology</u>

- Support | Microchip Technology

- Product Change Notification | Microchip Technology

- • Quality | Microchip Technology

- Microchip Lightning Support

- Client Support Services | Microchip Technology

- User Manual

Manuals+, Privacy Policy