# MICROCHIP CoreSmartBERT v2.9 Software User Guide

Home » MICROCHIP » MICROCHIP CoreSmartBERT v2.9 Software User Guide

### **Contents**

- 1 Introduction

- 2 Features

- **3 Functional Description**

- 4 Operation

- 5 Interface

- **6 Tool Flows**

- **7 Revision History**

- **8 Customer Support**

- 9 Worldwide Sales and

Service

- 10 Documents / Resources

- 11 Related Posts

## Introduction

The CoreSmartBERT core provides a broad-based evaluation and demonstration platform for PolarFire® and PolarFire SoC transceivers. CoreSmartBERT is configurable to use different transceivers, clocking topologies,

line rates, and reference clock rates. Data pattern generators and checkers are included for each transceiver, giving several different Pseudo Random Binary Sequences (PRBS) (27, 29, 223, and 231). The pattern generator sends data out through the transmitter. The pattern checker accepts data through the receiver and checks it against an internally generated pattern. These patterns are optimized for the logic width that has been selected at run time. SmartDebug provides the user interface to this core.

This user guide provides information on the CoreSmartBERT IP core and the features it supports. The purpose of this IP core is to add more test features for the transceiver, so that the end user can evaluate the Physical Media Attachment (PMA) functionality of transceiver on a board. The SmartDebug tool interfaces with this core, which allows the user to have an interactive Graphical User Interface (GUI) control.

### **Features**

CoreSmartBERT has the following features:

- Supports PolarFire and PolarFire SoC Transceiver built-in PRBS Generator or Checker

- · Generates a List of Patterns

- Inserts an Error into the Transmit Pattern

- Checking of Errors in the Receive Pattern

- Instantiating the Pattern Functionality Several Times to Support Multiple Lanes Simultaneously

### **Supported Families**

CoreSmartBERT supports the following families:

- PolarFire® SoC

- PolarFire

### **Device Utilization and Performance**

The following Field Programmable Gate Array (FPGA) device families implement CoreSmartBERT. The following table lists the summary of the implementation data for CoreSmartBERT.

**Table 1. CoreSmartBERT Utilization**

| Device Details |          | Resource | ces  |                | Performance (MHz)  |  |

|----------------|----------|----------|------|----------------|--------------------|--|

| Family         | Device   | LUTs     | DFF  | Logic Elements | renormance (wiriz) |  |

| PolarFire SoC  | MPFS250T | 2860     | 1082 | 3050           | 125                |  |

| PolarFire      | MPF300T  | 2860     | 1082 | 3050           | 125                |  |

**Note:** We get the data in the preceding table using typical synthesis and layout settings: CDR reference clock source as Dedicated and unchanged other configurator values.

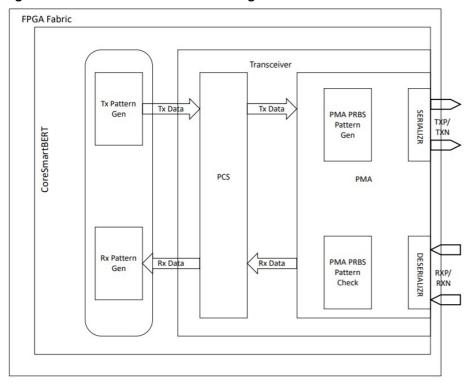

# **Functional Description**

CoreSmartBERT includes the transceiver, which interfaces with the SmartDEBUG tool through a user control GUI, to run the hardened PRBS generator and checkers. It also has fabric pattern generators and checkers with more

features (for example, error injection) than the ones included in transceiver.

Figure 1-1. CoreSmartBERT Block Diagram

### **TX Pattern Gen**

This transmitter block generates the following pattern:

• PRBS 7, 9, 23, 31 with error insertion logic

### **RX Pattern CHK**

The receiver block checks the following patterns:

• PRBS 7, 9, 23, 31

#### **Transceiver**

The transceiver is PolarFire/PolarFire SoC's transceiver macro in Physical Media Attachment (PMA) mode.

# Operation

This section describes the operation performed by CoreSmartBERT.

### **Test Pattern Overview**

CoreSmartBERT supports the following test patterns.

# **PRBS**

Pseudo Random Binary Sequence (PRBS) test patterns generate deterministic sequences with the properties of highly random signals, for example: white noise.

CoreSmartBERT supports the built in PBRS pattern generators and checkers in the transceiver and add the support for the fabric PRBS pattern generators and checkers with the ability to inject errors into the transmitter path.

These include support for the following

- PRBS 7

- PRBS 9

- PRBS 23

- PRBS 31

### **Smart Debug Tool**

SmartDebug provides the user interface to control the CoreSmartBERT core to use its features.

SmartDebug has the following capabilities:

- Ability to control CoreSmartBERT and have the signal integrity controls on the screen at the same time

- Automatic detection of the presence of CoreSmartBERT in the design

- Ability to select the particular transceiver lane associated with CoreSmartBERT

- · Availability of several patterns options

- An ability to enable to start the pattern transmitter

- · An ability to enable to start the pattern receiver

- · A button to insert a single error

- An error counter with a clear button

### **SLE DEBUG Marco**

SLE\_DEBUG Marco is used to communicate with SmartDebug. The SLE\_DEBUG mechanism gives ability to run synthesis while preserving a set of registers. It provides ability to identify, rename, and classify registers for SmartDebug.

CoreSmartBERT has SLE\_DEBUG write and read registers that are used to inform the Smart Debug tool of parameters settings chosen, IP core versions number, and control various functions (for example, error injection, read errors, and so on.). The following table describes the SLE\_DEBUG registers that are used in CoreSmartBERT.

# Table 2-1. SLE\_DEBUG Registers

| Bit<br>s | Function                      |   | Description                                                                                                                                                           |

|----------|-------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14       | 14 SLE_DATA_RATE              |   | Reads data rate selected from the GUI. 1: 250 Mbps2: 1 000 Mbps3: 1250 Mbps4: 2500 Mbps5: 3125 Mbps6: 50 00 Mbps7: 6250 Mbps8: 8000 Mbps9: 10000 Mbps10: 1 0312.5Mbps |

| 4        | SLE_TX_CLK_DIV_FACTOR         | R | Reads Tx Clock Divide Factor selected from the GUI.                                                                                                                   |

| 1        | SLE_CDR_REFERENCE_CLK_SOURC E |   | Reads the CDR Reference Clock Source selected from the GUI:0: Dedicated1: Fabric                                                                                      |

| 4        | SLE_CDR_REFERENCE_CLK_FREQ    |   | Reads the CDR Reference Clock Frequency selected from the GUI:0: 25.001: 31.252: 50.003: 62.504: 75.005: 10 0.006: 125.007: 150.008: 156.259: 312.50                  |

| 2        | SLE_NUMBER_OF_LANES           |   | Reads the number of lanes this IP core has enabled fro m the GUI.                                                                                                     |

| 1        | SLE_PATTERN_PRBS7             |   | Reads the PRBS7 pattern enable from the GUI.                                                                                                                          |

| 1        | SLE_PATTERN_PRBS9             |   | Reads the PRBS9 pattern enable from the GUI.                                                                                                                          |

| 1        | SLE_PATTERN_PRBS23            | R | Reads the PRBS23 pattern enable from the GUI.                                                                                                                         |

| 1        | SLE_PATTERN_PRBS31            | R | Reads the PRBS31 pattern enable from the GUI.                                                                                                                         |

| 16       | SLE_CPZ_VERSION               | R | Reads the CPZ Version number. This registers represent s 8bit major and 8bit minor version number. For example, v2.1 = {8'd2, 8'd1}                                   |

|          | continued                  |    |                                                                                                                |  |  |  |

|----------|----------------------------|----|----------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit<br>s | Function                   |    | Description                                                                                                    |  |  |  |

| 4        | SLE_TX_LANE[n]_PATTEN_GEN  | RW | Transmitter Pattern Generator: 0: PRBS71: PRBS 91: P<br>RBS232: PRBS31 <b>Note:</b> Default value is set to 0. |  |  |  |

| 1        | SLE_TX_LANE[n]_GEN_EN      | RW | Transmitter Pattern Generator Enable: 0: Disabled1: EnabledNote: Default value is set to 0.                    |  |  |  |

| 4        | SLE_RX_LANE[n]_PATTEN_CHK  | RW | Receiver Pattern Checker: 0: PRBS71: PRBS92: PRBS2 33: PRBS31 <b>Note:</b> Default value is set to 0.          |  |  |  |

| 1        | SLE_RX_LANE[n]_CHR_EN      | RW | Receiver Pattern Checker Enable: 0: Disabled1: EnabledNote: Default value is set to 0.                         |  |  |  |

| 32       | SLE_RX_LANE[n]_ERR_CNT     | R  | Receiver error counter.                                                                                        |  |  |  |

| 1        | SLE_RX_LANE[n]_ERR_CNT_CLR | RW | Receiver error counter clear button.                                                                           |  |  |  |

| 1        | SLE_RX_LANE[n]_ALIGN       | R  | Receiver channel aligned to pattern.                                                                           |  |  |  |

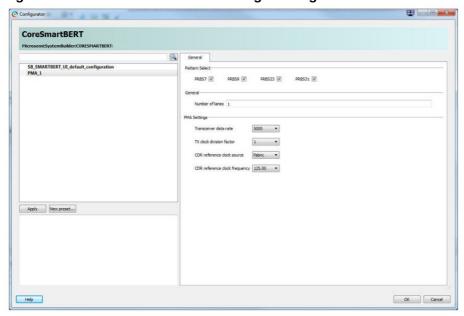

# Interface

This section discusses the parameters in the CoreSmartBERT GUI configurator and I/O signals.

# **Configuration GUI Parameters**

The following table describes the UI parameters for configuring the CoreSmartBERT core.

**Note:** The Name column shows the actual parameter name used in RTL. The Description column starts with parameter name as it appear in the CoreSmartBERT configurator (GUI interface). These two names are used interchangeably throughout the document.

**Table 3-1. CoreSmartBERT Parameters Descriptions**

| Name                         | Range                   | Defaul<br>t | Description                                                                                                                                              |

|------------------------------|-------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI_PATTERN_PRBS7             | 0 or 1                  | 1           | PRBS7Pattern Enable                                                                                                                                      |

| UI_PATTERN_PRBS9             | 0 or 1                  | 1           | PRBS9Pattern Enable                                                                                                                                      |

| UI_PATTERN_PRBS23            | 0 or 1                  | 1           | PRBS23Pattern Enable                                                                                                                                     |

| UI_PATTERN_PRBS31            | 0 or 1                  | 1           | PRBS31Pattern Enable                                                                                                                                     |

| UI_NUMBER_OF_LANES           | 1-4                     | 1           | Number of lanesNumber of lanes this I P core has enabled.                                                                                                |

| UI_DATA_RATE                 | 250 – 10000             | 5000        | Transceiver data rateSupported rates:• 250 Mbps• 1000 Mbps• 1250 M bps• 2500 Mbps• 3125 Mbps• 50 00 Mbps• 6250 Mbps• 8000 Mbps• 10000 Mbps• 10312.5 Mbps |

| UI_TX_CLK_DIV_FACTOR         | 1, 2, 4, 8 & 11         | 1           | TX clock division factor                                                                                                                                 |

| UI_CDR_REFERENCE_CLK_SOURC E | Dedicated or Fabri<br>c | Fabric      | CDR reference clock source                                                                                                                               |

| continued                 |         |             |                                                                                                                                                                |  |

|---------------------------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                      | Range   | Defaul<br>t | Description                                                                                                                                                    |  |

| UI_CDR_REFERENCE_CLK_FREQ | 0-312.5 | 125         | CDR reference clock frequencySupported frequencies: 25.00 MHz 31.2 5 MHz 50.00 MHz 62.50 MHz 75.00 MHz 100.00 MHz 125.00 MHz 150.00 MHz 156.25 MHz 3 12.50 MHz |  |

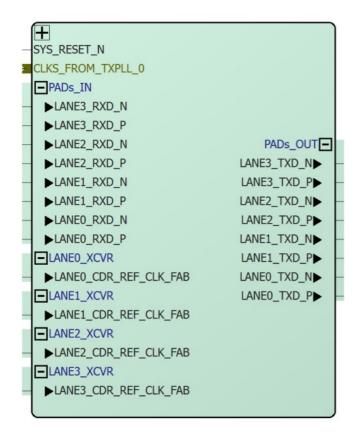

### I/O Signals

The following table describes the port signals for CoreSmartBERT.

**Note:** In the and following tables, n represents a range of 0 to 3 depending on the number of configured lanes.

# Table 3-2. CoreSmartBERT I/O Signal Descriptions

| Name                         | Widt<br>h | Directio<br>n | Description                                                                                                           |

|------------------------------|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| SYS_RESET_N                  | 1         | Input         | Active low system reset                                                                                               |

| LANE[n]_CDR_REF_CLK_FA<br>B  | 1         | Input         | CDR reference clock from fabric, only exposed when <b>Fabric</b> is selected as CDR reference clock source.           |

| LANE[n]_CDR_REF_CLK_0        | 1         | Input         | CDR reference clock from dedicated pin, only exposed when <b>Dedicated</b> is selected as CDR reference clock source. |

| LANE[n]_TX_BIT_CLK_0         | 1         | Input         | Tx Bit Clock                                                                                                          |

| LANE[n]_TX_PLL_REF_CLK_<br>0 | 1         | Input         | PLL Reference Clock                                                                                                   |

| LANE[n]_TX_PLL_LOCK_0        | 1         | Input         | PLL Lock                                                                                                              |

Table 3-3. CoreSmartBERT PAD Signal Descriptions

| Name          | Direction | Description             |  |

|---------------|-----------|-------------------------|--|

| LANE[n]_TXD_P | Output    | T " 0 : ID :            |  |

| LANE[n]_TXD_N | Output    | Transmitter Serial Data |  |

| LANE[n]_RXD_P | Input     | Receiver Serial Data    |  |

| Lane[n]_RXD_N | Input     | Heceivei Cenai Dala     |  |

# **Tool Flows**

This section discusses various tool flow related information.

# Licensing

CoreSmartBERT does not require any license.

### **RTL**

Complete RTL source code is provided for free with any Libero license.

# **SmartDesign**

CoreSmartBERT is available for download to the SmartDesign IP catalog through the Libero SOC web repository. To know how to create SmartDesign project, see SmartDesign User Guide.

The following figure shows an example of an instantiated view of CoreSmartBERT on the SmartDesign canvas.

Figure 4-1. Instantiation of CoreSmartBERT on SmartDesign Canvas

# **Configuring the CoreSmartBERT**

The following figures shows how the core instance can be configured using its configuration GUI.

Figure 4-2. CoreSmartBERT SmartDesign Configuration GUI

# Synthesising in Libero SoC

To run synthesis with the configuration selected in the configuration GUI, perform the following steps:

- 1. Set the design root appropriately.

- 2. Under Implement Design, in the Design Flow tab, right-click Synthesize, and then click Run.

# Running Place-and-Route in Libero SoC

To run the place and route, perform the following step:

• On the Design Flow tab, select Implement Design, right-click Place and Route, and then from the context menu, select Run.

# **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description                                                                                                                                                                                                            |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | 07/2022 | The following is the list of changes in revision A of the document:• The document was migrated to the Microchip template• Updated for CoreSmartBERT v2.9• The document number was updated to DS50003362A from 50200788 |

| 9.0      | 03/2021 | Updated for CoreSmartBERT v2.8.                                                                                                                                                                                        |

| 8.0      | 06/2020 | Updated for CoreSmartBERT v2.7.                                                                                                                                                                                        |

| 7.0      | 03/2020 | Updated for CoreSmartBERT v2.6.                                                                                                                                                                                        |

| 6.0      | 08/2019 | Updated for CoreSmartBERT v2.5.                                                                                                                                                                                        |

| 5.0      | 03/2019 | Updated for CoreSmartBERT v2.4.                                                                                                                                                                                        |

| 4.0      | 12/2018 | Updated for CoreSmartBERT v2.3.                                                                                                                                                                                        |

| 3.0      | 08/2018 | Updated for CoreSmartBERT v2.2.                                                                                                                                                                                        |

| 2.0      | 05/2018 | Updated for CoreSmartBERT v2.1.                                                                                                                                                                                        |

| 1.0      | 08/2017 | Initial release.                                                                                                                                                                                                       |

# **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at <a href="https://www.microchip.com/support">www.microchip.com/support</a>. Mention the FPGA Device

Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

### **Microchip Information**

# The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com">www.microchip.com</a>/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to <a href="https://www.microchip.com/pcn">www.microchip.com/pcn</a> and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code

protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright

Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly

evolving. Microchip is committed to continuously improving the code protection features of our products.

### **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services.">www.microchip.com/en-us/support/design-help/client-support-services.</a>

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM- ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA aretrademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2022, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-0763-2

### **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit <a href="www.microchip.com/quality.">www.microchip.com/quality.</a>

### **Worldwide Sales and Service**

### **AMERICAS**

### **Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

www.microchip.com/support

Web Address:

www.microchip.com

**Atlanta**Duluth, GA

**Tel:** 678-957-9614 **Fax:** 678-957-1455

Austin, TX

**Tel:** 512-257-3370

**Boston**

Westborough, MA **Tel:** 774-760-0087 **Fax:** 774-760-0088

Chicago Itasca, IL

**Tel:** 630-285-0071 **Fax:** 630-285-0075

**Dallas** Addison, TX

**Tel:** 972-818-7423 **Fax:** 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000 Houston, TX Tel: 281-894-5983 Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Tel: 317-536-2380

Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

Tel: 951-273-7800

Raleigh, NC

Tel: 919-844-7510 New York, NY Tel: 631-435-6000 San Jose, CA Tel: 408-735-9110

Tel: 408-436-4270 Canada – Toronto Tel: 905-695-1980 Fax: 905-695-2078

### ASIA/PACIFIC

Australia – Sydney Tel: 61-2-9868-6733 China – Beijing

Tel: 86-10-8569-7000 China – Chengdu Tel: 86-28-8665-5511 China – Chongqing Tel: 86-23-8980-9588 China – Dongguan Tel: 86-769-8702-9880 China – Guangzhou Tel: 86-20-8755-8029 China – Hangzhou

Tel: 86-571-8792-8115 China – Hong Kong SAR Tel: 852-2943-5100 China – Nanjing

Tel: 86-25-8473-2460 China – Qingdao Tel: 86-532-8502-7355 China – Shanghai Tel: 86-21-3326-8000 China – Shenyang

China – Shenyang Tel: 86-24-2334-2829 China – Shenzhen Tel: 86-755-8864-2200

China – Suzhou Tel: 86-186-6233-1526

China – Wuhan Tel: 86-27-5980-5300

China - Xian

Tel: 86-29-8833-7252 China – Xiamen Tel: 86-592-2388138 China – Zhuhai Tel: 86-756-3210040

ASIA/PACIFIC India – Bangalore

Tel: 91-80-3090-4444 India – New Delhi Tel: 91-11-4160-8631

India - Pune

Tel: 91-20-4121-0141 Japan – Osaka Tel: 81-6-6152-7160 Japan – Tokyo Tel: 81-3-6880- 3770

Korea – Daegu Tel: 82-53-744-4301 Korea – Seoul

Tel: 82-2-554-7200

Malaysia – Kuala Lumpur

Tel: 60-3-7651-7906 Malaysia – Penang Tel: 60-4-227-8870 Philippines – Manila Tel: 63-2-634-9065

Singapore

Tel: 65-6334-8870 Taiwan – Hsin Chu Tel: 886-3-577-8366 Taiwan – Kaohsiung Tel: 886-7-213-7830 Taiwan – Taipei

Tel: 886-2-2508-8600 Thailand – Bangkok Tel: 66-2-694-1351 Vietnam – Ho Chi Minh Tel: 84-28-5448-2100

### **Documents / Resources**

MICROCHIP CoreSmartBERT v2.9 Software [pdf] User Guide CoreSmartBERT, CoreSmartBERT v2.9 Software, Software

Manuals+,