### Home » MICROCHIP » MICROCHIP CoreFPU Core Floating Point Unit User Guide 📆

#### Contents [ hide ]

- 1 MICROCHIP CoreFPU Core Floating Point Unit

- 2 Introduction

- 3 1. Features

- 4 Functional Description

- 5 Implementation of CoreFPU in Libero Design Suite

- 6 Glossary

- 7 Device Resource Utilization and Performance

- 8 Revision History

- 9 Microchip Information

- 10 Documents / Resources

- 10.1 References

# **MICROCHIP CoreFPU Core Floating Point Unit**

### Introduction

- The Core Floating Point Unit (CoreFPU) is designed for floating-point arithmetic and conversion operations, for single and double precision floating-point numbers.

CoreFPU supports fixed-point to floating-point and floating-point to fixed-point conversions and floating-point addition, subtraction, and multiplication operations. The IEEE® Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for floating-point computation.

- Important: CoreFPU supports calculations with normalized numbers only, and only the Verilog language is supported; VHDL is not supported.

### **Summary**

The following table provides a summary of the CoreFPU characteristics.

**Table 1. CoreFPU Characteristics**

| Core Version                  | This document applies to CoreFPU v3.0.                                                                                                                                                                                                                                                                              |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supported Devi<br>ce Families | <ul> <li>PolarFire® SoC</li> <li>PolarFire</li> <li>RTG4™</li> </ul>                                                                                                                                                                                                                                                |

| Supported Tool<br>Flow        | Requires Libero® SoC v12.6 or later releases.                                                                                                                                                                                                                                                                       |

| Licensing                     | CoreFPU is not license locked.                                                                                                                                                                                                                                                                                      |

| Installation Instructions     | CoreFPU must be installed to the IP Catalog of Libero SoC automatically through the IP Catalog update function. Alternatively, CoreFPU could be manually downloaded from the catalog. Once the IP core is installed, it is configured, generated and instantiated within SmartD esign for inclusion in the project. |

| Device Utilizatio | A company of while the conduction and a sufficiency of the conduction for Cond EDI.                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| n and Performa    | A summary of utilization and performance information for CoreFPU is listed in Device Resource Utilization and Performance. |

### **CoreFPU Change Log Information**

This section provides a comprehensive overview of the newly incorporated features, beginning with the most recent release. For more information about the problems resolved, see the Resolved Issues section.

| Version | What's New                                                            |

|---------|-----------------------------------------------------------------------|

| v3.0    | Implemented additional output flags to enhance the accuracy of the IP |

| v2.1    | Added the double precision feature                                    |

| v2.0    | Updated the timing waveforms                                          |

| v1.0    | First production release of CoreFPU                                   |

#### 1. Features

CoreFPU has the following key features:

- Supports Single and Double Precision Floating Numbers as per IEEE-754 Standard

- Supports Conversions as listed:

- Fixed-point to Floating-point conversion

- Floating-point to Fixed-point conversion

- Supports Arithmetic Operations as listed:

- Floating-point addition

- $\circ \ \ \textbf{Floating-point subtraction}$

- Floating-point multiplication

- Provides the Rounding Scheme (Round to nearest even) for the Arithmetic Operations only

- Provides Flags for Overflow, Underflow, Infinity (Positive Infinity, Negative Infinity),

Quiet NaN (QNaN) and Signalling NaN (SNaN) for Floating-Point Numbers.

• Supports Fully pipelined implementation of Arithmetic Operations

• Provides Provision to configure the Core for Design Requirements

**Functional Description**

• The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for

floating-point computation. The term floating-point refers to the radix point of the

number (decimal point or binary point), which is placed anywhere with respect to the

significant digits of the number.

A floating-point number is typically expressed in the scientific notation, with a fraction

(F), and an exponent (E) of a certain radix (r), in the form of  $F \times r^*E$ . Decimal numbers

use radix of 10 (F  $\times$  10^E); while binary numbers use radix of 2 (F  $\times$  2^E).

• The representation of the floating-point number is not unique. For example, the

number 55.66 is represented as  $5.566 \times 10^{1}$ ,  $0.5566 \times 10^{2}$ ,  $0.05566 \times 10^{3}$ , and so

on. The fractional part is normalized. In the normalized form, there is only a single

non-zero digit before the radix point. For example, decimal number 123.4567 is

normalized as 1.234567 × 10<sup>2</sup>; binary number 1010.1011B is normalized as

$1.0101011B \times 2^3$ .

• It is important to note that floating-point numbers suffer from loss of precision when

represented with a fixed number of bits (for example, 32-bit or 64-bit). This is because

there are an infinite number of real numbers (even within a small range from 0.0 to

0.1). On the other hand, an

n- bit binary pattern represents a finite 2<sup>n</sup> distinct numbers. Hence, not all the real

numbers are represented. The nearest approximation is used instead, which results in

the loss of accuracy.

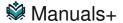

The single precision floating-point number is represented as follows:

• Sign bit: 1-bit

• Exponent width: 8 bits

• Significand precision: 24 bits (23 bits are explicitly stored)

Figure 2-1. 32-bit Frame

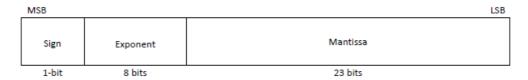

The double precision floating-point number is represented as follows:

• Sign bit: 1-bit

Exponent width: 11 bits

Significand precision: 53 bits (52 bits are explicitly stored)

Figure 2-2. 64-bit Frame

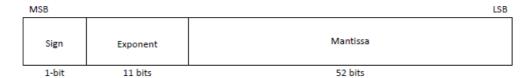

The CoreFPU is the top-level integration of the two conversion modules (Fixed to Float point and Float to Fixed point) and three arithmetic operations (FP ADD, FP SUB, and FP MULT). The user can configure any one of the operations based on the requirement so that the resources are utilized for the selected operation.

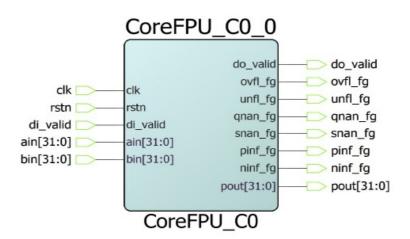

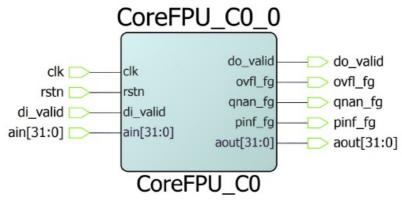

The following figure shows the top level CoreFPU block diagram with ports.

Figure 2-3. CoreFPU Ports Block Diagram

The following table lists the width of the Input and Output ports. Table 2-1. Input and Output Port Width

| Signal | Single Precision Width | Double Precision Width |

|--------|------------------------|------------------------|

| ain    | [31:0]                 | [63:0]                 |

| bin    | [31:0]                 | [63:0]                 |

| aout   | [31:0]                 | [63:0]                 |

| pout   | [31:0]                 | [63:0]                 |

## **Fixed-Point to Floating-Point (Conversion)**

CoreFPU configured as fixed to floating-point infers the fixed-point to floating-point conversion module. The input (ain) to CoreFPU is any fixed-point number containing the integer and fractional bits. The CoreFPU configurator has the options to select the input integer and fraction widths. The input is valid on di\_valid signal and output is valid on do\_valid. The output (aout) of the fixed to float operation is in single or double precision floating-point format.

Example for fixed-point to floating-point conversion operation is listed in the following table.

Table 2-2. Example for Fixed-Point to Floating-Point Conversion

| Fixed-Point Number         |                   |                             | Floating-Point Number |          |                  |                     |

|----------------------------|-------------------|-----------------------------|-----------------------|----------|------------------|---------------------|

| ain                        | Integer           | Fracti<br>on                | aout                  | Si<br>gn | Ex<br>pon<br>ent | Mantissa            |

| 0x121<br>53524<br>(32-bit) | 00010010000101010 | 0110<br>1010<br>0100<br>100 | 0x461<br>0a9a9        | 0        | 100<br>011<br>00 | 0010000101010011010 |

| 0x000<br>00000<br>00008<br>CCC<br>(64-bit) | 000000000000000000<br>0000000000000000000 | 0001<br>1001<br>1001<br>100 | 0x3FF<br>19999<br>99999<br>99A | 0 | 011<br>111<br>111<br>11 | 0001100110011001100<br>1100110011001100110 |

|--------------------------------------------|-------------------------------------------|-----------------------------|--------------------------------|---|-------------------------|--------------------------------------------|

|--------------------------------------------|-------------------------------------------|-----------------------------|--------------------------------|---|-------------------------|--------------------------------------------|

## **Floating-Point to Fixed-Point (Conversion)**

CoreFPU configured as floating to fixed-point infers the floating-point to fixed-point conversion module. The input (ain) to CoreFPU is any single or double precision floating-point number and produces an output (aout) in fixed-point format containing integer and fractional bits. The input is valid on di\_valid signal and output is valid on do\_valid. The CoreFPU configurator has the options to select the output integer and fraction widths. Example for floating-point to fixed-point conversion operation is listed in the following table.

**Table 2-3. Example for Floating-Point to Fixed-Point Conversion**

| Floating-Point Number     |          |                  | ber                         | Fixed-Point Number |                  |                             |

|---------------------------|----------|------------------|-----------------------------|--------------------|------------------|-----------------------------|

| ain                       | Si<br>gn | Ex<br>pon<br>ent | Mantissa                    | aout               | Integer          | Fracti                      |

| 0x41b<br>d6783<br>(32-bit | 0        | 100<br>000<br>11 | 0111101011001111000<br>0011 | 0x000<br>bd678     | 0000000000010111 | 1010<br>1100<br>1111<br>000 |

| 0x400<br>2094c<br>447c3<br>0d3<br>(64-bit | 0 100<br>000<br>000<br>000 | 0010000010010100110<br>0010001000111110000<br>11000011010011 | 0x000<br>00000<br>00012<br>095 | 00000000000000000000000000000000000000 | 0100<br>0001<br>0010<br>101 |

|-------------------------------------------|----------------------------|--------------------------------------------------------------|--------------------------------|----------------------------------------|-----------------------------|

|-------------------------------------------|----------------------------|--------------------------------------------------------------|--------------------------------|----------------------------------------|-----------------------------|

### Floating-Point Addition (Arithmetic Operation)

CoreFPU configured as FP ADD infers the floating-point addition module. It adds the two floating-point numbers (ain and bin) and provides the output (pout) in floating-point format. The input and output are single or double precision floating-point numbers. The input is valid on di\_valid signal and output is valid on do\_valid. The core produce ovfl\_fg (Overflow), qnan\_fg (Quiet Not a Number), snan\_fg (Signalling Not a Number), pinf\_fg(Positive Infinity), and ninf\_fg (Negative Infinity) flags based on the addition operation.

Examples for floating-point addition operation are listed in the following tables.

Table 2-4. Example for Floating-Point Addition Operation (32-bit)

| Floating-Point Value                             | Sig<br>n | Exponent | Mantissa                |

|--------------------------------------------------|----------|----------|-------------------------|

| Floating-point input 1 ain (0x4e989680)          | 0        | 10011101 | 00110001001011010000000 |

| Floating-point input 2 bin (0x4f19 1b40)         | 0        | 10011110 | 00110010001101101000000 |

| Floating-point addition output pout (0x4f656680) | 0        | 10011110 | 11001010110011010000000 |

Table 2-5. Example for Floating-Point Addition Operation (64-bit)

| Floating-Point Value                                       | Si<br>gn | Expone<br>nt    | Mantissa                                                 |

|------------------------------------------------------------|----------|-----------------|----------------------------------------------------------|

| Floating-point input 1 ain (0x3ff4106ee30c aa32)           | 0        | 0111111<br>1111 | 0100000100000110111011100011000011001<br>010101000110010 |

| Floating-point input 2 bin (0x40020b2a787 98e61)           | 0        | 1000000         | 001000001011001010101111000011110011<br>000111001100001  |

| Floating-point addition noutput pout (0x400 c1361e9ffe37a) | 0        | 1000000<br>0000 | 110000010011011000011110100111111111111                  |

### Floating-Point Subtraction (Arithmetic Operation)

CoreFPU configured as FP SUB infers the floating-point subtraction module. It subtracts the two floating-point numbers (ain and bin) and provides the output (pout) in floating-point format. The input and output are single or double precision floating-point numbers. The input is valid on di\_valid signal and output is valid on do\_valid. The core produce ovfl\_fg (Overflow), unfl\_fg (underflow), qnan\_fg (Quiet Not a Number), snan\_fg (Signalling Not a Number), pinf\_fg (Positive Infinity), and ninf\_fg (Negative Infinity) flags based on the subtraction operation.

Examples for floating-point subtraction operation are listed in the following tables. Table 2-6. Example for Floating-Point Subtraction Operation (32-bit)

| Floating-Point Value                     | Sig<br>n | Exponent | Mantissa                |

|------------------------------------------|----------|----------|-------------------------|

| Floating-point input 1 ain (0xac854 65f) | 1        | 01011001 | 00001010100011001011111 |

| Floating-point input 2 bin (0x2f5167 79)             | 0 | 01011110 | 10100010110011101111001 |

|------------------------------------------------------|---|----------|-------------------------|

| Floating-point subtraction output po ut (0xaf5591ac) | 1 | 01011110 | 10101011001000110101011 |

| Floating-Point Value                                         | Si<br>gn | Expone nt       | Mantissa                                                 |

|--------------------------------------------------------------|----------|-----------------|----------------------------------------------------------|

| Floating-point input 1 ain (0x405569764adff823)              | 0        | 100000<br>00101 | 010101101001011101100100101011011111<br>1111100000100011 |

| Floating-point input 2 bin (0x4057d04e78dee3fc )             | 0        | 100000<br>00101 | 011111010000010011100111100011011110<br>111000111111     |

| Floating-point subtraction output pou t (0xc02336c16ff75ec8) | 1        | 100000<br>00010 | 00110011011011000001011011111111111111                   |

## Floating-Point Multiplication (Arithmetic Operation)

CoreFPU configured as FP MULT infers the floating-point multiplication module. It multiplies the two floating-point numbers (ain and bin) and provides the output (pout) in floating-point format. The input and output are single or double precision floating-point numbers. The input is valid on di\_valid signal and output is valid on do\_valid. The core produce ovfl\_fg (Overflow), unfl\_fg (Underflow), qnan\_fg (Quiet Not a Number), snan\_fg (Signalling Not a Number), pinf\_fg (Positive Infinity), and ninf\_fg (Negative Infinity) flags based on the multiplication operation.

Examples for floating-point multiplication operation are listed in the following tables.

Table 2-8. Example for Floating-Point Multiplication Operation (32-bit)

| Floating-Point Value                                    | Sig<br>n | Exponent | Mantissa                |

|---------------------------------------------------------|----------|----------|-------------------------|

| Floating-point input 1 ain (0x1ec7a7 35)                | 0        | 0011110  | 10001111010011100110101 |

| Floating-point input 2 bin (0x6ecf15e 8)                | 0        | 1101110  | 10011110001010111101000 |

| Floating-point Multiplication output p out (0x4e21814a) | 0        | 1001110  | 01000011000000101001010 |

| Floating-Point Value                                                   | Si<br>gn | Expone          | Mantissa                                                 |

|------------------------------------------------------------------------|----------|-----------------|----------------------------------------------------------|

| Floating-point input 1 ain (0x40c1f5a9930be0 df)                       | 0        | 100000<br>01100 | 0001111101011010011001001100001011<br>1110000011011      |

| Floating-point input 2 bin (0x400a0866c962b501)                        | 0        | 100000<br>00000 | 101000001000011001101100100101100010<br>101101           |

| Floating-point multiplica<br>tion output pout (0x40d<br>d38a1c3e2cae9) | 0        | 100000<br>01101 | 110100111000101000011100001111100010<br>1100101011101001 |

#### **Truth Table for Addition and Subtraction**

The following truth tables list the values for addition and subtraction operation. Table 2-10. Truth Table for Addition

| Data A           | Data B           | Sign<br>Bit | Result          | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |

|------------------|------------------|-------------|-----------------|--------------|---------------|----------|----------|----------|----------|

| QNaN/S<br>NaN    | х                | 0           | POSQN<br>aN     | 0            | 0             | 0        | 1        | 0        | 0        |

| x                | QNaN/S<br>NaN    | 0           | POSQN<br>aN     | 0            | 0             | 0        | 1        | 0        | 0        |

| zero             | zero             | 0           | POSZE<br>RO     | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | posfinite(<br>y) | 0           | posfinite (y)   | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | negfinite(       | 1           | negfinite (y)   | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | posinfinit<br>e  | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| zero             | neginfinit<br>e  | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |

| posfinite(<br>y) | zero             | 0           | posfinite (y)   | 0            | 0             | 0        | 0        | 0        | 0        |

| posfinite        | posinfinit<br>e  | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| Table 2-10. Truth Table for Addition (continued) |                 |             |                 |              |               |          |          |          |          |  |

|--------------------------------------------------|-----------------|-------------|-----------------|--------------|---------------|----------|----------|----------|----------|--|

| Data A                                           | Data B          | Sign<br>Bit | Result          | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |  |

| posfinite                                        | neginfinit<br>e | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |  |

| negfinite(      | zero            | 1 | negfinite<br>(y) | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------------|-----------------|---|------------------|---|---|---|---|---|---|

| negfinite       | posinfinit<br>e | 0 | posinfini<br>te  | 0 | 0 | 0 | 0 | 1 | 0 |

| negfinite       | neginfinit<br>e | 1 | neginfini<br>te  | 0 | 0 | 0 | 0 | 0 | 1 |

| posinfinit<br>e | zero            | 0 | posinfini<br>te  | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | posfinite       | 0 | posinfini<br>te  | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | negfinite       | 0 | posinfini<br>te  | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | posinfinit<br>e | 0 | posinfini<br>te  | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | neginfinit<br>e | 0 | POSQN<br>aN      | 0 | 0 | 0 | 1 | 0 | 0 |

| neginfinit<br>e | zero            | 1 | neginfini<br>te  | 0 | 0 | 0 | 0 | 0 | 1 |

| neginfinit<br>e | posfinite       | 1 | neginfini<br>te  | 0 | 0 | 0 | 0 | 0 | 1 |

| neginfinit<br>e | negfinite       | 1 | neginfini<br>te  | 0 | 0 | 0 | 0 | 0 | 1 |

| neginfinit<br>e | posinfinit<br>e | 0 | POSQN<br>aN      | 0 | 0 | 0 | 1 | 0 | 0 |

| neginfinit<br>e | neginfinit<br>e | 1 | neginfini<br>te  | 0 | 0 | 0 | 0 | 0 | 1 |

| posfinite | posfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------|-----------|-----|-----------------|---|---|---|---|---|---|

| posfinite | posfinite | 0   | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posfinite | posfinite | 0/1 | QNaN            | 0 | 0 | 0 | 1 | 0 | 0 |

| posfinite | posfinite | 0/1 | SNaN            | 0 | 0 | 1 | 0 | 0 | 0 |

| posfinite | posfinite | 0   | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| posfinite | negfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite | negfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite | negfinite | 0   | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | posfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | posfinite | 0   | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| negfinite | negfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | negfinite | 1   | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| negfinite | negfinite | 0/1 | QNaN            | 0 | 0 | 0 | 1 | 0 | 0 |

| negfinite | negfinite | 0/1 | SNaN            | 0 | 0 | 1 | 0 | 0 | 0 |

| negfinite | negfinite | 0   | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| Data A           | Data B           | Sign<br>Bit | Result           | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |

|------------------|------------------|-------------|------------------|--------------|---------------|----------|----------|----------|----------|

| QNaN/S<br>NaN    | х                | 0           | POSQN<br>aN      | 0            | 0             | 0        | 1        | 0        | 0        |

| X                | QNaN/S<br>NaN    | 0           | POSQN<br>aN      | 0            | 0             | 0        | 1        | 0        | 0        |

| zero             | zero             | 0           | POSZE<br>RO      | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | posfinite(<br>y) | 1           | negfinite (y)    | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | negfinite(       | 0           | posfinite (y)    | 0            | 0             | 0        | 0        | 0        | 0        |

| zero             | posinfinit<br>e  | 1           | neginfini<br>te  | 0            | 0             | 0        | 0        | 0        | 1        |

| zero             | neginfinit<br>e  | 0           | posinfini<br>te  | 0            | 0             | 0        | 0        | 1        | 0        |

| posfinite(<br>y) | zero             | 0           | posfinite (y)    | 0            | 0             | 0        | 0        | 0        | 0        |

| posfinite        | posinfinit<br>e  | 1           | neginfini<br>te  | 0            | 0             | 0        | 0        | 0        | 1        |

| posfinite        | neginfinit<br>e  | 0           | posinfini<br>te  | 0            | 0             | 0        | 0        | 1        | 0        |

| negfinite(       | zero             | 1           | negfinite<br>(y) | 0            | 0             | 0        | 0        | 0        | 0        |

| negfinite        | posinfinit<br>e  | 1           | neginfini<br>te  | 0            | 0             | 0        | 0        | 0        | 1        |

| Table 2-11 | Table 2-11. Truth Table for Subtraction (continued)  Data A Data B Sign Result W W 2N 2N 2N NE N |      |        |         |          |    |    |    |   |

|------------|--------------------------------------------------------------------------------------------------|------|--------|---------|----------|----|----|----|---|

| Doto A     | Data P                                                                                           | Sign | Popult | Overflo | Underflo | SN | QN | PI | N |

| Dala A     | Dala B                                                                                           | Bit  | nesuit | w       | w        | aN | aN | NF | N |

| Data A          | Data B          | Sign<br>Bit | Result          | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |

|-----------------|-----------------|-------------|-----------------|--------------|---------------|----------|----------|----------|----------|

| negfinite       | neginfinit<br>e | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| posinfinit<br>e | zero            | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| posinfinit<br>e | posfinite       | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| posinfinit<br>e | negfinite       | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| posinfinit<br>e | posinfinit<br>e | 0           | POSQN<br>aN     | 0            | 0             | 0        | 1        | 0        | 0        |

| posinfinit<br>e | neginfinit<br>e | 0           | posinfini<br>te | 0            | 0             | 0        | 0        | 1        | 0        |

| neginfinit<br>e | zero            | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |

| neginfinit<br>e | posfinite       | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |

| neginfinit<br>e | negfinite       | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |

| neginfinit<br>e | posinfinit<br>e | 1           | neginfini<br>te | 0            | 0             | 0        | 0        | 0        | 1        |

| neginfinit<br>e | neginfinit<br>e | 0           | POSQN<br>aN     | 0            | 0             | 0        | 1        | 0        | 0        |

| posfinite | posfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------|-----------|-----|-----------------|---|---|---|---|---|---|

| posfinite | posfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite | posfinite | 0   | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| posfinite | negfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite | negfinite | 0   | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posfinite | negfinite | 0/1 | QNaN            | 0 | 0 | 0 | 1 | 0 | 0 |

| posfinite | negfinite | 0/1 | SNaN            | 0 | 0 | 1 | 0 | 0 | 0 |

| posfinite | negfinite | 0   | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | posfinite | 1   | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| negfinite | posfinite | 0/1 | QNaN            | 0 | 0 | 0 | 1 | 0 | 0 |

| negfinite | posfinite | 0/1 | SNaN            | 0 | 0 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 0   | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| negfinite | negfinite | 0   | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | negfinite | 1   | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | negfinite | 0   | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

- They in the preceding tables denotes any number.

- The in the preceding tables denotes a don't care condition.

## **Truth Table for Multiplication**

The following truth table lists the values for multiplication operation.

**Table 2-12. Truth Table for Multiplication**

| Data A        | Data B          | Sign<br>Bit | Result      | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |

|---------------|-----------------|-------------|-------------|--------------|---------------|----------|----------|----------|----------|

| QNaN/S<br>NaN | х               | 0           | POSQN<br>aN | 0            | 0             | 0        | 1        | 0        | 0        |

| Х             | QNaN/S<br>NaN   | 0           | POSQN<br>aN | 0            | 0             | 0        | 1        | 0        | 0        |

| zero          | zero            | 0           | POSZE<br>RO | 0            | 0             | 0        | 0        | 0        | 0        |

| zero          | posfinite       | 0           | POSZE<br>RO | 0            | 0             | 0        | 0        | 0        | 0        |

| zero          | negfinite       | 0           | POSZE<br>RO | 0            | 0             | 0        | 0        | 0        | 0        |

| zero          | posinfinit<br>e | 0           | POSQN<br>aN | 0            | 0             | 0        | 1        | 0        | 0        |

| zero          | neginfinit<br>e | 0           | POSQN<br>aN | 0            | 0             | 0        | 1        | 0        | 0        |

| Table 2-12 | . Truth Table | for Mult    | iplication (d | continued)   | )             |          |          |          |          |

|------------|---------------|-------------|---------------|--------------|---------------|----------|----------|----------|----------|

| Data A     | Data B        | Sign<br>Bit | Result        | Overflo<br>w | Underflo<br>w | SN<br>aN | QN<br>aN | PI<br>NF | NI<br>NF |

| posfinite       | zero 0          |   | POSZE<br>RO     | 0 | 0 | 0 | 0 | 0 | 0 |

|-----------------|-----------------|---|-----------------|---|---|---|---|---|---|

| posfinite       | posinfinit<br>e | 0 | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posfinite       | neginfinit<br>e | 1 | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| negfinite       | zero            | 0 | POSZE<br>RO     | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite       | posinfinit<br>e | 1 | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| negfinite       | neginfinit<br>e | 0 | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | zero            | 0 | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| posinfinit<br>e | posfinite       | 0 | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | negfinite       | 1 | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| posinfinit<br>e | posinfinit<br>e | 0 | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posinfinit<br>e | neginfinit<br>e | 1 | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| neginfinit<br>e | zero            | 0 | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| neginfinit<br>e | posfinite       | posfinite 1 |                 | 0 | 0 | 0 | 0 | 0 | 1 |

|-----------------|-----------------|-------------|-----------------|---|---|---|---|---|---|

| neginfinit<br>e | negfinite       | 0           | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| neginfinit<br>e | posinfinit<br>e | 1           | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| neginfinit<br>e | neginfinit<br>e | 0           | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posfinite       | posfinite       | 0           | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite       | posfinite       | 0           | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| posfinite       | posfinite       | 0           | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| posfinite       | posfinite       | 0           | POSSN<br>aN     | 0 | 0 | 1 | 0 | 0 | 0 |

| posfinite       | posfinite       | 0           | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| posfinite       | posfinite       | 0           | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| posfinite       | negfinite       | 1           | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| posfinite       | negfinite       | 1           | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| posfinite       | negfinite       | 0           | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| posfinite | negfinite | 0 | POSSN<br>aN     | 0 | 0 | 1 | 0 | 0 | 0 |

|-----------|-----------|---|-----------------|---|---|---|---|---|---|

| posfinite | negfinite | 0 | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| posfinite | negfinite | 0 | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 1 | negfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | posfinite | 1 | neginfini<br>te | 0 | 0 | 0 | 0 | 0 | 1 |

| negfinite | posfinite | 0 | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| negfinite | posfinite | 0 | POSSN<br>aN     | 0 | 0 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 0 | POSSN<br>aN     | 1 | 0 | 1 | 0 | 0 | 0 |

| negfinite | posfinite | 0 | POSSN<br>aN     | 0 | 1 | 1 | 0 | 0 | 0 |

| negfinite | negfinite | 0 | posfinite       | 0 | 0 | 0 | 0 | 0 | 0 |

| negfinite | negfinite | 0 | posinfini<br>te | 0 | 0 | 0 | 0 | 1 | 0 |

| negfinite | negfinite | 0 | POSQN<br>aN     | 0 | 0 | 0 | 1 | 0 | 0 |

| negfinite | negfinite | 0 | POSQN<br>aN     | 0 | 0 | 1 | 0 | 0 | 0 |

| negfinite | negfinite | 0 | POSQN<br>aN | 1 | 0 | 1 | 0 | 0 | 0 |

|-----------|-----------|---|-------------|---|---|---|---|---|---|

| negfinite | negfinite | 0 | POSQN<br>aN | 0 | 1 | 1 | 0 | 0 | 0 |

Sign Bit '0' defines positive output and '1' defines negative output.

The x in the preceding table denotes don't care condition.

## **CoreFPU Parameters and Interface Signals**

This section discusses the parameters in the CoreFPU Configurator settings and I/O signals.

### **Configuration GUI Parameters**

There are number of configurable options that apply to the FPU unit as shown in the following table. If a configuration other than default is required, configuration dialog box is used to select appropriate values for the configurable option.

Table 3-1. CoreFPU Configuration GUI Parameters

| Parameter Na<br>me | Default | Description                                                           |

|--------------------|---------|-----------------------------------------------------------------------|

| Precision          | Single  | Select the operation as required:  Single Precision  Double Precision |

| Conversion Ty<br>pe    | Fixed-point to Floating-p oint conversion | <ul> <li>Select the operation as required:</li> <li>Fixed-point to Floating-point conversion</li> <li>Floating-point to Fixed-point conversion</li> <li>Floating-point addition</li> <li>Floating-point subtraction</li> <li>Floating-point multiplication</li> </ul> |

|------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Fraction Width1  | 15                                        | Configures the fractional point in the Input ain and bin signals  Valid range is 31–1                                                                                                                                                                                 |

| Output Fraction Midth2 | 15                                        | Configures the fractional point in the Outp ut aout signals  Valid range is 51–1                                                                                                                                                                                      |

- 1. This parameter is configurable only during fixed-point to floating-point conversion.

- 2. This parameter is configurable only during floating-point to fixed-point conversion.

# Input and Output Signals (Ask a Question)

The following table lists the input and output port signals of CoreFPU.

**Table 3-2. Port Description**

| Signal | Wi  | Ty        | Description       |

|--------|-----|-----------|-------------------|

| Name   | dth | pe        |                   |

| clk    | 1   | Inp<br>ut | Main system clock |

| rstn         | 1         | Inp<br>ut      | Active-low asynchronous reset                                                                                                   |

|--------------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

| di_vali<br>d | 1         | Inp            | Active-high input valid  This signal indicates that the data present on ain[31:0], ain[63:0] and bin[31:0], bin[63:0] is valid. |

| ain          | 32/<br>64 | Inp<br>ut      | A Input Bus (It is used for all operations)                                                                                     |

| bin <u>1</u> | 32/<br>64 | Inp<br>ut      | B Input Bus (It is used for arithmetic operations only)                                                                         |

| aout2        | 32/       | Ou<br>tpu<br>t | Output value when fixed to floating-point or floating to fixed-point conversion operations are selected.                        |

| pout1        | 32/<br>64 | Ou<br>tpu<br>t | Output value when addition, subtraction, or multiplication operations are selected.                                             |

| Table 3-       | Table 3-2. Port Description (continued) |                |                                                                                                 |  |  |  |  |  |  |

|----------------|-----------------------------------------|----------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Signal<br>Name | Wi<br>dth                               | Ty<br>pe       | Description                                                                                     |  |  |  |  |  |  |

| do_vali<br>d   | 1                                       | Ou<br>tpu<br>t | Active-high signal  This signal indicates that the data present on pout/aout data bus is valid. |  |  |  |  |  |  |

| ovfl_fg 3 | 1 | Ou<br>tpu<br>t | Active-high signal  This signal indicates the overflow during floating-point operation s.                      |

|-----------|---|----------------|----------------------------------------------------------------------------------------------------------------|

| unfl_fg   | 1 | Ou<br>tpu<br>t | Active-high signal  This Signal indicates the underflow during floating point operations.                      |

| qnan_f    | 1 | Ou<br>tpu<br>t | Active-high signal  This signal indicates the Quiet Not a Number (QNaN) during floa ting-point operations.     |

| snan_f    | 1 | Ou<br>tpu<br>t | Active-high signal  This signal indicates the Signalling Not-a-Number (SNaN) during floating point operations. |

| pinf_fg   | 1 | Ou<br>tpu<br>t | Active-high signal  This signal indicates the positive infinity during floating-point ope rations.             |

| ninf_fg   | 1 | Ou<br>tpu<br>t | Active-high signal  This signal indicates the negative infinity during floating-point op erations.             |

- 1. This port is available only for floating-point addition, subtraction, or multiplication operations.

- 2. This port is available only for fixed-point to floating-point and floating-point to fixed-

- point conversion operations.

- 3. This port is available for floating-point to fixed-point, floating-point addition, floating-point subtraction, and floating-point multiplication.

## Implementation of CoreFPU in Libero Design Suite

This section describes the implementation of CoreFPU in the Libero Design Suite.

### **SmartDesign**

CoreFPU is available for download in the Libero IP catalog through the web repository. Once it is listed in the catalog, the core is instantiated using the SmartDesign flow. For information on using SmartDesign to configure, connect, and generate cores, see Libero SoC online help.

After configuring and generating the core instance, the basic functionality is simulated using the testbench supplied with the CoreFPU. The testbench parameters automatically adjust to the CoreFPU configuration. The CoreFPU is instantiated as a component of a larger design.

Figure 4-1. SmartDesign CoreFPU Instance for Arithmetic Operations

Figure 4-2. SmartDesign CoreFPU Instance for Conversion Operation

### **Fixed-Point to Floating-Point Conversion**

During fixed-point to floating-point conversion, the Input Fraction Width is configurable. The Output Width is set to 32-bit for single precision and 64-bit for double precision floating-point by default.

To convert from fixed-point to floating-point, select Fixed to floating point Conversion type, as shown in the following figure.

### Floating-Point to Fixed-Point

During floating-point to fixed-point conversion, the Output Fractional Width is configurable, and the Input Width is set to 32-bit for single precision and 64-bit for double precision floating-point by default.

To convert from floating-point to fixed-point, select Floating point to fixed Conversion type, as shown in the following figure.

Figure 4-4. CoreFPU Configurator for Floating Point to Fixed

### Floating-Point Addition/Subtraction/Multiplication

During floating-point addition, subtraction, and multiplication operation, the Input Fraction Width and Output Fraction Width are not configurable as these are floating-point arithmetic operations, and the Input/Output Width is set to 32-bit single precision and 64-bit for double precision floating-point by default.

The following figure shows the CoreFPU configurator for floating point subtraction operation.

Figure 4-5. CoreFPU Configurator for Floating Point Subtraction

## Simulation (Ask a Question)

To run simulations, in the core configuration window, select User Testbench. After generating the CoreFPU, the pre-synthesis testbench Hardware Description Language (HDL) files are installed in Libero.

## Simulation Waveforms (Ask a Question)

This section discusses the simulation waveforms for CoreFPU.

The following figures show the waveform of fixed-point to floating-point conversion for both 32-bit and 64-bit.

Figure 4-6. Fixed-Point to Floating-Point Conversion (32-bit)

Figure 4-7. Fixed-Point to Floating-Point Conversion (64-bit)

Figure 4-8. Floating-Point to Fixed-Point Conversion (32-bit)

Figure 4-9. Floating-Point to Fixed-Point Conversion (64-bit)

The following figures show the waveform of floating-point addition operation for both 32-bit and 64-bit.

Figure 4-10. Floating-Point Addition (32-bit)

Figure 4-11. Floating-Point Addition (64-bit)

Figure 4-12. Floating-Point Subtraction (32-bit)

Figure 4-13. Floating-Point Subtraction (64-bit)

Figure 4-14. Floating-Point Multiplication (32-bit)

Figure 4-15. Floating-Point Multiplication (64-bit)

### **System Integration**

The following figure shows an example of using the core. In this example, the design UART is used as a communication channel between the design and the host PC. The signals ain and bin (each of 32-bit or 64-bit width) are the inputs to the design from UART. After the CoreFPU receives the di\_valid signal, it computes the result. After computing the result, the do\_valid signal goes high and stores the result (aout/pout data) in the output buffer. This same procedure is applicable for conversion and arithmetic operations. For conversion operations, only input ain is sufficient whereas for arithmetic operations, both ain and bin inputs are required. Output aout is enabled for conversion operations and pout port is enabled for arithmetic operations.

Figure 4-16. Example of the CoreFPU System

Figure 4-16. Example of the CoreFPU System

## 1. Synthesis (Ask a Question)

To run synthesis on the CoreFPU, set the design root to the IP component instance and from the Libero design flow pane, run the Synthesis tool.

Place and Route (Ask a Question)

After the design is synthesized, run the Place-and-Route tool. CoreFPU requires no special placeand- route settings.

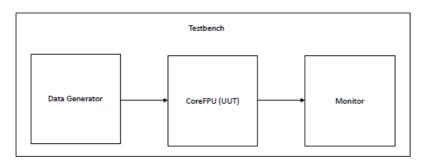

2. User Testbench (Ask a Question)

A user testbench is provided with the CoreFPU IP release. Using this testbench, you can verify functional behavior of CoreFPU.

A simplified block diagram of the user testbench is shown in the following figure. The user testbench instantiates the Configured CoreFPU design (UUT), and includes behavioral test data generator, necessary clock, and reset signals.

Figure 4-17. CoreFPU User Testbench

Figure 4-17. CoreFPU User Testbench

Important: You have to monitor the output signals in ModelSim simulator, see Simulation section.

### **Additional References (Ask a Question)**

This section provides a list for additional information.

For updates and additional information about the software, devices, and hardware, visit the

### Intellectual Property pages on the Microchip FPGAs and PLDs website.

- Known Issues and Workarounds (Ask a Question)

There are no known issues and workarounds for CoreFPU v3.0.

- Discontinued Features and Devices (Ask a Question)

There are no discontinued features and devices with this IP release.

## Glossary

The following are the list of terms and definitions used in the document.

Table 6-1. Terms and Definitions

| Term    | Definition                    |

|---------|-------------------------------|

| FPU     | Floating Point Unit           |

| FP ADD  | Floating-Point Addition       |

| FP SUB  | Floating-Point Subtraction    |

| FP MULT | Floating-Point Multiplication |

#### **Resolved Issues**

The following table lists all the resolved issues for the various CoreFPU releases.

#### Table 7-1. Resolved Issues

| Rel<br>eas<br>e | Description                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.0             | The following is the list of all resolved issues in the v3.0 release:  Case Number: 01420387 and 01422128  Added the rounding scheme logic (round to the nearest even number).                                                                               |

| 2.1             | The following is the list of all resolved issues in the v2.1 release:  The design encounters issues due to the presence of duplicate modules when multiple cores are instantiated.  Renaming the CoreFPU IP instance results in an "Undefined module" error. |

| 1.0             | Initial Release                                                                                                                                                                                                                                              |

## **Device Resource Utilization and Performance**

The CoreFPU macro is implemented in the families listed in the following table.

Table 8-1. FPU PolarFire Unit Device Utilization for 32-Bit

| FPGA Res                      | source                        | s        |           |           | Utilization |                |                 |        |

|-------------------------------|-------------------------------|----------|-----------|-----------|-------------|----------------|-----------------|--------|

| Family                        | 4L<br>UT                      | DF<br>F  | Tot<br>al | Math Bloc | Device      | Percentag<br>e | Performanc<br>e | Latenc |

| Fixed-Point to Floating-Point |                               |          |           |           |             |                |                 |        |

| PolarFir<br>e®                | 260                           | 10<br>4  | 364       | 0         | MPF30<br>0T | 0.12           | 310 MHz         | 3      |

| Floating-P                    | oint to                       | Fixed    | l-Point   |           |             |                |                 |        |

| PolarFir<br>e                 | 591                           | 10<br>2  | 693       | 0         | MPF30<br>0T | 0.23           | 160 MHz         | 3      |

| Floating-P                    | oint A                        | dditior  | า         |           |             |                |                 |        |

| PolarFir<br>e                 | 157<br>5                      | 15<br>51 | 312<br>6  | 0         | MPF30<br>0T | 1.06           | 340 MHz         | 16     |

| Floating-P                    | oint S                        | ubtrac   | tion      |           |             |                |                 |        |

| PolarFir<br>e                 | 156<br>1                      | 15<br>49 | 311<br>0  | 0         | MPF30<br>0T | 1.04           | 345 MHz         | 16     |

| Floating-P                    | Floating-Point Multiplication |          |           |           |             |                |                 |        |

| PolarFir<br>e                 | 465                           | 84<br>7  | 131<br>2  | 4         | MPF30<br>0T | 0.44           | 385 MHz         | 14     |

| FPGA                          | Resoul   | rces    |           |           | Utilization |  |  |  |  |

|-------------------------------|----------|---------|-----------|-----------|-------------|--|--|--|--|

| Famil<br>y                    | 4LU<br>T | DF<br>F | Tot<br>al | Math Bloc | Device      |  |  |  |  |

| Fixed-Point to Floating-Point |          |         |           |           |             |  |  |  |  |

|          |                               |          | 1        |    |             |      |         |    |

|----------|-------------------------------|----------|----------|----|-------------|------|---------|----|

| RTG4     | 264                           | 104      | 368      | 0  | RT4G1<br>50 | 0.24 | 160 MHz | 3  |

| Floating | g-Point                       | to Fix   | ed-Poi   | nt |             |      |         |    |

| RTG4     | 439                           | 112      | 551      | 0  | RT4G1<br>50 | 0.36 | 105 MHz | 3  |

| Floating | g-Point                       | Addit    | ion      |    |             |      |         |    |

| RTG4     | 173<br>3                      | 155<br>1 | 328<br>4 | 0  | RT4G1<br>50 | 1.16 | 195 MHz | 16 |

| Floating | g-Point                       | Subtr    | action   |    |             |      |         |    |

| RTG4     | 172<br>9                      | 154<br>9 | 325<br>8 | 0  | RT4G1<br>50 | 1.16 | 190 MHz | 16 |

| Floating | Floating-Point Multiplication |          |          |    |             |      |         |    |

| RTG4     | 468                           | 847      | 131<br>5 | 4  | RT4G1<br>50 | 0.87 | 175 MHz | 14 |

|          |                               |          |          |    |             |      |         |    |

| FPGA Re        | source                        | es      |                     |           | Utilization |                |                 |        |

|----------------|-------------------------------|---------|---------------------|-----------|-------------|----------------|-----------------|--------|

| Family         | 4L<br>UT                      | DF<br>F | Tot<br>al           | Math Bloc | Device      | Percentag<br>e | Performanc<br>e | Latenc |

| Fixed-Poir     | nt to Fl                      | oating  | <sub>J</sub> -Point |           |             |                |                 |        |

| PolarFir<br>e® | 638                           | 20<br>1 | 849                 | 0         | MPF30<br>0T | 0.28           | 305 MHz         | 3      |

| Floating-F     | Floating-Point to Fixed-Point |         |                     |           |             |                |                 |        |

| PolarFir<br>e  | 244                           | 20<br>3 | 264<br>5            | 0         | MPF30<br>0T | 0.89           | 110 MHz         | 3      |

| Floating-Point Addition       |                            |          |          |    |             |      |         |    |

|-------------------------------|----------------------------|----------|----------|----|-------------|------|---------|----|

| PolarFir<br>e                 | 514<br>4                   | 40<br>28 | 917<br>2 | 0  | MPF30<br>0T | 3.06 | 240 MHz | 16 |

| Floating-F                    | Floating-Point Subtraction |          |          |    |             |      |         |    |

| PolarFir<br>e                 | 515<br>3                   | 40<br>26 | 917<br>9 | 0  | MPF30<br>0T | 3.06 | 250 MHz | 16 |

| Floating-Point Multiplication |                            |          |          |    |             |      |         |    |

| PolarFir<br>e                 | 116<br>1                   | 38<br>18 | 497<br>9 | 16 | MPF30<br>0T | 1.66 | 340 MHz | 27 |

| FPGA                       | Resoui                        | ces      |           |           | Utilization |                |                 |        |  |

|----------------------------|-------------------------------|----------|-----------|-----------|-------------|----------------|-----------------|--------|--|

| Famil<br>y                 | 4LU<br>T                      | DF<br>F  | Tot<br>al | Math Bloc | Device      | Percentag<br>e | Performanc<br>e | Latenc |  |

| Fixed-F                    | Fixed-Point to Floating-Point |          |           |           |             |                |                 |        |  |

| RTG4                       | 621                           | 201      | 822       | 0         | RT4G1<br>50 | 0.54           | 140 MHz         | 3      |  |

| Floating                   | g-Point                       | to Fix   | ed-Poi    | nt        |             |                |                 |        |  |

| RTG4                       | 111                           | 203      | 121<br>5  | 0         | RT4G1<br>50 | 0.86           | 75 MHz          | 3      |  |

| Floating                   | g-Point                       | Addit    | ion       |           |             |                |                 |        |  |

| RTG4                       | 494<br>1                      | 402<br>8 | 896<br>9  | 0         | RT4G1<br>50 | 5.9            | 140 MHz         | 16     |  |

| Floating-Point Subtraction |                               |          |           |           |             |                |                 |        |  |

| RTG4                          | 519<br>0 | 402<br>6 | 921<br>6 | 0  | RT4G1<br>50 | 6.07 | 130 MHz | 16 |

|-------------------------------|----------|----------|----------|----|-------------|------|---------|----|

| Floating-Point Multiplication |          |          |          |    |             |      |         |    |

| RTG4                          | 116<br>5 | 381<br>8 | 498<br>3 | 16 | RT4G1<br>50 | 3.28 | 170 MHz | 27 |

Important: To increase the frequency, select Enable retiming option in synthesis setting.

## **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

Table 9-1. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С        | 04/2025 | <ul> <li>The following is the list of changes in this revision C of the document:</li> <li>Added a note in the Introduction section.</li> <li>Updated Figure 2-3 and Table 2-1 in the Functional Description section.</li> <li>Added Truth Table for Addition and Subtraction and Truth Table for Multiplication sections.</li> <li>Updated Figure 4-1 and Figure 4-2 in the SmartDesign section.</li> <li>Updated all the timing diagrams in the Simulation Waveforms section.</li> <li>Updated Figure 4-16 in the System Integration section.</li> <li>Updated Table 8-1, Table 8-2, Table 8-3 and Table 8-4 in the Device Resource Utilization and Performance section.</li> </ul> |

| В        | 01/2024 | The following is the list of changes in this revision B of the document:  Updated 64-bit value in the Table 2-2.  Updated output value in the Table 2-8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A        | 11/2023 | The following is the list of changes in this revision A of the document:  The document was converted to Microchip template  The document number was changed to DS50003587A from HB0784  Added simulation waveforms for double precision (64-bit) with examples in Simulation Waveforms section  Added Resolved Issues section                                                                                                                                                                                                                                                                                                                                                         |

| 1.1      | _       | The following is the list of changes in the document: Revision 1.1 is the updated version of Revision 1.0 (CoreFPU v2.1 Handbook)  Updated Simulation Waveforms by replacing the simulation waveforms (screenshots) to timing waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.0      | _       | Revision 1.0 is the first publication of this document. Created for CoreFPU v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources

prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at <a href="www.microchip.com/support">www.microchip.com/support</a>.

Mention the FPGA Device Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

## **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at <a href="https://www.microchip.com/en-us/about/legal-information/microchip-trademarks">https://www.microchip.com/en-us/about/legal-information/microchip-trademarks</a> ISBN: 979-8-3371-0947-3

## **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF

NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip products are strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

# **Documents / Resources**

MICROCHIP CoreFPU Core Floating Point Unit [pdf] User Guide

v3.0, v2.1, v2.0, v1.0, CoreFPU Core Floating Point Unit, Core Floating Point Unit, Floating Point Unit, Point Unit

#### References

- User Manual

- **■** MICROCHIP

- ◆ Core Floating Point Unit, CoreFPU Core Floating Point Unit, Floating Point Unit, MICROCHIP, Point Unit, V1.0, v2.0, V2.1, V3.0

# Leave a comment

Your email address will not be published. Required fields are marked\*

Comment\*

Name

Email

Website

☐ Save my name, email, and website in this browser for the next time I comment.

# **Post Comment**

#### Search:

e.g. whirlpool wrf535swhz

**Search**

Manuals+ | Upload | Deep Search | Privacy Policy | @manuals.plus | YouTube

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.