# **External Memory Interfaces (EMIF) IP User Guide**

## **Agilex<sup>™</sup> 5 FPGAs and SoCs**

Updated for Quartus® Prime Design Suite: 24.1

IP Version: 6.1.0

### Contents

| 1. About the Exte                                                                                                                                                 | ernal Memory Interfaces Agilex <sup>™</sup> 5 FPGA IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                                                                                                                                   | Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 2 Agiley 5 FPGA                                                                                                                                                   | EMIF IP - Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                            |

| _                                                                                                                                                                 | EMIF IP Protocol and Feature Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

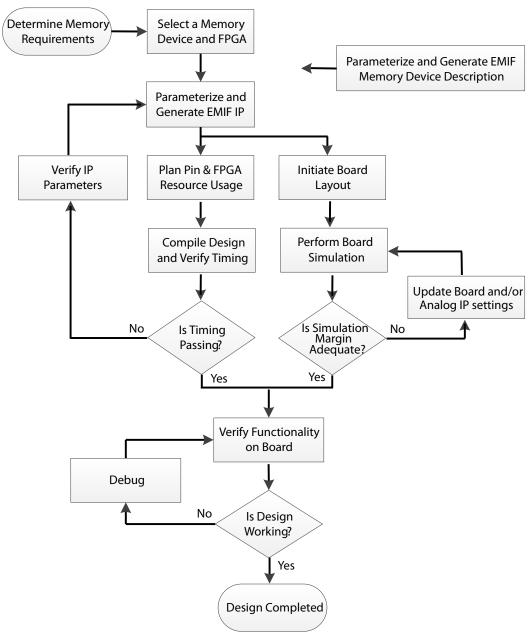

|                                                                                                                                                                   | 5 EMIF IP Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 EMIF IP Design Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

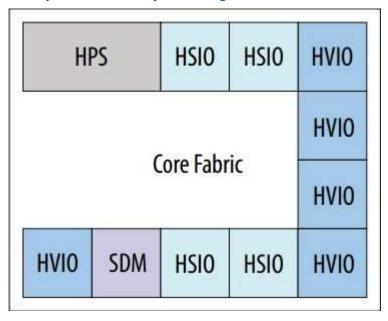

|                                                                                                                                                                   | EMIF IP - Product Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

|                                                                                                                                                                   | 5 EMIF Architecture: Protocol and Maximum Interface Width Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                                                   | 5 EMIF Architecture: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

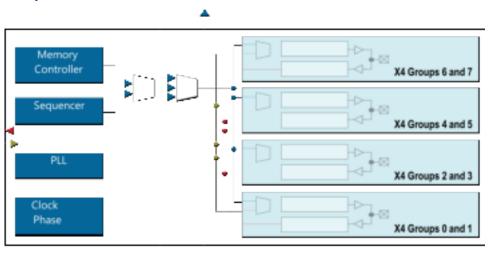

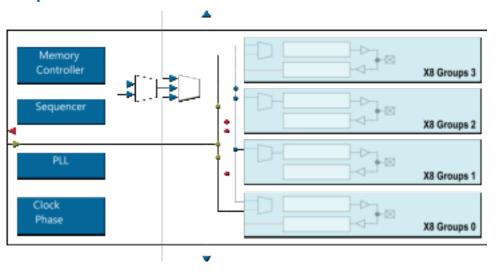

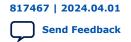

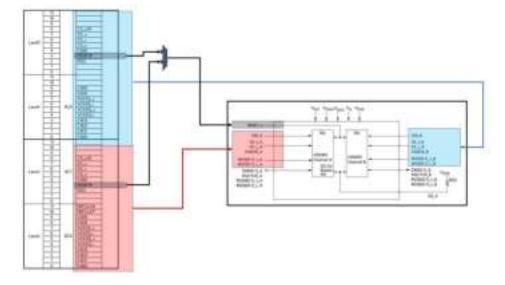

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: I/O Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

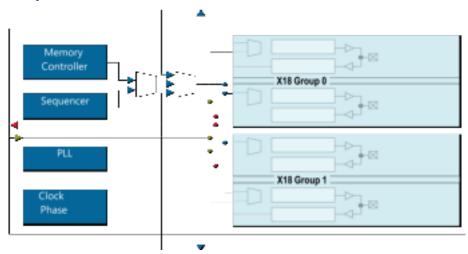

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: I/O SSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: HSIO Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: I/O Lane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: Input DQS Clock Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: PHY Clock Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

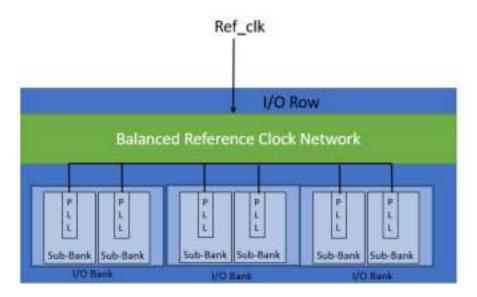

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: PLL Reference Clock Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

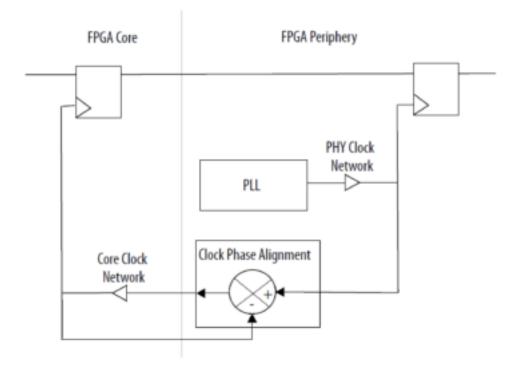

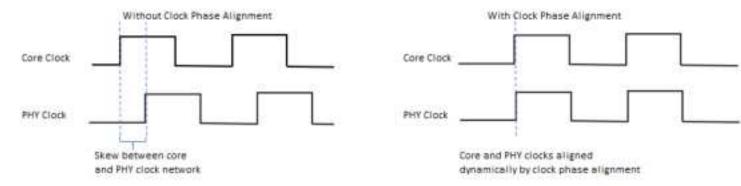

|                                                                                                                                                                   | . Agilex 5 EMIF Architecture: Clock Phase Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

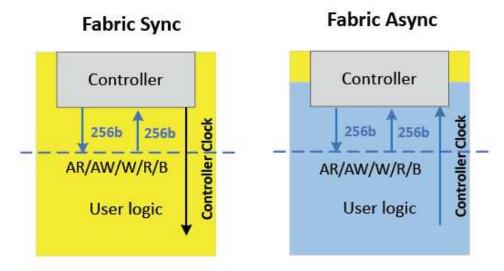

|                                                                                                                                                                   | . User Clock in Different Core Access Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

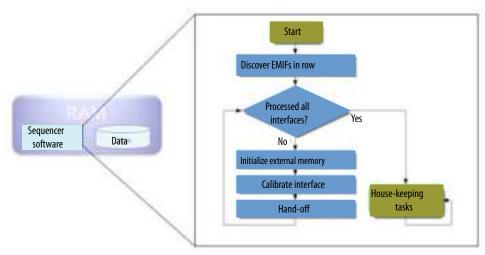

|                                                                                                                                                                   | 5 EMIF Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|                                                                                                                                                                   | . Agilex 5 Mailbox Structure and Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

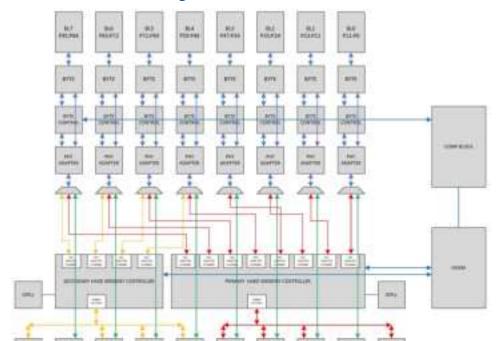

| _                                                                                                                                                                 | 5 EMIF Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.4.1                                                                                                                                                             | . Hard Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .46                                                                                          |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| _                                                                                                                                                                 | EMIF IP for Hard Processor Subsystem (HPS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 4. Agilex 5 FPGA                                                                                                                                                  | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP - End-User Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                                                           |

| 4. Agilex 5 FPGA<br>4.1. Agilex 5                                                                                                                                 | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . <b>50</b>                                                                                  |

| 4. Agilex 5 FPGA<br>4.1. Agilex 5                                                                                                                                 | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP - End-User Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . <b>50</b>                                                                                  |

| <b>4. Agilex 5 FPGA</b> 4.1. Agilex 5 4.1.1 4.1.2                                                                                                                 | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . <b>50</b><br>. 50<br>. 50                                                                  |

| 4. Agilex 5 FPGA<br>4.1. Agilex 5<br>4.1.1<br>4.1.2<br>4.1.3                                                                                                      | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP - End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . <b>50</b><br>. 50<br>. 50<br>. 50                                                          |

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4                                                                                                            | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . <b>50</b><br>. 50<br>. 50<br>. 50<br>. 51                                                  |

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5                                                                                                      | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP - End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51                                                  |

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6                                                                                                | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF  s0_axi4 for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51                                          |

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7                                                                                          | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF  s0_axi4 for EMIF  mem for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 54                                          |

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8                                                                                    | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  mem for EMIF  oct for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51                                          |

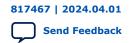

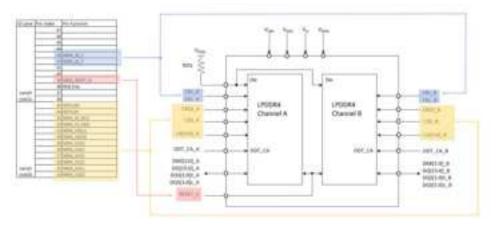

| 4. Agilex 5 FPGA 4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5                                                                      | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  mem for EMIF  oct for EMIF  FPGA EMIF IP Interfaces for LPDDR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55                                  |

| 4. Agilex 5 FPGA  4.1. Agilex 5  4.1.1  4.1.2  4.1.3  4.1.4  4.1.5  4.1.6  4.1.7  4.1.8  4.2. Agilex 5  4.2.1                                                     | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_clk for EMIF  usr_rst_n for EMIF  s0_axi4 for EMIF  mem for EMIF  oct for EMIF  FPGA EMIF IP Interfaces for LPDDR4  ref_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55                          |

| 4. Agilex 5 FPGA  4.1. Agilex 5  4.1.1  4.1.2  4.1.3  4.1.4  4.1.5  4.1.6  4.1.7  4.1.8  4.2. Agilex 5  4.2.1  4.2.2                                              | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4.  ref_clk for EMIF core_init_n for EMIF usr_async_clk for EMIF usr_clk for EMIF usr_rst_n for EMIF s0_axi4 for EMIF mem for EMIF oct for EMIF FPGA EMIF IP Interfaces for LPDDR4 ref_clk for EMIF core_init_n for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 55                  |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3                                                   | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4.  ref_clk for EMIF core_init_n for EMIF usr_async_clk for EMIF usr_clk for EMIF usr_rst_n for EMIF s0_axi4 for EMIF mem for EMIF oct for EMIF FPGA EMIF IP Interfaces for LPDDR4 ref_clk for EMIF core_init_n for EMIF usr_async_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 55                  |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4                                             | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4.  ref_clk for EMIF . core_init_n for EMIF . usr_async_clk for EMIF . usr_clk for EMIF . usr_rst_n for EMIF . s0_axi4 for EMIF . oct for EMIF . oct for EMIF . oct for EMIF . ref_clk for EMIF . ref_clk for EMIF . core_init_n for EMIF . usr_async_clk for EMIF . usr_async_clk for EMIF . usr_async_clk for EMIF . usr_async_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 55<br>. 56          |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5                                       | EMIF IP for Hard Processor Subsystem (HPS)  EMIF IP – End-User Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 55<br>. 56          |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6                                 | EMIF IP for Hard Processor Subsystem (HPS).  EMIF IP – End-User Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 56<br>. 56          |

| 4. Agilex 5 FPGA  4.1. Agilex 5  4.1.1  4.1.2  4.1.3  4.1.4  4.1.5  4.1.6  4.1.7  4.1.8  4.2. Agilex 5  4.2.1  4.2.2  4.2.3  4.2.4  4.2.5  4.2.6  4.2.7           | EMIF IP for Hard Processor Subsystem (HPS).  EMIF IP – End-User Signals.  5 FPGA EMIF IP Interfaces for DDR4.  core_init_n for EMIF.  usr_async_clk for EMIF.  usr_clk for EMIF.  so_axi4 for EMIF.  oct for EMIF.  oct for EMIF.  5 FPGA EMIF IP Interfaces for LPDDR4.  ref_clk for EMIF.  core_init_n for EMIF.  usr_async_clk for EMIF.  usr_async_clk for EMIF.  usr_clk for EMIF.  usr_clk for EMIF.  usr_st_n for EMIF.  usr_st_n for EMIF.  so_axi4 for EMIF.  usr_rst_n for EMIF.                                                                                                                                                                                                                                                                                                                                                                                                               | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 55<br>. 56<br>. 56  |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8                     | EMIF IP for Hard Processor Subsystem (HPS).  EMIF IP – End-User Signals.  5 FPGA EMIF IP Interfaces for DDR4.  5 ref_clk for EMIF  6 core_init_n for EMIF  7 usr_async_clk for EMIF  8 usr_rst_n for EMIF  8 s0_axi4 for EMIF  9 oct for EMIF  9 oct for EMIF  10 oct for EMIF  11 core_init_n for EMIF  12 core_init_n for EMIF  13 usr_async_clk for EMIF  14 usr_async_clk for EMIF  15 usr_async_clk for EMIF  16 usr_st_n for EMIF  17 usr_st_n for EMIF  18 usr_rst_n for EMIF  28 usr_rst_n for EMIF                                                                                                                                                                                                                                                                                                  | . <b>50</b><br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56  |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.3. Agilex 5       | EMIF IP for Hard Processor Subsystem (HPS).  EMIF IP – End-User Signals  FPGA EMIF IP Interfaces for DDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  mem for EMIF  oct for EMIF  FPGA EMIF IP Interfaces for LPDDR4  ref_clk for EMIF  core_init_n for EMIF  usr_async_clk for EMIF  usr_async_clk for EMIF  usr_async_clk for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  usr_rst_n for EMIF  so_axi4 for EMIF  so_baxi4 for EMIF  so_baxi4 for EMIF  so_baxi5 for EMIF  so_baxi6 for EMIF  so_baxi6 for EMIF  so_baxi7 for EMIF  so_baxi6 for EMIF  so_baxi7 for EMIF | . 50<br>. 50<br>. 50<br>. 51<br>. 51<br>. 51<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 56 |

| 4. Agilex 5 FPGA  4.1. Agilex 5 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.1.6 4.1.7 4.1.8 4.2. Agilex 5 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 4.2.7 4.2.8 4.3. Agilex 5 4.3.1 | EMIF IP for Hard Processor Subsystem (HPS).  EMIF IP – End-User Signals.  5 FPGA EMIF IP Interfaces for DDR4.  5 ref_clk for EMIF  6 core_init_n for EMIF  7 usr_async_clk for EMIF  8 usr_rst_n for EMIF  8 s0_axi4 for EMIF  9 oct for EMIF  9 oct for EMIF  10 oct for EMIF  11 core_init_n for EMIF  12 core_init_n for EMIF  13 usr_async_clk for EMIF  14 usr_async_clk for EMIF  15 usr_async_clk for EMIF  16 usr_st_n for EMIF  17 usr_st_n for EMIF  18 usr_rst_n for EMIF  28 usr_rst_n for EMIF                                                                                                                                                                                                                                                                                                  | . <b>50</b>                                                                                  |

|         | 4.3.3. usr_async_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|         | 4.3.4. usr_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|         | 4.3.5. usr_rst_n for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|         | 4.3.6. s0_axi4 for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|         | 4.3.7. oct for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|         | 4.4. Agilex 5 FPGA EMIF IP Interfaces for EMIF Calibration Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|         | 4.4.1. s0_axi4lite_clk for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|         | 4.4.2. s0_axi4lite_rst_n for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|         | 4.4.3. s0_axil for EMIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65   |

| 5. Agi  | ilex 5 FPGA EMIF IP – Simulating Memory IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66   |

|         | 5.1. Simulation Walkthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66   |