# **Micro Developer Board LEDs**

| LED        | Description                                                                                  |

|------------|----------------------------------------------------------------------------------------------|

| LED1       | User-definable LED.                                                                          |

| LED3/SDA   | Programming Status.                                                                          |

| LED2/PWR   | Power, blue light when the board has power.                                                  |

| LED4/PROXY | LED for the proximity sensor, which is next to it (labeled U14 on the top assembly diagram). |

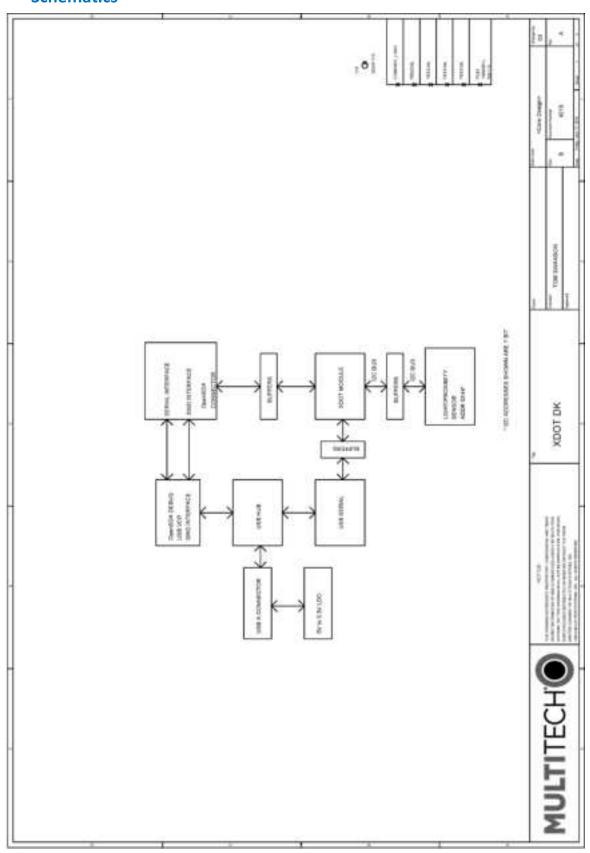

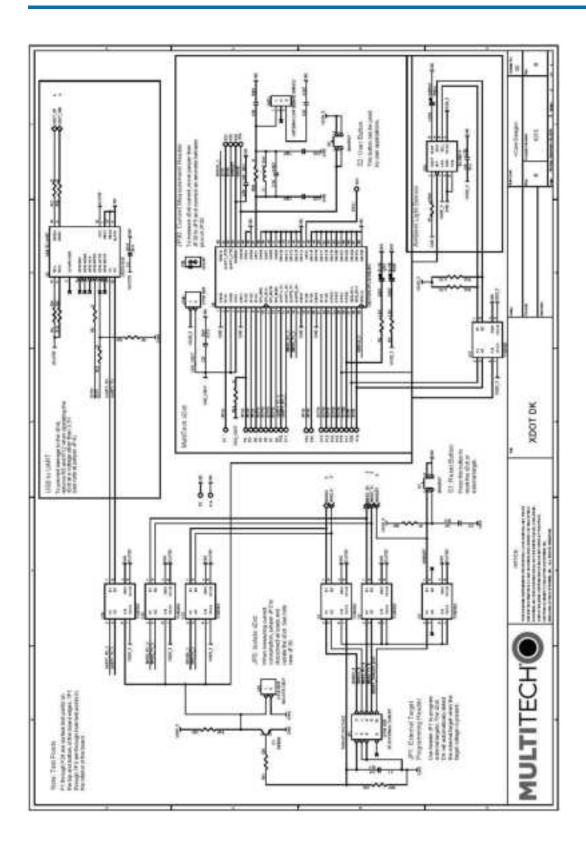

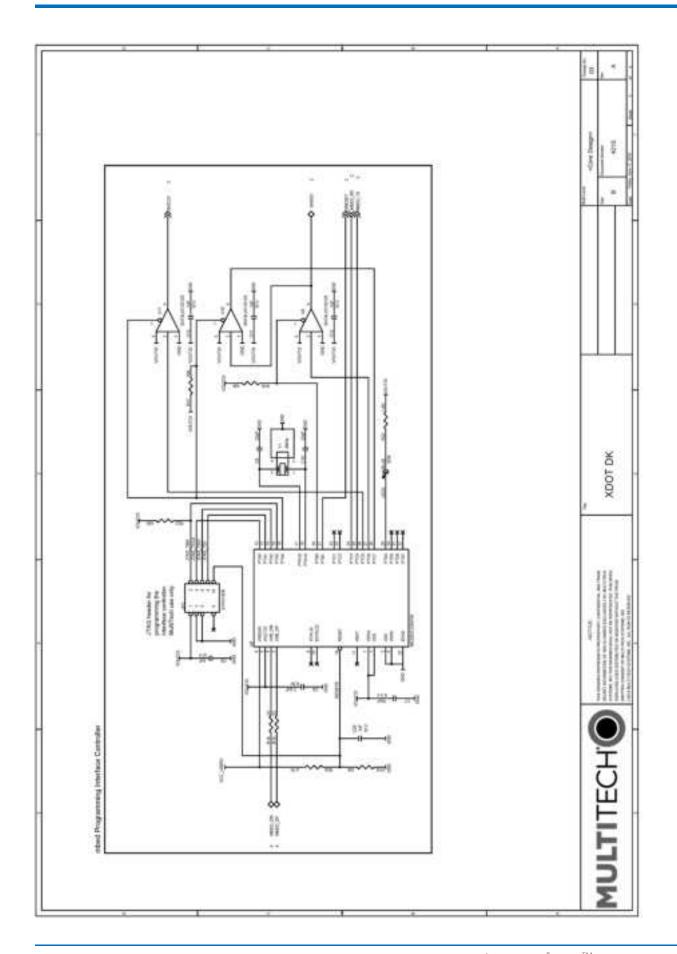

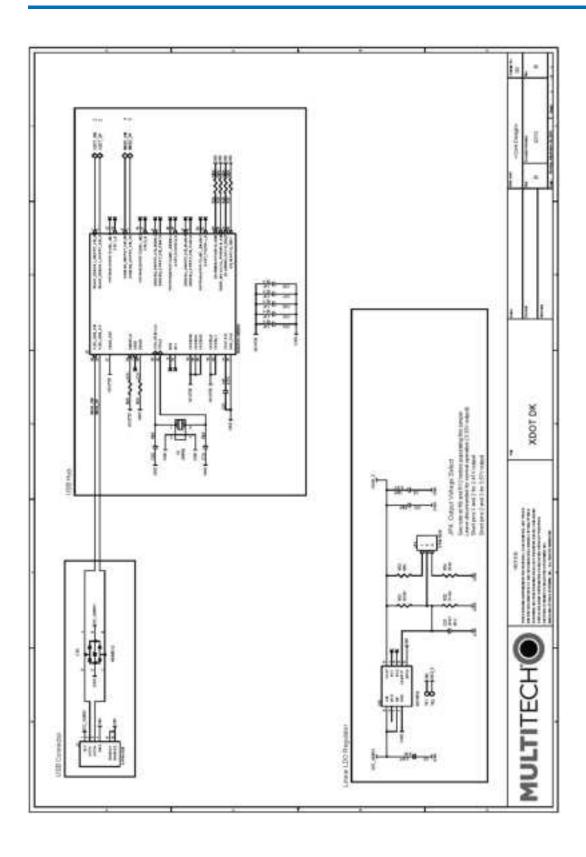

# **Chapter 11 Developer Board Schematics**

## **Assembly Diagrams and Schematics**

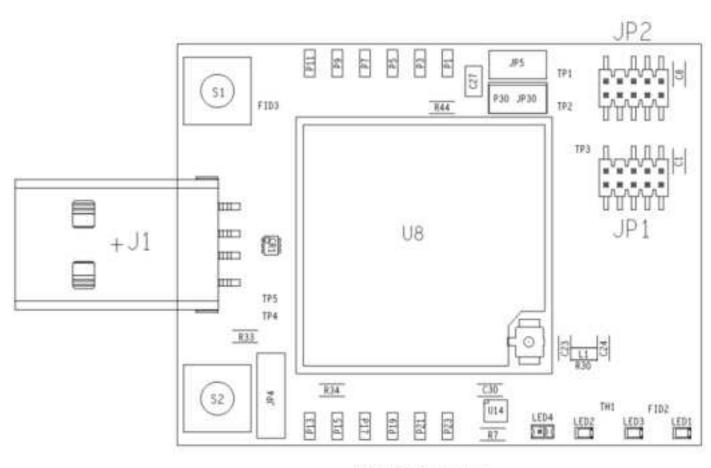

**Assembly Diagrams**

Top

R30 SITS ON L1 C34 SITS ON L1

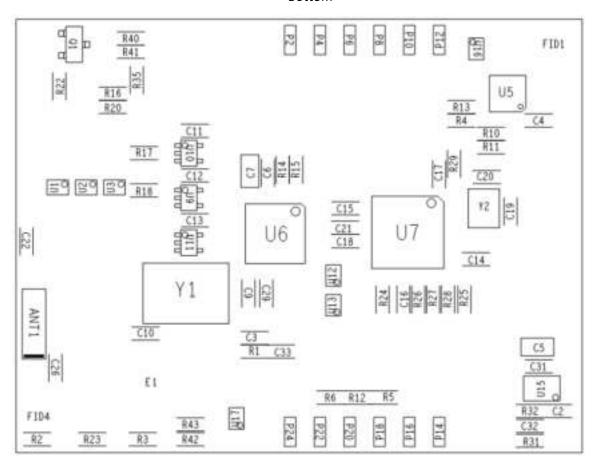

#### Bottom

#### **Schematics**

# **Chapter 12 Design Considerations**

#### **Noise Suppression Design**

Adhere to engineering noise-suppression practices when designing a printed circuit board (PCB). Noise suppression is essential to the proper operation and performance of the modem and surrounding equipment.

Any OEM board design must consider both on-board and off-board generated noise that can affect digital signal processing. Both on-board and off-board generated noise that is coupled on-board can affect interface signal levels and quality. Noise in frequency ranges that affect modem performance is of particular concern.

On-board generated electromagnetic interference (EMI) noise that can be radiated or conducted off-board is equally important. This type of noise can affect the operation of surrounding equipment. Most local government agencies have certification requirements that must be met for use in specific environments.

Proper PC board layout (component placement, signal routing, trace thickness and geometry, and so on) component selection (composition, value, and tolerance), interface connections, and shielding are required for the board design to achieve desired modem performance and to attain EMI certification.

Other aspects of proper noise-suppression engineering practices are beyond the scope of this guide. Consult noise suppression techniques described in technical publications and journals, electronics and electrical engineering text books, and component supplier application notes.

#### **PC Board Layout Guideline**

In a 4-layer design, provide adequate ground plane covering the entire board. In 4-layer designs, power and ground are typically on the inner layers. Ensure that all power and ground traces are 0.05 inches wide.

The recommended hole size for the device pins is 0.036 in. +/-0.003 in. in diameter. Use spacers to hold the device vertically in place during the wave solder process.

#### **Electromagnetic Interference**

The following guidelines are offered specifically to help minimize EMI generation. Some of these guidelines are the same as, or similar to, the general guidelines. To minimize the contribution of device-based design to EMI, you must understand the major sources of EMI and how to reduce them to acceptable levels.

- Keep traces carrying high frequency signals as short as possible.

- Provide a good ground plane or grid. In some cases, a multilayer board may be required with full layers for ground and power distribution.

- Decouple power from ground with decoupling capacitors as close to the device's power pins as possible.

- Eliminate ground loops, which are unexpected current return paths to the power source and ground.

- Decouple the telephone line cables at the telephone line jacks. Typically, use a combination of series inductors, common mode chokes, and shunt capacitors. Methods to decouple telephone lines are similar to decoupling power lines; however, telephone line decoupling may be more difficult and deserves additional attention. A commonly used design aid is to place footprints for these components and populate as necessary during performance/EMI testing and certification.

- Decouple the power cord at the power cord interface with decoupling capacitors. Methods to decouple power lines are similar to decoupling telephone lines.

- Locate high frequency circuits in a separate area to minimize capacitive coupling to other circuits.

- Locate cables and connectors to avoid coupling from high frequency circuits.

- Lay out the highest frequency signal traces next to the ground grid.

- If using a multilayer board design, make no cuts in the ground or power planes and be sure the ground plane covers all traces.

- Minimize the number of through-hole connections on traces carrying high frequency signals.

- Avoid right angle turns on high frequency traces. Forty-five degree corners are good; however, radius turns are better.

- On 2-layer boards with no ground grid, provide a shadow ground trace on the opposite side of the board to traces carrying high frequency signals. This will be effective as a high frequency ground return if it is three times the width of the signal traces.

- Distribute high frequency signals continuously on a single trace rather than several traces radiating from one point.

#### **Electrostatic Discharge Control**

Handle all electronic devices with precautions to avoid damage due to the static charge accumulation.

See the ANSI/ESD Association Standard (ANSI/ESD S20.20-1999) — a document "for the Development of an Electrostatic Discharge Control for Protection of Electrical and Electronic Parts, Assemblies and Equipment." This document covers ESD Control Program Administrative Requirements, ESD Training, ESD Control Program Plan Technical Requirements (grounding/bonding systems, personnel grooming, protected areas, packaging, marking, equipment, and handling), and Sensitivity Testing.

MultiTech strives to follow these recommendations. Input protection circuitry is incorporated in MultiTech devices to minimize the effect of static buildup. Take precautions to avoid exposure to electrostatic discharge during handling.

MultiTech uses and recommends that others use anti-static boxes that create a faraday cage (packaging designed to exclude electromagnetic fields). MultiTech recommends that you use our packaging when returning a product and when you ship your products to your customers.

# **Chapter 13 Mounting xDots and Programming Exter- nal Targets**

### **Mounting the Device on Your Board**

A footprint diagram is included on the xDot Mechanical Diagram.

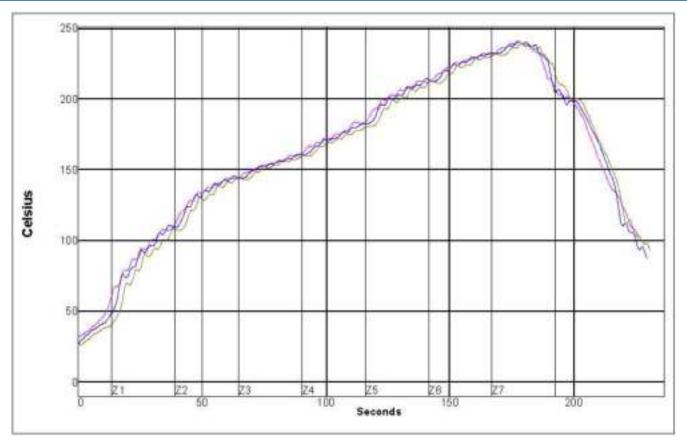

#### **Solder Profile**

Solder Paste: SAC NC 254

Note: Calculate slope over 120 seconds

| Name                          | Low Limit | High Limit | Units           |

|-------------------------------|-----------|------------|-----------------|

| Max Rising Slope (Target=1.0) | 0         | 2          | Degrees/Second  |

| Max Falling Slope             | -2        | -0.1       | Degrees/Second  |

| Soak Time 150-170C            | 15        | 45         | Seconds         |

| Peak Temperature              | 235       | 250        | Degrees Celsius |

| Total Time Above 218C         | 30        | 90         | Seconds         |

#### **Setpoints (Celsius)**

| Zone           | 1   | 2                | 3   | 4   | 5   | 6   | 7   |  |

|----------------|-----|------------------|-----|-----|-----|-----|-----|--|

| Тор            | 130 | 160              | 170 | 190 | 230 | 245 | 255 |  |

| Bottom         | 130 | 160              | 170 | 190 | 230 | 245 | 255 |  |

| Conveyer Speed |     | 32.0 inch/minute |     |     |     |     |     |  |

|       |             | Max Rising Slope |     | Max Falling Slope |     | Soak Time 150-<br>170C |      | Peak Temp |      | Total Time /218C |      |

|-------|-------------|------------------|-----|-------------------|-----|------------------------|------|-----------|------|------------------|------|

| TC    | Position    | Slope            | PWI | Slope             | PWI | Time                   | PWI  | Temp      | PWI  | Time             | PWI  |

| 1     | <tc2></tc2> | 1.38             | 38% | -0.63             | 45% | 28.82                  | -8%  | 240.22    | -30% | 43.61            | -55% |

| 2     | <tc3></tc3> | 1.38             | 38% | -0.75             | 32% | 26.75                  | -22% | 241.21    | -17% | 43.66            | -54% |

| 3     | <tc4></tc4> | 1.38             | 38% | -0.70             | 36% | 29.47                  | -4%  | 239.56    | -39% | 43.29            | -56% |

| Delta |             | 0.00             |     | 0.12              |     | 2.72                   |      | 1.65      |      | 0.37             |      |

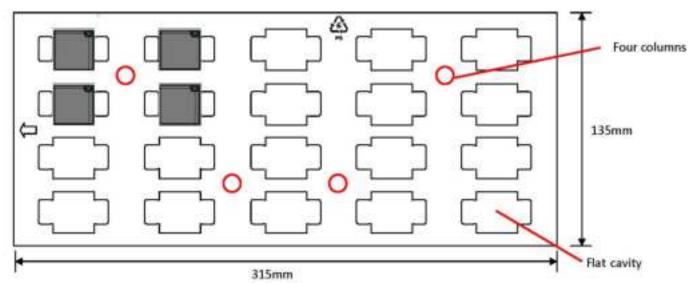

## **xDot Packing**

xDots ship on 20 piece trays, which you can use for pick and place handling.

Warning: Maximum temperature for these trays is 65° C.

## **Programming External Targets**

You can use the xDot developer board to program external targets. To do this:

- 1. Connect header JP1 to your target board with a 9-position ribbon cable.<sup>1</sup>

- 2. Apply power to your target board.

3. When the xDot developer board detects a target voltage on Pin 1 of header JP1, it redirects the mbed programming interface to the external target. You can use the mbed programming environment as normal to program and debug the external target.

<sup>1</sup>MultiTech recommends the Samtec FFSD-05-D-06.00-01-N ribbon cable.

#### JTAG/SWD Connector

The developer board uses an unshrouded 10-pin header.

Suitable connector headers include:

Harwin: M50-3500542

Mouser: 855-M50-3500542

■ Samtec shrouded header: FTSH-105-01-F-D-K

The Samtec FTSH-105 header dimensions are 0.25"x 0.188" (6.35mm x 4.78mm).

Ensure that you connect your cable correctly, typically by matching the "1" marked on the board to the cable's red stripe.

# Index

| schematics                   | E                                                      |     |

|------------------------------|--------------------------------------------------------|-----|

| Developer Board              | 44 electrical characteristics                          | 16  |

|                              | electrical characteristicselectromagnetic interference |     |

| Α.                           | electromagnetic interference                           |     |

| A                            | EMI                                                    |     |

| antenna22                    | 23 ESD                                                 |     |

| developer board              | 25 EUI                                                 |     |

| antenna design guidelines    | no                                                     |     |

| assembly diagrams            | external targets                                       | 53  |

| Developer Board              | 44                                                     |     |

| AT command                   | F                                                      |     |

| port                         | .9                                                     |     |

| F                            | FCC                                                    |     |

|                              | grant notes                                            | 30  |

| В                            | FCC Notice                                             |     |

| hand on ha                   | Class B                                                |     |

| baud rate                    | flow control                                           | 20  |

| board components             | ••                                                     |     |

| Micro Developer Board4       |                                                        |     |

| build options                | 8 <b>G</b>                                             |     |

|                              | ground plane                                           | 50  |

| С                            | 8. cana plane                                          |     |

| C                            |                                                        |     |

| cable                        | Н                                                      |     |

| coaxial                      | 24 handling massachians due to ECD                     | Г1  |

| certifications               | handling precautions due to ESD                        |     |

| Chinese hazardous substances | hazardous substances                                   |     |

| Chinese version              | host labeling                                          | 30  |

| English version              | 38                                                     |     |

| Class B                      | 33 <sub>I</sub>                                        |     |

| Industry Canada              | •                                                      |     |

| COM ports                    | localisations Caucarda                                 |     |

| Conduit                      | CI D                                                   | 34  |

|                              | interférence des radiofréquences                       | 31  |

| D                            |                                                        |     |

|                              | J                                                      |     |

| data bits                    | ITAC .                                                 | 5.4 |

| debug port                   | .9 7740 connector                                      |     |

| design guidelines            |                                                        |     |

| antenna                      | <sup>28</sup> к                                        |     |

| device                       |                                                        |     |

| maintenance                  |                                                        | 30  |

| dimensions                   |                                                        |     |

| documentation                | .6                                                     |     |

|                              | L                                                      |     |

|                              | labeling                                               |     |

|                              | •                                                      | 30  |

| labels40                       | related products                        | 6  |

|--------------------------------|-----------------------------------------|----|

| Linux9                         | ribbon cable                            | 53 |

| LoRa                           | RoHS                                    | 37 |

| range20                        | RSMA-to-UFL cable                       | 24 |

| М                              | S                                       |    |

| Mac9                           | safety                                  |    |

| maintenance32                  | RF interference                         |    |

| mbed6                          | safety standards                        | 50 |

| mechanical drawings11          | serial settings                         |    |

| Micro Developer Board42        | solder profile                          | 52 |

| MTAC-LORA6                     | specifications                          | 12 |

| MTCDT6                         | static                                  | 31 |

| MultiConnect6                  | stop bits                               | 20 |

|                                | sécurité                                |    |

|                                | interférences RF                        | 31 |

| N                              |                                         |    |

| network, connecting            | Т                                       |    |

|                                | trace antenna                           | 22 |

|                                | transmission                            | 12 |

| P                              |                                         |    |

| packing list41                 |                                         |    |

| parity20                       | U                                       |    |

| PC board layout50              | U.FL antenna                            | 22 |

| pin information16              | user responsibility                     |    |

| pinout notes20                 | , , , , , , , , , , , , , , , , , , , , |    |

| ports9                         |                                         |    |

| power draw15                   | W                                       |    |

| measuring15                    | Windows                                 | 0  |

| processor6                     | WIIIdows                                |    |

| programming external targets53 |                                         |    |

| programming excernar targets   | X                                       |    |

| R                              | xDot packing                            | 53 |

| radio frequency interference31 |                                         |    |

| range20                        |                                         |    |

| receive sensitivity12          |                                         |    |