Volume 54, Number 1, 2020

Your Engineering Resource for Innovative Design

- 5 Electric Vehicle Warning Sound System

- 10 ADI SDR Transceivers Enable Amateur Space Communication

- 14 Paralleling Very Low Dropout Linear Regulators for Increased Output Current and Even Heat Distribution

- 30 Open-Source LIDAR Prototyping Platform

- 43 Protecting and Powering Automotive Electronics Systems with No Switching Noise and 99.9% Efficiency

- 57 Why Does Voltage Reference Noise Matter?

- 64 Contactless Fluid-Level Measurement Using a Reflectometer Chip

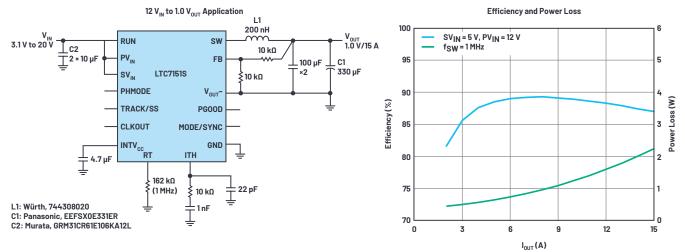

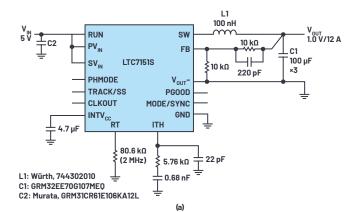

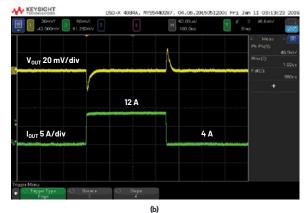

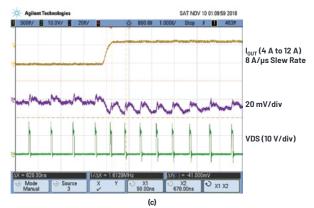

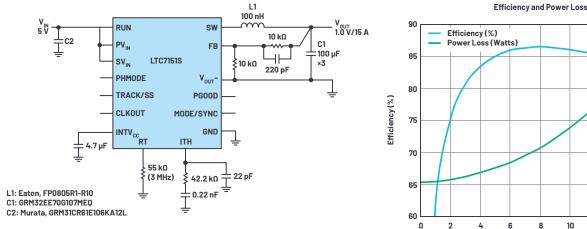

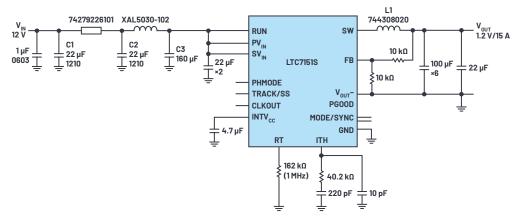

- 69 Reduce Power Supply Requirements for Ceramic Capacitors with a High Efficiency, High Frequency, Low EMI DC-to-DC Converter

Wireless Water Quality Monitoring System

## In This Issue

Electric Vehicle Warning Sound System

Traditional combustion engine vehicles emit sound, even at low travel speeds, making it easy for pedestrians to notice a moving vehicle. Electric vehicles (EVs) and hybrids, on the other hand, accelerate mostly silently at low speed. An electric vehicle warning sound system (EVWSS) produces a series of sounds designed to alert pedestrians to the presence of an electric vehicle.

10 ADI SDR Transceivers Enable Amateur Space Communication

With two dedicated transponders on board, the Es'hail-2 satellite is a new geostationary satellite that connects users across the globe in real time and provides reliable coverage to more than one-third of the Earth. The new software-defined radio approach to radio transceivers offers multiple advantages that have also impacted the amateur radio world.

Paralleling Very Low Dropout Linear Regulators for Increased Output Current and Even Heat Distribution

At high power densities with low output voltages, the problem of heat dissipation rises to the top of the design priority list, especially for linear regulators in low noise applications. Paralleling LDO regulators can increase supply current capability and mitigate heat dissipation, reducing the temperature rise of any component and the required size and number of cooling devices.

Rarely Asked Questions—Issue 173: Building Physically Accurate Analog Switch Macromodels

Our RAQ this month concentrates on LTspice® and how to generate an accurate analog switch macromodel. There are good macromodels available for op amps, but analog switch macromodels are not designed for high performance simulations. To achieve more accurate performance, you might need a new macromodeling approach to bring your simulation to a higher level.

30 Open-Source LIDAR Prototyping Platform

As autonomous vehicles and robots increasingly become reality, automotive and industrial customers are seeking new environmental perception solutions to enable these machines. LIDAR is one of the fast-growing technologies in this field and seeing wider adoption as the technology becomes more mature and reliable.

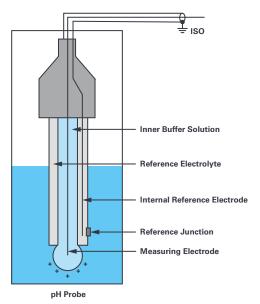

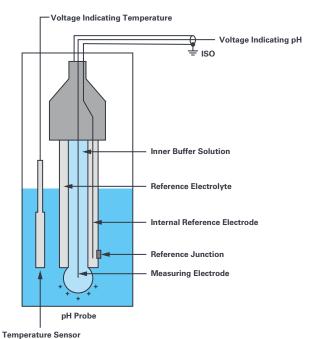

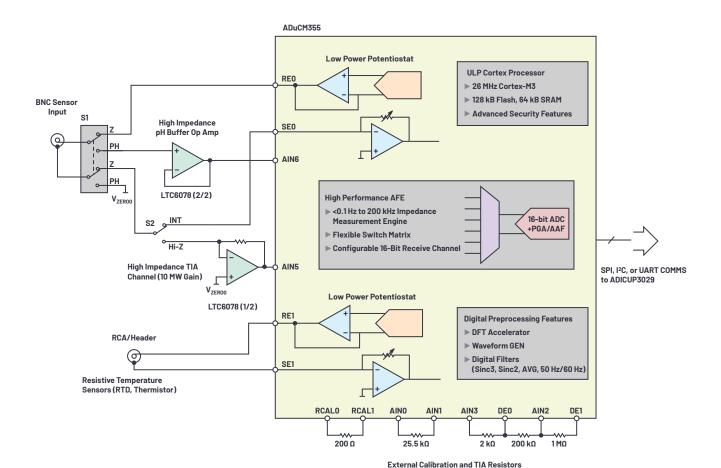

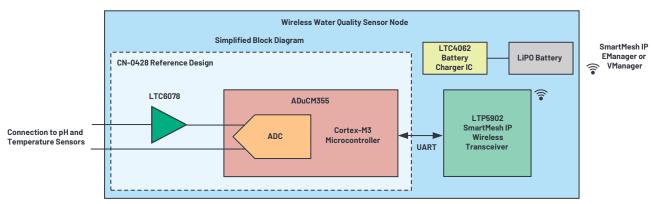

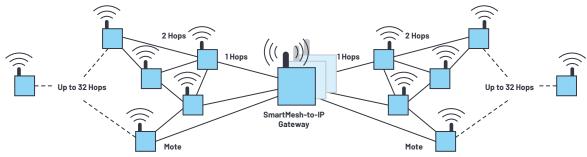

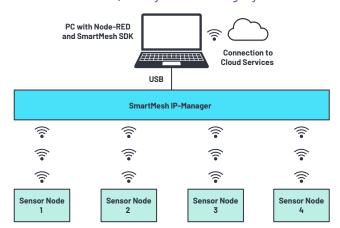

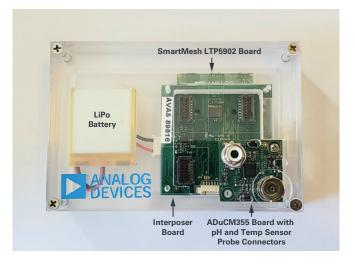

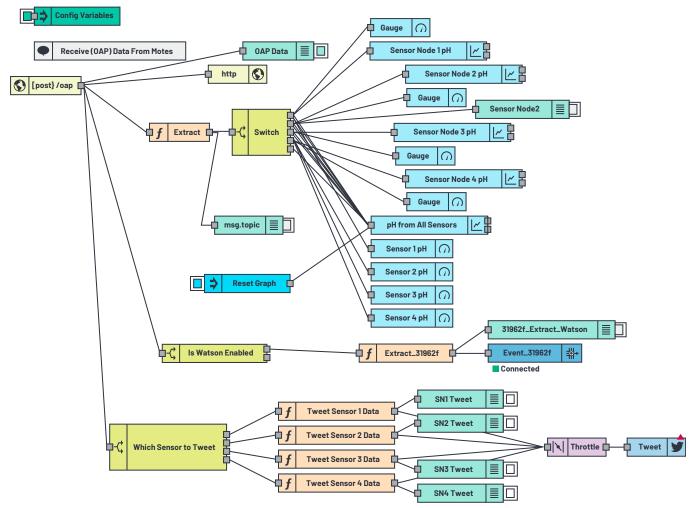

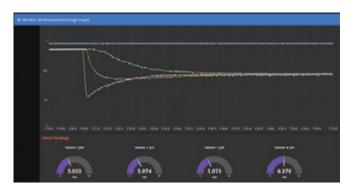

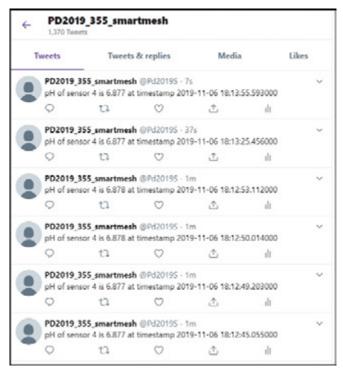

36 Wireless Water Quality Monitoring System

Several industries such as beverage production, pharmaceuticals, and wastewater treatment rely on water quality monitoring systems to measure and control important water quality indicators. This article discusses the benefits of combining the measurement system and wireless sensors with a robust and reliable wireless network.

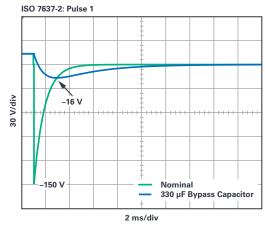

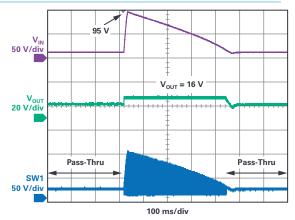

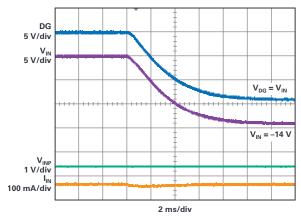

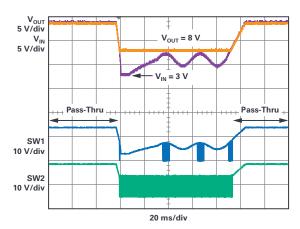

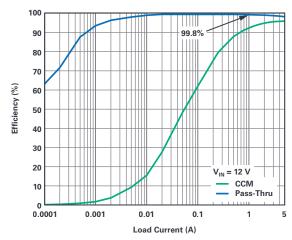

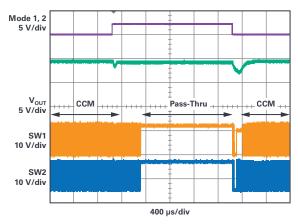

43 Protecting and Powering Automotive Electronics Systems with No Switching Noise and 99.9% Efficiency

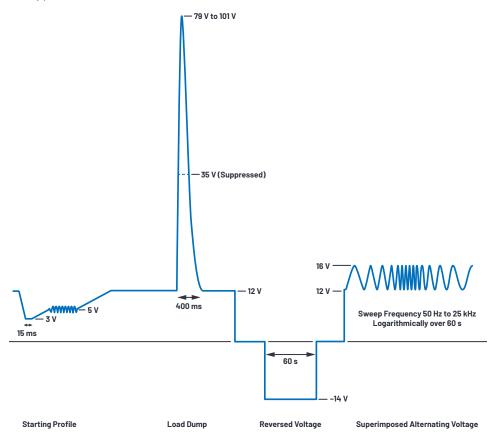

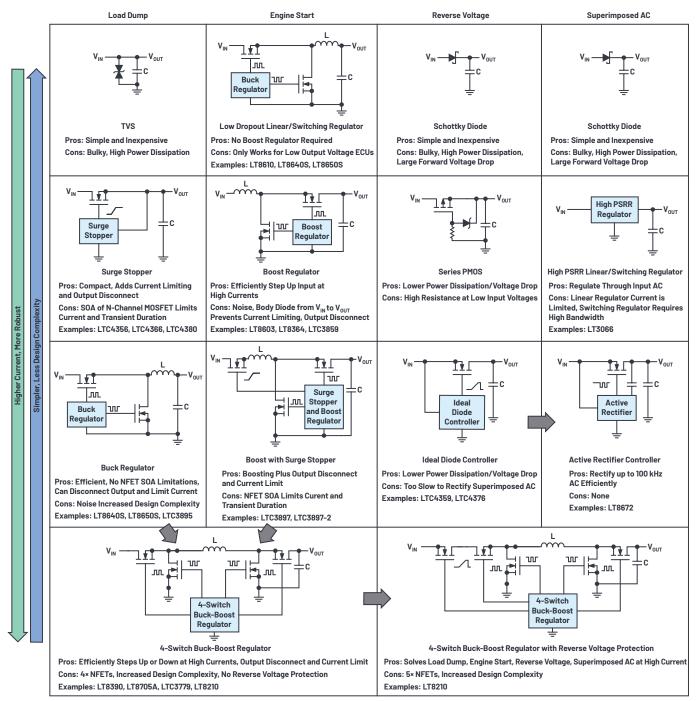

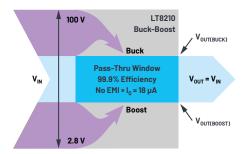

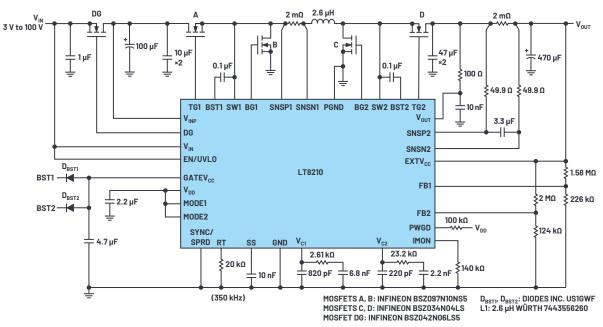

Powering automotive electronics is not trivial. The variety of electrical and mechanical systems that interface with the vehicle's battery can cause, what one might assume to be, a relatively stable 12 V supply to spike from −300 V to +150 V over short periods of time. Our new 4-switch buck-boost dc-to-dc controller offers a solution with a 2.8 V to 100 V input operating range, built-in reverse battery protection, and its new PassThru™ operating mode.

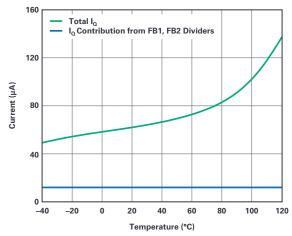

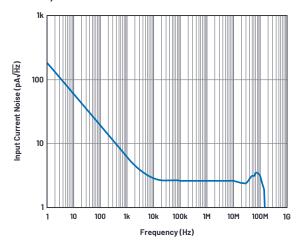

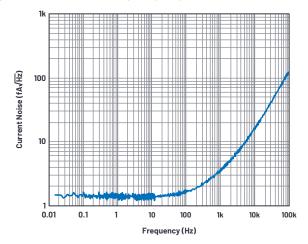

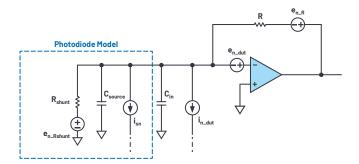

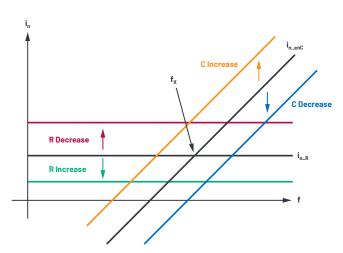

Rarely Asked Questions—Issue 174: Current Noise in FET Input Amps: Why Your Design Is Noisier at Higher Frequencies

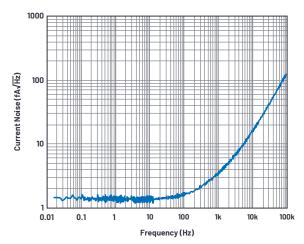

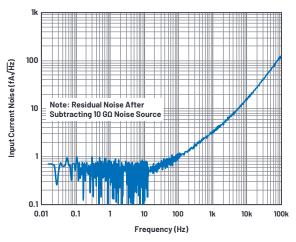

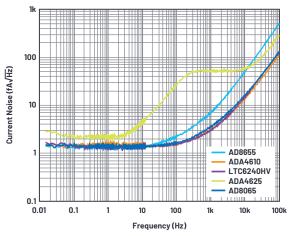

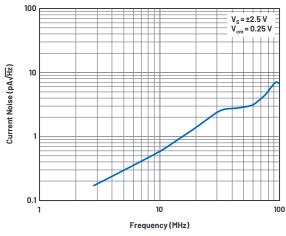

Many semiconductor manufacturer data sheets specify the current noise of an amplifier in the specification tables, typically at a frequency of 1 kHz. It isn't always clear where the current noise specifications come from. Is it measured or is it theoretical?

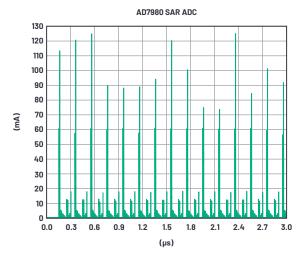

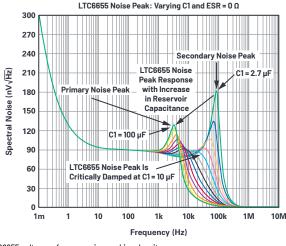

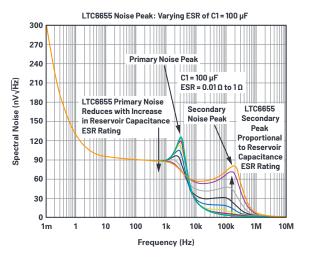

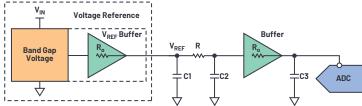

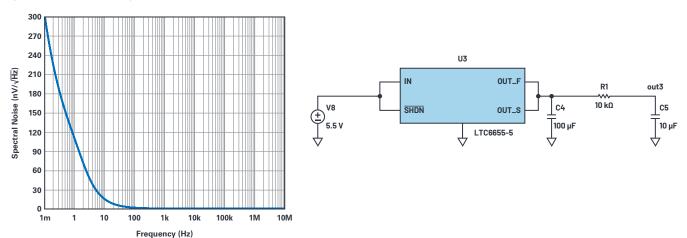

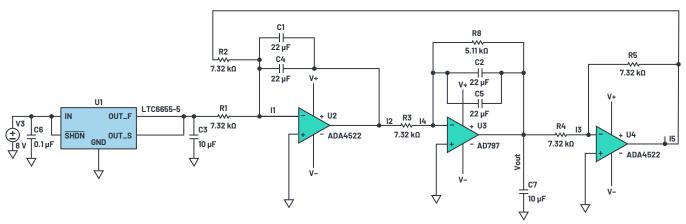

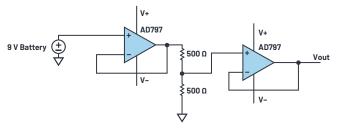

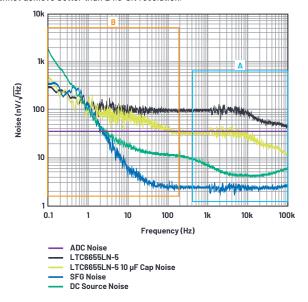

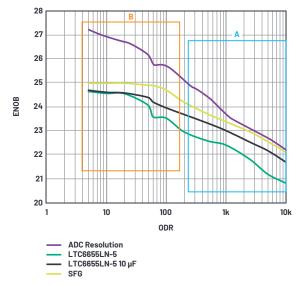

Why Does Voltage Reference Noise Matter?

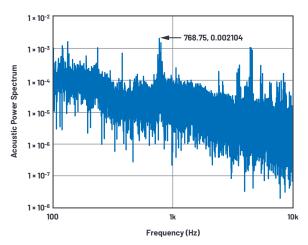

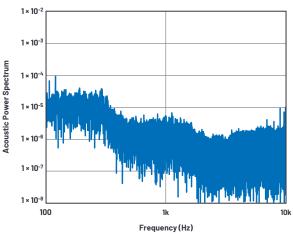

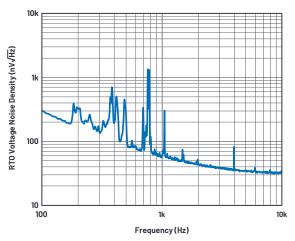

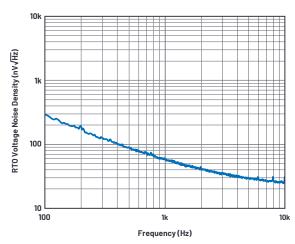

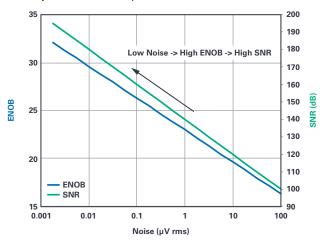

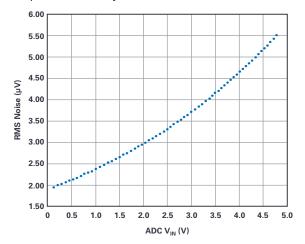

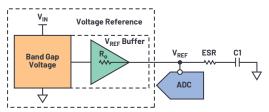

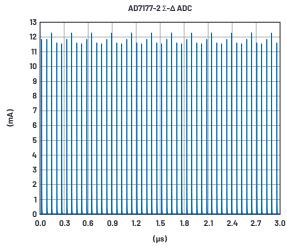

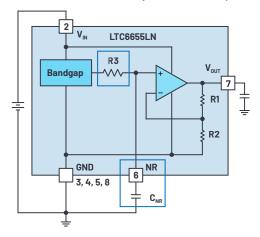

This article explains the impact of the voltage references in a high accuracy >20-bit data measurement system. To achieve this high resolution, a signal chain with exceptionally low noise is required. To provide perspective, to achieve 25-bit resolution, or 152 dB dynamic range, the maximum allowable system noise is  $0.2437~\mu V$  rms.

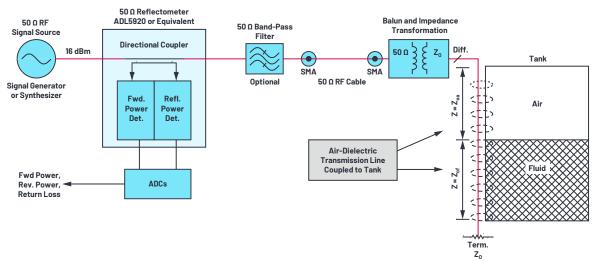

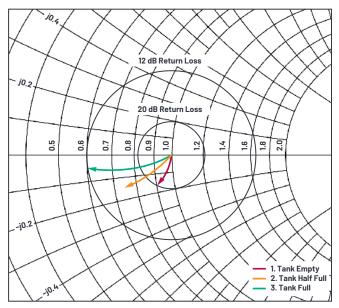

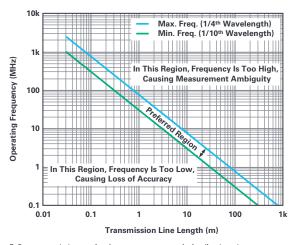

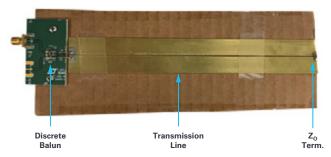

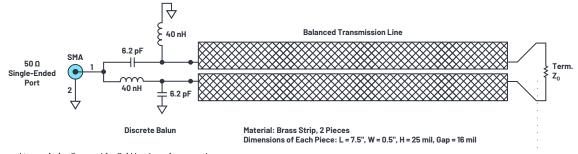

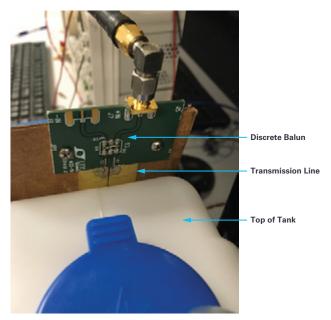

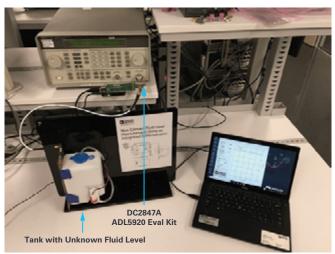

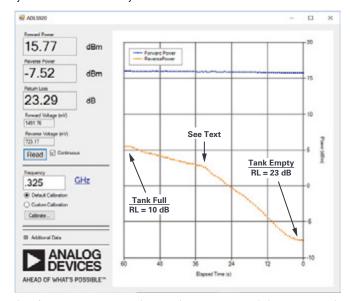

64 Contactless Fluid-Level Measurement Using a Reflectometer Chip

Fluid-level measurements can be accurately measured through the wall of a nonmetallic tank by placing an air-dielectric transmission line up against the side of the tank and sensing the RF impedance. This article provides an empirical design example that illustrates how a reflectometer device such as Analog Devices' ADL5920 can simplify the design.

## Reduce Power Supply Requirements for Ceramic Capacitors with a High Efficiency, High Frequency, Low EMI DC-to-DC Converter

Next, the price of multilayer ceramic capacitors (MLCCs) has risen sharply over the past several years. Ceramic capacitors are used in power supplies on the output to lower the output ripple and to control output voltage overshot and undershot due to high slew rate load transients. The input side requires ceramic capacitors for decoupling and to filter EMI, due to their low ESR and low ESL in high frequency applications.

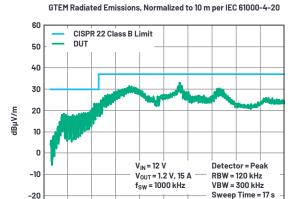

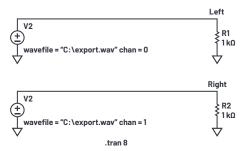

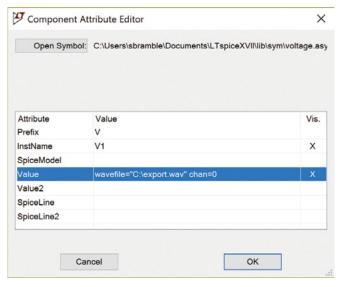

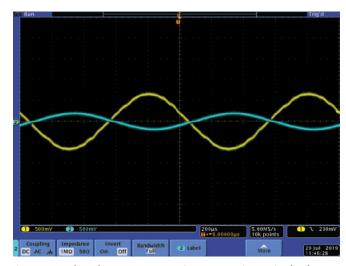

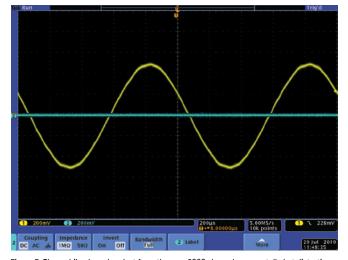

## Rarely Asked Questions—Issue 175: Fun with WAV Files in LTspice: Using Stereo and Encrypting Voice Messages

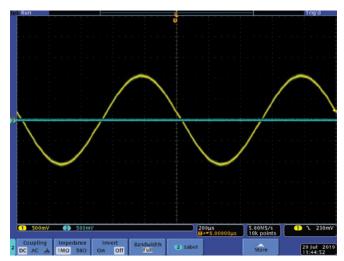

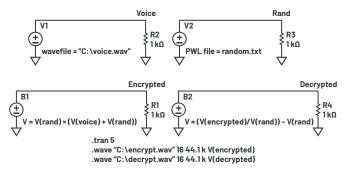

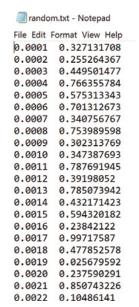

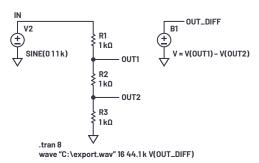

The next topic is: fun with WAV files using LTspice. LTspice has many superpowers, but its handling of audio files is one of its more impressive capabilities. LTspice can be used to generate WAV files as an output of a circuit simulation, as well as to import WAV files to excite a circuit simulation. This article details how to use LTspice audio WAV files for the lesser known syntax of stereo (and higher channel count).

## Bernhard Siegel, Editor

Bernhard became editor of Analog Dialogue in March 2017. He has been with Analog Devices for over 30 years, starting at the ADI Munich office in Germany. In his current role as the chief technical

editor, he is responsible for the worldwide technical article program within Analog Devices.

Bernhard has worked in various engineering roles including sales, field applications, and product engineering, as well as in technical support and marketing roles.

Residing near Munich, Germany, Bernhard enjoys spending time with his family and playing trombone and euphonium in both a brass band and a symphony orchestra.

You can reach him at bernhard.siegel@analog.com.

Analog Dialogue is a technical magazine created and published by Analog Devices. It provides in-depth design related information on products, applications, technology, software, and system solutions for analog, digital, and mixed-signal processing. Published continuously for over 50 years—starting in 1967—it is produced as a monthly online edition and as a printable quarterly journal featuring article collections. For history buffs, the *Analog Dialogue* archive includes all issues, starting with Volume 1, Number 1, and four special anniversary editions. To access articles, the archive, the journal, design resources, and to subscribe, visit the *Analog Dialogue* home page, *analogdialogue.com*.

## Electric Vehicle Warning Sound System

Andreas Pellkofer, Applications Engineer, Jagannath Rotti, Software Lead, and Danny Ko, Applications Engineer

## Introduction

Traditional combustion engine vehicles emit engine sound, even at low travel speeds. Typically, pedestrians and other traffic participants recognize an approaching or departing vehicle through sight and auditory identification of tire sounds and other emitted noise when the vehicle is out of sight.

Electric vehicles (EVs) do not emit engine sound. Hybrid electric vehicles (HEVs) or plug-in hybrid electric vehicles (PHEVs) move almost silently when traveling at low speeds and before the conventional internal combustion engine (ICE) kicks in. These vehicles are difficult to hear when travelling at speeds less than 19 mph. At greater speeds, tire sound becomes dominant.

Global governing bodies are exploring legislation that seeks to establish a minimum level of sound for PHEVs and HEVs when operating in electric mode so that visually impaired people, pedestrians, and cyclists can hear these vehicles approach and determine from which direction these vehicles are approaching. An example of this legislation can be found on the National Highway Traffic Safety Administration (NHTSA) website.

An electric vehicle warning sound system (EVWSS) produces a series of sounds designed to alert pedestrians to the presence of EVs, HEVs, and PHEVs. The driver can initiate warning sounds (similar to the sound from a car horn, but less urgent); however, the sounds must automatically be enabled at low speeds. These sounds vary from artificial tones to realistic sounds that mimic engine noise and tires moving over gravel.

Analog Devices offers two different solutions for advanced applications with an in-cabin engine sound for an EV as well as an external engine sound. Analog Devices developed a solution based on the ADSP-BF706. For entry-level systems, Analog Devices developed a solution based on the ADAU1450 SigmaDSP°. These solutions can synthesize sound and adjust frequency, sound volume, and other parameters depending on the traveling speed, and these solutions can send the audio to an audio power amplifier. Depending on the requirements of certain legislation, the warning sound can be simulated using combustion engine sounds or any other synthesized tones.

## Blackfin-Based Solution

The ADSP-BF706 Blackfin+\* processor provides a single-chip solution for audio processing and interfacing to the control area network (CAN) bus. Analog Devices developed a CAN software stack that runs on the ADSP-BF706, which enables users to build automotive grade demonstrations with minimal effort (a Vector\* CAN stack can also be used). Additionally, Analog Devices provides full hardware and software reference design and SigmaStudio\* compatibility for live tuning of parameters.

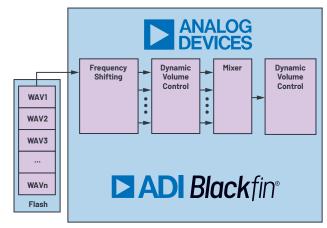

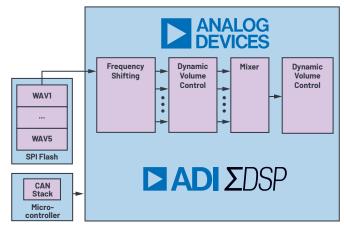

Figure 1 shows the different processing blocks inside the ADSP-BF706. External waveform audio files (WAVs) store signature engine sounds or audio tones. Up to 25 WAV files can be accessed simultaneously from the external serial peripheral interface (SPI). These files are frequency shifted and mixed internally in the digital signal processor (DSP) before adding the dynamic volume control.

Figure 1. Processing blocks on Blackfin+ processor.

The ADSP-BF706 utilizes a memory mapped SPI interface that provides faster, simplified access to the external memory, which eliminates the need for an external double data rate (DDR) memory for this application. Up to 25 WAV files can be accessed simultaneously from the SPI flash memory. The large number of accessible WAV files helps to create more realistic engine sounds.

The ADSP-BF706 can also implement up to  $16\times$  pitch shifting, a recommendation from the United States NHTSA, which increases the frequency of the output sound as the vehicle speed increases. The ADSP-BF706 can dynamically control the volume as the vehicle speed from the CAN bus increases.

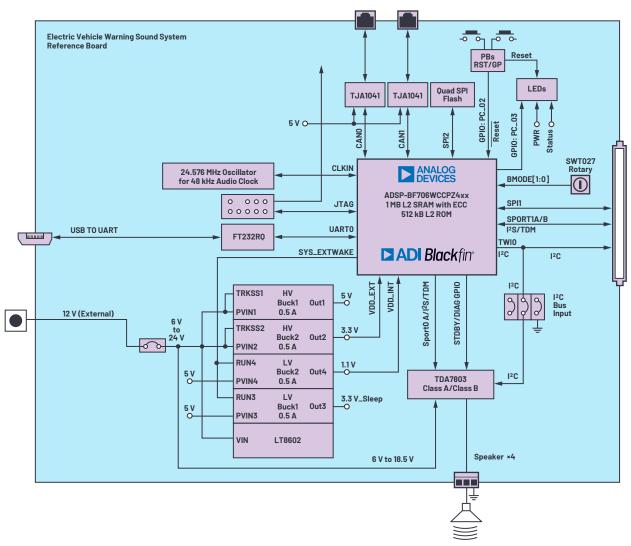

Figure 2 shows a detailed system block diagram. A Power by Linear LT8602 quad monolithic synchronous, step-down regulator provides all voltage rails required in the system, derived from the 12 V car battery supply. The 2 MHz switching frequency allows users to avoid critical, noise sensitive frequency bands—for example, the AM band. The 3 V to 42 V input voltage range of the LT8602 makes the device ideal for automotive applications, which must regulate through cold crank and start stop scenarios with minimum input voltages as low as 3 V and load dump transients more than 40 V.

Figure 2. Detailed system block diagram with a Blackfin+ processor on a full featured board.

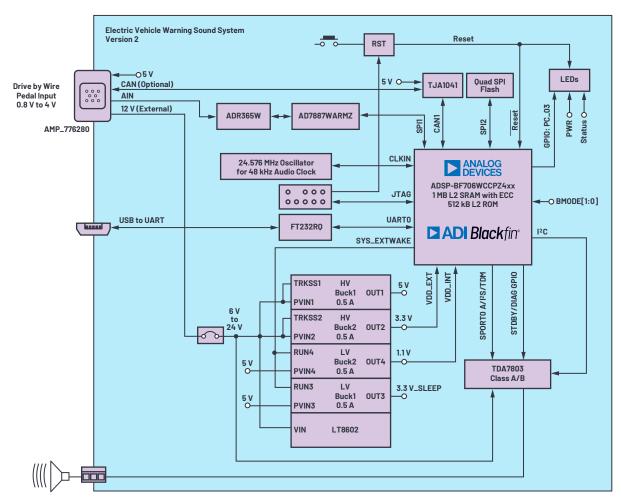

Figure 3 shows an alternative system block diagram with connectors, a reduced set of peripherals, and one automotive qualified connector carrying all relevant signals. This configuration allows the design of a smaller form factor board.

This system solution results in a reduced system bill of materials (BOM) cost because the ADSP-BF706 acts as a microcontroller and an audio processor.

For full details on the solution, see the EVWSS v1 Demo Manual and the EVWSS v2 Demo Manual, which are provided in the software download package. This software package (EVWSS-BF\_SRC-Rel2.0.0) is available by request from the Software Request Form page on the Analog Devices website. For full details on the ADSP-BF706, see the ADSP-BF70x Blackfin+TM Processory Hardware Reference and the ADSP-BF7xx Blackfin+TM Processor Programming Reference.

## EVWSS Software Architecture for the ADSP-BF706 Blackfin+ Processors

The EVWSS software architecture is based on the ADSP-BF706 hardware architecture. The processor dependence on the hardware architecture is due to the memory mapped SPI. The CAN interface reads directly from the flash memory using memory mapped SPI. This feature reduces the complexity of the EVWSS library and makes the memory access efficient for warning sound generation.

Figure 3. Detailed system block diagram with a Blackfin+ processor on a board with reduced components.

## Software Components

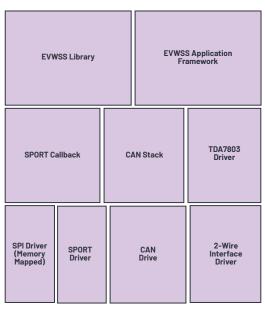

The EVWSS software architecture consists of the components shown in Figure 4.

This section details the software components. The SPORT callback feature maps to the audio data sample rate and runs in the SPORT transceiver interrupt service routine (ISR) context, reading flash files (SPI memory mapped), performing audio manipulation using the EVWSS library, and sending out modified audio on the SPORT transceiver interface. The EVWSS library holds the different functions to synthesize the warning sound. The EVWSS library also receives vehicle speed input from the CAN stack (or the universal asynchronous receiver and transmitter (UART) interface for debugging). The TDA7803 driver controls the external power amplifier to generate the warning sound. The EVWSS application framework configures the system peripherals, CAN stack, and the TDA7803 driver.

## **EVWSS Library Functions**

The following sections describe the functions of the EVWSS library. For full details, see the Electronic Vehicle Warning Sound System Release Notes, which can be found in the software download package.

Figure 4. EVWSS software architecture block diagram.

## Pitch Control

Pitch shifting is the concept of shifting the spectrum of the audio signal based on a control input. In the EVWSS application, the base pitch of the WAV file is shifted depending on the vehicle speed input.

## Frequency Modulation and Amplitude Modulation

The engine sound is dependent on the engine strokes, which include intake, compression, power (expansion), and exhaust. These strokes create frequency modulated tones instead of just pure tones. Vary the pitch shift parameter across the samples to achieve frequency modulation.

Two kinds of modulation (sawtooth and triangular) are included in this application. In sawtooth modulation, the frequency ramps from lowest to highest and then back to lowest with a jump. In triangular modulation, the frequency ramps from lowest to highest and then ramps back down to lowest.

## Audio Mixing in Slew

For audio mixing, configure the various gains with respect to vehicle speed.

## Playback of WAV Files

Although the required WAV files are present in flash, the user can play or stop some of the WAV files, depending on the dynamic conditions.

## SigmaDSP-Based Solution

For entry-level applications, an ADAU1450 SigmaDSP processor can be used as an alternative to the ADSP-BF706 processor. For evaluation purposes, the EVAL-ADAU1452 evaluation board can be used.

Figure 5 shows the different processing blocks inside the SigmaDSP processor.

Figure 5. Processing blocks on SigmaDSP processor.

The following software requirements are supported in the ADAU1450 using the SigmaStudio programming environment:

- ► Multiple tone generation

- ▶ Dynamic volume control with up to 64 ranges

- Sound mixing

- ► Limiter

- ▶ Pitch shifting that increases audio pitch as speed increases

- ► Simultaneous playback of up to 5 WAV files from the SPI flash memory

Analog Devices provides an engine sound simulator module in SigmaStudio to simplify engine sound tuning and reduce the number of external, simultaneous WAV files required. The engine sound simulator can internally generate up to 32 harmonics. The order and amplitude of these harmonics can be programmed through the graphical user interface (GUI).

The harmonic generator module is available as part of the ESS Toolbox. It can be downloaded directly from the SigmaStudio download page (Rev 4.4. upward). Note that SigmaStudio cannot support a CAN software stack, and an external microprocessor is required.

## SigmaStudio

SigmaStudio is a graphical programming environment originally designed for the SigmaDSP portfolio of processors. This software has a built in library of algorithms developed specifically for automotive applications. The GUI simplifies the tuning process and provides controls and filter coefficients that can be varied on the fly without the requirement for writing code. SigmaStudio can be downloaded from the SigmaStudio page on the Analog Devices website.

## Conclusion

Analog Devices offers comprehensive solutions for an entry-level system and for an advanced engine sound system that supports in-cabin engine sounds and external engine sounds. This article aims to ease the decision making process for the user, as well as reduce user time to market. Analog Devices offers a complete system solution, including the necessary software components for rapid prototyping and product development.

## About the Author

Andreas Pellkofer graduated from Technical University of Munich in electronic and information technology. He joined Analog Devices 2006 as an applications engineer working with the Blackfin processor family. Later he mainly dealt with automotive customers for DSPs. In 2013, he moved into a system engineer role in the Digital Video Products Group, focusing on video transport and camera systems for automotive. In 2018, he became part of the Emerging Systems and Technologies Group working on in-cabin vital sign monitoring and hands-on detection solutions. He can be reached at andreas.pellkofer@analog.com.

## About the Author

Jagannath Rotti graduated from PES Institute of Technology, Bangalore with a degree in electronics and communication. He has 13 years of automotive software experience. Prior to joining Analog Devices, he worked at Robert Bosch and Autoliv in the powertrain and safety domains, respectively. At ADI, he is a software lead in the Automotive SW Team, mainly working in cabin electronics in general and automotive audio buses. His areas of interest include automotive networks, network security and cryptography, audio algorithms, autonomous driving, sensor fusion, and Sanskrit literature. He can be reached at <code>jagannath.rotti@analog.com</code>.

## About the Author

Danny Ko is an automotive system applications engineer for audio and emerging technologies based in Seoul, Korea. Danny joined ADI in 2004 as a DSP FAE and supported Samsung, LG, and broad market for three years before changing his focus to automotive in 2007. In 2010, Danny transferred to the automotive segment as an automotive system application engineer and worked in the infotainment area, primarily in audio applications. Since 2018, his work has extended to emerging technology. He can be reached at <a href="mailto:danny.ko@analog.com">danny.ko@analog.com</a>.

# ADI SDR Transceivers Enable Amateur Space Communication

Diego Koch, Applications Engineer

Radio amateurs recently received another way to provide uninterrupted worldwide radio coverage. By means of a new geostationary satellite, it is now possible to reliably cover one-third of the Earth in just one hop. In order to contact the satellite, it is necessary to use dedicated equipment because the access frequencies are different from the ones used to bounce radio signals from the ionosphere. The new software-defined radio (SDR) approach to radio transceivers offers multiple advantages, such as flexible reconfiguration and the capability to observe the whole band of interest at a glance, just to name a few.

This article begins with an overview of this satellite, the story behind it, the areas covered, and how it can be accessed. Then the realization of a practical radio station by using the ADALM-PLUTO SDR, based on one of the ADI SDR transceivers, will be presented.

## The Satellite

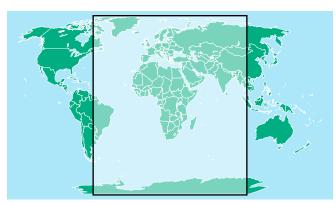

Launched in 2018 from Cape Canaveral, the Es'hail-2 communication satellite of the Qatar satellite company Es'hailSat provides television, voice, internet, corporate, and government communication services across Europe, the Middle East, Africa, and beyond. It has been operational since February 2019 and has been positioned above central Africa in a geostationary orbit. From a height of 36,000 km, it covers an area spanning from Brazil to Malaysia, from the Faroe Islands to Antarctica, as shown in Figure 1.

Figure 1. The Earth seen by Es'hail-2.

Es'hailSat was established in 2010. Based in Doha, Qatar, the company owns and operates satellites to serve broadcasters, businesses, and governments. In order to promote and foster space technology development in Qatar, Es'hailSat initiated the development of new technology for the Qatar Amateur Radio Society (QARS), a national nonprofit organization for amateur radio enthusiasts, together in partnership with Amateur Satellite Corporation (AMSAT), another global nonprofit organization. AMSAT designs, builds, arranges, launches, and operates satellites carrying amateur radio payloads. AMSAT affiliated national organizations exist in various countries, including AMSAT Germany (AMSAT-DL), which became involved on behalf of QARS in December 2012. This collaboration has made it possible to equip the Es'hail-2 satellite with two dedicated transponders, providing the first amateur radio geostationary communication capability that connects users across the visible globe in a single hop and in real time.

Many amateur satellites receive an OSCAR (orbiting satellite carrying amateur radio) designation. These satellites can be used free of charge by licensed amateur radio operators for voice and data communications. So far, they have been launched into low Earth orbits (LEOs) and into highly elliptical orbits (HEOs), and what all of them have in common is that it is necessary to track them with antennas when they appear above the horizon for just a few minutes. Once they disappear below the horizon, the communication is no longer possible. Satellites on a geostationary orbit have the advantage that, as observed from Earth, their positions do not shift in the sky. Although the antennas on Earth do not have to move to access them, the big distance of 36,000 km sets new challenges in terms of free space power loss, antenna pointing accuracy, and latency—about 250 ms for a trip from one ground-based transmitter to the satellite and back to another ground-based transmitter. The nickname given to Es'hail-2 is OSCAR100 because it is the one hundredth satellite to carry an amateur radio payload.

## Access to Es'hail-2

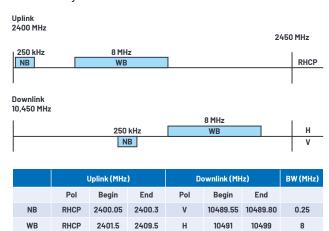

Radio amateurs have worked with satellites for many years. Traditionally, this has been done using analog downconverters and upconverters that shift the received and transmitted signals to and from the amateur bands where transceivers operate. The uplink (from Earth to satellite) and downlink (from satellite to Earth) frequencies used by satellites are sometimes beyond the capabilities of available transceivers. Es'hail-2 has two transponders: one for narrow-band (NB) transmissions and one for wideband (WB) transmissions. In this section, we will talk about the narrow-band transponder. Since, on this transponder, the available bandwidth is only 250 kHz, to accommodate multiple channels it is necessary to use appropriate modulation techniques. The types of analog modulation that are most commonly used are telegraphy (Morse code, also called continuous-wave (CW)) or telephony (voice, also called single sideband (SSB)).

Uplink is at 2.4 GHz (13 cm band) in right hand circular polarization (RHCP) and downlink is at 10.45 GHz (3 cm band) in either horizontal (H) or vertical (V) polarization. Radio amateurs have the privilege to transmit in the 13 cm band (2300 MHz to 2310 MHz and 2390 MHz to 2450 MHz) as licensed radio operators for satellite communication with sufficient power and high gain antennas. This band overlaps with the civilian radio allocation 2400 MHz to 2500 MHz, which is part of the industrial, scientific, and medical (ISM) bands. One of the most popular unlicensed emissions on the ISM band is wireless LAN. The transponders are detailed in Figure 2.

Figure 2. Transponders of Es'hail-2.

## The Innovative SDR Approach

The change that came with the introduction of SDR in its many variants also impacted the amateur radio world. Even though most transceivers still have the same controls of the older analog ones, many of them incorporate digital signal processor (DSP) technology after the mixer, at the intermediate frequency level. Some of them are also able to directly sample the whole shortwave portion of the spectrum (dc to 30 MHz). One advantage of the SDRs is that their performances do not degrade with time, since many critical analog components are partially replaced by digital algorithms. Another advantage is that the same performances that require expensive components in analog radios, like mixers or filters, can be obtained in a more cost-effective way by complementing them with different elements like analog-to-digital converters (ADCs) and DSPs. The integration of

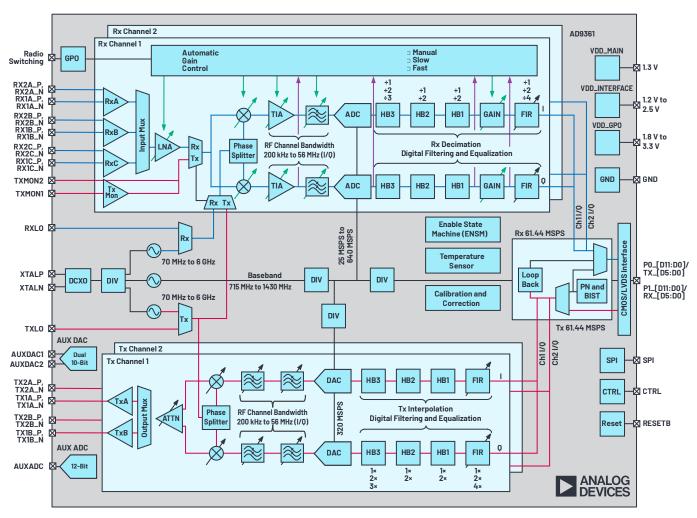

multiple blocks, such as image rejection mixers, oscillators, and ADCs, in the same silicon device has made feasible new receiver architectures that are very critical to implement with discrete technology. One example is devices like the AD9363/AD9364 RF agile transceivers that combine all RF front-end, mixed-signal, and digital blocks in a single device for both receiving and transmitting. When paired with an FPGA that manages the digital data flow into and out from the device, the elements remaining to build a complete station are the antennas, the power amplifier, and the software algorithms running on a computer.

ADI offers the ADALM-PLUTO SDR to demonstrate the capabilities of the AD9363, shown in Figure 3. This is a cost-effective hardware tool that can be used by engineers to develop applications where radio is involved based on the new SDR approach. The AD9363 has a receive and transmit bandwidth of 20 MHz and it can easily receive both the narrow and wide downlink transponders of the Es'hail-2, once they are downconverted externally to its frequency range of 235 MHz to 3.8 GHz. It can transmit on the uplink frequencies without any external upconverter. Another beneficial feature, when compared to devices of the same class and price, is that it has two connectors for receive and transmit, so it supports full-duplex operation. The normal amateur radio interaction is half-duplex (you either talk or listen), but the ability to receive your own transmission in real time allows you to understand whether you are modulating in a clear way, or whether you need to increase/decrease the transmitted power. It also helps to have the ability to point the transmit antenna to the sky once the receive antenna has been adjusted.

The ADALM-PLUTO is supported for both transmission and reception by some free software packages, often written by radio amateurs themselves. One example is the SDR Console by Simon Brown (amateur radio callsign G4ELI). This software manages the interaction between the user and the transceiver, and implements demodulation and modulation in software.

### An SDR Satellite Station

Radio amateurs are well known for building their own hardware and repurposing existing equipment to fit their needs. With receive antennas and downconverters, the cheapest alternative is an ordinary satellite dish for commercial satellite television and a low noise block (LNB). The LNB contains the waveguide and the downconverter that translate the incoming downlink signal at 10.450 GHz to less than 1 GHz, which falls inside the receivable band of the SDR. Narrow-band modulation types such as CW (a few tens of Hz) or SSB (less than 3 kHz) mandate highly stable local oscillators to avoid continuous retuning, which is less critical in wideband modulation types such as the ones used by broadcast television (some MHz). In modern digital communications, compensation for frequency offset and long-term drift due to thermal issues is built into the standards and implemented by everyone. Unfortunately, this is not standardized, or not implemented, for many narrow-band modulation schemes implemented by amateur radio operators, and the expectation is that PLL or sample rate accuracy and drift either in the LNB or baseband signals is perfect. To ensure this assumption is correct, sometimes high precision/low drift reference clocks are used. Since many amateur radio operators are more comfortable swapping a reference clock than implementing complex digital signal processing techniques, many will recommend this easy fix.

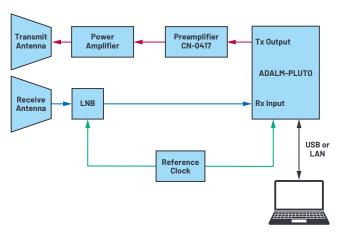

Figure 3. ADALM-PLUTO and its transceiver AD9363.

Since the uplink frequencies are within the WLAN 2.4 GHz band it is possible for licensed operators to repurpose existing WLAN equipment like power amplifiers and high gain antennae. The ADALM-PLUTO has about 5 dBm power output, which is insufficient to drive a power amplifier that has an output power of a few watts. The CN-0417 reference design, based on the ADL5606 20 dB power amplifier and powered by the LTM8045 SEPIC micromodule converter, yields enough power gain to overcome this limitation. Figure 4 shows how a communication station can be laid out. The station can also be rapidly deployed in the field to support emergency communication.

Figure 4. SDR satellite radio station.

## Summary

In conclusion, we see a shift toward SDR technology in radio communication. This has been possible by integrating multiple analog and mixed-signal blocks in one device. Immediate advantages are cost-effectiveness, improved reliability, and reconfigurability.

Quoting the words of Drew Glasbrenner, KO4MA, AMSAT VP Operations, "May the 100th OSCAR satellite be the guide star to future amateur radio satellites and payloads to geostationary orbit and beyond."

### References

"Es'hail-2/00-100." AMSAT-UK, 2019.

"Space Communication." American Radio Relay League, 2019.

Taylor, Wyatt and David Brown. "RF Transceivers Provide Breakthrough SWaP Solutions for Aerospace and Defense." *Analog Dialogue*, September 2016.

## About the Author

Diego Koch is an applications engineer with the European Centralized Applications Center based in Munich, Bavaria, Germany. He has been working in the semiconductor industry since 1998 and joined Analog Devices in 2017, providing design support for the Power by Linear portfolio for the European broad market. He holds a master's degree in electronics engineering from Politecnico di Milano, Lombardy, Italy. He is a radio amateur, licensed in two countries with callsigns IZ2MZL and DK2MZL. He can be reached at diego.koch@analog.com.

## Paralleling Very Low Dropout Linear Regulators for Increased Output Current and Even Heat Distribution

Molly Zhu, Senior Applications Engineer and Fei Guo, Field Applications Engineer

### Introduction

Each successive generation of computing systems demands more total power and lower supply voltages than its predecessor, challenging power supply designers to keep pace with higher output current in a small area. At high power densities with low output voltages, the problem of heat dissipation rises to the top of the design priority list, especially for linear regulators in low noise applications. Paralleling LDO regulators can increase the supply current capability and mitigate heat dissipation, reducing the temperature rise of any particular component and the required size and number of cooling devices.

This article shows how to parallel the 3 A LT3033 very low dropout (VLD0) regulator for applications that require a current higher than 3 A, with the added benefit of spreading heat dissipation. The LT3033 can be easily paralleled—and current balanced—due to its built-in output current monitoring feature.

The LT3033 converts 1.14 V to 10 V input supplies to outputs as low as 0.2 V with load currents up to 3 A. The dropout voltage is only 95 mV at full load. Quiescent current is 1.8 mA during operation, dropping to 22  $\mu\text{A}$  when shutdown. Programmable current limit and thermal protection give it the necessary robustness for high current, low voltage applications.

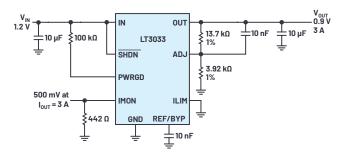

## For Reference: 3 A, Single VLDO Application

Figure 1 shows the LT3033 delivering 0.9 V at 3 A from a 1.2 V input supply. A minimum of 10  $\mu$ F very low ESR ceramic capacitor is required at the IN and OUT pins for stability. Adding a feedforward capacitor ( $C_{FF}$ ) from  $V_{OUT}$  to the ADJ pin can improve the transient response and lower the output voltage noise. A 10 nF bypass capacitor from the REF/BYP pin to GND typically reduces output voltage noise to 60  $\mu$ V rms in a 10 Hz to 100 kHz bandwidth and soft starts the reference. The minimum input voltage required for regulation equals the regulated output voltage  $V_{OUT}$  plus the dropout voltage or 1.14 V, whichever is greater. A demonstration board is shown in Figure 2.

Figure 1. LT3033 typical application.

Figure 2. LT3033 demonstration board.

Current limit is programmable by connecting a single resistor from the ILIM pin to GND, accurate to  $\pm 12\%$  over a wide temperature range. The external current limit may be overridden by internal current limit with foldback when the input and output differential voltage exceeds 5 V.

LT3033 provides an output current monitor by pulling the IMON pin to GND through a resistor. The IMON pin is the collector of a PNP, which mirrors the LT3033 output PNP at a ratio of 1:2650. The resistor voltage is proportional to the output current if it is not higher than  $V_{\text{DUT}}$  – 400 mV.

$$I_{OUT} = 2650 \times (V_{IMON}/R_{IMON}) \tag{1}$$

This output current monitor enables current sharing for multiple LT3033s.

Despite its tiny size, the LT3033 also includes a number of protection features, including internal current limit with foldback, thermal limit, reverse current, and reverse-battery protections.

## Using Two LT3033s in Parallel for a 6 A Application

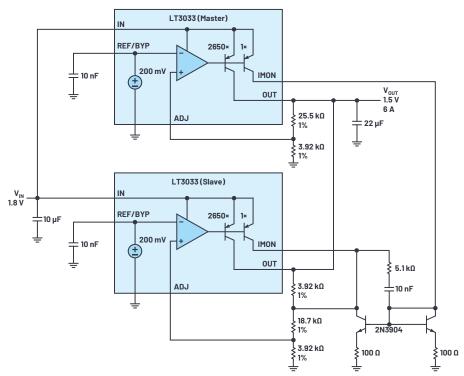

For applications that require more than 3 A, multiple LT3033s can be paralleled by taking advantage of its current monitor feature. Figure 3 illustrates two LT3033s in parallel together with two 2N3904 NPN devices to generate a 1.5 V, 6 A output. The individual IN pins and OUT pins are tied together, respectively. One LT3033 acts as master, controlling the LT3033 slave device.

The IMON pins combined with an NPN current mirror create a simple amplifier. This amplifier injects current into the feedback divider of the slave LT3033 to force the IMON currents from each LT3033 to be equal. The 100  $\Omega$  resistors provide 113 mV emitter degeneration at full load to guarantee good current mirror

matching. The output voltage of the slave LT3033 is set at 1.35 V, 10% lower than the circuit output to ensure the master LT3033 stays in control. The feedback resistors of the slave LT3033 are split into sections to ensure adequate headroom for the slave NPN. A 10 nF, 5.1 k $\Omega$  capacitor and resistor combination added to the IMON pin of the slave device frequency compensates the feedback loop.

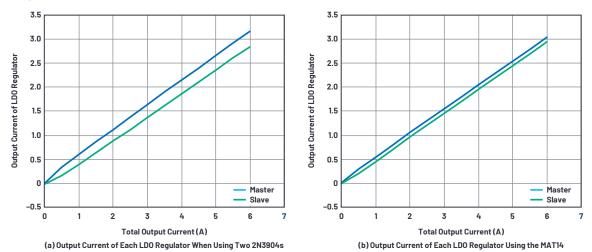

Though this circuit can supply 6 A load current, current sharing accuracy is limited by the mismatch between two NPN devices—mismatches result in uneven heat distribution on the board. Higher current sharing accuracy can be achieved by using a matched monolithic transistor, such as the MAT14 from Analog Devices, to replace the two discrete NPN devices. The MAT14 is a quad monolithic NPN transistor that offers excellent parametric matching. Its maximum current gain matching is 4%.

Figure 4 compares the output current of each LDO regulator using discrete and matched NPN devices, respectively. Compared to the 2N3904, the MAT14 current mirror reduces the current mismatch from 5.3% to 1.6%.

Figure 3. Paralleling two LT3033s.

Figure 4. Current sharing mismatch is reduced by using the MAT14 matched monolithic quad transistor with parallel LDO regulators.

Figure 5. Four LT3033s in parallel using the MAT14.

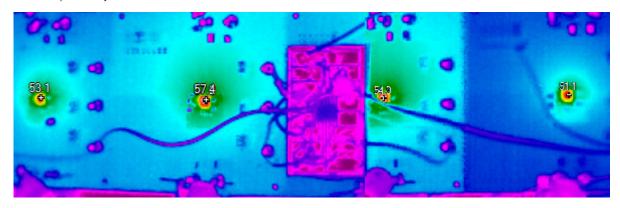

Figure 6. Thermal performance of four LT3033s in parallel.

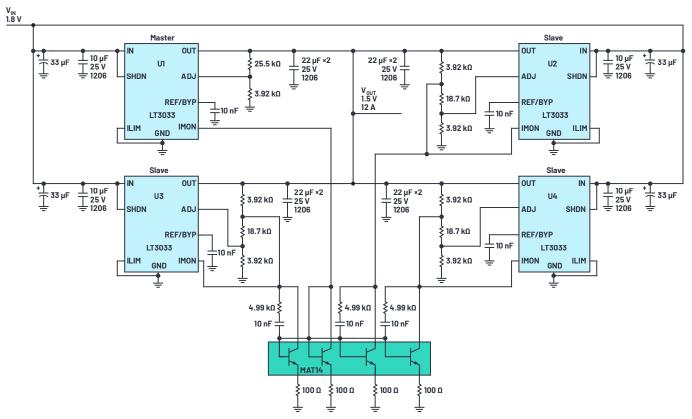

## Paralleling Four LT3033s Using Matched Components for Well Balanced Currents and Even Heat Spreading

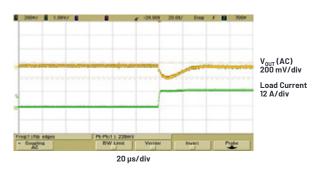

The paralleling circuit architecture is scalable to as many LT3033s as needed by extending the current mirror and adding slave LT3033 devices. Figure 5 shows a solution with four LT3033s in parallel using the MAT14 for current sharing. The thermal performance is shown in Figure 6. The four LT3033s reach temperatures ranging from 51°C to 58°C. Considering the voltage drop along the input trace for each part, the heat spreads evenly on the board, indicating balanced current sharing for this solution. Figure 7 shows the transient response of a 1.5 V output, 12 A power supply operating from a 1.8 V input.

Figure 7. Load transient response of four LT3033s in parallel.

## Conclusion

The LT3033 is a 3 A VLD0 regulator in a 3 mm  $\times$  4 mm package. Multiple LT3033 VLD0 regulators can be paralleled for high current applications because of their built-in output current monitor feature. With only 95 mV typical voltage drop at full load, LT3033 is ideal for low input voltage to low output voltage, high current applications, yielding comparable electrical efficiency to a switching regulator. Other features include programmable current limit, power good flag, and thermal limiting for reliable and robust solutions. Battery-powered systems benefit from low quiescent current and reverse-battery protection.

## About the Author

Huiyu (Molly) Zhu is a senior applications engineer in Analog Devices' Power by Linear Group. She received her B.S.E.E. and M.S. degrees from Tsinghua University, China in 1998 and 2000, respectively, and a Ph.D. degree in electrical engineering from Virginia Polytechnic Institute and State University, Blacksburg, Virginia in 2005. He can be reached at molly.zhu@analog.com.

## About the Author

Fei Guo is a field applications engineer for Analog Devices, supporting the San Francisco Bay area's broad market. His previous role was a senior applications engineer in Analog Devices, supporting the isolated power converter product line. Fei has an M.S. degree in electrical engineering from Santa Clara University. He has designed power converters for instrumentation, automotive, industrial, and communications products. Fei's hobbies include hi-fi audio, photography, and playing with his two young kids. He can be reached at fei.guo@analog.com.

## RAQ Issue 173: On Building Physically Accurate Analog Switch Macromodels

Barry Harvey, Analog IC Designer

## Ouestion:

Can I improve the LTspice model of an analog switch in case my analog design contains switches and muxes?

## Answer:

Sure; it is not difficult to generate your own models.

## Introduction

I was testing a circuit and found many discrepancies from the paper design I used to create it. The dynamics of the circuit were a bit unexpected, and the noise level was much larger than required. I needed to bring the circuit to a simulator to fully understand it.

The circuit involved analog switches and op amps. There are good macromodels for the op amps employed, but the analog switch macromodel was not designed for generality. In the header of the switch macromodel file is the warning that modeled parameters were only valid for a specific supply and temperature. Well, wouldn't you know it: my circuit has different operating conditions from the modeled one. The thing about analog switches is that they are so

general-purpose that one operating point is not enough. The existing industrystandard models provide a good start, but if you enter the analog performance arena, you might need a new macromodeling approach that brings your simulation to a higher level.

As I began to browse through various analog switch macromodels from Analog Devices and other IC companies, I noticed that all their headers tell of no supply nor temperature dependence being modeled. Thus, I would have to make my own macromodel.

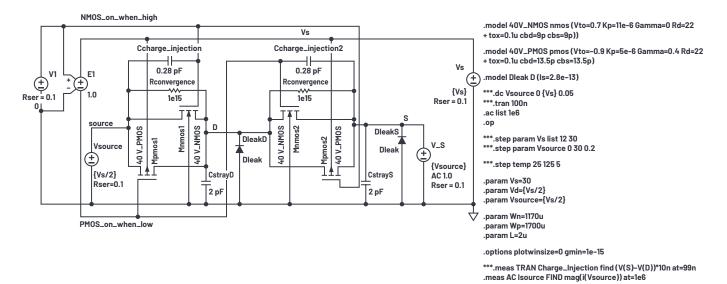

My philosophy in this work is that full transistors in the analog switches using the simplest device models provide all the behaviors to be emulated, but the interface from control pin to MOS gates should be the simplest behavioral components.

All work here is done with the LTspice simulator; the code would work on other simulators with a translation of the LTspice behavioral devices to SPICE-like polynomial functions.

We will develop the simulated behaviors in a specific sequence.

## Developing LTspice Model Parameters for On Resistance

We will use the simplest model to run real MOS devices. To model on resistance, we will employ:

- W/L, the width (W) divided by the length (L) of an MOS device. W/L is the size or relative strength of the device.

- ► V<sub>TO</sub>, the threshold voltage; and gamma, which modifies V<sub>TO</sub> with device back-bias. The back-bias is the voltage between the on device and its body voltage; the body is frequently connected to the positive supply for the PMOS and to the negative supply for the NMOS in the switch.

- ►  $K_{P'}$  in the model, also known as K' or K-prime. This parameter models the strength of the process and is multiplied by W/L to scale MOS currents. For a given process, the NMOS will have ~2.5× the  $K_P$  of the PMOS.

- ► RD, the parasitic resistance of the device's drain.

Different MOS processes have different intrinsic parameters. Table 1 is a collection of common CMOS processes, their characteristics, and estimated intrinsic parameters related to on resistance.

**Table 1. Typical Semiconductor Process Parameters**

| Voltage<br>Node (V) | Device<br>Construction | Gate Oxide<br>Thickness<br>(m) | V <sub>to</sub> ,<br>n/p, V | Gamma,<br>n/p, V <sup>0.5</sup> | K <sub>P</sub> ,<br>n/p,<br>μΑ/V² | L, μ | R <sub>D</sub> ,<br>n/p, Ω     |

|---------------------|------------------------|--------------------------------|-----------------------------|---------------------------------|-----------------------------------|------|--------------------------------|

| 40                  | Drain drift region     | 10-7                           | 0.7/-0.9                    | 0.4/-0.57                       | 11/5                              | 2    | ~80%<br>of R <sub>DS(ON)</sub> |

| 15                  | Soft drain diffusion   | 4×10 <sup>-8</sup>             | 0.7/-0.9                    | 0.4/-0.57                       | 22/10                             | 1.5  | ~20%<br>of R <sub>DS(ON)</sub> |

| 5                   | Simple                 | 1.4 × 10 <sup>-8</sup>         | 0.7/-0.9                    | 0.4/-0.57                       | 80/28                             | 0.5  | ~0                             |

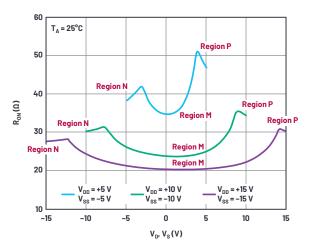

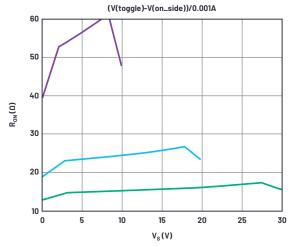

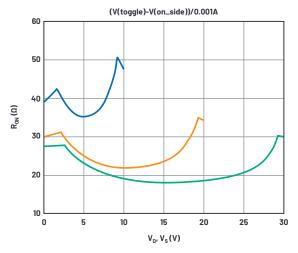

Let us look at the ADG333A  $R_{\text{ON}}$  curves we wish to reproduce in Figure 1.

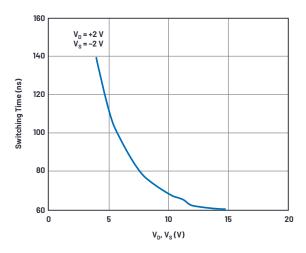

Figure 1.  $R_{DN}$  as a function of  $V_D$  ( $V_S$ ), dual supply.

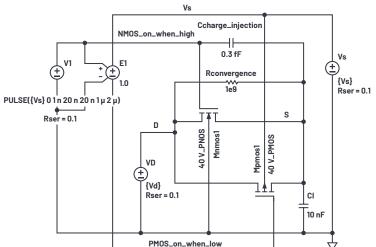

Figure 2. On resistance test circuit.

We see a general trend for this and any other analog switch that higher supply voltage reduces on resistance. As more voltage is applied to the switch MOS gates, the on resistance is reduced. We also see a distinct variation of on resistance with the analog level. In the N regions, the NMOS transistor in a switch is fully on, and as the analog voltage rises above the negative rail, the PMOS transistor turns on and helps reduce overall on resistance. The inflection point at region N is roughly a PMOS  $V_{\rm TO}$  above the negative supply.

Similarly, in regions P, the PMOS device of the switch is fully on and the NMOS starts assisting the PMOS transistor roughly an NMOS  $V_{10}$  below the positive supply.

Regions M are in the middle of the N and P regions with the NMOS and PMOS working in parallel, but each varying in on resistance depending on the analog signal level between the supplies.

To start the curve-fitting process, we first estimate the size of each transistor. The low voltage curve gives the best curve-fit for transistor  $R_{\mbox{\tiny DSION}}$ . In region N, with the analog signal at the negative supply, the PMOS device is off and  $R_{\mbox{\tiny ON}}$  of the part is equal to the  $R_{\mbox{\tiny ON}}$  of the NMOS transistor. With

$$R_{DS(ON)} = \frac{I}{k_P \left(\frac{W}{L}\right) (vgs - V_{TO})} \tag{1}$$

using the 40 V NMOS typical process values, we set  $R_{DS(DN)}=38~\Omega$  from the curve in Figure 1 and using the process quantities given find WNMOS = 2  $\mu$ A/(38  $\Omega$  × (11 × 10<sup>-6</sup>  $\mu$ A/V<sub>2</sub>) × (10 V – 0.7 V)) = 514  $\mu$ m. The PMOS switch would have an on resistance of 47  $\Omega$  from the above curve and thus a width of 936  $\mu$ m.

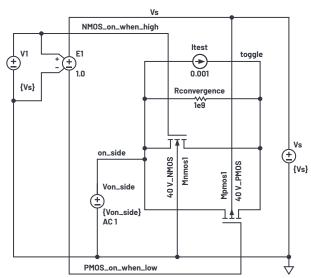

I used the LTspice test circuit in Figure 2. Note that parameters  $R_{\text{DN}}$  and  $R_{\text{DP}}$ , the parasitic drain resistances, are of modest value. I started with a value of 1  $\mu$ , which caused simulator convergence slowdown. The  $R_{\text{DN}}$  value of 1 allows proper simulation speed. Adding  $R_{\text{CONVERGENCE}}$  improved simulator noise and speed by giving the toggle node a convergeable conductance. I tested a floating current source for measuring on resistance.

```

.model 40V_NMOS nmos (Vto=0.7 Kp=11e-6 Gamma=0.4 Rd={Rdn})

.model 40V_PMOS pmos (Vto=0.9 Kp=5e-6 Gamma=0.57 Rd={Rdp})

.dc Von_side 0 {Vs} 0.05

step param Vs list 10 20 30.

*.step param Rdn 0 20 2

***.step param Rdp0 20 2

***.step param Wn 300u 800u 50u

***.step param RDn 1112

.param Von_side={Vs/2}

.param Vs=10

.param Wn=514u

.param Wp=936u

.param L=2u

.param Rdn=1

.param Rdp=1

.param k=0.4

.options plotwinsize=0

```

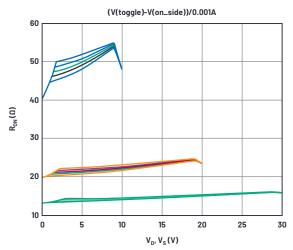

Figure 3 shows the simulated results for various supplies.

Figure 3. On resistance simulation results with initial model values.

This is a good start. The kink at the low voltage end for  $V_s = 30 \text{ V}$  is at 3.6 V in the simulation and 2.7 V in the data sheet. This suggests we reduce the PMOS  $V_{\tau_0}$ , but 0.9 V is already a realistic minimum. Better to adjust the gamma of the PMOS, which was only a guess anyway.

The kink near maximum supply is 2.5 V below the 30 V rail, where in the data sheet it should be ~1 V. Various values of gamma exaggerated the kink voltage from the rail; we will just set the NMOS  $V_{\text{TO}}$  to 1 V and its gamma to zero. A zero gamma is unexpected, but we're only trying to curve-fit. Figure 4 shows simulation results from these values with the gamma of the PMOS stepped for several supplies. We focus on the 30 V curves, which maximize the gamma effect compared to lower supplies.

Figure 4. On resistance simulation results with gamma-p varied.

From the stepped curves, we'll choose a PMOS gamma = 0.4.

On to  $R_{\text{ON}}$ . Observe that the 10 V curves are representative of the data sheet curve at the supply extremes, but the simulation produces too low a  $R_{\text{ON}}$  for

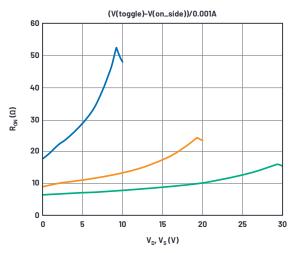

the 20 V and 30 V curves. The  $R_{\text{DN}}$ s are equal to  $R_{\text{DS(DN)}}$ (NMOS) +  $R_{\text{D}}$ (NMOS) at the negative supply extreme and  $R_{\text{DS(DN)}}$ (PMOS) +  $R_{\text{D}}$ (PMOS) at the positive supply extreme. For high supplies, the  $R_{\text{D}}$  parameter will be more significant than W/L, and for low supplies, W/L will dominate. We have two variables to juggle here; too laborious. We will posit that  $R_{\text{DN}}$  varies with supply due to the NMOS being variably enhanced, but the  $R_{\text{D}}$  value doesn't change with supply voltage (okay, it probably does in the case of drains with drift regions, but let's keep this simple). If we note the difference in data sheet  $R_{\text{DN}}$  between 10 V and 30 V supplies (11.4  $\Omega$ ), we can compare that to the above curves where we step only  $W_{\text{N}}$  (width of the NMOS in the switch). After a bit of iterations of  $W_{\text{N}}$  in simulations it's clear that we need  $W_{\text{N}}$  = 1170  $\mu$ m to get the required  $\Delta R_{\text{DN}}$ , quite a lot more than the initial guess. Figure 5 shows our current results.

Figure 5. On resistance simulation results with  $W_N$  determined.

While the  $R_{DN}$  of the NMOS has the right supply sensitivity, the curves are too low a value at zero volts, and we must increase the fixed  $R_{DN}$ . After increasing and iterating  $R_{DN}$ , we get a best value of  $R_{DN}$  = 22  $\Omega$ , and the resulting curves are in Figure 6.

Figure 6. On resistance simulation results with  $R_{DN}$  determined.

We next determine  $W_P$  (width of the PMOS in the switch) to simulate the  $R_{DN}$  at maximum voltage, and get  $W_P$  = 1700  $\mu$ m, again quite a lot more than initially guessed. With  $R_{DP}$  also set to 22  $\Omega$ , we get the final  $R_{DN}$  curve in Figure 7.

Figure 7. On resistance simulation results with  $W_P$  and  $R_{nP}$  determined.

Pretty good agreement here; there are only a few features different from the data sheet. One is that the inflection points are smooth in the data sheet curve but truly pointed in simulation. This is probably because the simple MOS model

used does not support subthreshold conduction, and the simulated device turns truly off at  $V_{T0}$ . Real devices are not off at  $V_{T0}$ , but smoothly reduce current below that voltage

Another error is most obvious in the 30 V curve.  $R_{\text{ON}}$  is 15% low at midsupply compared to data sheet. Perhaps this is due to JFET effects within the drain drift region, also not modeled.

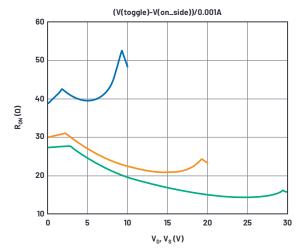

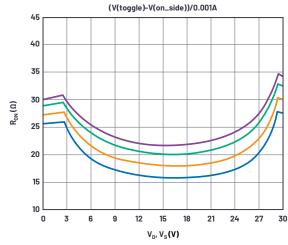

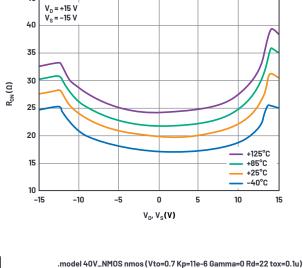

As for temperature, there is fair but not strong compliance, seen in Figure 8.

The simulation has temperature dependence, but not as much as the data sheet curves. In the simulation model the  $R_0$  terms do not have tempco.  $R_0$ s could be modeled by external resistors with correct tempco, but we will leave it as is for simplicity.

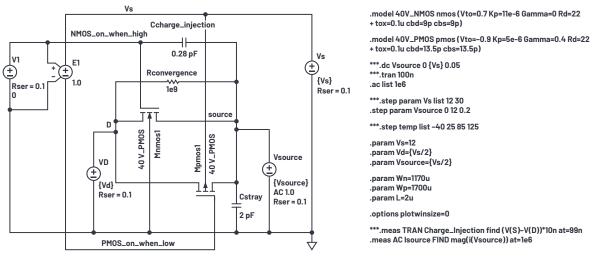

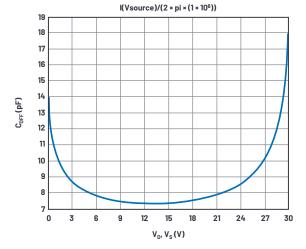

## Obtaining LTspice Model Parameters for Charge Injection

When MOS transistors turn off, the charge in the channel must go somewhere, so it squirts out of the drain and source terminals. When an analog switch is turned off, charge also goes out and is called charge injection. A common way of measuring it is to place a fixed voltage on one end of an on switch and a large capacitor at the other end. When turned off, the charge is captured by the capacitor and a small voltage step occurs. We will now the add gate oxide thickness  $T_{\text{ox}} = 1 \times 10^{-7}$  to the MOS models (gate capacitance is the largest source of charge injection). Our simulation setup is shown in Figure 9.

Figure 8. On resistance simulation and data sheet results over temperature.

.model 40V\_PMOS pmos (Vto=0.9 Kp=5e-6 Gamma=0.4 Rd=22 tox=0.1u)

Rser = 0.1 .step param Vd 0 30 0.2

\*\*\*\*.step temp list -40 25 85 125

.param Vs=30

.param Vd={Vs/2}

.param Wn=1170u

.param Wp=1700u

.param L=2u

.options plotwinsize=0

.meas TRAN Charge\_Injection find (V(S)-V(D))\*10n at=99n

\*\*\*.dc Vd 0 {Vs} 0.05

\*\*\*.step param Vs list 12 33

Figure 9. Charge injection simulation setup.

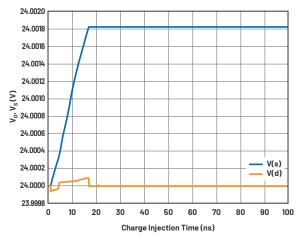

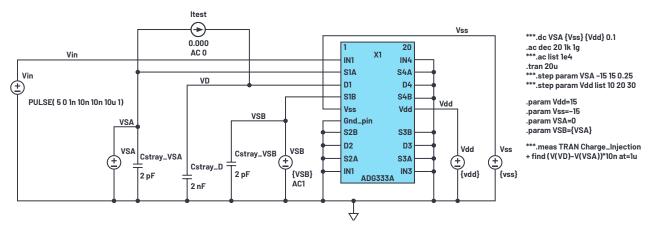

The data sheet charge injection test circuit places a voltage source at the D terminal of a switch, and the capacitor CI at the S terminal of the switch. When the switch transistors are turned off, CI is isolated and integrates charge pumped into it by the switches. The waveform of such an event with  $V_0$  held to 24 V with a 30 V supply is shown in Figure 10.

Figure 10. Charge injection simulation waveforms.

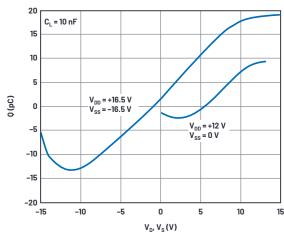

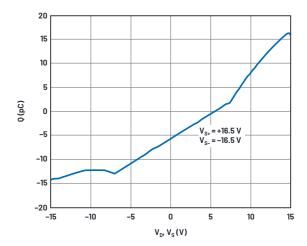

The charge injected is the voltage jump between V(S) and V(D) times the 10 nF hold capacitor. We can step the switch voltage  $V_{\scriptscriptstyle D}$  across the supply voltage and use the .meas statement to capture the value of charge injection at each voltage. Figure 11 shows the data sheet curve and simulated results.

Our simple MOS model does not mimic the shape of the data sheet curve very well, but the peak-to-peak charge injection is 32 pC in the data sheet curves and 31 pC in simulation. Surprisingly close, but if we had to, we could tweak  $T_{\text{ox}}$  to perfect the simulation results.

Figure 11. Charge injection data sheet and simulation waveforms.

There is an offset between the curves that we can compensate for using  $C_{\text{CHARGE\_INJECTION}}$ . After fiddling with some values, we choose an optimal  $C_{\text{CHARGE\_INJECTION}}$  would be reconnected to the PMOS\_on\_when\_low node.

The tweak capacitor  $C_{\text{Charge\_INJECTION}}$  was a convenient way to offset the charge injection vs. the analog voltage simulation curve. What if the peak-to-peak injection simulated were too small? Well, most of the charge injection is mostly the switches' gate voltage swings sending charge through the gate-channel capacitance of the switch transistors. If we simulate too little injection, we can simply increase one or both gate areas. To do this we would increase the parameters L and W of a switch device by the same factor, being careful to not modify the W/L ratio that sets on resistance. Rather than use  $C_{\text{Charge\_INJECTION}}$  we could have increased the NMOS W and L.

Alternatively, we could adjust  $T_{\text{ox}}$  in each device to get better charge injection correlation. This would not be physically possible, but hey—it's just a simulation. With the simple models we are using,  $T_{\text{ox}}$  does not influence other behaviors.

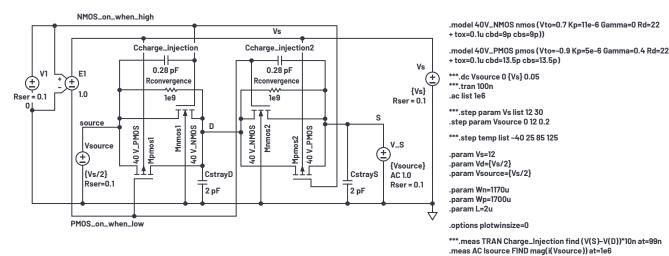

## Obtaining LTspice Model Parameters for Capacitances

Having set up parameters for good  $R_{\text{ON}}$  and charge injection simulation results, we now simulate S and D terminal capacitances.

One important point is that both the drain and source regions of high voltage MOS switches must have drift regions. As a switch, you can't tell the functional difference between sources and drains, and the body potential to both drains and sources will require the drift regions in each. This is also true of the medium-voltage soft diffusions, but non-existent in low voltage MOS. We have lumped the drift region resistance that would exist in both drain and source into  $R_{\text{D}}$  and that works fine for switches, but not transistors in saturation.

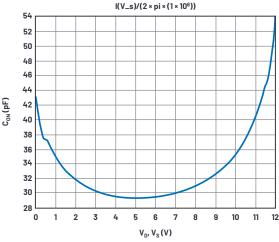

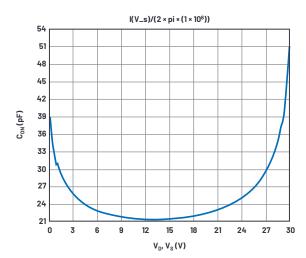

Figure 12 shows our simulation setup.

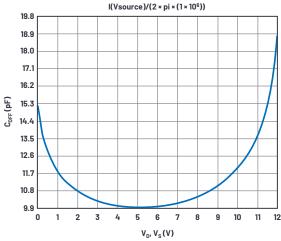

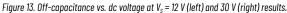

In LTspice, you can run an .ac on only one frequency, using the list option in .ac, but offer only one frequency argument (1 MHz here). Then you run a .step V<sub>SOURCE</sub> dc voltage across the supply range to get a capacitance vs. voltage sweep.

The D terminal of the off-switch device is held to midsupply. The S terminal, renamed source here to prevent confusion with  $V_s$ , is driven by a voltage source with dc value sweeping from 0 V to  $V_s$  and with an ac drive of 1 V. Capacitance is derived from I( $V_{\text{SOURCE}}$ )/(2 ×  $\pi$  × 1 MHz × 1 V). The logic drive V1 is changed to 0 V to turn the transistors off.

Drain and source capacitances to bulk are  $C_{80}$  and  $C_{8S}$  respectively in the model statement. There are built-in default concentrations, built-in voltage, and exponent in the model that make  $C_{80}$  and  $C_{8S}$  voltage variable. Because they are symmetrical, drain and source capacitances would be made equal. Further,

because the PMOS is a different width from the NMOS, the ratio of  $C_{BD,NMOS}/C_{BD,PMOS}$  =  $C_{BS,NMOS}/C_{BS,PMOS} = W_N/W_P$ , which we established in the on resistance modeling. Figure 13 shows the simulation results.

The displays are I( $V_{\text{SOURCE}}$ )/(2 ×  $\pi$  × 1 MHz), which is capacitance. LTspice doesn't know this and displays pA instead of pF.

Unfortunately, we have no data sheet curves to compare to. We do know from the specification table in the data sheet that the capacitance—probably at midsupply, but not specified in the data sheet—is typically 7 pF at 30 V supply and 12 pF at 12 V supply. I adjusted the CBs to obtain the 7 pF curve at 30 V, but only simulated 10 pF at a 12 V supply. After fiddling with built-in potential and capacitance formula exponent, the model used allows no flexibility to improve the 12 V/30 V compliance.

Figure 14 shows the on-state capacitance simulation setup.

Figure 12. Off-capacitance test simulation setup.

Here the right switch of a full spdt switch is on, and the left switch is off and connected to a  $V_s/2$  source. The capacitances of the right half of the left switch and full capacitances of the right switch, plus inevitable parasitic capacitances at D and S terminals are all paralleled and driven by our 1 MHz test signal at the V\_s source, whose dc level is stepped across ground to  $V_s$ . Figure 15 shows the results.

We simulate 29.5 pF and 21.4 pF where the data sheet gives 26 pF and 25 pF. Considering the variability in circuit-board layout capacitance, we'll call this close enough.

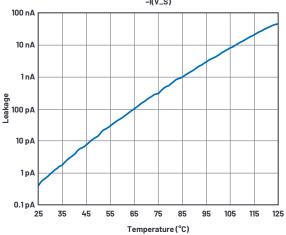

## Leakage Currents

The data sheet curves show voltage-dependent pA-level leakage currents at  $25^{\circ}$ C, but the data sheet specification only guarantees hundreds of pA. I am swayed more by the curves' results at  $25^{\circ}$ C. The small leakage currents apparently were not considered important enough in this device to guarantee at test. To be fair, measuring single pA takes a lot of engineering development effort as well as long test times.

At  $85^{\circ}$ C, the guarantee is a few nA (which can be measured efficiently) with a typical result in the range of a few hundred pA. I'm going to accept these typical results as good.

Leakage current is a product shortcoming; it doesn't have tight statistics and varies wildly with temperature. It is not the kind of specification that we design to—rather, it's a quantity that disrupts the circuits it's connected to. For macromodel use, any leakage of proper magnitude will be simulated as a circuit defect and be a useful warning to the designer. I'll choose a target of 1 nA for an on switch at  $85^{\circ}$ C.

The model we have shows no leakage beyond  $R_{\text{CONVERGENCE}}$  and  $G_{\text{MIN}}$  currents.  $G_{\text{MIN}}$  is a resistor the simulator places across junctions to assist convergence. It is normally 1 × 10<sup>-12</sup> conductance, but in the presence of 30 V supplies we can get multiples of 30 pA currents, way too high for this work.  $G_{\text{MIN}}$  will be reduced to 1 × 10<sup>-15</sup> in the .options line of the simulation and  $R_{\text{CONVERGENCE}}$  raised to 1 × 10<sup>15</sup>.

The physical origin of these leakages is probably mostly from electrostatic discharge (ESD) protection diodes connected to every pin. We will insert them into the simulation setup in Figure 16.

Figure 14. On-capacitance test simulation setup.

Figure 15. On-capacitance vs. dc voltage at  $V_s = 12 \text{ V (left)}$  and 30 V (right) results.

After fiddling with IS in the diode model, we get leakage over temperature in Figure 17.

## Logic Interface and Gate Drivers

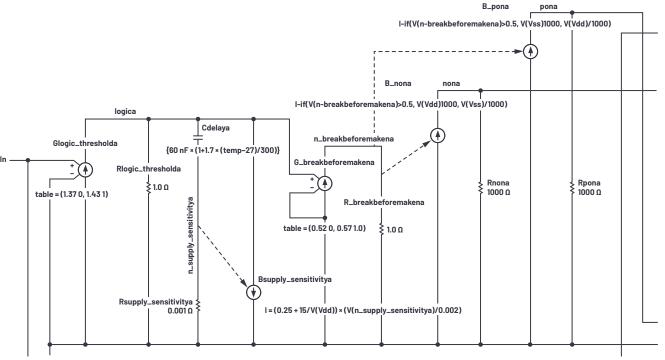

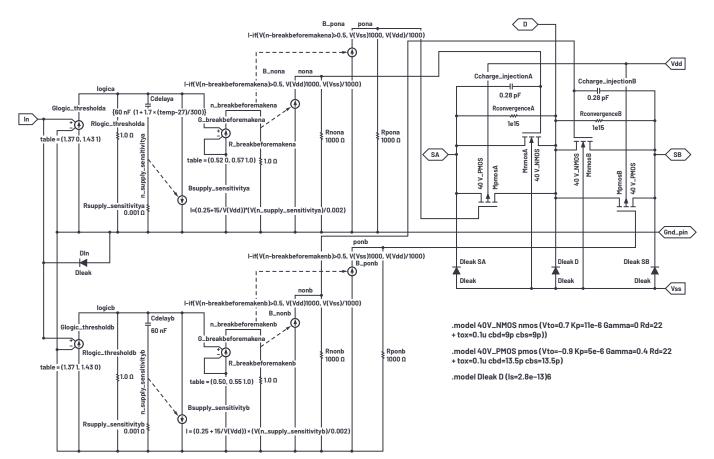

A purely behavioral logic-to-gate drive circuit is shown in Figure 18.

Figure 16. Leakage test simulation setup.

Figure 17. Leakage test over temperature simulation results.

The external logic input is at the In terminal at the left of Figure 18. It is the input of an ideal transconductance Glogic\_thresholda, which has a piecewise-linear transfer function. For logic inputs below 1.37 V, the output at logica node is 0 V; for inputs above 1.43 V logica is at 1 V; and between 1.37 V and 1.43 V in logica moves linearly from 0 V to 1 V. Glogic\_thresholda thus ignores supply variations to provide a 1.4 V input threshold.

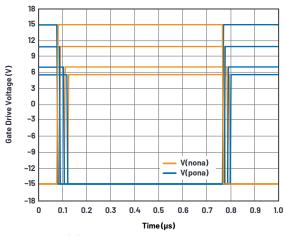

Transiently, Cdelaya slows down the logica node so that we can pick off some time points from it. To make a comparator we again use a transconductance, here Gbreakbeforemakena whose output goes from 0 V to 1 V again but with the threshold skewed a bit above 0.5 V. As seen in Figure 19, the skewed pickoff voltages 0.52 V and 0.57 V rather than 0.5 V allow faster turn-off from exponentials falling from 1 V than the turn-on time for exponentials rising from 0 V.

Full gate drive voltage is produced by the B\_non and B\_pon behavioral current sources. B\_nona sources a current of  $V_{\tiny DD}/1000$  when node n\_breakbeforemakena  $>\!0.5$  V, driving the voltage at node nona to  $V_{\tiny DD}$ , as loaded by a 1000  $\Omega$  resistor. When node n\_breakbeforemakena  $<\!0.5$  V, the node nona is driven to  $V_{\tiny SS}$ . Thus, we have a nice rail-to-rail gate drive that complies with supply voltages and has a fixed 1.4 V input threshold.

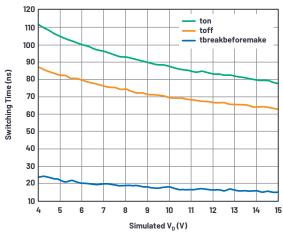

One more characteristic needs explanation. Note that in Figure 20, higher supply voltages reduce the delay times. This is implemented by B\_supplysensitivitya, which feeds back to Cdelaya a fraction of its own dynamic current that varies with  $V_{00}$ . Rsupply\_sensitivitya drops very little voltage due to Cdelaya current, leaving Cdelaya's behavior mostly a pure capacitor. Feeding a replica of Cdelaya's current back to Cdelaya essentially creates a controllable variable capacitor, and the math inside Bsupply\_sensitivitya creates the delay vs.  $V_{00}$  curve in Figure 20.

1.0

0.9

Figure 18. Behavioral logic-to-gate interface.

0.8 0.7 Internal Timing Nodes (V) 0.6 0.5 0.4 0.3 0.2 0.1 V(logica V(logicb) Hysteretic Thresholds -0. 0.3 0.4 0.5 Time (µs)

Figure 19. Break-before-make timing.

Figure 20. Break-before-make timing results from simulation and data sheet curve.

Well, our circuit emulates the  $T_{\text{ON}}$  delay as 111 ns for  $V_{\text{DD}}=4$  V while the data sheet curve says 140 ns; and for  $V_{\text{DD}}=15$  V simulated delay is 77 ns vs. data sheet delay of 60 ns. Not great correlation; I'll leave it to the reader to refine the Bsupply\_sensitivity function to do better. At least the break-before-make varies nicely between 15 ns and 24 ns.

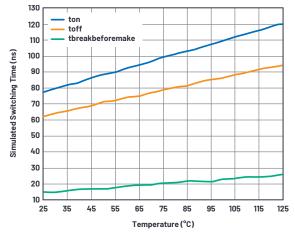

While we don't have much data sheet data on delay vs. temperature, I added a temperature term in Cdelaya to at least model slowdown when hot, seen in Figure 21.

Figure 21. Timing delays vs. temperature.

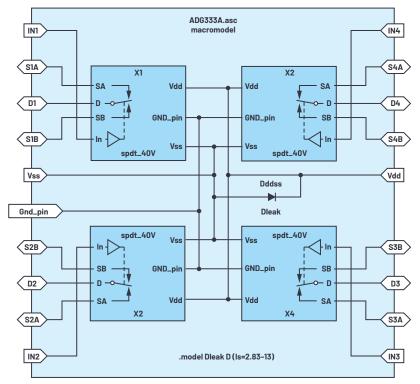

## Assembling the Macromodel

Figure 22 shows the assembled analog switch that will become a subcircuit. Hard L and W numbers were placed into the transistor symbols instead of parameters, and all excitation and I/O are removed in favor of pin connections SA, D, SB, In,  $V_{\text{DD}}$ ,  $V_{\text{SS}}$ , and  $Gnd_{\text{pin}}$ .

A second logic interface is provided for the other switch of the spdt pair. ESD protection diodes are installed between analog terminals and  $\rm V_{SS}$  and between the logic In and ground. Note that the "-a" suffix in names of the upper logic interface devices and nodes are replicated as "-b" suffix in the lower interface. Glogic\_thresholdb interface has the opposite output from the table in Glogic\_thresholda to allow one or the other switch pair to operate rather than be turned on simultaneously.

An alternative ESD protection scheme involves diodes from a protected pin to both  $V_{00}$  and  $V_{ss}$ , and a clamp between  $V_{00}$  and  $V_{ss}$ . The data sheet generally gives insight as to the protection scheme, and leakage currents are assigned to both supplies.

The spdt subcircuit is given a symbol and used four times in the master schematic ADG333A.asc of Figure 23.

Figure 22. Assembled SPDT subcircuit spdt 40V.asc.

Figure 23. ADG333A macromodel circuit schematic.

Figure 24. ADG333A macromodel test bench.

Figure 24 is the test bench schematic for verifying final macromodel results.

## Summary

We've seen how to realize a decent macromodel for a specific analog switch and how to obtain parameters that support a few different semiconductor processes used to realize the physical device. The resulting macromodel displays defects such as on resistance and its variations, charge injection as a function of supply and signal level, parasitic capacitances and their variations over voltage, logic interface delays, and leakages. Hopefully, the macromodels will be helpful in simulating the real performance of analog switches.

### Addendum

To download LTspice, please visit analog.com/Itspice.

Here is the LTspice text file of the macromodel symbol, to be filed under the name ADG333.asy. It contains subcircuit simulation details. Rather than copy the ADG333.asc schematic into every schematic that uses it, we use a symbol that refers to it as the .asy. Within the ADG333 symbol are individual switch symbols. This is the symbol simulation content to be filed as spdt\_40V.asc. The actual symbol is to be filed as spdt\_40V.asy.

### About the Author

Barry Harvey has worked as an analog IC designer, designing high speed op amps, voltage references, mixed-signal circuits, video circuits, DSL line drivers, DACs, sample-and-hold amplifiers, multipliers, and more. He has an M.S.E.E. from Stanford University. He holds more than 20 patents and has published about as many articles and papers. Barry's hobbies include repairing used test equipment, playing guitar, and working on Arduino-related projects. He can be reached at <a href="mailto:barry.harvey@analog.com">barry.harvey@analog.com</a>.

# Open-Source LIDAR Prototyping Platform

István Csomortáni, FPGA Design Engineer, Dragos Bogdan, Software Development Engineer Manager, Cristian Orian, System Design Engineer, and Andrei Cozma, Engineer Manager

### Abstract

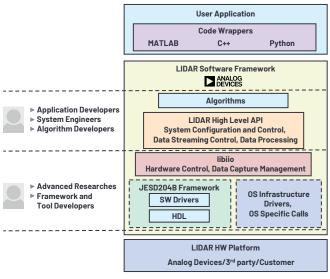

This article discusses Analog Devices' new broad market LIDAR prototyping platform and how it helps shorten the customers' product development time by providing a complete hardware and software solution that customers can use to prototype their algorithms and custom hardware solutions. It goes over the details of the modular hardware design, including the light receive and transmit signal chains, FPGA interface, and optics for long range sensing. The system partitioning decisions that were made are explained, helping highlight the importance of good system design, interface definition, and right level of modularity. The components of the open source LIDAR software stack and the platform specific API are described showing how customers can benefit from these during product development and integrate them in their final solutions.

### Introduction

As autonomous vehicles and robots continue to move from science fiction to reality, automotive and industrial customers are seeking new environment perception solutions to enable these machines to navigate autonomously. LIDAR is one of the fastest growing technologies in this field and is seeing wider adoption as the technology becomes more mature and reliable, opening up a huge market opportunity. As many startups and well renowned sensor companies are working toward developing more precise, less power hungry, smaller form factor, and more cost-effective LIDAR sensors, they all face the same challenges when it comes to system hardware design and implementing the software infrastructure to talk to all the components in the system. These are the exact areas where ADI can bring value through hardware reference designs accompanied by open-source software stacks, enabling customers to easily integrate into their products ICs from the ADI LIDAR portfolio, as well as software modules and HDL IPs, shortening their time to market.

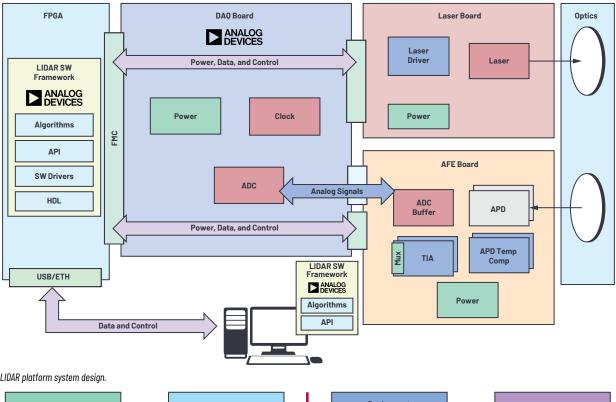

## System Architecture

As customers develop their LIDAR sensors, there are few areas of differentiation in the system design: receive and transmit optics, number and orientation of lasers, laser firing patterns, laser beam steering, and number of light receive elements. But, regardless of these choices, there is a high degree of commonality in the receive signal chain and laser drive signal requirements. Based

on these assumptions, Analog Devices designed a modular LIDAR prototyping platform, AD-FMCLIDAR1-EBZ, intended to allow customers to easily configure or replace parts of the design with their own hardware, designed according to specific applications requirements, but still be able to use the platform as a whole system. The system is partitioned into three different boards with standardized digital and analog interfaces:

- ▶ A data acquisition (DAQ) board containing a high speed JESD204B ADC and corresponding clocking and power. This board has an FMC compliant interface to connect to the users' preferred FPGA development board. It serves as the baseboard in the system by having the other two boards connected to it via digital connectors that route control and feedback signals between these boards and the FPGA and through coaxial cables for analog signals.

- An analog front-end (AFE) board containing the avalanche photodetector (APD) light sensor and the entire signal chain required for conditioning the APD output signal so that it can be fed into the ADC on the DAO board.

- ► A laser board containing the lasers and drive circuit.

As always, in system design, modularity means flexibility, but it also comes with drawbacks such as increased complexity, performance degradation, and increased cost, which must be thoroughly evaluated when deciding on the system partitioning. In this case, the system was broken down into these three boards for the following reasons:

- The ADC and clocking are very likely to stay the same regardless of the implementation of the analog front end and chosen laser solution.

- The analog front-end hardware design and form factor is subject to change depending on the chosen APD, overall system receive sensitivity, and chosen optics.

- ► The laser board design and form factor are also subject to change depending on the chosen illumination solution and optics.

- The system must provide a lot of flexibility in positioning and orienting the receiver and the transmitter so that they are aligned with each other or other targets, which is why flex cables are being used for the digital signals and coaxial cables for the analog signals that go between the boards.

Figure 1. LIDAR platform system design.

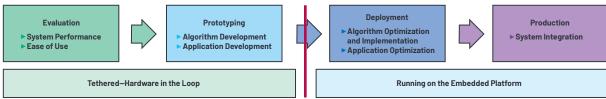

Figure 2. Product development cycle.

The software stack that accompanies the hardware design is based on a hierarchical approach with a few layers dividing it into OS specific drivers and interfaces, a system specific API, and an application layer. This allows the upper layers of the stack to remain unchanged regardless of whether the software is running on an embedded target or a PC talking to the system via the network or a USB connection. This is very valuable in the different product development stages, shown in Figure 2, since it means that the same application software that was developed during the prototyping stages, when the system is tethered to a PC for ease of development, can be easily deployed onto the embedded production system without ever touching the low level interfaces.

## Hardware Design

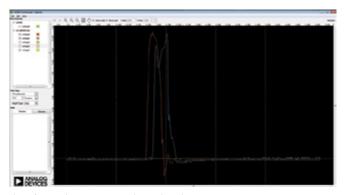

A LIDAR sensor computes the distance to a target by measuring the time it takes for the light pulse to travel to the target and back. The time is measured in increments of the ADC sampling rate since that determines the resolution with which the system samples the received light pulse. Equation 1 shows how the distance is computed relative to the ADC sampling rate.

$$d = N \times \frac{L_S}{2 \times f_S} \tag{1}$$

### Where:

$L_s$  is the speed of light,  $3 \times 10^8$  m/s

$f_s$  is the ADC sampling rate

N is the number of ADC samples since the light pulse is generated until it is received back

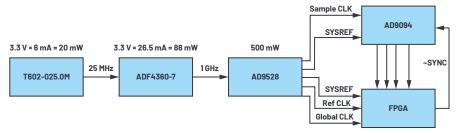

Given the 1 GHz sampling rate of the AD9094 JESD204B guad ADC being used in the system, the results of each sample correspond to a distance of 15 cm. For this reason, it is critical that there aren't any sampling uncertainties in the system since even an uncertainty of a few samples can result in large distance measurement errors. Traditionally, LIDAR systems are based on parallel ADCs that inherently provide zero sampling uncertainty. As the number of receive channels keeps increasing and the power and PCB size requirements become more stringent, these types of ADCs do not scale well. Another option is to use ADCs with high speed serial outputs, such as JESD204B, which solve the issues the parallel ADCs have. This option comes with an increased complexity on the data interface and makes it harder to achieve zero sampling uncertainty.

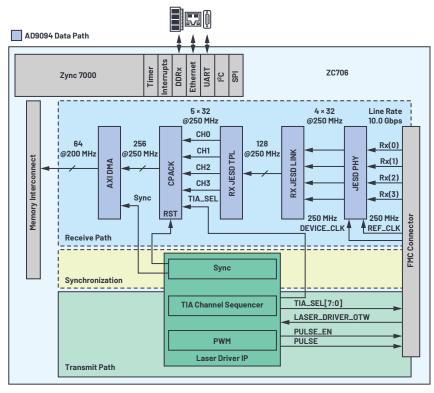

Figure 3. DAQ board clocking and data path.

Figure 4. AFE board signal chain.

The LIDAR DAQ board provides a solution to these challenges by showing how to design the power, clocking, and data interface for a JESD204B data acquisition system operating in Subclass 1 mode, ensuring deterministic latency so that zero sampling uncertainty can be achieved, while taking advantage of all the benefits that the JESD204B interface provides and having the lowest possible power for the clocking scheme. To operate in JESD204B Subclass 1 mode, there is a total of five clocks needed in the system:

- ▶ ADC sampling clock: drives the ADC signal sampling process.

- ADC and FPGA SYSREF: source synchronous, high slew rate timing resolution signals responsible for resetting device clock dividers to ensure deterministic latency.

- ► FPGA global clock (also referenced as core clock or device clock): drives the output of the JESD204B PHY layer and FPGA logic.

- ► FPGA reference clock: generates the PHY layer internal clocks needed by the JESD204B transceivers; needs to be equal to or an integer multiple of the device clock.

All the clocks are generated by one AD9528 JESD204B clock generator, thus ensuring they are all synchronized with each other. Figure 3 shows the clocking scheme and the data interface with the FPGA.

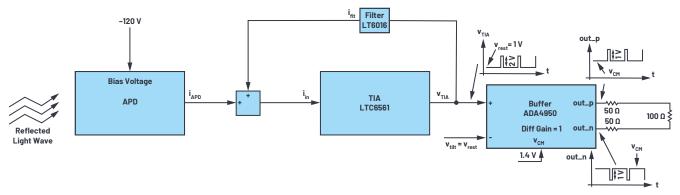

The AFE board receives the optical reflected signal, converts it to an electrical signal, and transfers it to the ADC on the DAQ board. This board is probably the most sensitive part of the entire design since it mixes signal condition circuits working with microampere current signals generated by the 16-channel APD array, converting the optical signal to an electrical signal, with high voltage power supplies in the range of –120 V to –300 V needed to power the same APD. The 16 current outputs are fed into four low noise, 4-channel, transimpedance

amplifier (TIA) LTC6561s with an internal 4-to-1 mux to select the output channel that is afterward fed into one of the four ADC inputs. The input section of the TIAs needs a lot of attention to achieve the desired level of signal integrity and channel isolation so that there is no additional noise added to the very low current signal generated by the APD, thus maximizing the SNR and the object detection rate of the system. The design of the AFE board shows the best practices to achieve the maximum signal quality by keeping the length of the traces between the APD and the TIA as short as possible, adding vias in between the TIA inputs for maximum channel-to-channel isolation, and positioning the signal condition circuits so that they do not interfere with the other power circuits on the board. Another important feature is the ability to measure the temperature of the APD to be able to compensate for APD signal output variations due to temperature changes as the APD's temperature increases during normal operation. A few knobs are provided to control the offsets of the signal chain and the APD bias, which translates into APD sensitivity, to be able to maximize the ADC input range for maximum SNR. Figure 4 shows a block diagram of the AFE board signal chain.

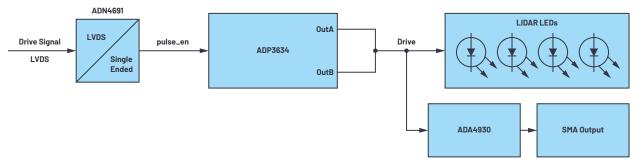

The laser board generates the optical pulses with a wavelength of 905 nm. It uses four lasers that are driven simultaneously for an increase in beam strength, resulting in a longer measurement range. A PWM signal generated by the FPGA carrier board with programmable pulse width and frequency is used to control the lasers. The signal is generated on the FPGA as LVDS to make it less susceptible to noise as it travels from the FPGA to the laser board through the DAQ board and the ribbon cable connecting the DAQ and the laser boards. The drive signal can be fed back to one of the ADC channels for time of flight reference. An external power supply is used to power the lasers. The design complies with International Standards IEC 60825-1:2014 and IEC 60825-1:2007 for a Class 1 laser product.

Figure 5. Laser board signal chain.

Figure 6. HDL design block diagram.

Both the AFE and laser boards require optics for long distance operation. The system was proven to operate at 60 m using fast axis collimators for the laser diodes that narrow the vertical FoV to 1° while keeping the horizontal field of view unchanged, and an aspherical lens for the receive side.

## **HDL** Reference Design

The HDL design constitutes the primary interface to the hardware and implements all the logic to transfer data from the JESD link to the system's memory, drive the lasers, synchronize the receiver and transmitter for accurate time of flight measurement, and implement the communication interfaces to all the components in the hardware design. Figure 6 shows a simplified block diagram of the HDL design. The generic architecture of the ADI's HDL reference designs makes the framework scalable and more accessible to port to another FPGA carrier. The design is using the Analog Devices JESD204B framework² along with several SPI and GPIO interfaces to receive data from the AD9094 ADC and to control all the devices on the prototyping platform.