# **Serial Lite IV Intel® FPGA IP User Guide**

Updated for Quartus® Prime Design Suite: 25.1

IP Version: **5.5.2**

# Contents

| 1. | . About the Serial Lite IV Intel $^{	extstyle 8}$ FPGA IP User Guide | 4  |

|----|----------------------------------------------------------------------|----|

| 2. | Serial Lite IV Intel FPGA IP Overview                                | 6  |

|    | 2.1. Release Information                                             |    |

|    | 2.2. Supported Features                                              |    |

|    | 2.3. IP Version Support Level                                        |    |

|    | 2.4. Device Speed Grade Support                                      |    |

|    | 2.5. Resource Utilization and Latency                                |    |

|    | 2.6. Bandwidth Efficiency                                            |    |

| 3. | Functional Description                                               | 11 |

|    | 3.1. TX Datapath                                                     | 12 |

|    | 3.1.1. TX MAC Adapter                                                |    |

|    | 3.1.2. Control Word (CW) Insertion                                   | 15 |

|    | 3.1.3. TX CRC                                                        | 20 |

|    | 3.1.4. TX MII Encoder                                                | 21 |

|    | 3.1.5. TX PCS and PMA                                                | 22 |

|    | 3.2. RX Datapath                                                     |    |

|    | 3.2.1. RX PCS and PMA                                                | 23 |

|    | 3.2.2. RX MII Decoder                                                | 23 |

|    | 3.2.3. RX CRC                                                        | 24 |

|    | 3.2.4. RX Deskew                                                     |    |

|    | 3.2.5. RX CW Removal                                                 |    |

|    | 3.3. Serial Lite IV Intel FPGA IP Clock Architecture                 |    |

|    | 3.4. Reset and Link Initialization                                   |    |

|    | 3.4.1. TX Reset and Initialization Sequence                          |    |

|    | 3.4.2. RX Reset and Initialization Sequence                          |    |

|    | 3.4.3. PMA Adaptation Flow                                           |    |

|    | 3.5. Link Rate and Bandwidth Efficiency Calculation                  | 36 |

| 4. | Getting Started                                                      |    |

|    | 4.1. Installing and Licensing Intel FPGA IP Cores                    |    |

|    | 4.1.1. Intel FPGA IP Evaluation Mode                                 |    |

|    | 4.2. Specifying the IP Parameters and Options                        | 39 |

|    | 4.3. Generated File Structure                                        |    |

|    | 4.4. Simulating Intel FPGA IP Cores                                  | 42 |

|    | 4.4.1. Simulating and Verifying the Design                           | 43 |

|    | 4.5. Synthesizing IP Cores in Other EDA Tools                        |    |

|    | 4.6. Compiling the Full Design                                       | 44 |

| 5. | Parameters                                                           | 45 |

| 6. | . Serial Lite IV Intel FPGA IP Interface Signals                     | 47 |

|    | 6.1. Clock Signals                                                   |    |

|    | 6.2. Reset Signals                                                   |    |

|    | 6.3. MAC Signals                                                     |    |

|    | 6.4. Transceiver Reconfiguration Signals                             |    |

|    | 6.5. PMA Signals                                                     |    |

## Contents

| 7. Designing with Serial Lite IV Intel FPGA IP                                | 54 |

|-------------------------------------------------------------------------------|----|

| 7.1. Reset Guidelines                                                         | 54 |

| 7.2. Error Handling Guidelines                                                | 54 |

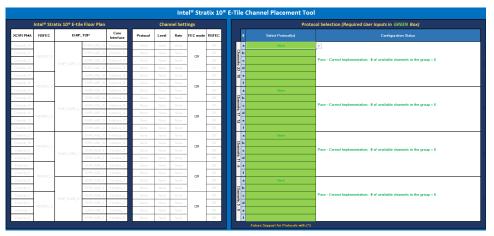

| 7.3. E-Tile Channel Placement Tool                                            |    |

| 8. Serial Lite IV Intel FPGA IP Registers                                     | 57 |

| 9. Serial Lite IV Intel FPGA IP User Guide Archives                           | 58 |

| 10. Document Revision History for the Serial Lite IV Intel FPGA IP User Guide | 59 |

# 1. About the Serial Lite IV Intel® FPGA IP User Guide

This document describes IP features, architecture description, steps to generate, and guidelines to design the Serial Lite IV Intel<sup>®</sup> FPGA IP using the E-tile transceivers in Stratix<sup>®</sup> 10 (TX and MX series) and Agilex<sup> $^{\text{TM}}$ </sup> 7 (F-series) devices.

#### **Intended Audience**

This document is intended for the following users:

- Design architects to make IP selection during the system-level design planning phase

- Hardware designers when integrating the IP into their system-level design

- Validation engineers during the system-level simulation and hardware validation phases

#### **Related Documents**

The following table lists other reference documents that are related to the Serial Lite IV Intel FPGA IP.

#### **Table 1.** Related Documents

| Reference                                                                                     | Description                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Lite IV Stratix 10 FPGA IP Design Example User Guide                                   | This document provides generation, usage guidelines, and functional description of the Serial Lite IV Intel FPGA IP design examples in Stratix 10 devices.       |

| Serial Lite IV Agilex 7 FPGA IP Design Example User Guide                                     | This document provides generation, usage guidelines, and functional description of the Serial Lite IV Intel FPGA IP design examples in Agilex 7 devices.         |

| E-tile Hard IP User Guide: E-tile Hard IP for Ethernet and E-<br>Tile CPRI PHY Intel FPGA IPs | This document describes the features, functionality, and guidelines of the E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs in Stratix 10 devices. |

| Stratix 10 Device Data Sheet                                                                  | This document describes the electrical characteristics, switching characteristics, configuration specifications, and timing for Stratix 10 devices.              |

| Agilex 7 FPGAs and SoCs Device Data Sheet: F-Series and I-Series                              | This document describes the electrical characteristics, switching characteristics, configuration specifications, and timing for Agilex 7 devices.                |

| E-Tile Transceiver PHY User Guide                                                             | This document describes the features, functionality, and guidelines of the E-tile transceiver PHY in Stratix 10 devices.                                         |

<sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Acronyms and Glossary**

## **Table 2.** Acronym List

| Acronym | Expansion                              |

|---------|----------------------------------------|

| CW      | Control Word                           |

| RS-FEC  | Reed-Solomon Forward Error Correction  |

| РМА     | Physical Medium Attachment             |

| тх      | Transmitter                            |

| RX      | Receiver                               |

| PAM4    | Pulse-Amplitude Modulation 4-Level     |

| NRZ     | Non-return-to-zero                     |

| PCS     | Physical Coding Sublayer               |

| MII     | Media Independent Interface            |

| XGMII   | 10 Gigabit Media Independent Interface |

## 2. Serial Lite IV Intel FPGA IP Overview

Serial Lite IV Intel FPGA IP is suitable for high bandwidth data communication for chip-to-chip, board-to-board, and backplane applications.

The Serial Lite IV Intel FPGA IP incorporates a media access control (MAC), physical coding sublayer (PCS), and physical media attachment (PMA) block. The IP supports data transfer up to 56 Gbps per lane with a maximum of eight PAM4 lanes in a single link or 28 Gbps per lane with a maximum of 16 NRZ lanes. This protocol offers high bandwidth, low overhead frames, low I/O count, and supports high scalability in both numbers of lanes and speed. The IP is easily reconfigurable with support of a wide range of data rates with Ethernet PCS mode of the E-tile transceiver. It also supports reference clocks provided from separate clock chips or oscillators with a tolerance of ±100 ppm clock variation between the different clock chips or oscillators.

This IP supports two transmission modes:

- Basic mode—This is a pure streaming mode where data is sent without the startof-packet, empty cycle, and end-of-packet to increase bandwidth. The IP takes the first valid data as the start of a burst.

- Full mode—This is a packet transfer mode. In this mode, the IP sends a burst and a sync cycle at the start and end of a packet as delimiters.

<sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

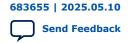

Figure 1. Serial Lite IV High Level Block Diagram

You can generate Serial Lite IV Intel FPGA IP design examples to learn more about the IP features. Refer to Serial Lite IV Stratix 10 FPGA IP Design Example User Guide and Serial Lite IV Agilex 7 FPGA IP Design Example User Guide.

#### **Related Information**

- Functional Description on page 11

- Serial Lite IV Intel Stratix 10 FPGA IP Design Example User Guide

- Serial Lite IV Intel Agilex 7 FPGA IP Design Example User Guide

## 2.1. Release Information

Intel FPGA IP versions match the Quartus<sup>®</sup> Prime Design Suite software versions until v19.1. Starting in Quartus Prime Design Suite software version 19.2, Intel FPGA IP has a new versioning scheme.

The Intel FPGA IP version (X.Y.Z) number can change with each Quartus Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

Table 3. Serial Lite IV Intel FPGA IP Release Information

| Item                  | Description |

|-----------------------|-------------|

| IP Version            | 5.5.2       |

| Quartus Prime Version | 25.1        |

| Release Date          | 2025.04.07  |

| Ordering Code         | IP-SLITE4   |

## 2.2. Supported Features

The following table lists the features available in Serial Lite IV Intel FPGA IP:

Table 4. Serial Lite IV Intel FPGA IP Features

| Feature                      | Description                                                                                                                                                                     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Transfer                | Supports up to 56 Gbps per lane with a maximum of eight PAM4 lanes in a single link.                                                                                            |

|                              | Supports up to 28 Gbps per lane with a maximum of 16 NRZ lanes.                                                                                                                 |

|                              | Supports continuous streaming (Basic) or packet (Full) modes.                                                                                                                   |

|                              | Supports low overhead frame packets.                                                                                                                                            |

|                              | Supports byte granularity transfer for every burst size.                                                                                                                        |

|                              | Supports user-initiated or automatic lane alignment.                                                                                                                            |

|                              | Supports programmable alignment period.                                                                                                                                         |

| PCS                          | Uses hard IP logic that interfaces seamlessly to Stratix 10 and Agilex 7 E-tile transceivers for soft logic resource reduction.  Supports PAM4 modulation mode for 100GBASE-KP4 |

|                              | specification. RS-FEC is always enabled in this modulation mode.                                                                                                                |

|                              | Supports NRZ with optional RS-FEC modulation mode.                                                                                                                              |

|                              | Supports 64b/66b encoding decoding.                                                                                                                                             |

| Error Detection and Handling | <ul> <li>Supports CRC error checking on TX and RX data paths.</li> <li>Supports RX link error checking.</li> <li>Supports RX PCS error detection.</li> </ul>                    |

| Interfaces                   | Supports only full duplex packet transfer with independent links.                                                                                                               |

|                              | Uses point-to-point interconnect to multiple FPGA devices with low transfer latency.                                                                                            |

|                              | Supports user-defined commands.                                                                                                                                                 |

# 2.3. IP Version Support Level

The Quartus Prime software and Intel FPGA device support for the Serial Lite IV Intel FPGA IP is as follows:

Table 5. IP Version and Support Level

| Quartus Prime | Device                         | IP Version | Simulation | Compilation | Hardware Design |

|---------------|--------------------------------|------------|------------|-------------|-----------------|

| 25.1          | Stratix 10 E-tile transceivers | 5.5.2      | √          | √           | <b>✓</b>        |

|               | Agilex 7 E-tile transceivers   | 5.5.2      | √          | √           | √               |

## 2.4. Device Speed Grade Support

The Serial Lite IV Intel FPGA IP supports the following speed grades for Stratix 10 and Agilex 7 E-tile devices:

• Transceiver speed grade: -1, -2, and -3

• Core speed grade: -1, -2, and -3

## 2.5. Resource Utilization and Latency

The resources and latency for the Serial Lite IV Intel FPGA IP were obtained from the Quartus Prime Pro Edition software version 21.1.

#### Table 6. Stratix 10 Serial Lite IV Intel FPGA IP Resource Utilization

The latency measurement is based on the round trip latency from the TX core input to the RX core output.

| Variant      | Number of Data<br>Lanes | Mode  | RS-FEC   | ALM    | Latency (TX core clock cycle) |

|--------------|-------------------------|-------|----------|--------|-------------------------------|

| 28 Gbps NRZ  | 16                      | Basic | Disabled | 16,171 | 80                            |

|              | 16                      | Full  | Disabled | 16,724 | 82                            |

|              | 16                      | Basic | Enabled  | 15,383 | 239                           |

|              | 16                      | Full  | Enabled  | 15,771 | 240                           |

| 56 Gbps PAM4 | 8                       | Basic | Enabled  | 11,197 | 154                           |

|              | 8                       | Full  | Enabled  | 11,591 | 152                           |

## Table 7. Agilex 7 Serial Lite IV Intel FPGA IP Resource Utilization

The latency measurement is based on the round trip latency from the TX core input to the RX core output.

| Variant      | Number of Data<br>Lanes | Mode  | RS-FEC   | ALM    | Latency (TX core clock cycle) |

|--------------|-------------------------|-------|----------|--------|-------------------------------|

| 28 Gbps NRZ  | 16                      | Basic | Disabled | 16,480 | 80                            |

|              | 16                      | Full  | Disabled | 16,896 | 82                            |

|              | 16                      | Basic | Enabled  | 15,173 | 239                           |

|              | 16                      | Full  | Enabled  | 15,534 | 240                           |

| 56 Gbps PAM4 | 8                       | Basic | Enabled  | 11,356 | 154                           |

|              | 8                       | Full  | Enabled  | 11,448 | 152                           |

## 2.6. Bandwidth Efficiency

#### Table 8. Bandwidth Efficiency

| Variables                                    | Settings |         |          |         |          |           |

|----------------------------------------------|----------|---------|----------|---------|----------|-----------|

| XCVR Mode                                    | PAM4     | NRZ     |          | NRZ     |          |           |

| Streaming Mode                               | Full     | Basic   | Full     |         | Basic    |           |

| RS-FEC                                       | Enabled  | Enabled | Disabled | Enabled | Disabled | Enabled   |

| Serial interface bit rate in Gbps (RAW_RATE) | 56.0     | 56.0    | 28.0     | 28.0    | 28.0     | 28.0      |

|                                              |          | '       |          |         |          | continued |

| Variables                                                                    | Settings     |              |                  |                  |             |             |

|------------------------------------------------------------------------------|--------------|--------------|------------------|------------------|-------------|-------------|

| Burst size of a transfer in<br>number of word<br>(BURST_SIZE) <sup>(1)</sup> | 2,048        | 4,194,304    | 2,048            | 2,048            | 4,194,304   | 4,194,304   |

| Alignment period in clock cycle (SRL4_ALIGN_PERIOD)                          | 4,096        | 4,096        | 4,096            | 4,096            | 4,096       | 4,096       |

| 64/66b encode                                                                | 0.96969697   | 0.96969697   | 0.96969697       | 0.96969697       | 0.96969697  | 0.96969697  |

| Overhead of a burst size in number of word (BURST_SIZE_OVHD)                 | 2            | 0            | 2 <sup>(2)</sup> | 2 <sup>(2)</sup> | 0(3)        | 0(3)        |

| Alignment marker period in clock cycle (ALIGN_MARKER_PERIOD)                 | 81,915       | 81,915       | 81,916           | 81,916           | 81,916      | 81,916      |

| Alignment marker width in clock cycle (ALIGN_MARKER_WIDTH)                   | 5            | 5            | 0                | 4                | 0           | 4           |

| Bandwidth efficiency <sup>(4)</sup>                                          | 0.96821788   | 0.96916433   | 0.96827698       | 0.96822967       | 0.96922348  | 0.96917616  |

| Effective rate (Gbps) (5)                                                    | 54.2202012   | 54.27320236  | 27.11175544      | 27.11043076      | 27.13825744 | 27.13693248 |

| Maximum user clock<br>frequency (MHz) <sup>(6)</sup>                         | 423.59532225 | 424.00939437 | 423.62117875     | 423.6004806      | 424.0352725 | 424.01457   |

#### **Related Information**

Link Rate and Bandwidth Efficiency Calculation on page 36

<sup>(6)</sup> Refer to *Link Rate and Bandwidth Efficiency Calculation* for maximum user clock frequency calculation.

<sup>(1)</sup> The BURST\_SIZE for Basic mode approaches infinity, hence a large number is used.

<sup>(2)</sup> In Full mode, the BURST\_SIZE\_OVHD size is inclusive of the START/END paired Control Words in a data stream.

<sup>(3)</sup> For Basic mode, BURST\_SIZE\_OVHD is 0 because there is no START/END during streaming.

<sup>(4)</sup> Refer to Link Rate and Bandwidth Efficiency Calculation for bandwidth efficiency calculation.

<sup>(5)</sup> Refer to Link Rate and Bandwidth Efficiency Calculation for effective rate calculation.

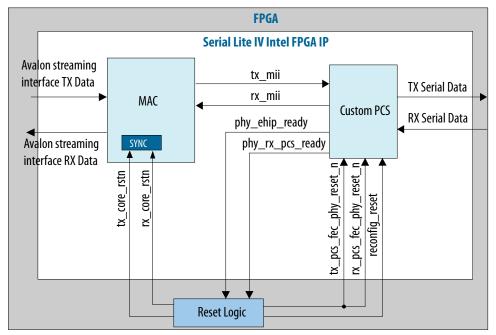

## 3. Functional Description

Serial Lite IV Intel FPGA IP consists of MAC and custom PCS. The MAC communicates with the custom PCS through MII interfaces.

The IP supports two modulation modes:

- PAM4—Provides 2, 4, 6, or 8 number of lanes for selection. A PCS block in PAM4

modulation mode contains four Ethernet channels. The IP always instantiates two

PCS channels for each lane in PAM4 modulation mode.

- NRZ—Provides 1 to 16 number of lanes for selection. In this modulation mode, each PCS block supports up to a maximum of four Ethernet channels.

Each modulation mode supports two data modes:

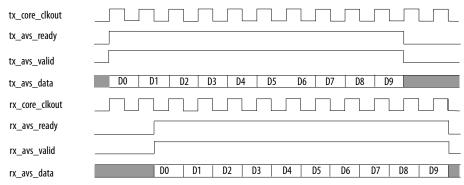

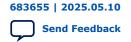

Basic mode—This is a pure streaming mode where data is sent without the startof-packet, empty cycle, and end-of-packet to increase bandwidth. The IP takes the first valid data as the start of a burst.

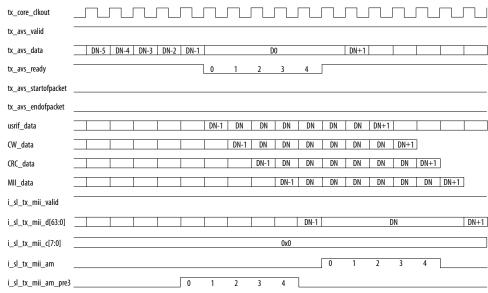

#### Figure 2. Basic Mode Data Transfer

<sup>&</sup>lt;sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

<sup>9001:2015</sup> Registered

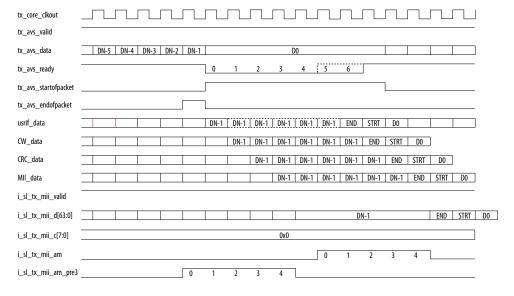

• Full mode—This is the packet mode data transfer. In this mode, the IP sends a burst and a sync cycle at the start and the end of a packet as delimiters.

#### Figure 3. Full Mode Data Transfer

#### **Related Information**

- Serial Lite IV Intel FPGA IP Overview on page 6

- Serial Lite IV Intel Stratix 10 FPGA IP Design Example User Guide

- Serial Lite IV Intel Agilex 7 FPGA IP Design Example User Guide

- E-Tile Transceiver PHY User Guide

- Ethernet Link Inspector User Guide for Intel Stratix 10 Devices

Information about the Ethernet Link Inspector, an inspection tool that can

continuously monitor an Ethernet link.

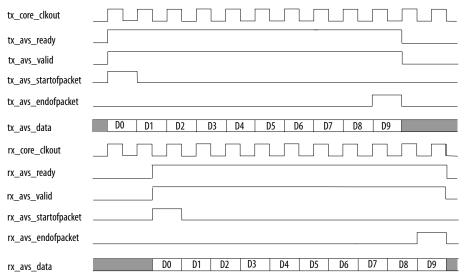

## 3.1. TX Datapath

The TX datapath consists of the following components:

- MAC adapter

- Control word insertion block

- CRC

- MII encoder

- PCS block

- PMA block

Figure 4. TX Datapath

## 3.1.1. TX MAC Adapter

The TX MAC adapter controls the data transmission to the user logic using the Avalon® streaming interface. This block supports user-defined information transmission and flow control.

## **Transferring User-defined Information**

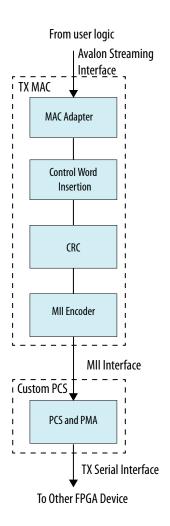

In Full mode, the IP provides the  $tx\_is\_usr\_cmd$  signal that you can use to initiate user-defined information cycle such as XOFF/XON transmission to the user logic. You can initiate the user-defined information transmission cycle by asserting this signal and transfer the information using  $tx\_avs\_data$  along with the assertion of  $tx\_avs\_startofpacket$  and  $tx\_avs\_valid$  signals. The block then deasserts the  $tx\_avs\_ready$  for two cycles.

Note: The user-defined information feature is available only in Full mode.

#### **Flow Control**

There are conditions where the TX MAC is not ready to receive data from the user logic such as during link re-alignment process or when there is no data available for transmission from the user logic. To avoid data loss due to these conditions, the IP uses the tx\_avs\_ready signal to control the data flow from the user logic. The IP deasserts the signal when the following conditions occur:

- When tx\_avs\_startofpacket is asserted, tx\_avs\_ready is deasserted for one clock cycle.

- When tx\_avs\_endofpacket is asserted, tx\_avs\_ready is deasserted for one clock cycle.

- When any paired CWs is asserted tx\_avs\_ready is deasserted for two clock cycles.

- When RS-FEC alignment marker insertion occurs at the custom PCS interface, tx\_avs\_ready is deasserted for four clock cycles.

- Every 17 Ethernet core clock cycles in PAM4 modulation mode and every 33 Ethernet core clock cycles in NRZ modulation mode. The tx\_avs\_ready is deasserted for one clock cycle.

- When user logic deasserts tx\_avs\_valid during no data transmission.

The following timing diagrams are examples of TX MAC adapter using  $tx\_avs\_ready$  for data flow control.

Figure 5. Flow Control with tx\_avs\_valid Deassertion and START/END Paired CWs

# Figure 7. Flow Control with START/END Paired CWs Coincide with Alignment Marker Insertion

## 3.1.2. Control Word (CW) Insertion

The Serial Lite IV Intel FPGA IP constructs CWs based on the input signals from the user logic. The CWs indicate packet delimiters, transmission status information or user data to the PCS block and they are derived from XGMII control codes.

The following table shows the description of the supported CWs:

## **Table 9.** Description of Supported CWs

| cw        | Number of Words (1 word<br>= 64 bits) | In-band | Description                         |

|-----------|---------------------------------------|---------|-------------------------------------|

| START     | 1                                     | Yes     | Start of data delimiter.            |

| END       | 1                                     | Yes     | End of data delimiter.              |

| ALIGN     | 2                                     | Yes     | Control word (CW) for RX alignment. |

| EMPTY_CYC | 2                                     | Yes     | Empty cycle in a data transfer.     |

| IDLE      | 1                                     | No      | IDLE (out of band).                 |

| DATA      | 1                                     | Yes     | Payload.                            |

## **Table 10. CW Field Description**

| Field               | Description                                                                                                                                                                                                |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSVD                | Reserved field. May be used for future extension. Tied to 0.                                                                                                                                               |

| num_valid_bytes_eob | Number of valid bytes in the last word (64-bit). This is a 3-bit value.  • 3'b000: 8 bytes  • 3'b001: 1 byte  • 3'b010: 2 bytes  • 3'b101: 3 bytes  • 3'b100: 4 bytes  • 3'b101: 5 bytes  • 3'b11: 7 bytes |

| EMPTY               | Number of non-valid words at the end of a burst.                                                                                                                                                           |

| еор                 | Indicates the RX Avalon streaming interface to assert an end-of-packet signal.                                                                                                                             |

| sop                 | Indicates the RX Avalon streaming interface to assert a start-of-packet signal.                                                                                                                            |

| seop                | Indicates the RX Avalon streaming interface to assert a start-of-packet and an end-of-packet in the same cycle.                                                                                            |

| align               | Check RX alignment.                                                                                                                                                                                        |

| CRC32               | The values of computed CRC.                                                                                                                                                                                |

| usr                 | Indicates that the control word (CW) contains user-defined information.                                                                                                                                    |

#### 3.1.2.1. Start-of-burst CW

Figure 8. Start-of-burst CW Format

|         |       | START       |                      |   |     |   |   |   |   |

|---------|-------|-------------|----------------------|---|-----|---|---|---|---|

|         | 63:56 |             |                      |   | RSV | D |   |   |   |

|         | 55:48 |             |                      |   | RSV | D |   |   |   |

|         | 47:40 |             | RSVD                 |   |     |   |   |   |   |

| data    | 39:32 | RSVD        |                      |   |     |   |   |   |   |

| uata    | 31:24 |             |                      |   | RSV | D |   |   |   |

|         | 23:16 |             | sop usr align=0 seop |   |     |   |   |   |   |

|         | 15:8  | channel     |                      |   |     |   |   |   |   |

|         | 7:0   | 'hfb(start) |                      |   |     |   |   |   |   |

| control | 7:0   | 0           | 0                    | 0 | 0   | 0 | 0 | 0 | 1 |

In Full mode, you can insert the START CW by asserting the  $tx\_avs\_startofpacket$  signal. When you assert only the  $tx\_avs\_startofpacket$  signal, the sop bit is set. When you assert both the  $tx\_avs\_startofpacket$  and  $tx\_avs\_endofpacket$  signals, the seop bit is set.

Table 11. START CW Field Values

| Field              | Value                                                                                        |

|--------------------|----------------------------------------------------------------------------------------------|

| sop/seop           | 1                                                                                            |

| usr <sup>(7)</sup> | Depending on the tx_is_usr_cmd signal:  1: When tx_is_usr_cmd = 1  0: When tx_is_usr_cmd = 0 |

| align              | 0                                                                                            |

In Basic mode, the MAC sends a START CW after the reset is deasserted. If no data is available, the MAC continuously sends EMPTY\_CYC paired with END and START CWs until you start sending data.

#### 3.1.2.2. End-of-burst CW

Figure 9. End-of-burst CW Format

|         |       | END         |      |      |         |        |             |          |   |

|---------|-------|-------------|------|------|---------|--------|-------------|----------|---|

|         | 63:56 |             | 'hFD |      |         |        |             |          |   |

|         | 55:48 |             |      |      | CRC32[3 | 31:24] |             |          |   |

|         | 47:40 |             |      |      | CRC32[2 | 3:16]  |             |          |   |

| data    | 39:32 | CRC32[15:8] |      |      |         |        |             |          |   |

| uata    | 31:24 |             |      |      | CRC32   | [7:0]  |             |          |   |

|         | 23:16 | eop=1       | RSVD | RSVD | RSVD    |        | RSV         | /D       |   |

|         | 15:8  | RSVD EMPTY  |      |      |         |        |             |          |   |

|         | 7:0   | RSVD        |      |      |         | n      | um_valid_by | /tes_eob |   |

| control | 7:0   | 1           | 0    | 0    | 0       | 0      | 0           | 0        | 0 |

<sup>(7)</sup> This is supported only in Full mode.

The MAC inserts the END CW when the  $tx_avs_endofpacket$  is asserted. The END CW contains the number of valid bytes at the last data word and the CRC information.

The CRC value is a 32-bit CRC result for the data between the START CW and the data word before the END CW.

The following table shows the values of the fields in END CW.

Table 12. END CW Field Values

| Field               | Value                                        |

|---------------------|----------------------------------------------|

| eop                 | 1                                            |

| CRC32               | CRC32 computed value.                        |

| num_valid_bytes_eob | Number of valid bytes at the last data word. |

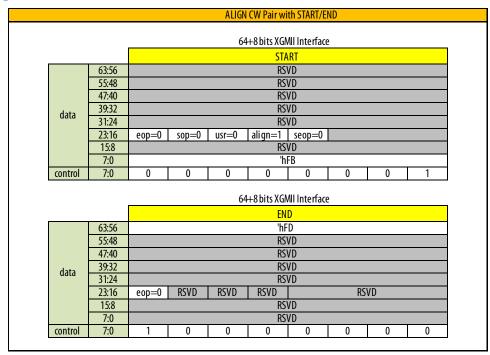

## 3.1.2.3. Alignment Paired CW

Figure 10. Alignment Paired CW Format

The ALIGN CW is a paired CW with START/END or END/START CWs. You can insert the ALIGN paired CW by either asserting the tx\_link\_reinit signal, set the Alignment Period counter, or initiating a reset. When the ALIGN paired CW is inserted, the align field is set to 1 to initiate the receiver alignment block to check data alignment across all lanes.

Table 13. ALIGN CW Field Values

| Field | Value |

|-------|-------|

| align | 1     |

| eop   | 0     |

| sop   | 0     |

| usr   | 0     |

| seop  | 0     |

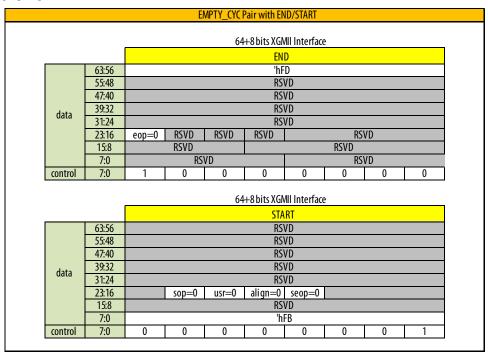

## 3.1.2.4. Empty-cycle CW

Figure 11. Empty-cycle CW Format

When you deassert  $tx_{avs\_valid}$  for two clock cycles during a burst, the MAC inserts an EMPTY\_CYC CW paired with END/START CWs. You can use this CW when there is no data available for transmission momentarily.

When you deassert  $tx_avs_valid$  for one cycle, the IP deasserts  $tx_avs_valid$  for twice the period of  $tx_avs_valid$  deassertion to generate a pair of END/START CWs.

Table 14. EMPTY\_CYC CW Field Values

| Field | Value     |

|-------|-----------|

| align | 0         |

| eop   | 0         |

|       | continued |

| Field | Value |

|-------|-------|

| sop   | 0     |

| usr   | 0     |

| seop  | 0     |

## 3.1.2.5. Idle CW

Figure 12. Idle CW Format

|         |       | IDLE CW |      |   |    |    |   |   |   |

|---------|-------|---------|------|---|----|----|---|---|---|

|         | 63:56 |         |      |   | 'h | 07 |   |   |   |

|         | 55:48 |         |      |   | 'h | 07 |   |   |   |

|         | 47:40 |         | 'h07 |   |    |    |   |   |   |

| data    | 39:32 |         | 'h07 |   |    |    |   |   |   |

| uata    | 31:24 |         | 'h07 |   |    |    |   |   |   |

|         | 23:16 |         | 'h07 |   |    |    |   |   |   |

|         | 15:8  | 'h07    |      |   |    |    |   |   |   |

|         | 7:0   | 'h07    |      |   |    |    |   |   |   |

| control | 7:0   | 1       | 1    | 1 | 1  | 1  | 1 | 1 | 1 |

The MAC insert the IDLE CW when there is no transmission. During this period, the  $tx_avs_valid$  signal is low.

You can use the IDLE CW when a burst transfer has completed or the transmission is in an idle state.

#### 3.1.2.6. Data Word

The data word is the payload of a packet. The XGMII control bits are all set to 0 in data word format.

Figure 13. Data Word Format

64+8 bits XGMII Interface DATA WORD 63:56 user data 7 55:48 user data 6 47:40 user data 5 39:32 user data 4 data 31:24 user data 3 23:16 user data 2 15:8 user data 1 7:0 user data 0 7:0 control 0 0 0

## 3.1.3. TX CRC

You can enable the TX CRC block using the **Enable CRC** parameter in the IP Parameter Editor. This feature is supported in both Basic and Full modes.

The MAC adds the CRC value to the END CW by asserting the  $tx\_avs\_endofpacket$  signal. In the BASIC mode, only the ALIGN CW paired with END CW contains a valid CRC field.

The TX CRC block interfaces with the TX Control Word Insertion and TX MII Encode block. The TX CRC block computes the CRC value for 64-bit value per-cycle data starting from the START CW up to the END CW.

You can assert the  $crc\_error\_inject$  signal to intentionally corrupt data in a specific lane to create CRC errors.

## 3.1.4. TX MII Encoder

The TX MII encoder handles the packet transmission from the MAC to the TX PCS.

In PAM4 mode, a custom PCS always contains four Ethernet channels. Therefore the MII bus data pattern in PAM4 mode is different than the MII bus data pattern in NRZ mode. The following figure shows the data pattern on the 8-bit MII bus in PAM4 modulation mode. The START and END CW appear once in every four MII lanes.

Figure 14. PAM4 Modulation Mode MII Data Pattern

| CYCLE 1    | CYCLE 2 | CYCLE 3 | CYCLE 4 | CYCLE 5 |

|------------|---------|---------|---------|---------|

| SOP_CW     | DATA_1  | DATA_9  | DATA_17 | EOP_CW  |

| DATA_DUMMY | DATA_2  | DATA_10 | DATA_18 | IDLE    |

| DATA_DUMMY | DATA_3  | DATA_11 | DATA_19 | IDLE    |

| DATA_DUMMY | DATA_4  | DATA_12 | DATA_20 | IDLE    |

| SOP_CW     | DATA_5  | DATA_13 | DATA_21 | EOP_CW  |

| DATA_DUMMY | DATA_6  | DATA_14 | DATA_22 | IDLE    |

| DATA_DUMMY | DATA_7  | DATA_15 | DATA_23 | IDLE    |

| DATA_DUMMY | DATA_8  | DATA_16 | DATA_24 | IDLE    |

The following figure shows the data pattern on the 8-bit MII bus in NRZ modulation mode. The START and END CW appear in every MII lanes.

Figure 15. NRZ Modulation Mode MII Data Pattern

| CYCLE 1 | CYCLE 2 | CYCLE 3 | CYCLE 4 | CYCLE 5 |

|---------|---------|---------|---------|---------|

| SOP_CW  | DATA_1  | DATA_9  | DATA_17 | EOP_CW  |

| SOP_CW  | DATA_2  | DATA_10 | DATA_18 | EOP_CW  |

| SOP_CW  | DATA_3  | DATA_11 | DATA_19 | EOP_CW  |

| SOP_CW  | DATA_4  | DATA_12 | DATA_20 | EOP_CW  |

| SOP_CW  | DATA_5  | DATA_13 | DATA_21 | EOP_CW  |

| SOP_CW  | DATA_6  | DATA_14 | DATA_22 | EOP_CW  |

| SOP_CW  | DATA_7  | DATA_15 | DATA_23 | EOP_CW  |

| SOP_CW  | DATA_8  | DATA_16 | DATA_24 | EOP_CW  |

## 3.1.5. TX PCS and PMA

The Serial Lite IV Intel FPGA IP uses the custom PCS variant in the E-tile Hard IP for Ethernet Intel FPGA IP.

For more information about the custom PCS variant from the E-tile Hard IP for Ethernet Intel FPGA IP, refer to E-tile Hard IP User Guide: E-tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs.

## **Related Information**

About the E-tile Hard IP for Ethernet Intel FPGA IP Core

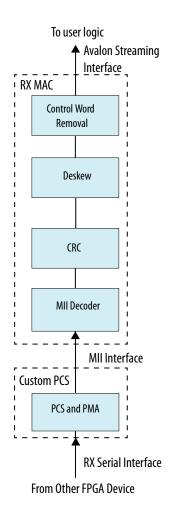

## 3.2. RX Datapath

The RX datapath consists of the following components:

- PMA block

- PCS block

- MII decoder

- CRC

- Deskew block

- Control Word removal block

Figure 16. RX Datapath

## 3.2.1. RX PCS and PMA

The Serial Lite IV Intel FPGA IP uses the custom PCS variant in the E-tile Hard IP for Ethernet Intel FPGA IP.

For more information about the custom PCS variant from the E-tile Hard IP for Ethernet Intel FPGA IP, refer to the *E-tile Hard IP User Guide: E-tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs.*

#### **Related Information**

About the E-tile Hard IP for Ethernet Intel FPGA IP Core

## 3.2.2. RX MII Decoder

This block identifies if incoming data contains control word and alignment markers.

The RX MII decoder outputs data in the form of 1-bit valid, 1-bit marker indicator, 1-bit control indicator, and 64-bit data per lane.

#### 3.2.3. RX CRC

You can enable the TX CRC block using the **Enable CRC** parameter in the IP Parameter Editor. This feature is supported in both Basic and Full modes.

The RX CRC block interfaces with the RX Control Word Removal and RX MII Decoder blocks. The IP asserts rx crc error signal when a CRC error occurs.

The IP deasserts the  $rx\_crc\_error$  at every new burst. It is an output to the user logic for user logic error handling.

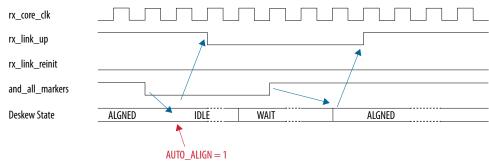

## 3.2.4. RX Deskew

The RX deskew block detects the alignment markers for each lane and re-aligns the data before sending it to the RX CW removal block.

You can choose to let the IP core to align the data for each lane automatically when an alignment error occurs by setting the **Enable Auto Alignment** parameter in the IP parameter Editor. If you disable the automatic alignment feature, the IP core asserts the  $rx\_error$  signal to indicate alignment error. You must assert the  $rx\_link\_reinit$  to initiate the lane alignment process when a lane alignment error occurs.

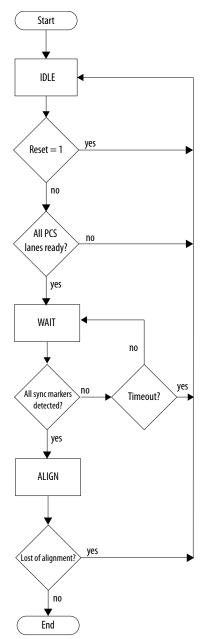

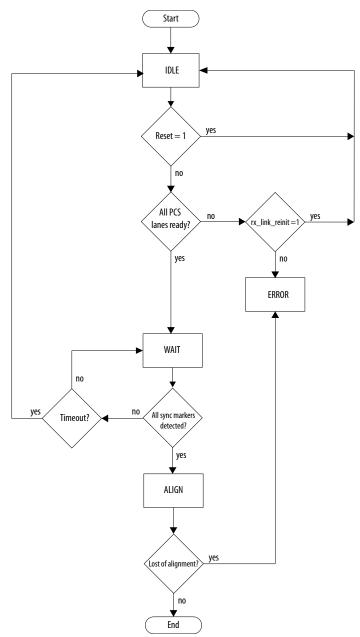

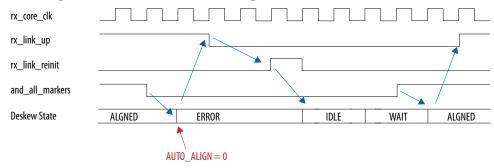

The RX deskew detects the alignment markers based on a state machine. The following diagram shows the states in the RX deskew block.

Figure 17. RX Deskew Lane Alignment State Machine with Auto Alignment Enabled Flow Chart

Figure 18. RX Deskew Lane Alignment State Machine with Auto Alignment Disabled Flow Chart

- 1. The alignment process starts with the IDLE state. The block moves to WAIT state when all PCS lanes are ready and rx\_link\_reinit is deasserted.

- 2. In WAIT state, the block checks all detected markers are asserted within the same cycle. If this condition is true, the block moves to the ALIGNED state.

- 3. When the block is in the ALIGNED state, it indicates the lanes are aligned. In this state, the block continues to monitor lane alignment and check if all markers are present within the same cycle. If at least one marker is not present in the same cycle and the **Enable Auto Alignment** parameter is set, the block goes to the

IDLE state to re-initialize the alignment process. If **Enable Auto Alignment** is not set and at least one marker is not present in the same cycle, the block goes to ERROR state and waits for the user logic to assert  $rx_link_reinit$  signal to initiate lane alignment process.

Figure 19. Lane Realignment with Enable Auto Alignment Enabled

Figure 20. Lane Realignment with Enable Auto Alignment Disabled

#### 3.2.5. RX CW Removal

This block decodes the CWs and sends data to the user logic using the Avalon streaming interface after the removal of the CWs.

When there is no valid data available, the RX CW removal block deasserts the  $rx\_avs\_valid$  signal.

In FULL mode, if the user bit is set, this block asserts the  $rx_is_usr_cmd$  signal and the data in the first clock cycle is used as user-defined information or command.

When  $rx_{avs\_ready}$  deasserts and  $rx_{avs\_valid}$  asserts, the RX CW removal block generates an error condition to the user logic.

The Avalon streaming signals related to this block are as follow:

- rx\_avs\_startofpacket

- rx\_avs\_endofpacket

- rx\_avs\_channel

- rx\_avs\_empty

- rx\_avs\_data

- rx\_avs\_valid

- rx\_num\_valid\_bytes\_eob

- rx\_is\_usr\_cmd (only available in Full mode)

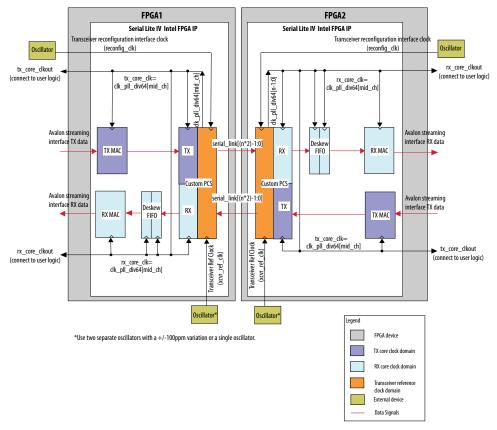

## 3.3. Serial Lite IV Intel FPGA IP Clock Architecture

The Serial Lite IV Intel FPGA IP has four clock inputs which generate clocks to different blocks:

- Transceiver reference clock (xcvr\_ref\_clk)—Input clock from external clock chips or oscillators which generates clocks for TX MAC, RX MAC, and TX and RX custom PCS blocks. The IP supports reference clocks provided from separate clock chips or oscillators with a tolerance of ±100 ppm clock variation between the different clock chips or oscillators. Refer to Parameters for supported frequency range.

- TX core clock (tx\_core\_clk)—This clock is derived from transceiver PLL (clk\_pll\_div64[mid\_ch]) in the custom PCS and is used for TX custom PCS interface and TX MAC. This clock is also an output clock from the IP to connect to the TX user logic.

- RX core clock (rx\_core\_clk)—This clock is derived from the transceiver PLL (clk\_pll\_div64[mid\_ch]) in the custom PCS and is used for RX custom PCS interface, RX deskew FIFO, and RX MAC. This clock is also an output clock from the IP to connect to the RX user logic.

- Clock for transceiver reconfiguration interface (reconfig\_clk)—input clock from external clock circuits or oscillators which generates clocks for custom PCS and RS-FEC reconfiguration interface in both TX and RX datapaths. The clock frequency is 100 to 162 MHz. For more about custom PCS and RS-FEC reconfiguration interface, refer to E-tile Hard IP User Guide: E-tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs.

The following block diagram shows Serial Lite IV Intel FPGA IP clock domains and the connections within the IP.

Figure 21. Serial Lite IV Intel FPGA IP Clock Architecture

#### **Related Information**

- E-Tile Transceiver PHY User Guide: Ports and Parameters

- E-tile Hard IP User Guide: E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs

More information about Ethernet reconfiguration interfaces.

• Parameters on page 45

## 3.4. Reset and Link Initialization

The MAC, custom PCS, and reconfiguration blocks have different reset signals:

- TX and RX MAC blocks use tx\_core\_rst\_n and rx\_core\_rst\_n reset signals.

- TX and RX RS-FEC blocks use tx\_pcs\_fec\_phy\_reset\_n and rx\_pcs\_fec\_phy\_reset\_n reset signals.

- Reconfiguration block uses the reconfig\_reset reset signal.

Figure 22. Reset Architecture

#### **Related Information**

- Reset Guidelines on page 54

- Serial Lite IV Intel Stratix 10 FPGA IP Design Example User Guide: Serial Lite IV IP Toolkit

- Serial Lite IV Intel Agilex 7 FPGA IP Design Example User Guide

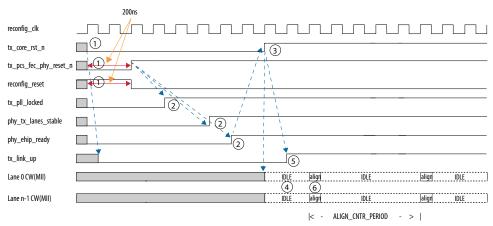

## 3.4.1. TX Reset and Initialization Sequence

The TX reset sequence for Serial Lite IV Intel FPGA IP is as follows:

- Assert tx\_pcs\_fec\_phy\_reset\_n, tx\_core\_rst\_n, and reconfig\_reset simultaneously to reset the custom PCS, MAC, and reconfiguration blocks. Release the custom PCS (tx\_pcs\_fec\_phy\_reset\_n) and reconfiguration reset (reconfig\_reset) after 200 ns to ensure the blocks are properly reset.

- 2. The IP then asserts the phy\_tx\_lanes\_stable, tx\_pll\_locked, and phy\_ehip\_ready signals after the custom PCS reset is released, to indicate the TX PHY is ready for transmission.

- 3. The tx\_core\_rst\_n signal deasserts after phy\_ehip\_ready signal goes high.

- 4. The IP starts transmitting IDLE characters on the MII interface once the MAC is out of reset. There is no requirement for TX lane alignment and skewing because all lanes use the same clock.

- 5. While transmitting IDLE characters, the MAC asserts the tx\_link\_up signal.

- 6. The MAC then starts transmitting ALIGN paired with START/END or END/START CWs at a fixed interval to initiate the lane alignment process of the connected receiver.

Figure 23. TX Reset and Initialization Timing Diagram

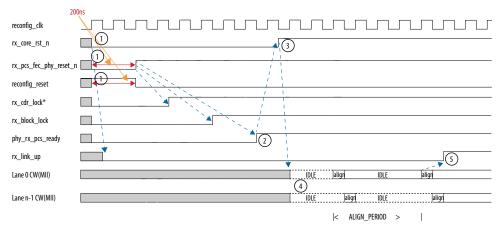

## 3.4.2. RX Reset and Initialization Sequence

The RX reset sequence for Serial Lite IV Intel FPGA IP is as follows:

- 1. Assert rx\_pcs\_fec\_phy\_reset\_n, rx\_core\_rst\_n, and reconfig\_reset simultaneously to reset the custom PCS, MAC, and reconfiguration blocks. Release the custom PCS (rx\_pcs\_fec\_phy\_reset\_n) and reconfiguration reset (reconfig\_reset) after 200 ns to ensure the blocks are properly reset.

- 2. The IP then asserts the phy\_rx\_pcs\_ready signal after the custom PCS reset is released, to indicate RX PHY is ready for transmission.

- 3. The rx\_core\_rst\_n signal deasserts after phy\_rx\_pcs\_ready signal goes high.

- 4. The IP starts the lane alignment process after the RX MAC reset is released and upon receiving ALIGN paired with START/END or END/START CWs.

- 5. The RX deskew block asserts the rx\_link\_up signal once alignment for all lanes has complete.

- 6. The IP then asserts the  $rx_link_up$  signal to the user logic to indicate that the RX link is ready to start data reception.

Figure 24. RX Reset and Initialization Timing Diagram

This timing diagram is only valid for the power-up initialization sequence.

For RX Reset after power-up, the rx\_cdr\_lock signal will remain asserted while the other signals perform as illutrated in the diagram.

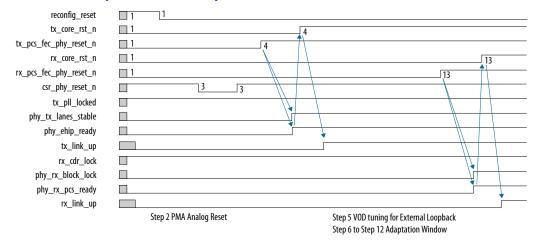

## 3.4.3. PMA Adaptation Flow

The PMA block in the Serial Lite IV Intel FPGA IP uses the same PMA adaptation flow as the E-Tile Hard IP for Ethernet Intel FPGA IP. Refer to the *Ethernet Adaptation Flow with Non-external AIB Clocking* section in *E-tile Hard IP User Guide: E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs* to trigger the PMA adaptation flow for the Serial Lite IV Intel FPGA IP.

Table 15. Signal Mapping Between Serial Lite IV Intel FPGA IP and E-Tile Hard IP for Ethernet Intel FPGA IP

| Signal Name<br>(Serial Lite IV Intel FPGA IP) | Equivalent Signal Name (E-Tile Hard IP for Ethernet Intel FPGA IP) |                   |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------|-------------------|--|--|--|

|                                               | NRZ Mode (10GE/25GE)                                               | PAM4 Mode (100GE) |  |  |  |

| tx_pcs_fec_phy_reset_n                        | i_sl_tx_rst_n                                                      | i_tx_rst_n        |  |  |  |

| rx_pcs_fec_phy_reset_n                        | i_sl_rx_rst_n                                                      | i_rx_rst_n        |  |  |  |

| reconfig_reset                                | i_reconfig_reset                                                   | i_reconfig_reset  |  |  |  |

#### **Related Information**

E-tile Hard IP User Guide: E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel FPGA IPs

More information about PMA adaptation flow.

## 3.4.3.1. Starting the PMA Adaptation Flow

For E-tile Serial Lite IV Intel FPGA IP core variations, perform the following steps to start the PMA adaptation:

- Assert the TX, RX Digital Resets (tx\_pcs\_fec\_phy\_reset\_n, rx\_pcs\_fec\_phy\_reset\_n, tx\_core\_rst\_n, rx\_core\_rst\_n) and reconfiguration reset (reconfig\_reset) signals. Release the reconfiguration reset (reconfig\_reset) signal.

- 2. Trigger the PMA analog reset and re-load the initial PMA settings.

- a. Write 0x200[7:0] = 0x00.

- b. Write 0x201[7:0] = 0x00.

- c. Write 0x202[7:0] = 0x00.

- d. Write 0x203[7:0] = 0x81.

- e. Read 0x207 until it becomes 0x80. This indicates that the operation completed successfully.

- f. Write 0x91[0] = 1 to load the initial settings in the programming file.

- 3. Apply the control status registers (CSR) Reset (csr\_phy\_reset\_n) signal and de-assert the CSR Reset (csr\_phy\_reset\_n) signal.

- 4. De-assert the TX Digital reset (tx\_pcs\_fec\_phy\_reset\_n) and (tx\_core\_rst\_n) signals.

- 5. Configure the Attenuation Value (VOD) (skip this step if using internal serial loopback).

- a. Write 0x84[7:0] = 0x01.

- b. Write 0x85[7:0] = 0x40.

- c. Write 0x86[7:0] = 0x15.

- d. Write 0x87[7:0] = 0x00.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B [0] until it changes to 0.

- h. Write 0x8A[7] to 1 to clear the 0x8A[7] flag.

- 6. Set the operation mode, enable Internal Serial Loopback Mode via PMA attribute code. Attribute = 0x8, data = 0x101.

- a. Write 0x84[7:0] = 0x01.

- b. Write 0x85[7:0] = 0x01.

- c. Write 0x86[7:0] = 0x08.

- d. Write 0x87[7:0] = 0x00.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- 7. Perform Initial Adaptation in Serial Loopback Mode. Attribute = 0xA, data = 0x1.

- a. Write 0x84[7:0] = 0x01.

- b. Write 0x85[7:0] = 0x00.

- c. Write 0x86[7:0] = 0x0A.

- d. Write 0x87[7:0] = 0x00.

- e. Write  $0 \times 90[0] = 1'b1$ .

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- 8. Verify that the initial adaptation status is complete using interrupt code. Attribute = 0x0126, data = 0x0B00.

- a. Write 0x84[7:0] = 0x00.

- b. Write 0x85[7:0] = 0x0B.

- c. Write 0x86[7:0] = 0x26.

- d. Write 0x87[7:0] = 0x01.

- e. Write  $0 \times 90[0] = 1'b1$ .

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- i. Read register 0x88. Repeat Step 8 until 0x88[0] = 0, to confirm that adaptation is no longer in process.

- 9. Enable mission mode and disable internal serial loopback (skip this step if using internal serial loopback). Attribute = 0x8, data = 0x100.

- a. Write 0x84[7:0] = 0x00.

- b. Write 0x85[7:0] = 0x01.

- c. Write 0x86[7:0] = 0x08.

- d. Write 0x87[7:0] = 0x00.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- 10. Run initial adaptation via PMA attribute code (skip this step if using internal serial loopback). Attribute = 0xA, data = 0x1.

- a. Write 0x84[7:0] = 0x01.

- b. Write 0x85[7:0] = 0x00.

- c. Write 0x86[7:0] = 0x0A.

- d. Write 0x87[7:0] = 0x00.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- 11. Verify that the initial adaptation status is complete using interrupt code (skip this step if using internal serial loopback). Attribute = 0x0126, data = 0x0B00.

- a. Write 0x84[7:0] = 0x00.

- b. Write 0x85[7:0] = 0x0B.

- c. Write 0x86[7:0] = 0x26.

- d. Write 0x87[7:0] = 0x01.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- i. Read register 0x88. Repeat Step 11 until 0x88[0] = 0, to confirm that adaptation is no longer in process.

- 12. Perform Continuous adaptation via PMA attribute code (skip this step if using internal serial loopback). Attribute = 0xA, data = 0x6.

- a. Write 0x84[7:0] = 0x06.

- b. Write 0x85[7:0] = 0x00.

- c. Write 0x86[7:0] = 0x0A.

- d. Write 0x87[7:0] = 0x00.

- e. Write 0x90[0] = 1'b1.

- f. Read 0x8A[7]. It should be 1.

- g. Read 0x8B[0] until it changes to 0.

- h. Write 0x8A[7] to 1'b1 to clear the 0x8A[7] value.

- 13. De-assert RX Digital reset (rx\_pcs\_fec\_phy\_reset\_n) and (rx\_core\_rst\_n) signals.

- 14. Verify that the link status signals (tx\_link\_up) and (rx\_link\_up) transitions high. If the link status signals are not high, repeat all the steps above.

- 15. Send packets.

Figure 25. Reset and Adaptation Flow Sequence

## 3.5. Link Rate and Bandwidth Efficiency Calculation

The Serial Lite IV Intel FPGA IP bandwidth efficiency calculation is as below:

Bandwidth efficiency = 64/66 \* (burst\_size - burst\_size\_ovhd)/burst\_size \* [align\_marker\_period / (align\_marker\_period + align\_marker\_width)] \* [(srl4\_align\_period - 2) / srl4\_align\_period]

**Table 16.** Bandwidth Efficiency Variables Description

| Variable            | Description                                                                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| raw_rate            | This is the bit rate achieved by the serial interface. raw_rate = SERDES width * transceiver clock frequency Example: raw_rate = 64 * 402.812500 Gbps = 25.78 Gbps                                              |

| burst_size          | Value of burst size. To calculate average bandwidth efficiency, use common burst size value. For maximum rate, use maximum burst size value.                                                                    |

| burst_size_ovhd     | The burst size overhead value.  In Full mode, the burst_size_ovhd value is referring to the START and END paired CWs.  In Basic mode, there is no burst_size_ovhd because there is no START and END paired CWs. |

| align_marker_period | The value of the period where an alignment marker is inserted.  The value is 81920 clock cycle for compilation and 1280 for fast simulation. This value is obtained from the PCS hard logic.                    |

| align_marker_width  | The number of clock cycles where a valid alignment marker signal is held high.                                                                                                                                  |

| srl4_align_period   | The number of clock cycles between two alignment markers. You can set this value using the <b>Alignment Period</b> parameter in the IP Parameter Editor.                                                        |

The link rate calculations are as below:

Effective rate = bandwidth efficiency \* raw\_rate

You can get the maximum user clock frequency with the following equation. The maximum user clock frequency calculation assumes continuous data streaming and no IDLE cycle occurs at the user logic. This rate is important when designing the user logic FIFO to avoid FIFO overflow.

Maximum user clock frequency = effective rate / 64

# 4. Getting Started

### 4.1. Installing and Licensing Intel FPGA IP Cores

The Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

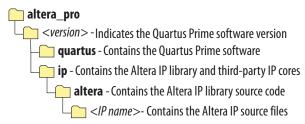

The Quartus Prime software installs IP cores in the following locations by default:

### Figure 26. IP Core Installation Path

**Table 17. IP Core Installation Locations**

| Location                                                               | Software                  | Platform |

|------------------------------------------------------------------------|---------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Quartus Prime Pro Edition | Windows* |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Quartus Prime Pro Edition | Linux*   |

*Note:* The Quartus Prime software does not support spaces in the installation path.

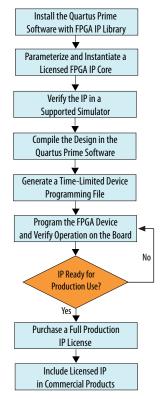

### 4.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP in your system.

- Verify the functionality, size, and speed of the IP quickly and easily.

- Generate time-limited device programming files for designs that include IPs.

- Program a device with your IP and verify your design in hardware.

<sup>&</sup>lt;sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

<sup>9001:2015</sup> Registered

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial JTAG cable connected between the JTAG port on your board and the host computer, which is running the Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Quartus Prime software, and requires no Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IPs in the design support tethered mode, the evaluation time runs until any IP evaluation expires. If all of the IPs support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP reverts to untethered mode if the device disconnects from the host computer running the Quartus Prime software. The IP also reverts to untethered mode if any other licensed IP in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IPs that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP for production, purchase a full production license for the IP.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (roject name> time limited.sof) that expires at the time limit.

Figure 27. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP's user guide for parameterization steps and implementation details.

Altera licenses IPs on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IPs that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Altera Software License Agreements govern the installation and use of licensed IPs, the Quartus Prime design software, and all unlicensed IPs.

#### **Related Information**

- FPGA Licensing Support Center

- Introduction to Altera Software Installation and Licensing

# 4.2. Specifying the IP Parameters and Options

The IP parameter editor allows you to quickly configure your custom IP variation. Use the following steps to specify IP options and parameters in the Quartus Prime Pro Edition software.

- 1. If you do not already have an Quartus Prime Pro Edition project in which to integrate your Serial Lite IV Intel FPGA IP, you must create one.

- a. In the Quartus Prime Pro Edition, click **File** ➤ **New Project Wizard** to create a new Quartus Prime project, or **File** ➤ **Open Project** to open an existing Quartus Prime project. The wizard prompts you to specify a device.

- b. Specify the device family **Stratix 10** or **Agilex 7** and select a production E-tile device that meets the speed grade requirements for the IP.

- c. Click Finish.

- 2. In the IP Catalog, locate and select **Serial Lite IV**. The **New IP Variation** window appears.

- 3. Specify a top-level name for your new custom IP variation. The parameter editor saves the IP variation settings in a file named <your\_ip>.ip.

- 4. Click **OK**. The parameter editor appears.

- 5. Specify the parameters for your IP variation. Refer to Parameters on page 45 for information about Serial Lite IV Intel FPGA IP parameters.

- 6. Optionally, to generate a simulation testbench or compilation and hardware design example, follow the instructions in the *Design Example User Guide*.

- 7. Click **Generate HDL**. The **Generation** dialog box appears.

- 8. Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- 9. Click **Finish**. The parameter editor adds the top-level .ip file to the current project automatically. If you are prompted to manually add the .ip file to the project, click **Project** > **Add/Remove Files in Project** to add the file.

- 10. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports and set any appropriate per-instance RTL parameters.

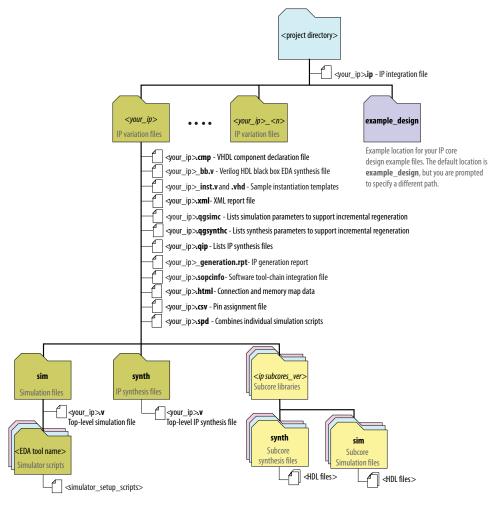

### 4.3. Generated File Structure

The Quartus Prime Pro Edition software generates the following IP core output file structure.

For information about the file structure of the design example, refer to the Serial Lite IV Stratix 10 FPGA IP Design Example User Guide and Serial Lite IV Agilex 7 FPGA IP Design Example User Guide.

Figure 28. Serial Lite IV IP Core Generated Files

Table 18. Serial Lite IV IP Core Generated Files

| File Name                                     | Description                                                                                                                                                                    |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><your_ip>.ip</your_ip></pre>             | The Platform Designer system or top-level IP variation file. <your_ip> is the name that you give your IP variation.</your_ip>                                                  |

| <pre><your_ip>.cmp</your_ip></pre>            | The VHDL Component Declaration (.cmp) file is a text file that contains local generic and port definitions that you can use in VHDL design files.                              |

| <pre><your_ip>.html</your_ip></pre>           | A report that contains connection information, a memory map showing the address of each slave with respect to each master to which it is connected, and parameter assignments. |

| <pre><your_ip>_generation.rpt</your_ip></pre> | IP or Platform Designer generation log file. A summary of the messages during IP generation.                                                                                   |

| <pre><your_ip>.qgsimc</your_ip></pre>         | Lists simulation parameters to support incremental regeneration.                                                                                                               |

| <pre><your_ip>.qgsynthc</your_ip></pre>       | Lists synthesis parameters to support incremental regeneration.                                                                                                                |

| <pre><your_ip>.qip</your_ip></pre>            | Contains all the required information about the IP component to integrate and compile the IP component in the Quartus Prime software.                                          |

|                                               | continued                                                                                                                                                                      |

| File Name                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><your_ip>.sopcinfo</your_ip></pre>                     | Describes the connections and IP component parameterizations in your Platform Designer system. You can parse its contents to get requirements when you develop software drivers for IP components.                                                                                                                                                                                                                                                                  |

|                                                             | Downstream tools such as the Nios® II tool chain use this file. The .sopcinfo file and the system.h file generated for the Nios II tool chain include address map information for each slave relative to each master that accesses the slave. Different masters may have a different address map to access a particular slave component.                                                                                                                            |

| <pre><your_ip>.csv</your_ip></pre>                          | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre><your_ip>.spd</your_ip></pre>                          | Required input file for ip-make-simscript to generate simulation scripts for supported simulators. The .spd file contains a list of files generated for simulation, along with information about memories that you can initialize.                                                                                                                                                                                                                                  |

| <pre><your_ip>_bb.v</your_ip></pre>                         | You can use the Verilog black-box (_bb.v) file as an empty module declaration for use as a black box.                                                                                                                                                                                                                                                                                                                                                               |

| <pre><your_ip>_inst.v or _inst.vhd</your_ip></pre>          | HDL example instantiation template. You can copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                                                                                                                                                                                                                                            |

| <pre><your_ip>.regmap</your_ip></pre>                       | If IP contains register information, .regmap file generates. The .regmap file describes the register map information of master and slave interfaces. This file complements the .sopcinfo file by providing more detailed register information about the system. This enables register display views and user customizable statistics in the System Console.                                                                                                         |

| <pre><your_ip>.svd</your_ip></pre>                          | Allows hard processor system (HPS) System Debug tools to view the register maps of peripherals connected to HPS in a Platform Designer system.  During synthesis, the .svd files for slave interfaces visible to System Console masters are stored in the .sof file in the debug section. System Console reads this section, which Platform Designer can query for register map information. For system slaves, Platform Designer can access the registers by name. |

| <pre><your_ip>.v or <your_ip>.vhd</your_ip></your_ip></pre> | HDL files that instantiate each submodule or child IP core for synthesis or simulation.                                                                                                                                                                                                                                                                                                                                                                             |

| mentor/                                                     | Contains a ModelSim* or QuestaSim* script msim_setup.tcl to set up and run a simulation.                                                                                                                                                                                                                                                                                                                                                                            |

| synopsys/vcs/                                               | Contains a shell script vcs_setup.sh to set up and run a VCS* simulation.                                                                                                                                                                                                                                                                                                                                                                                           |