## **Programming Guide and User Manual**

Infineon Coreless Current Sensor for high voltage industry applications

## **About this document**

- This document describes how to program the TLI4971 with the Infineon proprietary one wire interface (SICI)

to set different gain levels, over current thresholds, operating modes and further features described in the

data sheet.

- Besides the timing of the serial inspection interface, the command structure and all possible commands for write read and EEPROM access are described in this document.

- A detailed description of the user changeable EEPROM bits are part of this application note.

- The document includes a programming example for changing the measurement range to ±120A full scale range by changing the parameter via the interface.

- Besides the document also describes application circuits for three phase systems as they are typically used in inverter and motor control applications.

- In order to allow in circuit programming of the sensor in an application the document gives a recommendation how to protect a micro controller against the required programming voltage.

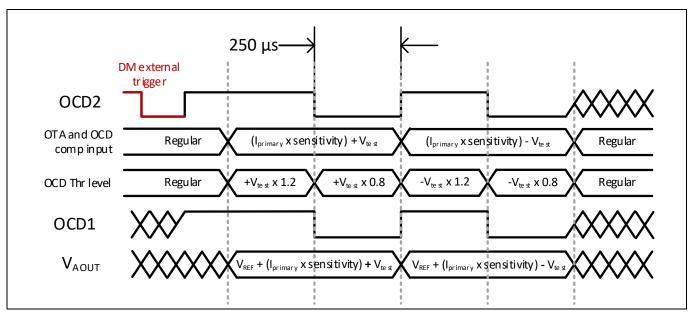

- In addition, there is also a description of the different operating modes and the OCD functionality.

- Since the TLI4971 has also implemented an internal diagnostic mode this application note also describes how to trigger the diagnosis mode and how to interpret the output pattern.

## **Programming Guide and User Manual**

For productive in circuit programming Infineon recommends to use a verified programmer which has been a coproduction development between Infineon and CGS. The programmer is fully compatible with the NI standard and provides the connections for the communication as well as the required programming voltage. For further documentation please refer to Sensor – Programmer – CGS – Computer Gesteuerte Systeme GmbH (cgs-gruppe.de)

Further Infineon provides a lab usage programming board. The tool can be used to communicate with three sensors in parallel and can be supplied via the USB connection port of a PC.

## Scope and purpose

TLI4971 Coreless Current Sensor Feature set, EEPROM and interface description.

### Intended audience

- Users who use the high variety of the TLI4971 current sensor by programming the functionality like full scale or over current detection, operating modes etc. to their need.

- Current Sensor Module Developers.

# **Programming Guide and User Manual**

## **Table of contents**

| Curre | ent Sensor TLI4971                                   | 1  |

|-------|------------------------------------------------------|----|

| Abou  | ut this document                                     | 1  |

| Table | le of contents                                       | 3  |

| 1     | Application and Programming circuit                  | 4  |

| 1.1   | Circuit / Precondition                               |    |

| 1.2   | In-circuit programming with external Programmer      | 6  |

| 1.3   | In-circuit programming w/o external Programmer       |    |

| 2     | Serial Inspection and Configuration Interface (SICI) | 9  |

| 2.1   | Hardware Implementation                              |    |

| 2.2   | Entering Communication Mode                          | 10 |

| 2.3   | Communication timing                                 | 11 |

| 2.3.1 | Single low/high PWM transmission                     | 11 |

| 2.4   | Interface Timing Definition                          |    |

| 2.5   | Definition of Voltage Levels                         | 14 |

| 3     | Interface description                                |    |

| 3.1   | Command Structure                                    |    |

| 3.2   | Interface Commands                                   |    |

| 3.3   | Read Command                                         |    |

| 3.4   | Write Command                                        |    |

| 3.5   | Write and programming sequence                       |    |

| 3.5.1 | 1 7 0                                                |    |

| 3.6   | Read Example (temperature register read out)         |    |

| 4     | EEPROM                                               |    |

| 4.1   | EEPROM Content                                       |    |

| 4.2   | Programming Example                                  |    |

| 4.3   | Cyclic Redundancy Check                              |    |

| 4.4   | Code example CRC calculation                         |    |

| 5     | Operation Mode                                       |    |

| 5.1   | Single-Ended Mode                                    |    |

| 5.2   | Fully-differential Mode                              |    |

| 5.3   | Semi-differential Mode                               |    |

| 6     | How to connect the sensor in a 5V domain             |    |

| 6.1   | Single-Ended Mode                                    |    |

| 6.2   | Semi and or Fully-differential Mode                  |    |

| 7     | Diagnosis Mode                                       | 41 |

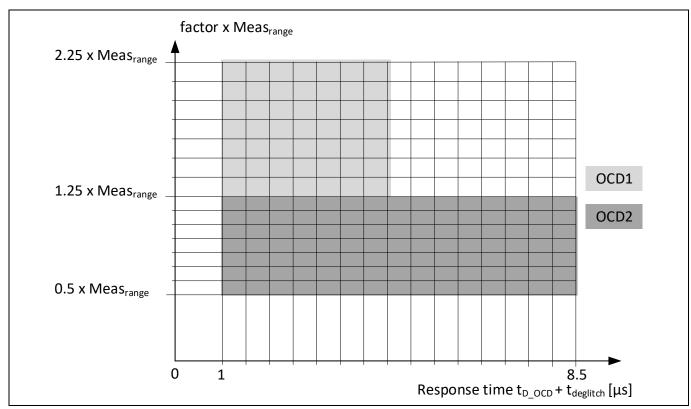

| 8     | Over Current detection (OCD)                         | 44 |

| 9     | Glossary                                             | 45 |

# 1 Application and Programming circuit

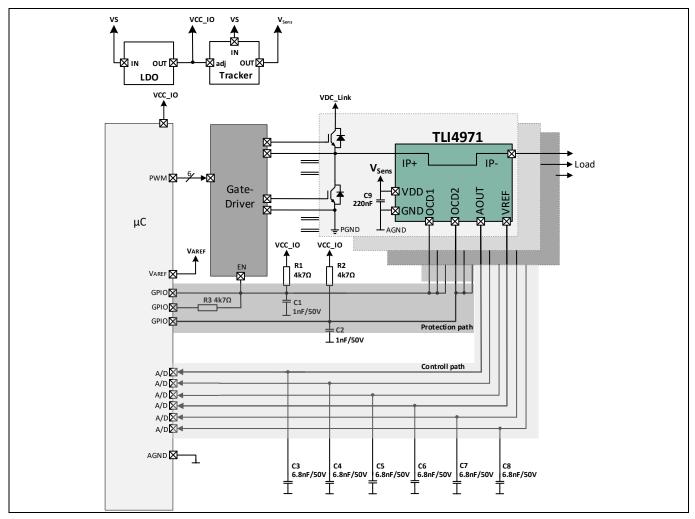

The sensor supports a variety of output modes as well as measurement ranges. Also the threshold and blanking time of the over current channels can be programmed. Therefore, the device has implemented a serial interface to set the EEPROM content of each sensor separately. This chapter describes the hardware implementation to program the device. Further, it shows the recommended circuit for a three-phase GPD application.

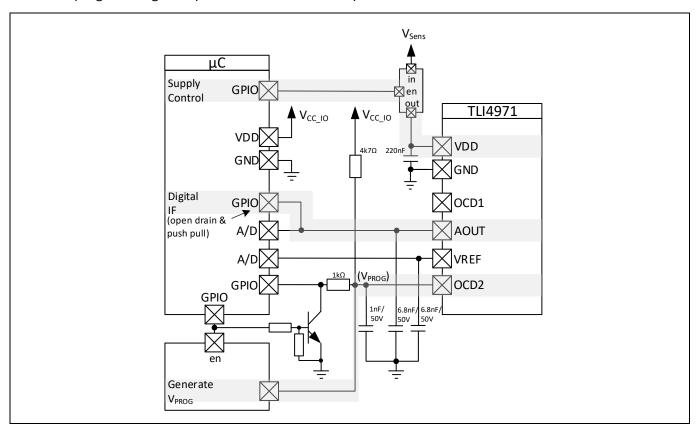

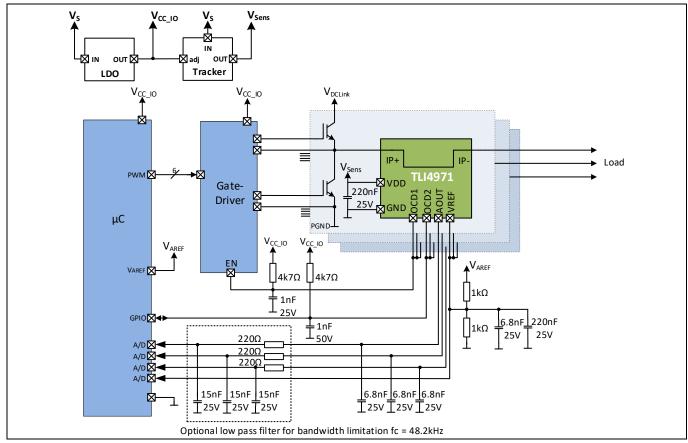

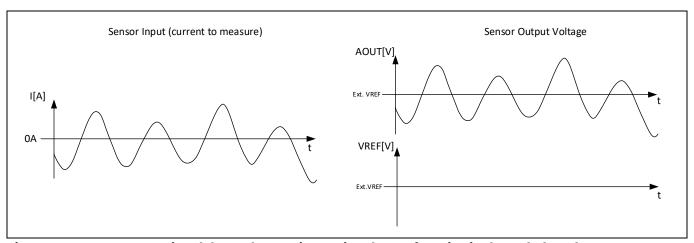

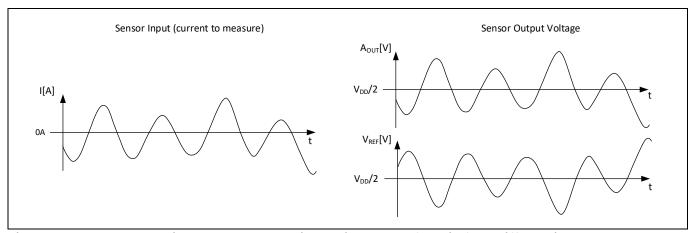

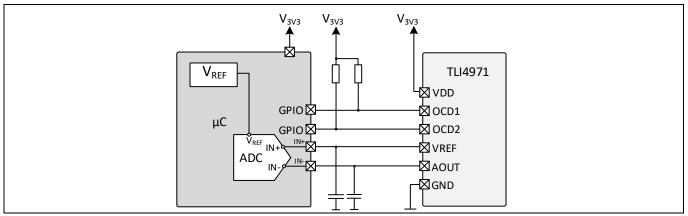

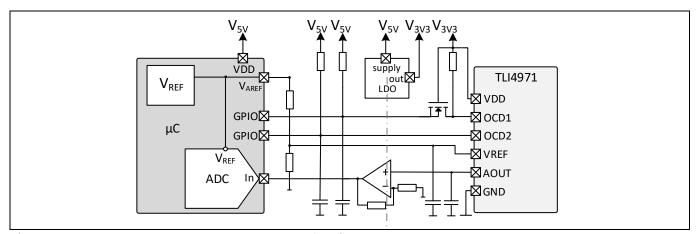

Figure 1 TLI4971 3-phase GPD application circuit for semi and or fully- differential mode

Figure 1 shows the recommended circuit for a three-phase GPD application. As shown in the figure, the sensor provides a control as well as a protection interface. The protection functionality is covered by two open drain outputs (OCD1 and OCD2) to indicate an overload and to protect the system in case of an over current event. In this case the OCDs will indicate in less than 1 $\mu$ s. The OCD1 output is typically connected to the enable input of the HV gate-driver to de-activate the IGBT. The second open drain output OCD2 is connected to an interrupt input of the microcontroller. The threshold of the OCD2 is typically set below the threshold of the OCD1 to enable a pre-warning. For controlling purpose, the  $A_{OUT}$  and  $V_{REF}$  are connected to the analog to digital converter of a microcontroller or FPGA.

In-circuit programming of the sensor device can be done with an external programmer. It is also possible to access the EEPROM without an external programmer by using the GPIO pin of the controller or FPGA used in the current sensing application to establish a communication with the sensor.

## **Programming Guide and User Manual**

#### 1.1 **Circuit / Precondition**

Each device can be set separately via the SICI-one wire interface.

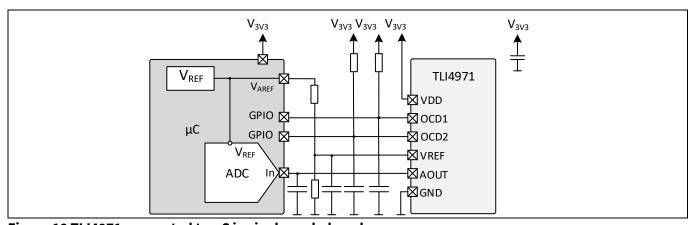

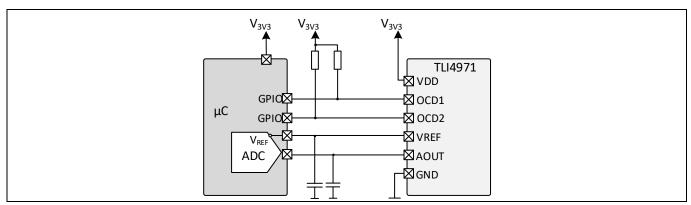

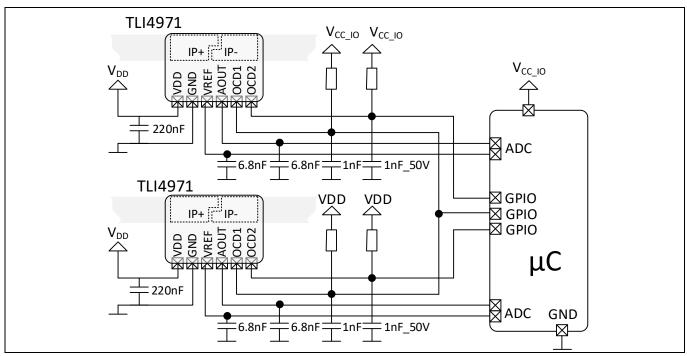

In order to communicate with the sensor via the SICI one wire interface the A<sub>OUT</sub> lines of each sensor has to be connected with a microcontroller or FPGA. Figure 3 shows a simple drawing how to connect the relevant pins to enable an in-circuit communication between the sensors and a microcontroller.

In order to use an external programmer, a programing connector has to be linked with each A<sub>OUT</sub> pin to establish a communication to the sensors.

As a first step of the programming procedure, the parameter has to be downloaded into the volatile memory area of the sensor via the SICI interface.

As a second step of the programming procedure, the parameter needs to get stored into the non volatile memory (EEPROM) by sending the programming command via the AOUT pin and applying the programming voltage on OCD2 pin.

Therefore, the OCD2 needs also to be connected to the programming connector.

To enter the interface the controller needs to enable a power down of the sensor. Therefore, also the sensor supply needs to be controlled by the programmer.

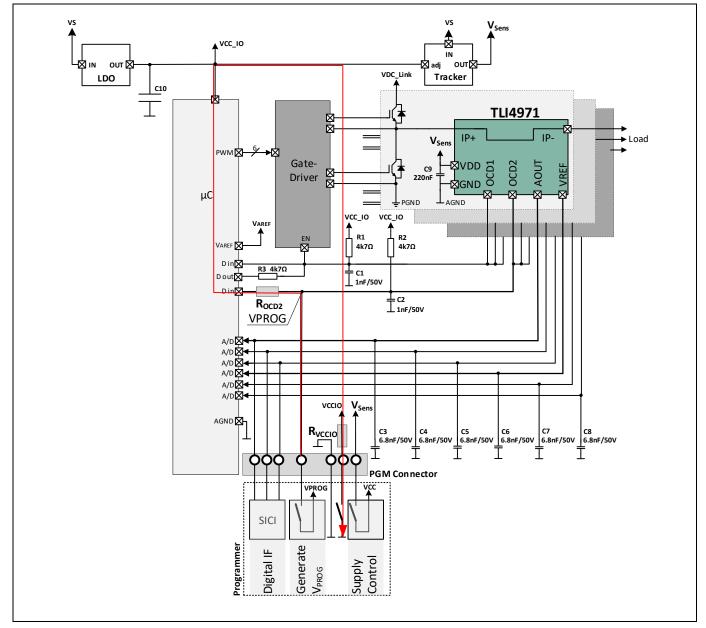

## 1.2 In-circuit programming with external Programmer

This chapter shows the hardware implementation for a programming connector to be used with an external programmer in order to program the sensors.

To enter the sensor's interface a control of the sensor supply is necessary to enable a controlled power down of the sensor by an external controller. Beside the OCD2 and the  $A_{OUT}$  pin must be connected to an external programmer.

In order to program the EEPROM a digital interface via the  $A_{OUT}$  pin is used to apply the particular programming sequence. After sending the programming sequence, an assertion of the programming voltage is required at pin OCD2. It is not possible to reprogram the sensor without sending the according programming sequence via the  $A_{OUT}$  pin before. Therefore in a multiple sensor system the OCD2 can be tied together as each sensor will receive their individual data set via the separated  $A_{OUT}$  pin connection. The programming voltage can then be applied to all sensors in parallel considering the max current consumption. Find a detailed programming example in the chapter 0.

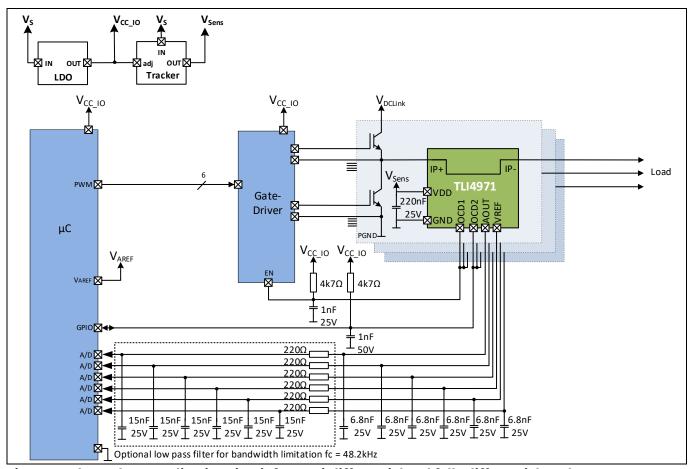

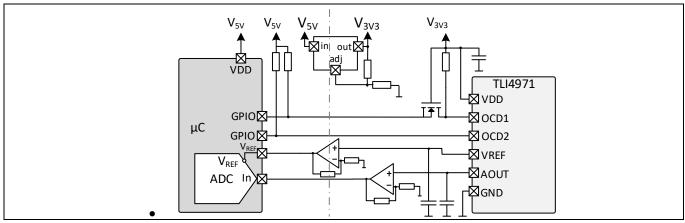

Figure 2 External Programmer connected to GPD application circuit (TLI4971 in-circuit-programming)

## **Programming Guide and User Manual**

Figure 2 shows the recommended circuit for a three-phase GPD application with the required add-on circuit to enable in-circuit programming.

A programming connector needs to be connected to each A<sub>OUT</sub> pin of the sensor to access the digital interface.

The OCD2 pin needs to be connected to apply the programming voltage.

The senor supply needs to be connected to the programmer in order to allow a controlled power down of the sensor.

The serial resistors R<sub>OCD2</sub> and R<sub>VCCIO</sub> are recommended to avoid a current feedback into the supply and to avoid possible high floating of the μC supply.

Figure 2 shows the overall programming circuit including the μC supply, the tracker and the programmer. The high voltage assertion during programming may cause a current feedback into the supply rail of e.g. the μC. This can happen when the  $\mu$ C does not pull-down the pin or a needle prober would keep the line to 3.3V or the rail current consumption is lower than the current via the series resistor R<sub>OCD2</sub>. Figure 2 shows the recommended series resistors to avoid a feedback current into the supply.

Therefore, the resistors R<sub>OCD2</sub> and R<sub>VCCIO</sub> have to be determined as described in following formula.

$$\frac{V_{CCIO}}{R_{VCCIO}} > \frac{V_{PROG} - V_{CCIO}}{R_{OCD2}} \mid R_{OCD2} = 10 \text{k}\Omega \text{ R}_{VCCIO} = 330\Omega$$

Alternatively, the OCD2 channel can be connected with a pull down resistor to GND while applying the programming voltage on the OCD2 pin as shown in Figure 4.

## 1.3 In-circuit programming w/o external Programmer

This chapter describes the hardware implementation allowing in-circuit programming of the device without an external controller.

As mentioned before the device features a digital interface to access the sensor's memory, which can be accessed via the  $A_{OUT}$  pin. To enter the interface the senor supply needs to be controlled to enable a power-down respectively power on of the device. To store the data into the non-volatile memory of sensor a programming voltage has to be applied on the OCD2 pin. Therefore, the following has to be considered:

- Connect the AOUT pin of each device with a GPIO port.

- For a proper communication between the sensor and the controller, the GPIO pin shall support open drain as well as push pull functionality. While sending data to the sensor the GPIO pin shall be set into push-pull mode. While reading data from the sensor the GPIO pin shall behave in open drain mode.

- To program the content of the register into the non-volatile memory (EEPROM) a programming voltage has to be applied on the OCD2 pin. The microcontroller shall control the programming voltage.

- The high voltage assertion of the programming voltage might cause a current feedback into the supply rail. It

is recommended to protect the μC against possible high floating voltage by connecting the OCD2 pin to GND.

Figure 3 shows an optional implementation to connect the OCD2 to GND while applying the programming

voltage to the device preventing the μC supply to float high.

- The microcontroller shall control the sensor supply in order to meet the correct timing to enter the interface. A controlled power-down respectively power-on of the sensor's supply is required to enter the interface.

A detailed programming example is described in the chapter 0.

Figure 3 TLI4971 In-circuit programming without external programmer

# 2 Serial Inspection and Configuration Interface (SICI)

The sensor features a digital interface (SICI). Connect the  $A_{OUT}$  pin to a GPIO port in order to establish a communication between the sensor and the controller. The SICI interface is a 16bit bidirectional one wire interface. The protocol specification and command structure is described in this chapter.

## 2.1 Hardware Implementation

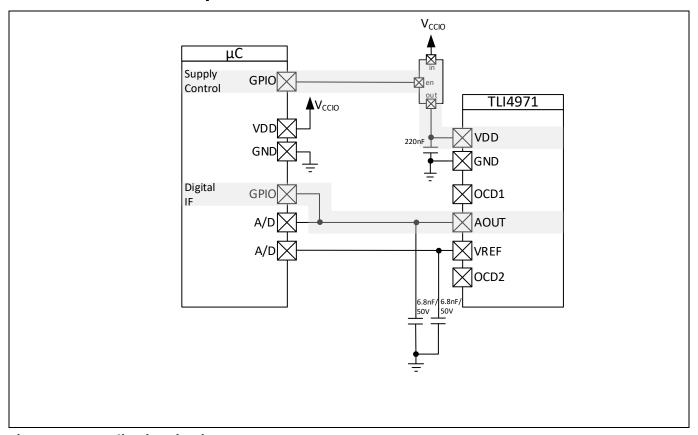

Figure 4 SICI application circuit

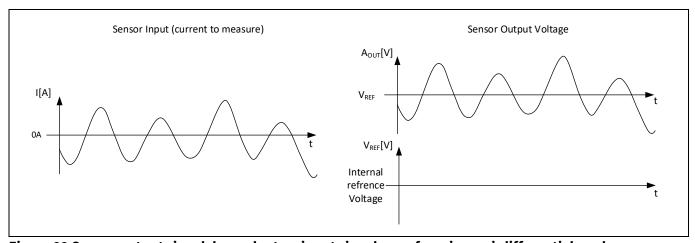

Figure 4 shows the application circuit to communicate with the TLI4971 current sensor.

In order to change the register values the sensor features a digital interface, which can be accessed by a microcontroller via the  $A_{OUT}$  pin. Therefore, the microcontroller needs to drive the  $A_{OUT}$  pin to GND to modulate the pin according to the SICI protocol description.

For communication, it is necessary that the A<sub>OUT</sub> have to be connected to a GPIO port of a microcontroller.

To activate the interface the AOUT shall be forced to GND during and after the sensor startup.

Therefore, the external controller shall control the sensor supply to meet the correct timing and to allow a successful interface activation.

The communication is based on transmitting a bit stream to the sensor driven by an external controller. For this interface, the  $A_{OUT}$  pin is used as an I/O pin to read from the device and to write the registers of the device by forcing the pin with a defined timing.

The interface timing specification is shown in Table 1 and described in Figure 6 and Figure 7.

#### 2.2 **Entering Communication Mode**

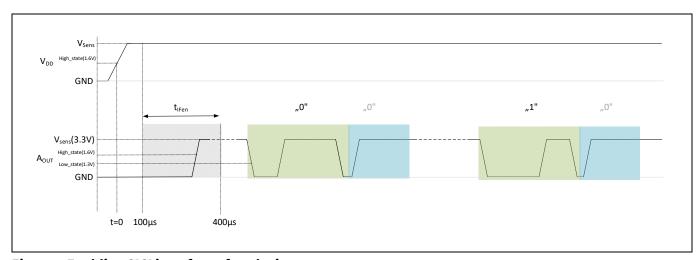

After or while suppling the sensor, the A<sub>OUT</sub> pin shall be forced to GND to enter the interface mode of the device. Figure 5 shows the "interface enable time" t<sub>IFen</sub> which is the valid time window to enable the SICI interface. Therefore, it is important to control also the device supply to meet the correct timing after supplying the sensor. The output buffer of the sensor keeps the A<sub>OUT</sub> pin to V<sub>DD</sub> (open drain with internal pull up) within the first 400µs after supplying the device. The A<sub>OUT</sub> pin has to be controlled by an external controller to GND for t<sub>low</sub> time in between the defined time window t<sub>IFen</sub>. This low state has only to be present once after start up to allow the device to receive the 16 bit enter-interface-command. The activation will also work if the A<sub>OUT</sub> stays at ground from the beginning. There is no need to set the  $A_{OUT}$  to  $V_{DD}$  before forcing it to GND. Figure 5 shows the modulation of the A<sub>OUT</sub> pin while enabling the interface after supplying the sensor.

While sending the enter-interface-command, the device answers to each sent bit with logic "0" as shown in Figure 5.

After a correct enter-interface-command has been sent, the A<sub>OUT</sub> pin will remain at V<sub>Sens</sub> (open drain).

If the interface activation is unsuccessful then the A<sub>OUT</sub> pin will reflect the quiescent voltage.

To enable the access to the sensor memory the internal intelligent state machine (ISM) needs to be disabled with a dedicated command like described in chapter 3.

Figure 5 Enabling SICI interface after device start up

## 2.3 Communication timing

This describes the timing of the  $A_{OUT}$  pin to ensure a correct communication between the sensor and a microcontroller. To set the  $A_{OUT}$  to low state, force the  $A_{OUT}$  to GND from an external micro controller or FPGA.

By default, the device drives the A<sub>OUT</sub> to high state except during response time depending on the sent data (open drain).

As communication runs in both direction the GPIO of the external controller shall support tri state.

Force the  $A_{OUT}$  to GND within the first 400 $\mu$ s after power on to activate the interface.

After releasing the  $A_{OUT}$  back to  $V_{Sens}$ , send the 16-bit enter-interface-command with LSB first from controller. Figure 5 shows the LSB and MSB of the enter-interface-command.

In the Figure 5, the green highlighted squares indicate the received bit while the blue highlighted squares indicate the bits sent by the sensor.

## 2.3.1 Single low/high PWM transmission

For a single low/high PWM transmission, the duty cycle shall be at least 30/70 or 70/30.

- Logic "0" is sent as a short low and long high PWM pulse

- Logic "1" is sent as a long low and short high PWM pulse

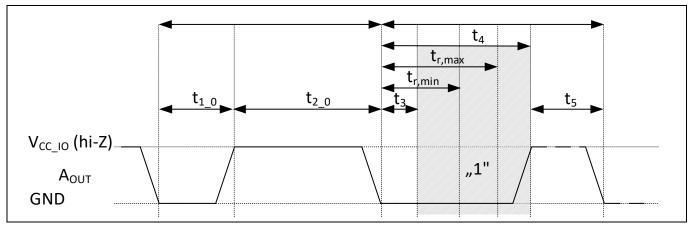

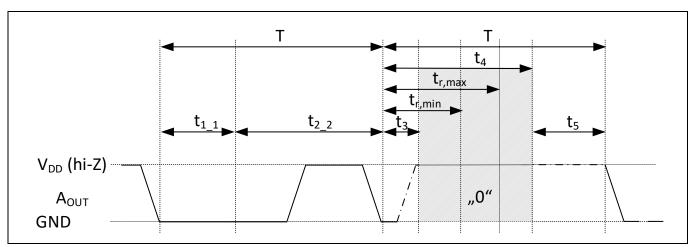

Figure 6 SICI duty cycle; sending logic '0' to the device; receiving logic '1' from the device

The initial pulse length  $t_1$  &  $t_2$  in Figure 6 and Figure 7 determines the write sequence. The read-out time  $t_4$  is marked with a grey square shown in Figure 6 and Figure 7

Table 1 describes the interface timing. An example of a 1-bit transmission sending a logic '0' to the device by receiving a logic '1' can be seen in Figure 6.

Figure 7 shows an example of a 1-bit transmission sending logic "1" to the device by receiving logic "0".

When sending a logic "0" to the device the low time t<sub>1</sub> has to be shorter than the high time t<sub>2</sub>.

The timing of the read sequence  $t_4$  is depending on the low time  $t_1$  and high time  $t_2$  as described in Table 1.

Perform a read access at half of the t₄time window. Figure 6 shows the voltage level of the A<sub>OUT</sub> pin while sending a logic "1" bit. Figure 7 shows the voltage level of the A<sub>OUT</sub> while sending a logic "0".

The grey squares in Figure 6 and Figure 7 mark the time window when reading shall be performed by a microcontroller or FPGA. During the reading time, the master shall not drive the  $A_{OUT}$  pin.

Figure 7 SICI duty cycle; sending logic '1' to the device; receiving logic '0' from the device

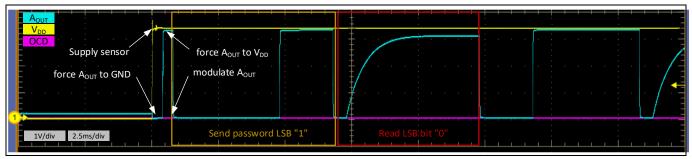

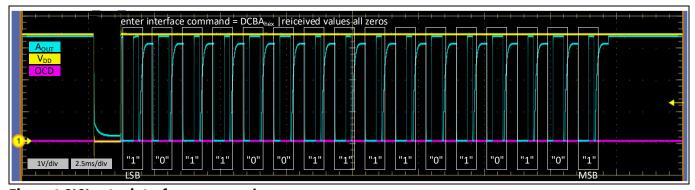

Figure 8 SICI enter interface sequence

Figure 8 describes the interface activation by modulating the AOUT after startup. The modulation of the first two password bits can be seen in the oscilloscope picture.

Figure 9 SICI enter interface command

Figure 9 shows the oscilloscope picture of the enter interface command to activate the sensor interface after performing the startup sequence.

The oscilloscope pattern shows the PWM-modulation of each sent bit followed by the answer bit.

After sending the enter interface command the next falling edge of the  $A_{OUT}$  will start the subsequent 16bit commands.

After sending a 16bit command, the  $A_{OUT}$  is still driven high by the device.

To perform a high state the A<sub>OUT</sub> shall be set to tri state. Especially during the response phase, the A<sub>OUT</sub> shall be set to tri state because the sensor needs to drive the A<sub>OUT</sub>.

## **Programming Guide and User Manual**

Table 1 shows the defined timing for the SICI interface. There is no timing restriction between two commands.

# 2.4 Interface Timing Definition

Table 1 describes the SICI interface timing.

Table 1 Interface timing

| Parameter             | Symbol                | Min.                                       | Тур.                           | Max. | Unit                | Notes                                                                                                                                                                                                        |

|-----------------------|-----------------------|--------------------------------------------|--------------------------------|------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface enable time | t <sub>IFen</sub>     | 100                                        | 150                            | 400  | μs                  | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| Period time of 1 bit  | Т                     | 40                                         | t <sub>1</sub> +t <sub>2</sub> | 7500 | μs                  | One communication frame consist of 16 x 2 bits (16bits write / 16bits read)                                                                                                                                  |

| Low time sending 0    | t <sub>1_0</sub>      | 28                                         | 33                             | 38   | % of T              | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| Low time sending 1    | t <sub>1_1</sub>      | 62                                         | 67                             | 72   | % of T              | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default.                                                                                                                                            |

| High time sending 0   | t <sub>2_0</sub>      |                                            | T-t <sub>1_0</sub>             |      | μs                  | Drive A <sub>OUT</sub> to GND                                                                                                                                                                                |

| High time sending 1   | t <sub>2_1</sub>      |                                            | T-t <sub>1_0</sub>             |      | μs                  | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default.                                                                                                                                            |

| Low time before read  | <b>t</b> <sub>3</sub> | 10                                         | -                              | 30   | % of t <sub>4</sub> | Drive $A_{OUT}$ to GND<br>$t_4 = 2 * ABS(t_{1\_x} - t_{2\_x})$<br>$t_3$ can be set as applicable. Increase of<br>$t_3$ will reduce sensor response time $t_4$ .<br>Therefore $t_r$ has to be set accordingly |

| Reading time          | t <sub>r</sub>        | 50                                         | -                              | 80   | % of t <sub>4</sub> | The device drives A <sub>OUT</sub> to V <sub>DD</sub> by default. Set the external controller in tri state.                                                                                                  |

| Response time         | t <sub>4</sub>        | 2 abs(t <sub>1_x</sub> -t <sub>2_x</sub> ) | -                              | -    | μs                  | t <sub>3</sub> can be set as applicable. Increase of t <sub>3</sub> will reduce the response time t <sub>4</sub> .                                                                                           |

| Time between 2 bits   | t <sub>5</sub>        | 1                                          | T-t <sub>4</sub>               | 5400 | μs                  |                                                                                                                                                                                                              |

| Max high time         | thigh                 | 1                                          | -                              | 5400 | μs                  | Only valid for a single bit high time. There is no restriction in timing between two commands                                                                                                                |

| Min low time          | t <sub>low</sub>      | 1                                          | -                              | 5400 | μs                  |                                                                                                                                                                                                              |

- There is no timing restriction between two commands as long as the A<sub>OUT</sub> pin is not driven to GND.

- The typical threshold level to detect a logic "0" during a high to low transition is 1.3V.

- The typical threshold level to detect a logic "1" during a low to high transition is 1.6V.

### Interfaces enable time

The interface enable time  $t_{IFen}$  defines the time window to force the  $A_{OUT}$  pin to GND after start up to enable the interface communication via SICI.

### Period time of 1 bit

The period time defines the time to transmit 1 bit between the device and a micro controller. One communication frame consists of 16 write and 16 read bits.

## Low time sending 0

The  $t_{1_0}$  defines the first low time of a bit. The low time has to be shorter than the next high time to send a logic 0 bit to the device. Every bit has to start with a low time.

## Low time sending 1

## **Programming Guide and User Manual**

The  $t_{1.1}$  defines the first low time of a bit. The low time has to be longer than the next high time to send a logic 1 bit to the device. Every bit has to start with a low time.

## High time sending 0

The  $t_{2_{-0}}$  defines the first high time after the low time of a single bit. In order to send a logic 0 to the device the high time has to be longer than the previous low time.

### High time sending 1

The  $t_{2,1}$  defines the first high time after the low time of a single bit. In order to send a logic 1 to the device the high time has to be shorter than the previous low time.

### Low time before read

The  $A_{OUT}$  pin has to be forced to GND after the first high time of a transmitted bit to initiate the reading sequence. This low time is described by  $t_3$ .

## **Response time**

During this time, the  $A_{OUT}$  pin is driven from the device. Therefore, the  $A_{OUT}$  pin shall not be driven by the master. The device drives the  $A_{OUT}$  either to GND or  $V_{DD}$  as described in Figure 6 and Figure 7. The  $A_{OUT}$  pin level shall be read by the master in the defined time window to receive the answer. The data from the device shall be read between 50% and 80% of the response time ( $t_r$ ).

### Time between two bits

The maximum high time between two bits is limited by the maximum allowed high time. By exceeding the maximum high time, the interface is deactivated and can only be entered after restarting the device.

## Max high time

If  $A_{OUT}$  stays at  $V_{DD}$  longer than the defined max high time  $t_{high}$ , the SICI communication is closed and the sensor starts working in the defined operating mode. To start a new communication the sensor shall be powered off and on again.

### Min low time

If  $A_{OUT}$  stays at GND longer than the defined max low time  $t_{low}$  the SICI communication is closed and the sensor starts working in the defined operating mode. To start a new communication the sensor shall be powered off and on again.

# 2.5 Definition of Voltage Levels

The SICI interface voltage levels and the voltage level to program the EEPROM are specified in Table 2.

### Table 2 SICI High and low level definition

| Parameter                                   | Symbol                 | Min. | Тур. | Мах. | Unit | comment    |

|---------------------------------------------|------------------------|------|------|------|------|------------|

| Voltage level for SICI – High <sup>1)</sup> | V <sub>SICI_High</sub> | 1.6  | 3.3  | 3.5  | V    | high state |

| Voltage level for SICI – Low <sup>2)</sup>  | Vsici_Low              | -0.3 | 0    | 1.3  | V    | low state  |

### Interface description 3

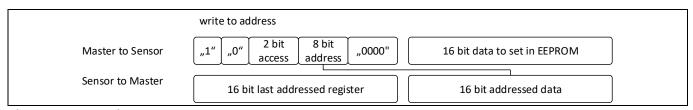

#### 3.1 **Command Structure**

A typical SICI communication consists in multiple input commands sent to the device via A<sub>OUT</sub> voltage modulation, to which the sensor responds modulating the same A<sub>OUT</sub> pin.

An input command is composed of 16 bits LSB first. One bit consists of a transmission sequence initiated by the master and a receiving sequence driven by the device. The reply data stream sent by the device starts with the LSB.

A typical communication consists of a command including the access information and address sent by the master to the device. The device replies with the data, which has been addressed by the former received command.

The upper nibble of the command include the access information. The MSB has to be set to '1' to perform a write command. To send a read command the MSB has to be set to '0'. Depending on the two LSB of the upper 4 bits, the sent data will be set in the addressed register.

Table 4 describes the usage of the access bit.

Table 3 describes the command structure. Depending on the access bit, the device interprets the received data as either a write or a read command.

### **Table 3 SICI Command structure**

| 15  | 14 | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3 | 2 | 1 | LSB |

|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|-----|

| w/r | 0  | Ac1 | Ac0 | Ad7 | Ad6 | Ad5 | Ad4 | Ad3 | Ad2 | Ad1 | Ad0 | 0 | 0 | 0 | 0   |

### **Table 4Access bit description**

| w/r | Ac1 | Ac0 | description                                       |

|-----|-----|-----|---------------------------------------------------|

| 1   | 0   | Χ   | Set ones and zeros like the sent 16 bit data word |

| 1   | 1   | 0   | Set only the sent zeros. The ones will not be set |

| 1   | 1   | 1   | Set only the sent ones. The zeros will not be set |

# **Programming Guide and User Manual**

### 3.2 **Interface Commands**

## **Table 5 Available Commands**

| Command name               | address <sub>hex</sub>                 | command <sub>hex</sub> | description                                                                                            |

|----------------------------|----------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|

| Enter Interface command    |                                        | ABCD <sub>hex</sub>    | Activate communication as described in chapter Entering Communication Mode                             |

| Power down ISM             | 25 <sub>hex</sub>                      | 8000 <sub>hex</sub>    | reserve if-access to the EEPROM data bus to avoid that ISM is blocking the data bus                    |

| Disable failure indication | 02 <sub>hex</sub>                      | 0000 <sub>hex</sub>    | Prevent unintended activation of the OCD2 output                                                       |

| Write command              | 40 <sub>hex</sub> to 42 <sub>hex</sub> | 8400 <sub>hex</sub>    | Initialize Write command to address 40 <sub>hex</sub>                                                  |

| Send values                |                                        | XYXY                   | send data XYXY to previous addressed line<br>where XYXY stand for 16bit data<br>placeholder            |

| Read command               | 40 <sub>hex</sub> to 51 <sub>hex</sub> | 0400 <sub>hex</sub>    | Initialize read command at address 40 <sub>hex</sub>                                                   |

| Read command               | 41 <sub>hex</sub>                      | 0410 <sub>hex</sub>    | Initialize read command at address 41 <sub>hex</sub> read data from previous address 40 <sub>hex</sub> |

| Read command               | 51 <sub>hex</sub>                      | 0510 <sub>hex</sub>    | Initialize read command at address 51 <sub>hex</sub> read data from previous address                   |

| NOP                        |                                        | FFFF <sub>hex</sub>    | No operation command, to read former addressed values.                                                 |

| EEPROM set all zeros       | 3E <sub>hex</sub>                      | 0248 <sub>hex</sub>    | Set all EEPROM bit to zero                                                                             |

| EEPROM set all ones        | 3E <sub>hex</sub>                      | 024B <sub>hex</sub>    | Set all EEPROM bit to one                                                                              |

| EEPROM refresh             | 3E <sub>hex</sub>                      | 024C <sub>hex</sub>    | Refresh the all EEPROM lines                                                                           |

| EEPROM program zeros       | 3E <sub>hex</sub>                      | 024E <sub>hex</sub>    | Program all set zeros into EEPROM                                                                      |

| EEPROM program ones        | 3E <sub>hex</sub>                      | 024F <sub>hex</sub>    | Program all set ones into EEPROM                                                                       |

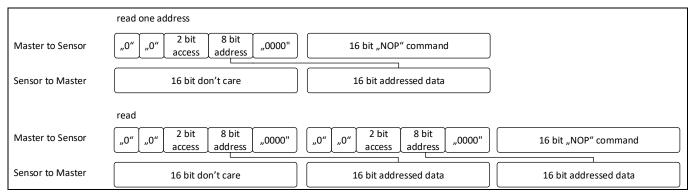

#### **Read Command** 3.3

There is always a delay of one command between the request command and the addressed data. When a new read command is sent to the sensor, the device replies with the data requested with the former command. Therefore, two commands have to be sent to read one address. A read sequence consists of the read command with the requested address followed by a second command to receive the previous addressed data. The second command can either be a read or write command to address the next line. The NOP command terminates a read sequence without initializing a new read or write sequence. Every command replies with the previous addressed data except the enter interface command. While sending the enter interface command the device replies with all zeros.

Figure 10 SICI read sequence

#### 3.4 Write Command

To perform a write command in order to change register values in the device the MSB of the command has to be set to one as described in Table 4. After each write command, the device is expecting further 16 bit of data. To perform an EEPROM command send a write sequence to the device. A write sequence consists of two 16 bits data sets. Before sending the 16 bits command data, send the write command with the according address and access information to the device.

Table 5 describes the EEPROM commands, which have to be send to their corresponding addresses.

Figure 11 SICI write sequence

#### 3.5 Write and programming sequence

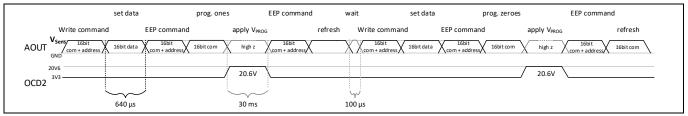

**Figure 12 Programming Seequence**

Figure 12 shows the command sequence for a write command and describes the sequence to program the EEPROM.

A command always consists of a 16bit command which also includes the address followed by 16bit data.

After writing the values into the EEPROM, the programming voltage has to by applied for 30ms to program the values.

After programming, a refresh command shall be performed as shown in Figure 12.

#### 3.5.1 **Temporary register**

For test purpose, it is possible to change the sensor settings in the temporary registers. This allows testing all user access able settings without applying the programming voltage to the sensor.

It is not possible to store the content of the temporary registers in to the EEPROM.

It is not recommended to write into the temporary register to change sensor settings to be used in normal operating mode.

The addresses for the temporary registers are different from the EEPROM addresses. Table 1 shows the correlating address for the temporary and EEPROM registers.

In order to get access to the register send 0x8000 to address 25<sub>hex</sub>.

To temporary disable the CRC-check, set the register  $1_{hex}$  to 0x0000.

Set the register 25<sub>hex</sub> to 0x1000 to leave the interface mode and to change into normal operating mode.

After the sensor remains in operating mode until the next power down.

The sensor uses the content of the temporary registers instead of the correlating EEPROM values until the next power down.

**Table 6 Temporary register description**

| Temporary register address | EEPROM register address | Note                                                                                                                           |

|----------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 25 <sub>hex</sub>          | -                       | Write 0x8000 to this address to get access to the register (otherwise the registers gets occupied / overwritten by the sensor) |

| 01 <sub>hex</sub>          | -                       | Write 0x0000 to temporary disables failure indications like CRC check.                                                         |

| 17 <sub>hex</sub> 1)       | 40 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |

| 18 <sub>hex</sub> 1)       | 41 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |

| 19 <sub>hex</sub> 1)       | 42 <sub>hex</sub>       | Bit description and bit position same for both addresses                                                                       |

<sup>1)</sup> Change values in temporary registers for test purpose only. Please refer to bit description of corresponding EEPROM addresses.

#### 3.6 Read Example (temperature register read out)

The accurate and linear temperature value can be read out via the SICI interface. The following example describes the required command sequence to enter the interface and to read out the 16 bit temperature value. In the following table the commands with the correct timing order and the required minimum time for each command respectively sequence are listed. The temperature sensitivity is set to a sensitivity of 16LSB16/°C. The ADC value for 25°C corresponds to .1408LSB16. The following formula describes how to calculate the temperature dependent on the 16bit value.

$$Temperature = \frac{ADC_{value} - 2048}{16} + 65$$

Table 7 Command sequence example to read out the internal 16 bit temperature value

| Command / sequence                         | minimum frame time | Description                                                                                                                                     |

|--------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD <sub>hex</sub>                        | 0.64ms             | Enter interface command (sending 16bit reading 16bit)                                                                                           |

| Write command to address 25 <sub>hex</sub> | 0.64ms             | Power down ISM<br>(write to address 25 <sub>hex</sub> )                                                                                         |

| 8000 <sub>hex</sub>                        | 0.64ms             | Power down ISM<br>(write data)                                                                                                                  |

| Read command at address 18 <sub>hex</sub>  | 0.64ms             | Sending the address to read the temperature value                                                                                               |

| FFFF <sub>hex</sub>                        | 0.64ms             | Reading the data by sending the next command or sending the NOP command. In case of sequential read out the data can be received every 1.28 ms. |

Power on and off the device to activate normal operating mode. (1.5ms typical after power on) Alternatively set the device in normal operating mode by sending the following commands:

| Write command to address 25 <sub>hex</sub> | 0.64ms | Power on ISM<br>(write command to address) |

|--------------------------------------------|--------|--------------------------------------------|

| 1000 <sub>hex</sub>                        | 0.64ms | Power on ISM<br>(send data)                |

Wait until the A<sub>OUT</sub> settles back into calibrated mode. In calibrated mode, the A<sub>OUT</sub> reflects the voltage level of the V<sub>REF</sub> pin. Assumed no current flows through the primary current rail of the device.

#### 4 **EEPROM**

The sensor's non volatile memory (EEPROM) is organized in 16-bit (word) registers which can be addressed individually. The storage space is separated into two areas, a user area with allows read/write access and a reserved area with read access only.

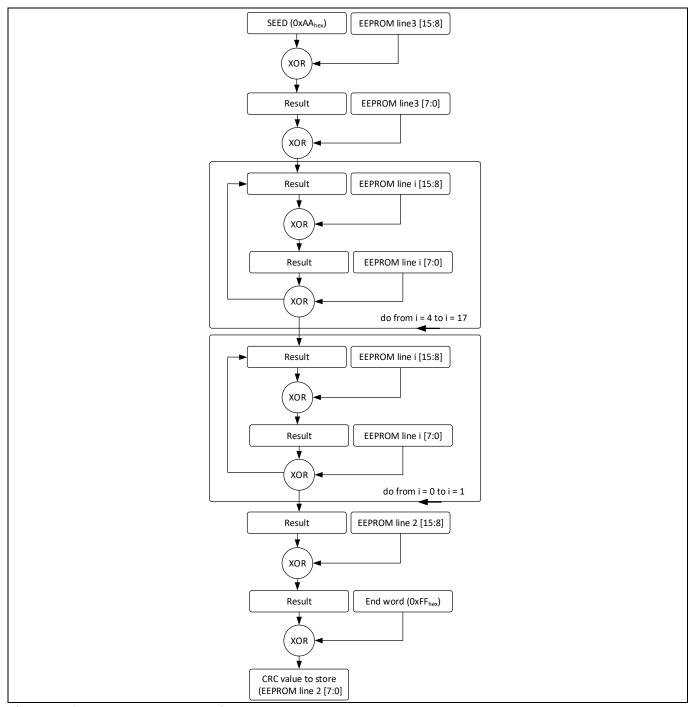

When content in the user area is reprogrammed, a CRC check register has to be updated. Since the EEPROM CRC is calculated covering the entire EEPROM storage space, the user is required to readout the entire EEPROM content, calculate the new CRC values and store it into the respective registers. An incorrect CRC value will be detected by the sensor and cause a transition to its safe state. In case of a CRC error the OCD open drain output will be set to GND.

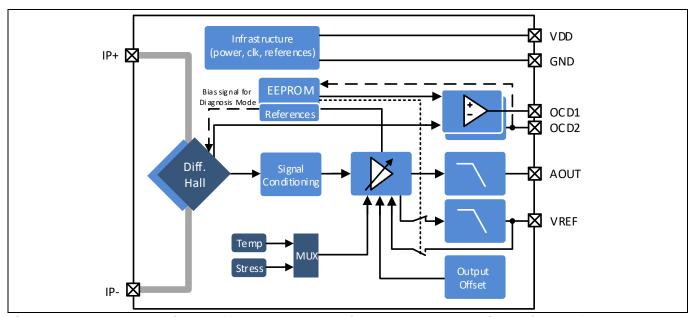

This chapter gives an overview of the programmable content of the current sensor. Figure 13 shows the structure of the EEPROM. The addresses indicated in green are accessible for the user and can be set to according to individual application requirements. All 18 lines of the EEPROM are readable because the CRC calculation has to be done with the complete data content of the EEPROM. The device is doing a cyclic redundancy check (CRC) of the EEPROM content while accessing the EEPROM and indicates an error on the OCD pin in case of a wrong programmed CRC. Therefore, program the CRC according to the EEPROM content. This safety feature protects the sensor to load EEPROM values which are has been programmed unintended. A detailed description of the user accessible content is described in this chapter. The CRC calculation procedure explained in detail at the end of this chapter.

A programming example shows how to use the EEPROM commands to program the sensor to the user needs.

| Address           | 15 | 14        | 13     | 12      | 11      | 10     | 09  | 08 | 07                           | 06 | 05        | 04 | 03 | 02 | 01 | 00 |  |

|-------------------|----|-----------|--------|---------|---------|--------|-----|----|------------------------------|----|-----------|----|----|----|----|----|--|

| 40 <sub>hex</sub> |    | Cı        | istome | er acce | essible | settir | ngs |    | Customer accessible settings |    |           |    |    |    |    |    |  |

| 41 <sub>hex</sub> |    | Cu        | istome | er acce | essible | settir | ngs |    | Customer accessible settings |    |           |    |    |    |    |    |  |

| 42 <sub>hex</sub> |    | Cu        | istome | er acce | essible | settir | ngs |    | Customer accessible CRC      |    |           |    |    |    |    |    |  |

| 43 <sub>hex</sub> |    |           |        | read    | only    |        |     |    | read only                    |    |           |    |    |    |    |    |  |

|                   |    | read only |        |         |         |        |     |    |                              |    | read only |    |    |    |    |    |  |

| 51 <sub>hex</sub> |    |           |        | read    | only    |        |     |    | read only                    |    |           |    |    |    |    |    |  |

Figure 13 EEPROM overview

- The EEPROM consist of 18 lines. Each line consists of 16 bit.

- The lower 8 bits of address 42<sub>hex</sub> are used for the CRC value to protect the EEPROM with a cyclic redundancy check.

# **Programming Guide and User Manual**

### 4.1 **EEPROM Content**

## Table 8 EEPROM (address $40_{hex} - 42_{hex}$ )

| address           | 15                 | 14                    | 13        | 12                       | 11    | 10 | 9                       | 8 | 7    | 6                                 | 5    | 4 | 3                   | 2 | 1 | 0 |

|-------------------|--------------------|-----------------------|-----------|--------------------------|-------|----|-------------------------|---|------|-----------------------------------|------|---|---------------------|---|---|---|

| 40 <sub>hex</sub> | OCD2 <sub>en</sub> | OCD1 <sub>en</sub>    |           | OCD2 <sub>deglitch</sub> |       |    |                         |   | itch | OP                                | mode |   | MEAS <sub>rng</sub> |   |   |   |

| 41 <sub>hex</sub> |                    | OCD2 <sub>thrsh</sub> |           |                          |       |    |                         |   |      | $OCD1_{thrsh}$ $OCD_{comp\_hyst}$ |      |   |                     |   |   |   |

| 42 <sub>hex</sub> | RATIOoff           | RATIO <sub>Gain</sub> | OCD2fonly | QV1V5 <sub>sd</sub>      | Empty | ٧  | VREF <sub>ext</sub> CRC |   |      |                                   |      |   |                     |   |   |   |

Table 9 Functional description Address 40<sub>box</sub>

| Bit field<br>name        | Bit   | Туре | Bit field description                                                                                                                                                                                                                    | Default value |

|--------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| $MEAS_{rng}$             | 4:0   | rw   | The measurement range bits define the sensitivity in mV/A according to Table 4 described in the data sheet Further information are listed in Table 12                                                                                    | xxx0x         |

| $OP_{mode}$              | 6:5   | rw   | The operating mode can be set according to Table 12 The device standard setting is the semi-differential mode                                                                                                                            | 00            |

| $OCD1_{deglitch}$        | 9:7   | rw   | The deglitching time of the over-current channel 1 can be set according to  Table 12. The device standard setting is 0 (no additional delay)                                                                                             | 00            |

| OCD2 <sub>deglitch</sub> | 13:10 | rw   | The deglitching time of the over-current channel 2 can be set according to  Table 12. The device standard setting is 0 (no additional delay)                                                                                             | 00            |

| OCD1 <sub>en</sub>       | 14    | rw   | The over-current detection enable bit 1 activates the over-current functionality of channel 1. If this bit set to zero the OCD pin 1 will not indicate an internal failure or an over-current event. The standard setting is 1 = enabled | 1             |

| OCD2 <sub>en</sub>       | 15    | rw   | The over-current detection enable bit 2 activates the over-current functionality of channel 2. If this bit set to zero the OCD pin 2 will not indicate an internal failure or an over-current event. The standard setting is 1 = enabled | 1             |

Table 10 Functional description Address 41<sub>hex</sub>

| Bit field Bit Type       |       | Туре | Bit field description                                                                                                                                             |        |  |  |  |  |

|--------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| OCD <sub>comp_hyst</sub> | 3:0   | rw   | Over-current detection hysteresis setting. Settings are listed in Table 13                                                                                        | 0x1x   |  |  |  |  |

| OCD1 <sub>thrsh</sub>    | 9:4   | rw   | The threshold level of the over-current detection channel 1 shall be set according to the Full Scale (FS) in Table 12. The OCD settings are described in Table 13 | xxxxxx |  |  |  |  |

| OCD2 <sub>thrsh</sub>    | 15:10 | rw   | The threshold level of the over-current detection channel 2 shall be set according to the Full Scale (FS) in Table 12. The OCD settings are described in Table 13 | xxxxx  |  |  |  |  |

# **Programming Guide and User Manual**

Table 11 Functional description Address 42<sub>hex</sub>

| Bit field<br>name     | Bit field description | Default value |                                                                                                                                                                                                                                                             |     |

|-----------------------|-----------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CRC                   | 7:0                   | rw            | CRC calculation is byte by byte, starting from address $42_{hex}$ . After reaching the end of the EEPROM (address $51_{hex}$ ), the address $40_{hex}$ to $41_{hex}$ are append. The CRC calculation is based on the polynomial $x^8 + x^4 + x^3 + x^2 + 1$ | -   |

| VREF <sub>ext</sub>   | 10:8                  | rw            | The external $V_{\text{REF}}$ bits have to be set according to Table 14 depending on the external applied reference voltage on the $V_{\text{REF}}$ pin. Standard is set to 1.65V                                                                           | 000 |

| Not used              | 11                    | rw            | Not used                                                                                                                                                                                                                                                    | 0   |

| QV1V5 <sub>sd</sub>   | 12                    | rw            | The bit enables the quiescent voltage to 1.5V in semi-differential. Default is 0 (=disabled)                                                                                                                                                                | 0   |

| OCD2f <sub>only</sub> | 13                    | rw            | If the bit is set to one only failure indication is activated at the OCD2 channel. Over current detection is not activated if the bit is set to one.  Default is 0 (= fault signal on both OCDs)                                                            | 0   |

| RATIO <sub>Gain</sub> | 14                    | rw            | If the bit is set, the sensitivity is ratio metric to VDD respective to VREF in single-ended mode. Default is 0 (=disabled)                                                                                                                                 | 0   |

| RATIO <sub>off</sub>  | 15                    | rw            | The ratio-metric offset behavior of the quiescent voltage is activated if the bit is set to one. Default is 0 (=disabled)                                                                                                                                   | 0   |

Table 12 EEPROM bit field description address  $40_{\text{hex}}$

| Bit field name      | Description | n                 |                                                         |  |  |  |  |  |

|---------------------|-------------|-------------------|---------------------------------------------------------|--|--|--|--|--|

| MEAS <sub>rng</sub> | Symbol      | Setting           | Description / Full Scale setting                        |  |  |  |  |  |

|                     | S1          | 05 <sub>hex</sub> | ±120A Full Scale (FS) / 10mV/A                          |  |  |  |  |  |

|                     | S2          | 06 <sub>hex</sub> | ±100A / 12 mV/A                                         |  |  |  |  |  |

|                     | S3          | 08 <sub>hex</sub> | ±75A / 16 mV/A                                          |  |  |  |  |  |

|                     | S4          | 0C <sub>hex</sub> | ±50A / 24 mV/A                                          |  |  |  |  |  |

|                     | <b>S</b> 5  | 10 <sub>hex</sub> | ±37.5A / 32 mV/A                                        |  |  |  |  |  |

|                     | S6          | 18 <sub>hex</sub> | ±25A / 48 mV/A                                          |  |  |  |  |  |

| OP <sub>mode</sub>  | Symbol      | Setting           | Description                                             |  |  |  |  |  |

|                     |             |                   | Semi-differential bidirectional                         |  |  |  |  |  |

|                     | SD bid      | $0_{hex}$         | $V_{OQbid_{-1}}: V_{REF} = V_{DD} / 2$ standard setting |  |  |  |  |  |

|                     |             |                   | $V_{OQbid_2}: V_{REF} = 1.5 (QV1V5 = 1)$                |  |  |  |  |  |

|                     |             | $1_{hex}$         | Fully-differential                                      |  |  |  |  |  |

|                     | FD          |                   | $(V_{OQ} = V_{DD}/2)$ (doubled sensitivity)             |  |  |  |  |  |

|                     | SD uni      | 2 <sub>hex</sub>  | Semi-differential unidirectional                        |  |  |  |  |  |

|                     | JD uili     | ∠hex              | $V_{OQuni}: V_{REF} = V_{DD}/5.5$                       |  |  |  |  |  |

|                     | SE          | 3 <sub>hex</sub>  | Single-ended                                            |  |  |  |  |  |

|                     | JL          |                   | $V_{OQ} = V_{REF} = V_{REF\_ext}$                       |  |  |  |  |  |

| $OCD1_{deglitch}$   | Symbol      | Setting           | Deglitch time in ns                                     |  |  |  |  |  |

|                     | d0          | $0_{hex}$         | 0 / standard setting                                    |  |  |  |  |  |

|                     | d1          | $1_{hex}$         | 500                                                     |  |  |  |  |  |

|                     | d2          | $2_{\text{hex}}$  | 1000                                                    |  |  |  |  |  |

|                     | d3          | $3_{\text{hex}}$  | 1500                                                    |  |  |  |  |  |

|                     | d4          | 4 <sub>hex</sub>  | 2000                                                    |  |  |  |  |  |

|                     | d5          | 5 <sub>hex</sub>  | 2500                                                    |  |  |  |  |  |

|                     | d6          | 6 <sub>hex</sub>  | 3000                                                    |  |  |  |  |  |

|                     | d7          | 7                 | 3500                                                    |  |  |  |  |  |

| Application Note    |             |                   | 22 of 47 V 1                                            |  |  |  |  |  |

# **Programming Guide and User Manual**

| OCD2 <sub>deglitch</sub> | Symbol    | Setting | Deglitch time in ns  |

|--------------------------|-----------|---------|----------------------|

|                          | d0        | 0       | 0 / standard setting |

|                          | d1        | 1       | 500                  |

|                          | d2        | 2       | 1000                 |

|                          | d3        | 3       | 1500                 |

|                          | <u>d4</u> | 4       | 2000                 |

|                          | d5        | 5       | 2500                 |

|                          | d6        | 6       | 3000                 |

|                          | d7        | 7       | 3500                 |

|                          | d8        | 8       | 4000                 |

|                          | d9        | 9       | 4500                 |

|                          | d10       | 10      | 5000                 |

|                          | d11       | 11      | 5500                 |

|                          | d12       | 12      | 6000                 |

|                          | d13       | 13      | 6500                 |

|                          | d14       | 14      | 7000                 |

|                          | d15       | 15      | 7500                 |

Table 13 FFPROM hit field description address 41 hex

| Bit field name           | Description                                                                                        |

|--------------------------|----------------------------------------------------------------------------------------------------|

| OCD <sub>comp_hyst</sub> | Standard setting out of range 0 <sub>hex</sub> F <sub>hex</sub> :                                  |

|                          | <ul> <li>3<sub>hex</sub> for 25A- and 75A-full-scale-variant</li> </ul>                            |

|                          | <ul> <li>6<sub>hex</sub> for 50A- and 120A-full-scale-variant</li> </ul>                           |

|                          | Calculated thresholds for 120A-full-scale-variant:                                                 |

|                          | OCD1 <sub>thresh</sub> = 120 A * 1.25 = 150 A                                                      |

|                          | $OCD1_{rel\_thresh} = OCD1_{thresh} * (1 - (OCD_{comp\_hyst\_setting} / OCD1_{thrsh\_setting})) =$ |

|                          | $= 150 \text{ A} * (1 - (6_{\text{hex}} / 13_{\text{hex}})) = 103 \text{ A}$                       |

|                          | OCD2 <sub>thresh</sub> = 120 A * 0.82 = 98 A                                                       |

|                          | $OCD2_{rel\_thresh} = OCD2_{thresh} * (1 - (OCD_{comp\_hyst\_setting} / OCD2_{thrsh\_setting})) =$ |

|                          | $= 98 \text{ A} * (1 - (6_{\text{hex}} / 1B_{\text{hex}})) = 77 \text{ A}$                         |

|                          | Calculated thresholds for 75A-full-scale-variant:                                                  |

|                          | OCD1 <sub>thresh</sub> = 75 A * 1.25 = 94 A                                                        |

|                          | $OCD1_{rel\_thresh} = 94 \text{ A} * (1 - (3_{hex} / 0A_{hex})) = 66 \text{ A}$                    |

|                          | $OCD2_{thresh} = 75 \text{ A} * 0.82 = 62 \text{ A}$                                               |

|                          | $OCD2_{rel\_thresh} = 62 \text{ A} * (1 - (3_{hex} / 0F_{hex})) = 49 \text{ A}$                    |

|                          | Calculated thresholds for 50A-full-scale-variant:                                                  |

|                          | OCD1 <sub>thresh</sub> = 50 A * 1.25 = 63 A                                                        |

|                          | $OCD1_{rel\_thresh} = 63 A * (1 - (6_{hex} / 14_{hex})) = 44 A$                                    |

|                          | $OCD2_{thresh} = 50 \text{ A} * 0.82 = 41 \text{ A}$                                               |

|                          | $OCD2_{rel\_thresh} = 41 \text{ A} * (1 - (6_{hex} / 1C_{hex})) = 32 \text{ A}$                    |

|                          | Calculated thresholds for 25A-full-scale-variant:                                                  |

|                          | OCD1 <sub>thresh</sub> = 25 A * 1.25 = 31 A                                                        |

|                          | $OCD1_{rel\_thresh} = 31 \text{ A} * (1 - (3_{hex} / 07_{hex})) = 18 \text{ A}$                    |

|                          | OCD2 <sub>thresh</sub> = 25 A * 0.82 = 21 A                                                        |

|                          | $OCD2_{rel\_thresh} = 21 \text{ A} * (1 - (3_{hex} / 0B_{hex})) = 15 \text{ A}$                    |

# **Programming Guide and User Manual**

| OCD1 <sub>thrsh</sub> | Symbol                                      |           |                             |                   | Setting              |                             |                   |                             |  |

|-----------------------|---------------------------------------------|-----------|-----------------------------|-------------------|----------------------|-----------------------------|-------------------|-----------------------------|--|

|                       | level                                       | x FS      | S1                          | S2                | S3                   | S4                          | S5                | S6                          |  |

|                       | I <sub>THR1.1</sub>                         | 1.25      | <b>13</b> hex*)             | 0F <sub>hex</sub> | <b>0A</b> hex*)      | <b>14</b> <sub>hex</sub> *) | $0D_{\text{hex}}$ | <b>07</b> <sub>hex</sub> *) |  |

|                       | I <sub>THR1.2</sub>                         | 1.39      | $16_{\text{hex}}$           | $11_{hex}$        | $0B_{\text{hex}}$    | $17_{\text{hex}}$           | $0F_{\text{hex}}$ | 09 <sub>hex</sub>           |  |

|                       | I <sub>THR1.3</sub>                         | 1.54      | 19 <sub>hex</sub>           | 14 <sub>hex</sub> | $OD_{hex}$           | $1A_{\text{hex}}$           | 12 <sub>hex</sub> | $0A_{hex}$                  |  |

|                       | I <sub>THR1.4</sub>                         | 1.68      | $1C_{\text{hex}}$           | 16 <sub>hex</sub> | $0F_{\text{hex}}$    | $1D_{hex}$                  | 14 <sub>hex</sub> | $0C_{\text{hex}}$           |  |

|                       | I <sub>THR1.5</sub>                         | 1.82      | $1E_{\text{hex}}$           | 18 <sub>hex</sub> | $11_{hex}$           | $20_{\text{hex}}$           | 16 <sub>hex</sub> | $0D_{\text{hex}}$           |  |

|                       | I <sub>THR1.6</sub>                         | 1.96      | $21_{\text{hex}}$           | $1B_{\text{hex}}$ | $12_{\text{hex}}$    | $23_{\text{hex}}$           | 18 <sub>hex</sub> | $0F_{hex}$                  |  |

|                       | I <sub>THR1.7</sub>                         | 2.11      | 24 <sub>hex</sub>           | $1D_{\text{hex}}$ | 14 <sub>hex</sub>    | $26_{\text{hex}}$           | $1B_{\text{hex}}$ | $10_{\text{hex}}$           |  |

|                       | I <sub>THR1.8</sub>                         | 2.25      | $27_{\text{hex}}$           | $1F_{\text{hex}}$ | $16_{\text{hex}}$    | $29_{\text{hex}}$           | $1D_{\text{hex}}$ | 12 <sub>hex</sub>           |  |

|                       | *) Standard setting datecode 2104 and later |           |                             |                   |                      |                             |                   |                             |  |

| OCD2 <sub>thrsh</sub> | Symbol                                      |           | Setting                     |                   |                      |                             |                   |                             |  |

|                       | level                                       | x FS      | S1                          | S2                | S3                   | S4                          | S5                | S6                          |  |

|                       | I <sub>THR2.1</sub>                         | 0.50      | 0E <sub>hex</sub>           | 0B <sub>hex</sub> | 07 <sub>hex</sub>    | 0E <sub>hex</sub>           | 09 <sub>hex</sub> | 04 <sub>hex</sub>           |  |

|                       | I <sub>THR2.2</sub>                         | 0.61      | 13 <sub>hex</sub>           | $0F_{hex}$        | $0A_{hex}$           | 13 <sub>hex</sub>           | 0D <sub>hex</sub> | 06 <sub>hex</sub>           |  |

|                       | I <sub>THR2.3</sub>                         | 0.71      | $17_{\text{hex}}$           | $12_{\text{hex}}$ | $0C_{\text{hex}}$    | 17 <sub>hex</sub>           | $10_{\text{hex}}$ | $08_{\text{hex}}$           |  |

|                       | I <sub>THR2.4</sub>                         | 0.82      | <b>1B</b> <sub>hex</sub> *) | 16 <sub>hex</sub> | OF <sub>hex</sub> *) | <b>1C</b> <sub>hex</sub> *) | 13 <sub>hex</sub> | OB <sub>hex</sub> *)        |  |

|                       | I <sub>THR2.5</sub>                         | 0.93      | 1F <sub>hex</sub>           | 1A <sub>hex</sub> | 12 <sub>hex</sub>    | 21 <sub>hex</sub>           | 17 <sub>hex</sub> | $0D_{hex}$                  |  |

|                       | I <sub>THR2.6</sub>                         | 1.04      | 24 <sub>hex</sub>           | 1D <sub>hex</sub> | 15 <sub>hex</sub>    | 25 <sub>hex</sub>           | 1A <sub>hex</sub> | 0F <sub>hex</sub>           |  |

|                       | I <sub>THR2.7</sub>                         | 1.14      | 28 <sub>hex</sub>           | 21 <sub>hex</sub> | 17 <sub>hex</sub>    | 2A <sub>hex</sub>           | 1D <sub>hex</sub> | 11 <sub>hex</sub>           |  |

|                       | I <sub>THR2.8</sub>                         | 1.25      | $2D_{\text{hex}}$           | 24 <sub>hex</sub> | 1A <sub>hex</sub>    | 2E <sub>hex</sub>           | 21 <sub>hex</sub> | 14 <sub>hex</sub>           |  |

|                       | *) Standard                                 | setting c | latecode 2                  | 104 and l         | ater                 |                             |                   |                             |  |

## Table 14 EEPROM bit field description address 42hex

| Bit field name      | Description |                  |                                                                                    |  |  |  |

|---------------------|-------------|------------------|------------------------------------------------------------------------------------|--|--|--|

| Vref <sub>ext</sub> | Symbol      | Setting          | Description                                                                        |  |  |  |

|                     | 1V65        | 0 <sub>hex</sub> | V <sub>REF_nom</sub> = 1.65 V (±10% if ratiometricity is enabled) standard setting |  |  |  |

|                     | 1V2         | 1 hex            | $V_{REF\_nom} = 1.2 \text{ V } (\pm 10\% \text{ if ratiometricity is enabled})$    |  |  |  |

|                     | 1V5         | 2 hex            | V <sub>REF_nom</sub> = 1.5 V (±10% if ratiometricity is enabled)                   |  |  |  |

|                     | 1V8         | 3 hex            | V <sub>REF_nom</sub> = 1.8 V (±10% if ratiometricity is enabled)                   |  |  |  |

## **Programming Guide and User Manual**

#### 4.2 **Programming Example**

This chapter gives an example how to change the EPPROM content in order to change the sensitivity range of the device. Therefore, the communication interface between the microcontroller and the sensor has to be activated as described in the chapter Serial Inspection and Configuration Interface (SICI).

Table 15 will guide the user through a complete programming sequence by following the listed commands line by line. Figure 12 shows an exemplary sequence to program the EEPROM.

The first command sequence which has to be sent after power up is the enter interface command. Therefore, the power supply of the sensor has to be controlled by the microcontroller to ensure the correct modulation sequence within the defined start up window of the A<sub>OUT</sub> pin. A detailed description on how to enter the interface is described in the chapter Entering communication mode.

After activating the interface the sensors integrated intelligent state machine (ISM) has to be powered down by sending the "power down ISM" command.

To avoid unintended high current consumption during applying the programming voltage at the OCD2 pin, the error indication has to be disabled by writing the disable failure indication command to the device. EEPROM Content

Table 8 gives an overview of the EEPROM content and the composition of the different parameters.

Programming requires two single commands followed by the programming pulse. One sequence is required to program the ones and one sequence to program the zeros into the EEPROM. After this, all digital values are stored in the EEPROM. Figure 12 gives timing and an exemplary description of the programming sequence.

After sending the values to the EEPROM, the program one command has to be sent.

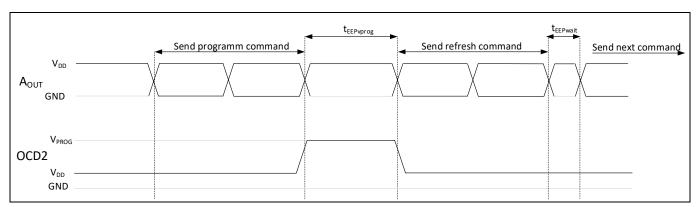

After sending the programming command, the programming voltage shall be applied for telepuprog as seen in Figure 14 and Figure 12.

After t<sub>eepwalt</sub> the refresh command has to be executed.

Then the program zero command shall be sent followed by the programming pulse.

The programming voltage shall be applied again for teepvprog.

Afterwards the refresh command shall be executed or the device shall be powered off and on. Table 15 describes an exemplary programming sequence.

# **Programming Guide and User Manual**

Table 15 EEPROM programming example

| Command name                   | address <sub>hex</sub> | command <sub>hex</sub>                                          | description                                                                                                                                                  |  |  |  |

|--------------------------------|------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Enter Interface                |                        | ABCD <sub>hex</sub>                                             | Enter interface as described in chapter Entering<br>Communication Mode                                                                                       |  |  |  |

| Power down ISM                 | 25 <sub>hex</sub>      | 8250 <sub>hex</sub>                                             | Write command get access to the register by the interface                                                                                                    |  |  |  |

|                                |                        | 8000 <sub>hex</sub>                                             | Set data                                                                                                                                                     |  |  |  |

| Disable failure indication     | 01 <sub>hex</sub>      | 8010 <sub>hex</sub>                                             | Write command                                                                                                                                                |  |  |  |

| Disable failure indication     |                        | 0000 <sub>hex</sub>                                             | Set data                                                                                                                                                     |  |  |  |

| Read all register              |                        |                                                                 | Read data before modifying values to CRC calculation                                                                                                         |  |  |  |

| Read command                   | 40 <sub>hex</sub>      | 0400 <sub>hex</sub>                                             | Read command at EEPROM line 0                                                                                                                                |  |  |  |

| Pood command In 100n0 I        |                        | Read command for address "n"<br>Receive previous addressed data |                                                                                                                                                              |  |  |  |

| Read command 51 <sub>hex</sub> |                        | 0510 <sub>hex</sub>                                             | Address last line in EEPROM<br>Receive previous addressed data                                                                                               |  |  |  |

| NOP                            |                        | FFFF <sub>hex</sub>                                             | Read values from previous address without initializing a new command. The data can also be read with the next write command instead of using the NOP command |  |  |  |

| Write command                  | 40 <sub>hex</sub>      | A400 <sub>hex</sub>                                             | Write command to EEPROM line 0 Access: only set sent zeros                                                                                                   |  |  |  |

| Write data                     |                        | FFF0 <sub>hex</sub>                                             | Write meas <sub>rng</sub> to all zero                                                                                                                        |  |  |  |

|                                | 3E <sub>hex</sub>      | 83E0 <sub>hex</sub>                                             | Write to EEPROM command line                                                                                                                                 |  |  |  |

| EEPROM program zeros           |                        | 024 <b>E</b> <sub>hex</sub>                                     | Set EEPROM command program zeros                                                                                                                             |  |  |  |

|                                | •                      |                                                                 | Applying the programming voltage at OCD2 pin for teepvprog                                                                                                   |  |  |  |

| TERRON we free the             | 3E <sub>hex</sub>      | 83E0 <sub>hex</sub>                                             | Write to EEPROM command line                                                                                                                                 |  |  |  |

| EEPROM refresh                 |                        | 024 <b>C</b> <sub>hex</sub>                                     | Set EEPROM command refresh                                                                                                                                   |  |  |  |

|                                |                        |                                                                 |                                                                                                                                                              |  |  |  |

# **Programming Guide and User Manual**

## Table 15 cont....

| Command name address <sub>hex</sub> command <sub>he</sub> |                   | $command_{hex}$             | description                                                    |  |

|-----------------------------------------------------------|-------------------|-----------------------------|----------------------------------------------------------------|--|

|                                                           |                   |                             | Wait for 100 μs                                                |  |

| Write command                                             | 40 <sub>hex</sub> | B400 <sub>hex</sub>         | Write command to EEPROM line 0 only set sent ones              |  |

| Write data                                                |                   | 0005 <sub>hex</sub>         | Write meas <sub>rng</sub> to 5 (FS = 120A)                     |  |

| FEDDOM                                                    | 3E <sub>hex</sub> | 83E0 <sub>hex</sub>         | Write to EEPROM command line                                   |  |

| EEPROM program ones                                       |                   | 024 <b>F</b> <sub>hex</sub> | Set EEPROM command program ones                                |  |