### Gowin FP Comp IP

### **User Guide**

IPUG1049-1.0E, 05/09/2024

Copyright © 2024 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN** is a trademark of Guangdong Gowin Semiconductor Corporation and is registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date       | Version | Description                |

|------------|---------|----------------------------|

| 05/09/2024 | 1.0E    | Initial version published. |

### **Contents**

| Contents                          | i   |

|-----------------------------------|-----|

| List of Figures                   | ii  |

| List of Tables                    | iii |

| 1 About This Guide                | 1   |

| 1.1 Purpose                       | 1   |

| 1.2 Related Documents             |     |

| 1.3 Terminology and Abbreviations | 2   |

| 1.4 Support and Feedback          | 2   |

| 2 Overview                        | 3   |

| 2.1 Features                      | 3   |

| 2.2 Max. Frequency                | 3   |

| 2.3 Latency                       | 3   |

| 2.4 Resource Utilization          | 4   |

| 3 Functional Description          | 5   |

| 4 Port List                       | 6   |

| 5 Timing Description              | 8   |

| 6 GUI Configuration               | 9   |

| 6.1 IP Generation                 | 9   |

| 6.2 Configuration Interface       |     |

| 7 Reference Design                | 11  |

| 8 File Delivery                   | 12  |

| 8.1 Documentation                 | 12  |

| 8.2 Reference Design              | 12  |

### **List of Figures**

| Figure 4-1 Gowin FP Comp IP IO Port Diagram    | 6  |

|------------------------------------------------|----|

| Figure 5-1 Gowin FP Comp IP Signal Timing      | 8  |

| Figure 6-1 Open GUI Via Icon                   | 9  |

| Figure 6-2 Gowin FP IP Configuration Interface | 10 |

IPUG1049-1.0E

### **List of Tables**

| Table 1-1 Terminology and Abbreviations                  | 2  |

|----------------------------------------------------------|----|

| Table 2-1 Gowin FP Comp IP Overview                      | 3  |

| Table 2-2 Resource Utilization                           | 4  |

| Table 4-1 Gowin FP Comp IP IO Port List                  | 6  |

| Table 8-1 Document List                                  | 12 |

| Table 8-2 Gowin FP Comp IP RefDesign Folder Content List | 12 |

IPUG1049-1.0E ii

1 About This Guide 1.1 Purpose

# 1 About This Guide

#### 1.1 Purpose

The purpose of Gowin FP Comp IP User Guide is to help you learn the features and usage of Gowin FP Comp IP by providing the descriptions of functions, ports, timing, GUI and reference design, etc. The software screenshots and the supported products listed in this manual are based on Gowin Software V1.9.9 Beta-3. As the software is subject to change without notice, some information may not remain relevant and may need to be adjusted according to the software that is in use.

#### 1.2 Related Documents

The latest user guides are available on the GOWINSEMI website. You can find the related documents at <a href="https://www.gowinsemi.com">www.gowinsemi.com</a>:

- DS100, GW1N series of FPGA Products Data Sheet

- DS117, GW1NR series of FPGA Products Data Sheet

- DS821, GW1NS series of FPGA Products Data Sheet

- DS861, GW1NSR series of FPGA Products Data Sheet

- DS102, GW2A series of FPGA Products Data Sheet

- DS226, GW2AR series of FPGA Products Data Sheet

- DS971, GW2AN-18X & 9X Data Sheet

- DS976, GW2AN-55 Data Sheet

- SUG100, Gowin Software User Guide

IPUG1049-1.0E 1(12)

#### 1.3 Terminology and Abbreviations

The terminology and abbreviations used in this manual are as shown in Table 1-1.

**Table 1-1 Terminology and Abbreviations**

| Terminology and Abbreviations | Meaning                 |

|-------------------------------|-------------------------|

| ALU                           | Arithmetic Logical Unit |

| LUT                           | Look-up Table           |

| IP                            | Intellectual Property   |

#### 1.4 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly using the information provided below.

Website: <a href="www.gowinsemi.com">www.gowinsemi.com</a>

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

IPUG1049-1.0E 2(12)

2 Overview 2.1 Features

### **2** Overview

Gowin FP Comp IP is designed to realize integer addition and division operations with less logic resources. Gowin FP Comp IP can compare two single-precision floating-point numbers. This IP supports optional output ports such as A=B, A!=B, A>B, A>=B, A<B, A<=B, and NaN (Not a Number).

Table 2-1 Gowin FP Comp IP Overview

| Gowin FP Comp IP     |                                          |  |

|----------------------|------------------------------------------|--|

| Logic Resource       | See Table 2-2.                           |  |

| Delivered Doc.       |                                          |  |

| Design Files         | Verilog                                  |  |

| Reference Design     | Verilog                                  |  |

| TestBench            | Verilog                                  |  |

| Test and Design Flow |                                          |  |

| Synthesis Software   | GowinSynthesis                           |  |

| Application Software | Gowin Software (V1.9.9.Beta-3 and above) |  |

#### Note!

For the devices supported, you can click <u>here</u> to get the information.

#### 2.1 Features

Supports optional output ports such as A=B, A!=B, A>B, A>=B, A<B, A<=B, and NaN (Not a Number).

### 2.2 Max. Frequency

The max. frequency of Gowin FP Comp IP is mainly determined by speed grade of the selected devices.

#### 2.3 Latency

The latency of Gowin FP Comp IP is determined by the configuration parameters.

IPUG1049-1.0E 3(12)

2 Overview 2.4 Resource Utilization

#### 2.4 Resource Utilization

Gowin FP Comp IP can be implemented by Verilog. Its performance and resource utilization may vary when the design is employed in different devices, or at different densities, speeds, or grades. Taking Gowin GW2A-55 series of FPGA as an instance, the resource utilization is as shown in Table 2-2. For the resource utilization of other devices, please refer to later release information.

**Table 2-2 Resource Utilization**

| Device  | Speed Grade | Resource Name | Resource Utilization |

|---------|-------------|---------------|----------------------|

| GW2A-55 | C8/I7       | Registers     | 5                    |

|         |             | LUTs          | 110                  |

|         |             | ALUs          | 38                   |

|         |             | I/O Buffer    | 13                   |

IPUG1049-1.0E 4(12)

# 3 Functional Description

Gowin FP Comp IP can implement the comparison of two singleprecision floating-point numbers. Users can configure parameters according to their requirements when generating this module.

IPUG1049-1.0E 5(12)

# 4 Port List

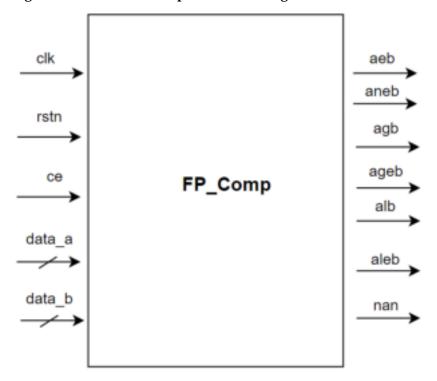

The details of Gowin FP Comp IP IO port are shown in Table 4-1, and the port diagram is as shown in Figure 4-1.

Figure 4-1 Gowin FP Comp IP IO Port Diagram

Table 4-1 Gowin FP Comp IP IO Port List

| Signal | I/O    | Description                                 |

|--------|--------|---------------------------------------------|

| clk    | Input  | Clock signal                                |

| rstn   | Input  | Reset signal, active-low                    |

| ce     | Input  | Clock enable signal, active-high (optional) |

| data_a | Input  | Input a                                     |

| data_b | Input  | Input b                                     |

| aeb    | Output | a=b (optional)                              |

| aneb   | Output | a!=b (optional)                             |

IPUG1049-1.0E 6(12)

| Signal  | I/O    | Description       |

|---------|--------|-------------------|

| agb     | Output | a> b (optional)   |

| ageb    | Output | a> = b (optional) |

| alb     | Output | a< b (optional)   |

| aleb    | Output | a< = b (optional) |

| unorder | Output | NaN (optional)    |

| result  | Output | Output result     |

IPUG1049-1.0E 7(12)

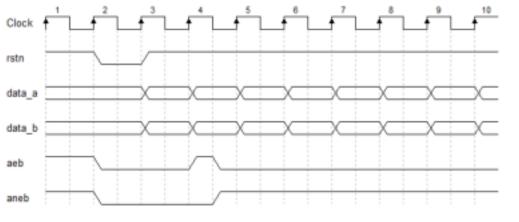

## 5 Timing Description

This section describes the timing of Gowin FP Comp IP. The timing of Gowin FP Comp IP is shown in Figure 5-1.

Figure 5-1 Gowin FP Comp IP Signal Timing

As shown in the figure above, after inputting two single-precision floating-point data, the result of comparison is output with a delay of one clock cycle.

IPUG1049-1.0E 8(12)

6 GUI Configuration 6.1 IP Generation

# 6 GUI Configuration

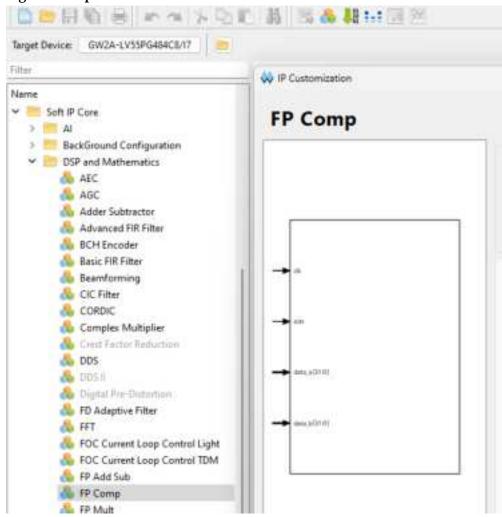

#### 6.1 IP Generation

Click "Tools > IP Core Generator > DSP and Mathematics" to call and configure FP Comp; toolbar icon is also available to open the IP as shown in Figure 6-1.

Figure 6-1 Open GUI Via Icon

IPUG1049-1.0E 9(12)

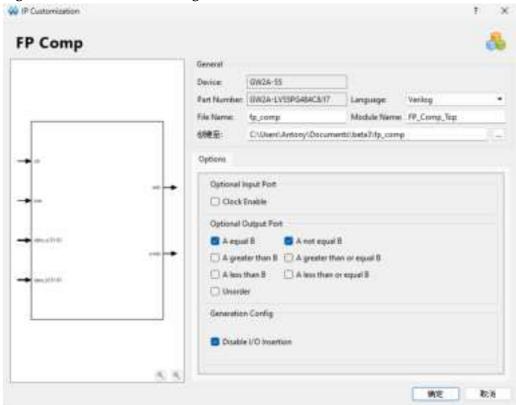

#### **6.2 Configuration Interface**

Gowin FP Comp IP configuration interface is shown in Figure 6-2.

Figure 6-2 Gowin FP IP Configuration Interface

This manual takes GW2A-55 chip and GW2A-LV55PG484C8/I7 part number as an example.

- You can configure the path of generated IP core folder in the "Create In" text box.

- You can configure the generated IP file name in the "File Name" text box.

- You can configure the generated IP module name in the "Module Name" text box.

IPUG1049-1.0E 10(12)

# **7** Reference Design

Please see Gowin FP Comp IP Reference Design for details at Gowinsemi website.

IPUG1049-1.0E 11(12)

8 File Delivery 8.1 Documentation

## **8** File Delivery

The delivery file of Gowin FP Comp IP includes documentation and reference design.

#### 8.1 Documentation

The folder mainly contains the user guide in PDF version.

**Table 8-1 Document List**

| Name                                     | Description                                  |

|------------------------------------------|----------------------------------------------|

| IPUG1049, Gowin FP Comp IP User<br>Guide | Gowin FP Comp IP User Guide, namely this one |

### 8.2 Reference Design

Gowin FP Comp IP RefDesign folder contains the netlist file, user reference design, constraints file, top-level file, and project file, etc.

Table 8-2 Gowin FP Comp IP RefDesign Folder Content List

| Name        | Description                                   |

|-------------|-----------------------------------------------|

| top.v       | The top module of reference design            |

| FP_Comp.cst | Project physical constraints file             |

| FP_Comp.sdc | Project timing constraints file               |

| FP_Comp.rao | Online logic analyzer file                    |

| fp_comp.v   | Generate FP Comp IP top-level file, encrypted |

IPUG1049-1.0E 12(12)