### **IoT Security**

Using IoT Security Features

**Getting Started**

IoT Endpoint Security Fundamentals

Introduction

Overview

No Universal Passwords

Secured Interfaces

Proven Cryptography

Security by Default

Signed Software Updates

**Automatically Applied Updates**

Vulnerability Reporting Program

Security Expiration Date

Next Steps

Series 2 Device Security Features

Developer's Guide

Overview

Series 2 Secure Debug

Introduction

Series 2 Device Security Features

Introduction To Secure Debug

Secure Engine Subsystem

Debug Lock

Debug Unlock

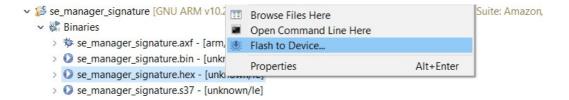

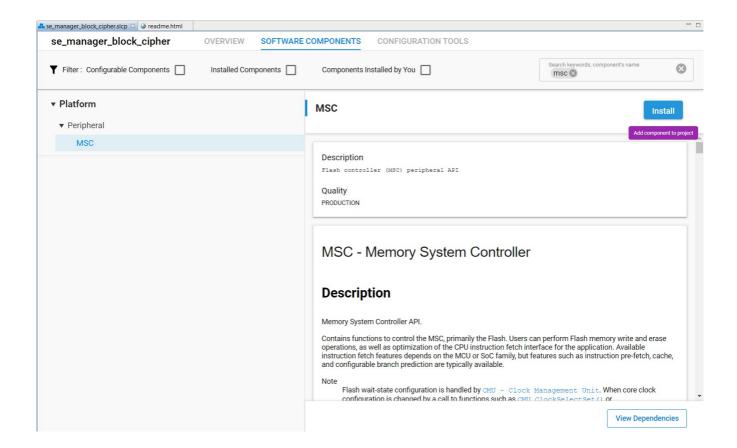

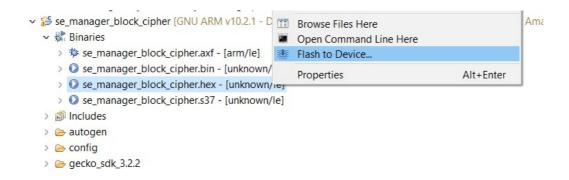

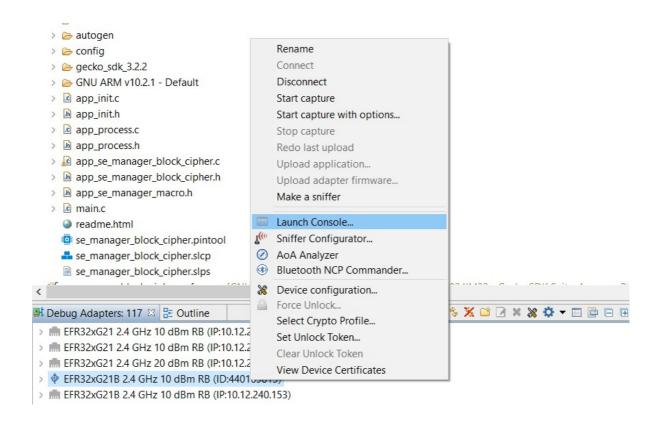

**Examples**

Precautions

Failure Analysis

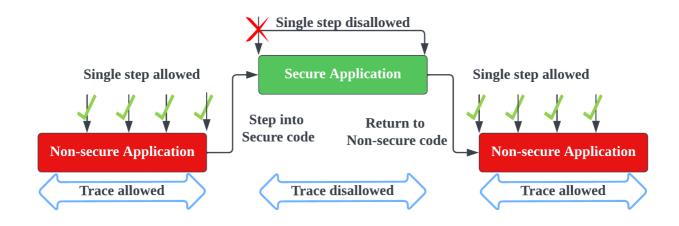

Series 2 TrustZone

Introduction

Series 2 Device Security Features

TrustZone Basics

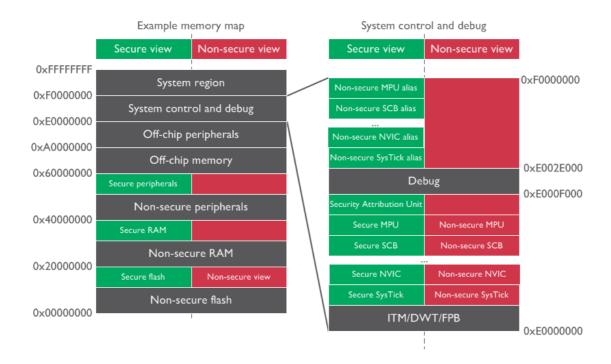

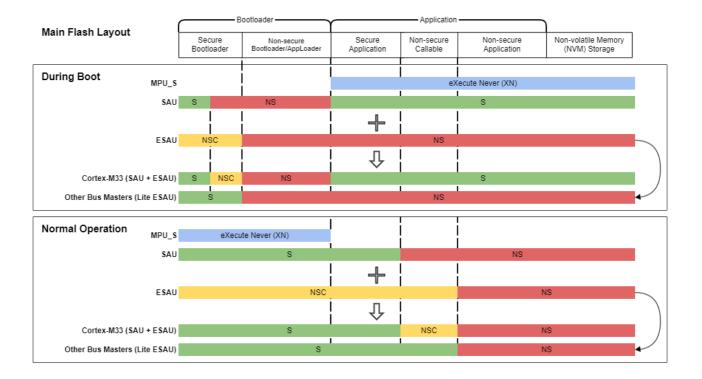

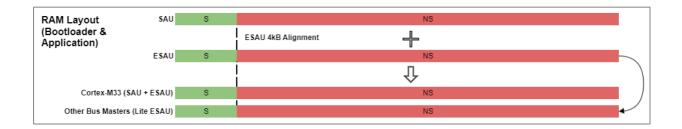

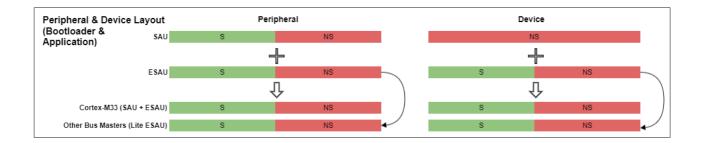

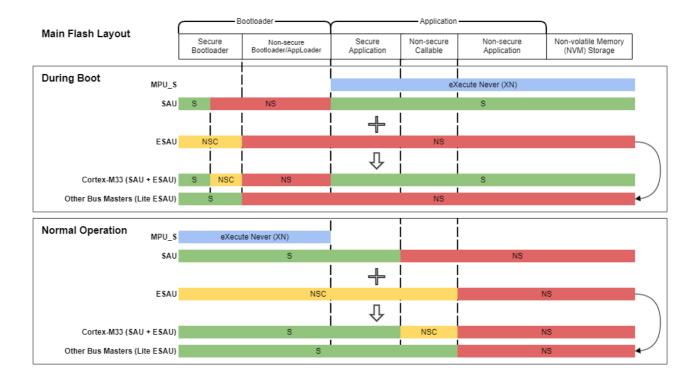

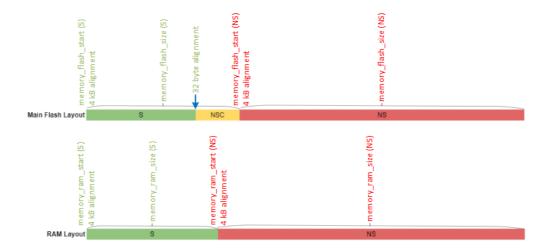

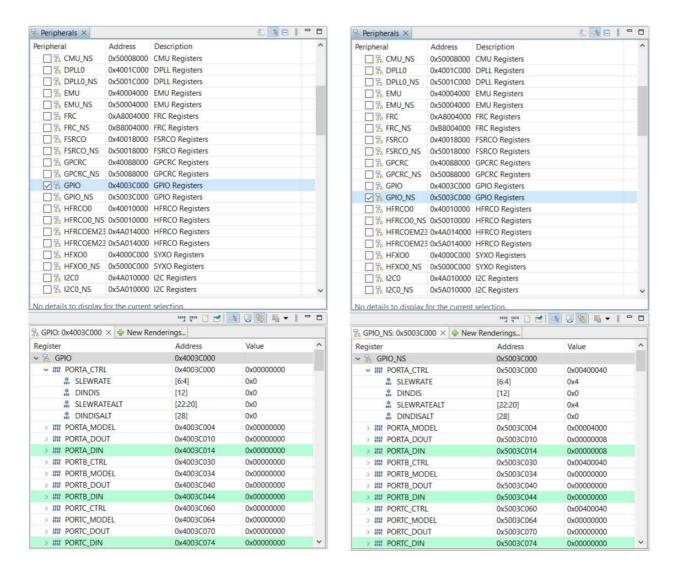

Bus Level Security (BLS)

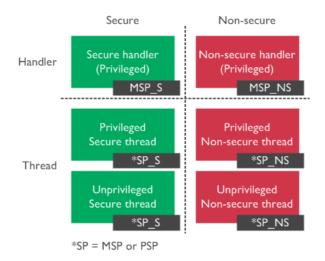

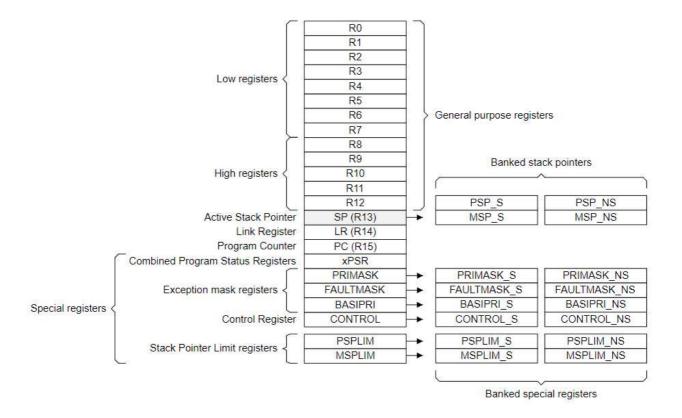

Secure And Privileged Programming Model

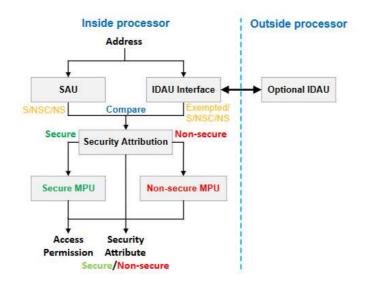

TrustZone Implementation

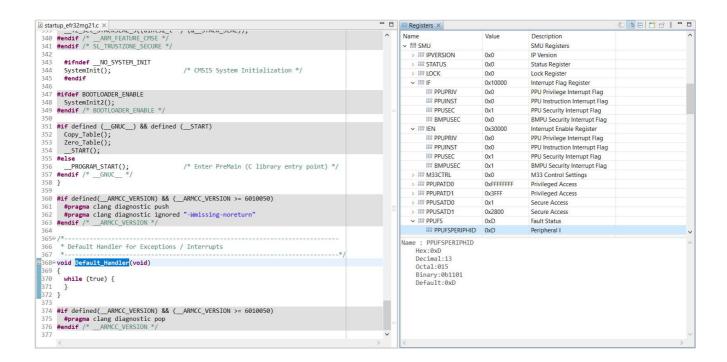

Upgrade Existing Application To TrustZone

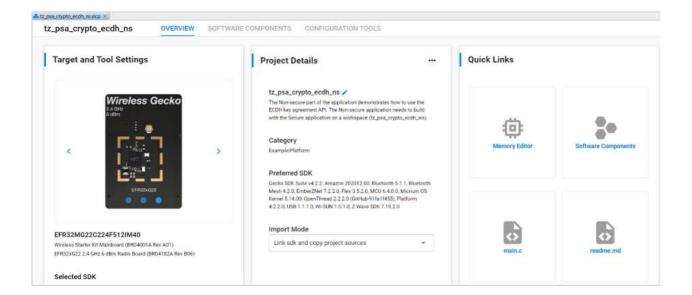

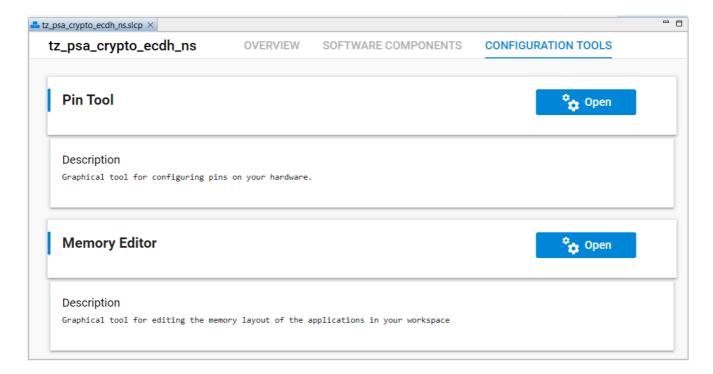

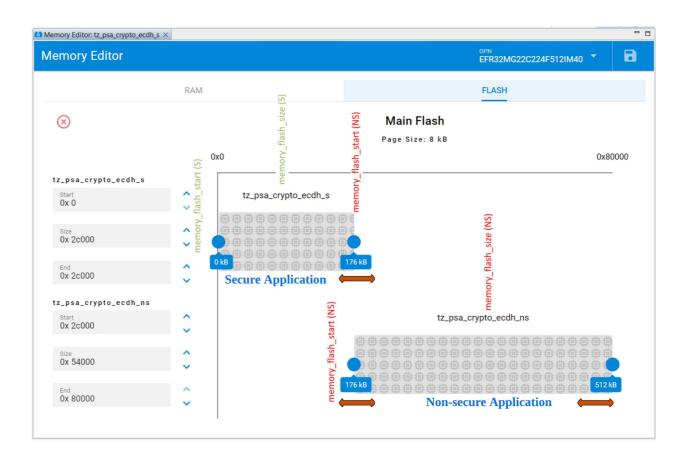

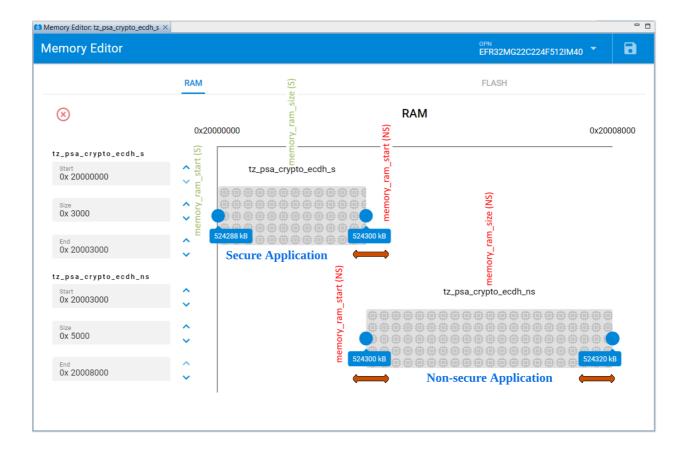

TrustZone Platform Examples

Production Programming of Series 2 Devices (PDF)

Anti-Tamper Protection Configuration and Use

Overview

Series 2 Device Security Features

Introduction

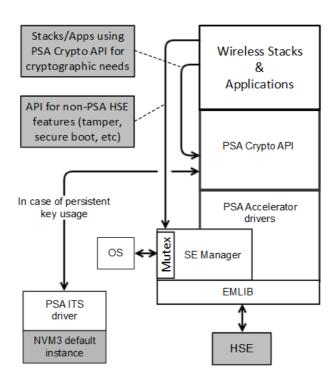

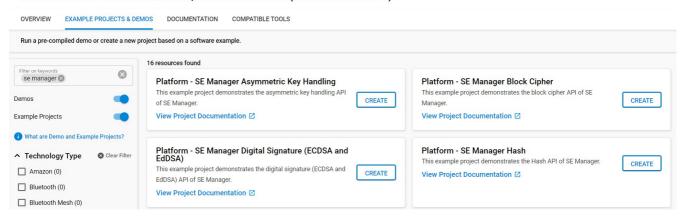

Secure Engine Manager

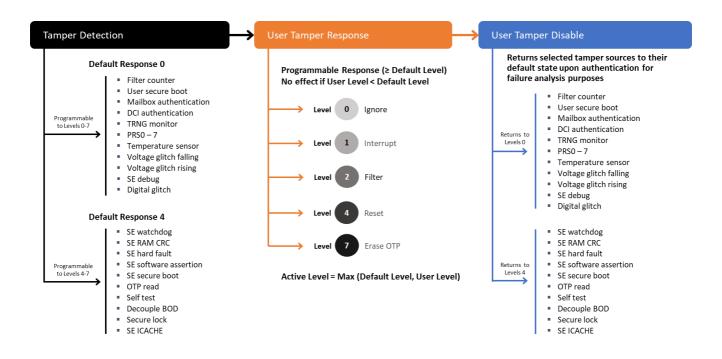

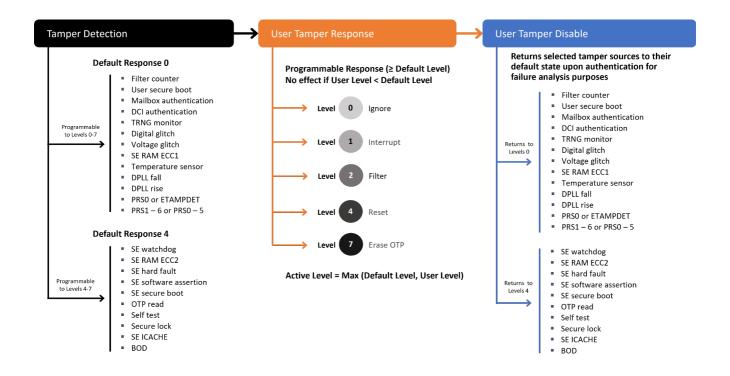

**Tamper Responses**

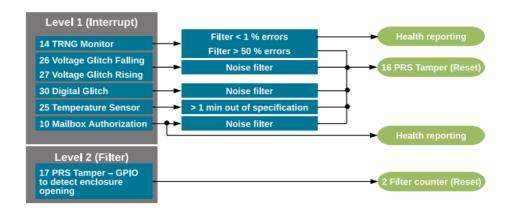

**Tamper Sources**

**Anti-Tamper Configuration**

**Usage Example**

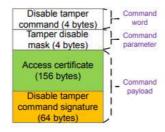

**Tamper Disable**

Examples

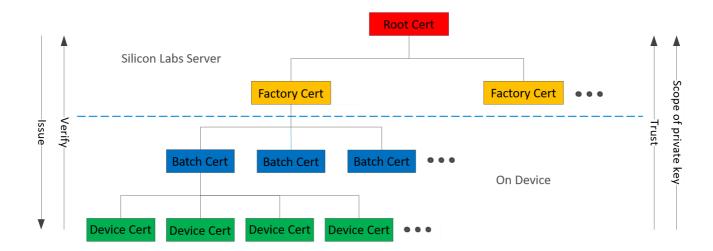

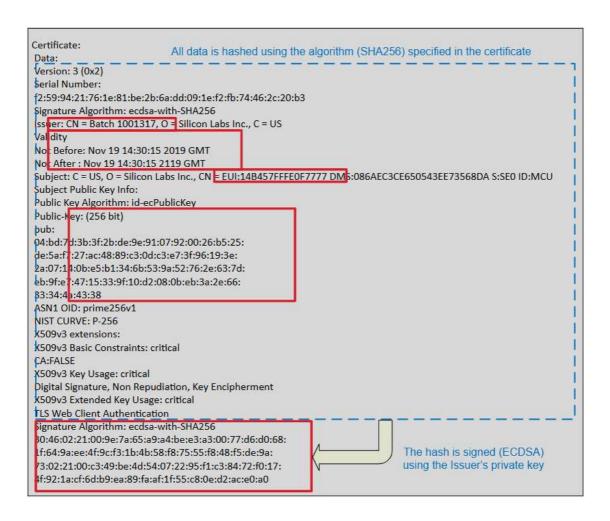

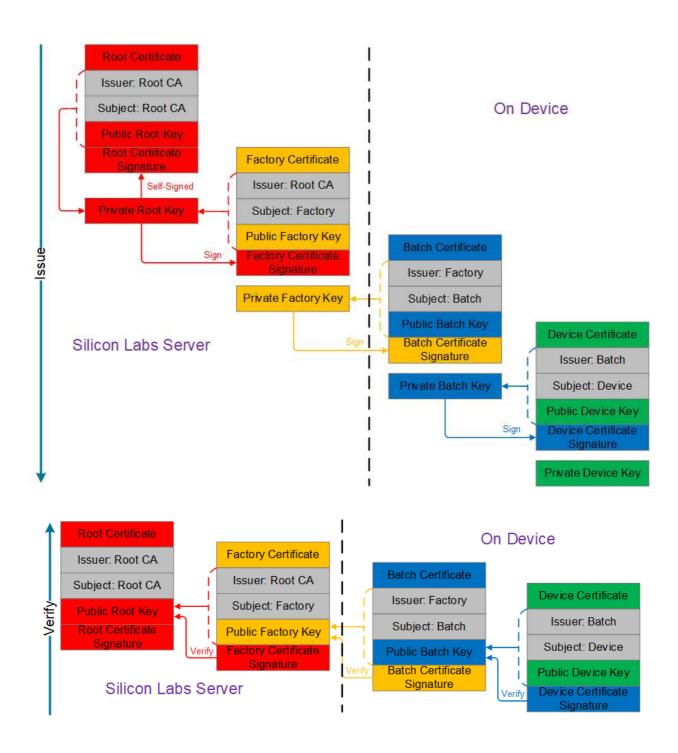

Authenticating Silicon Labs Devices using Device Certificates

Overview

Series 2 Device Security Features

Introduction

Secure Identification on HSE-SVH Devices

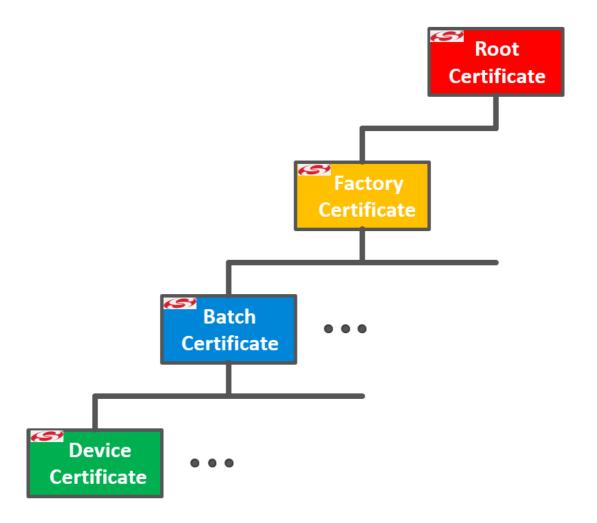

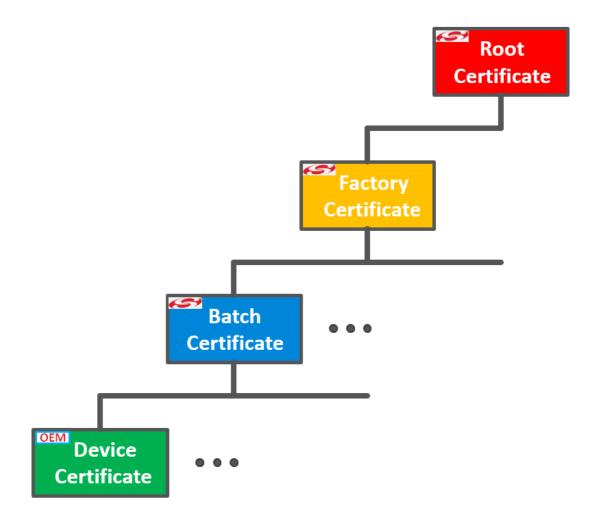

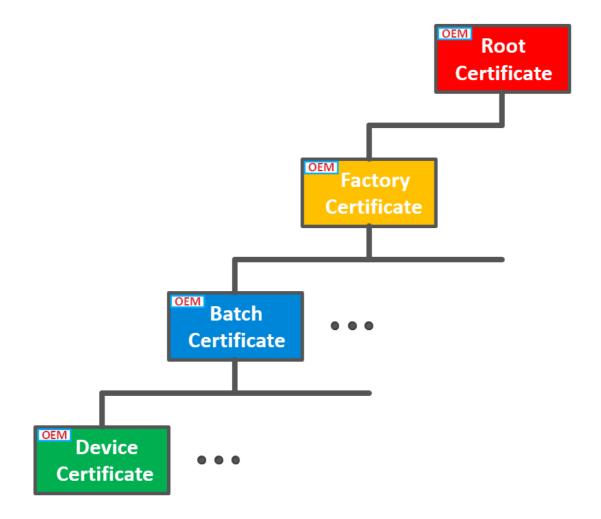

**Device Certificate Options**

Entity Attestation Token (EAT)

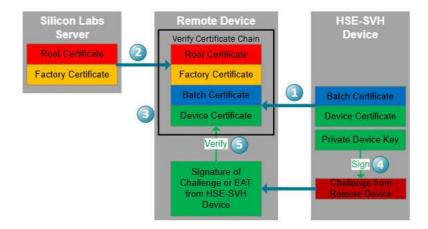

Remote Authentication Process

Secure Engine Manager

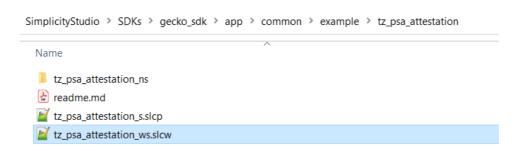

Examples

Secure Key Storage

Overview

Series 2 Device Security Features

Introduction

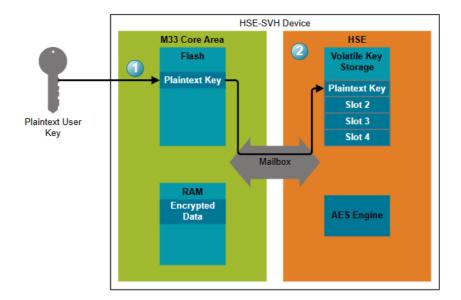

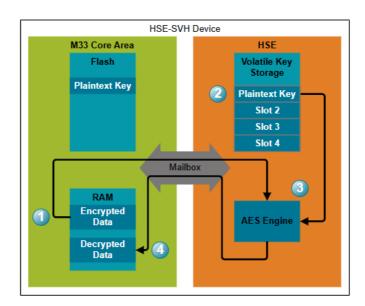

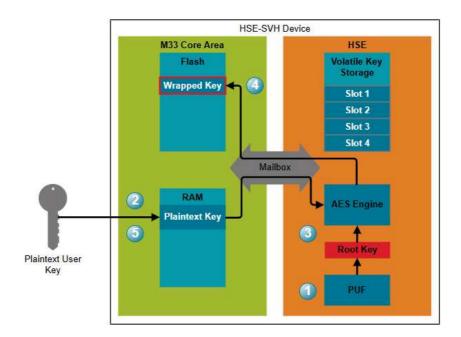

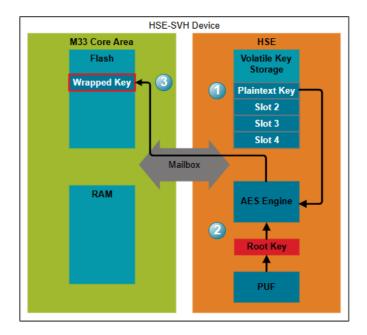

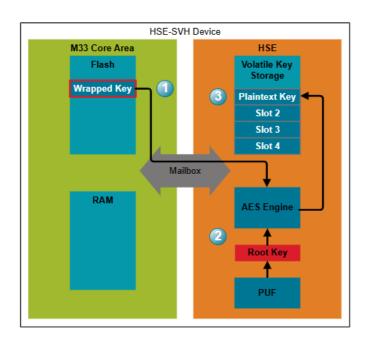

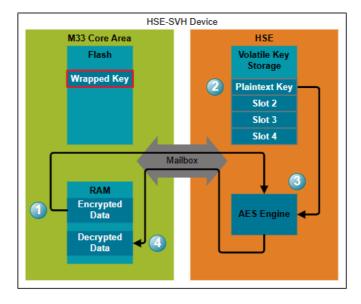

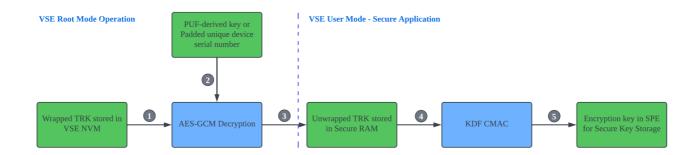

**HSE Secure Key Storage**

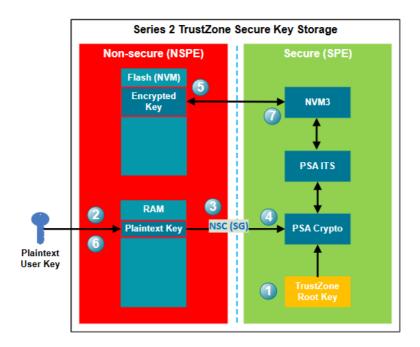

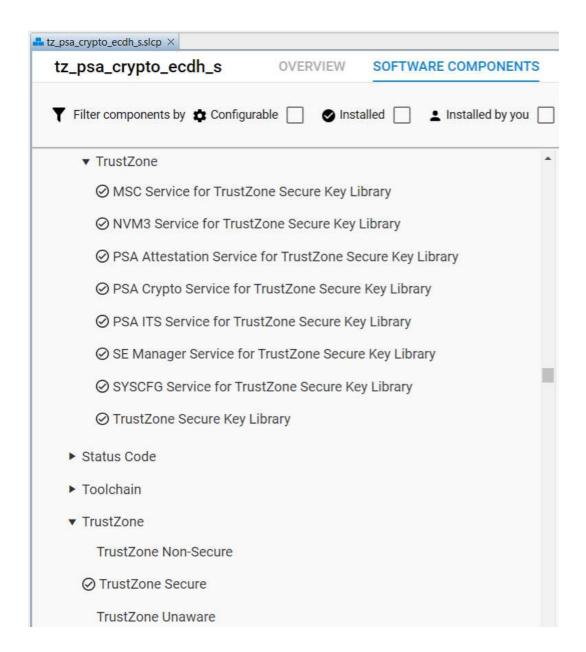

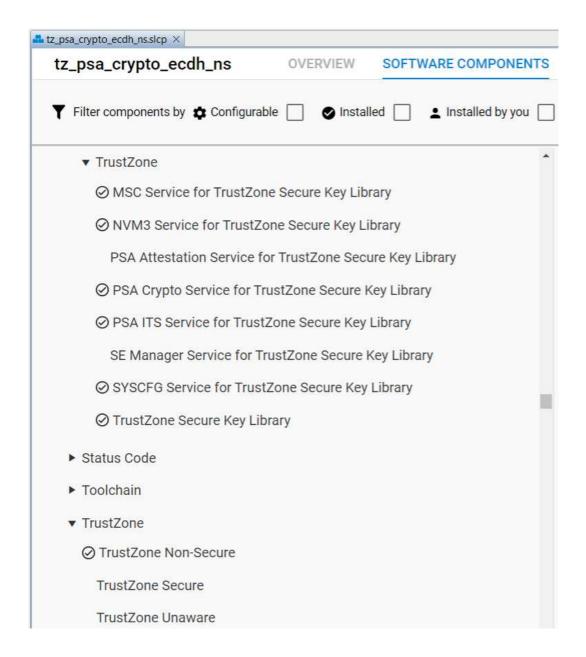

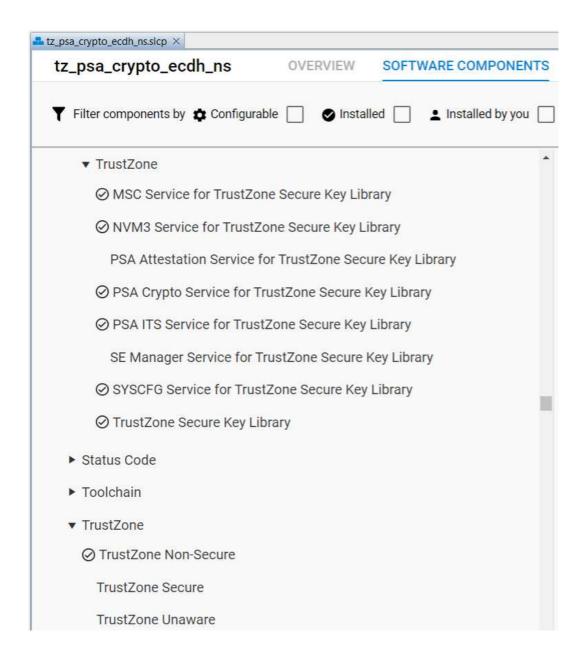

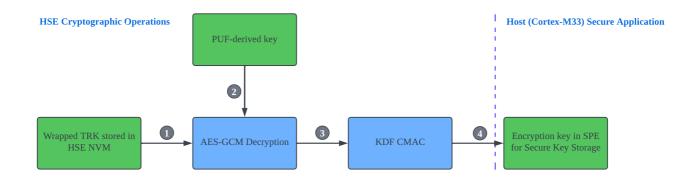

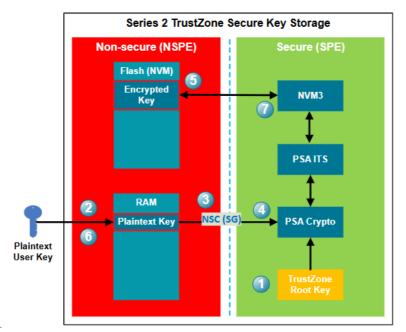

TrustZone Secure Key Storage

Secure Key Storage Implementations

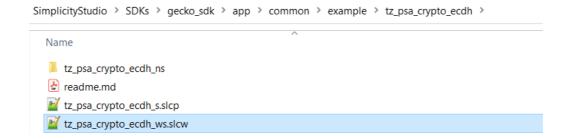

Examples

Programming Series 2 Devices Using the DCI and SWD (PDF)

Integrating Crypto Functionality with PSA Crypto vs. Mbed TLS (PDF)

Protocol-Specific Information

**Production Guide**

Overview

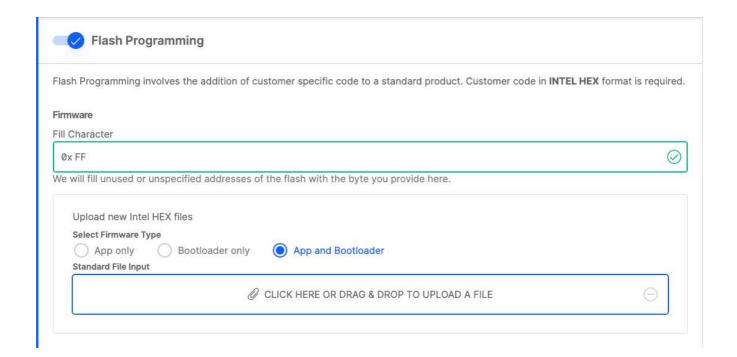

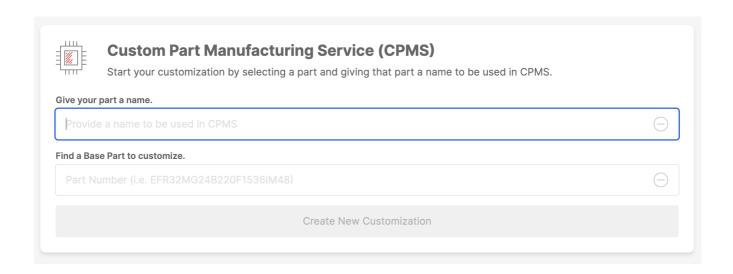

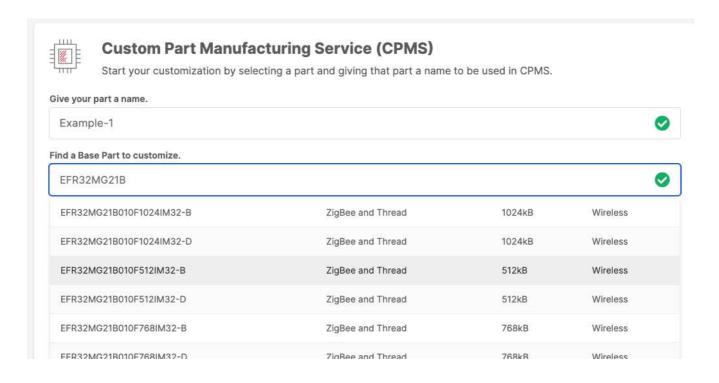

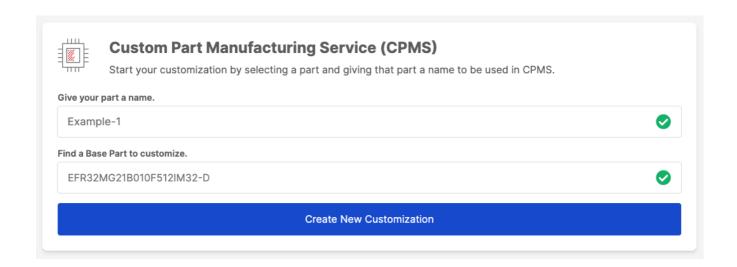

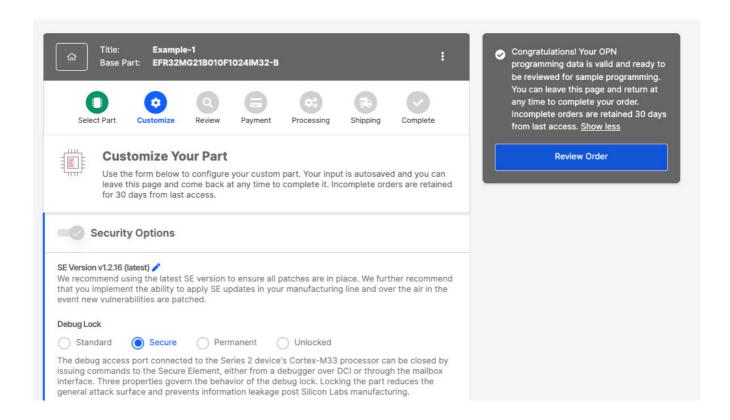

Custom Part Manufacturing Service

Overview

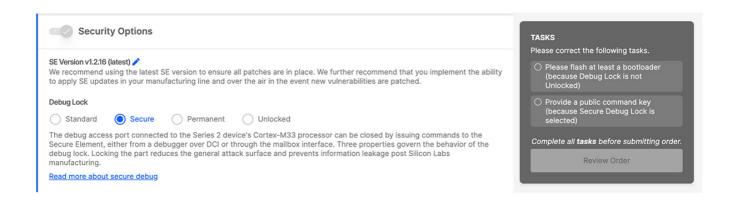

SE Firmware Version

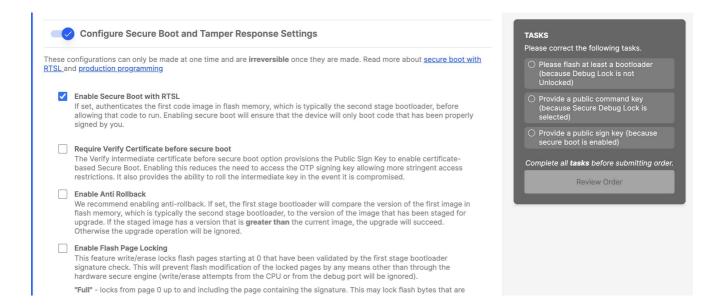

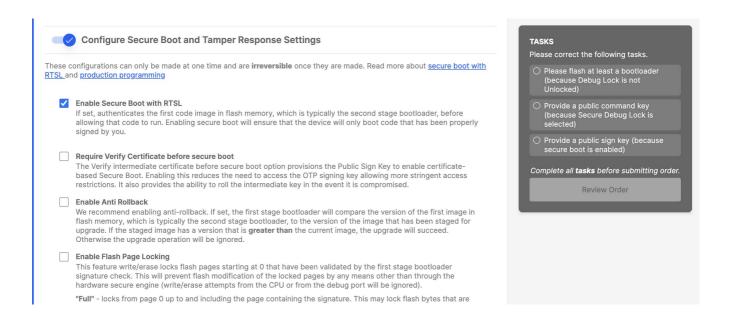

**Debug Lock Settings**

Secure Boot with RTSL Settings

**Tamper Response**

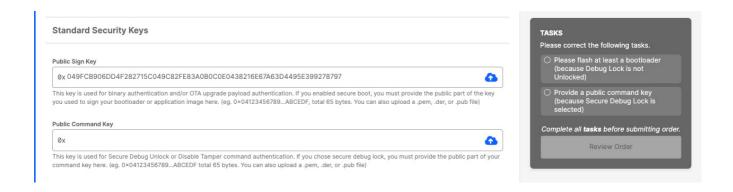

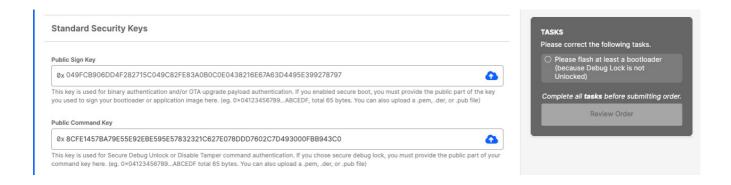

Standard Security Keys

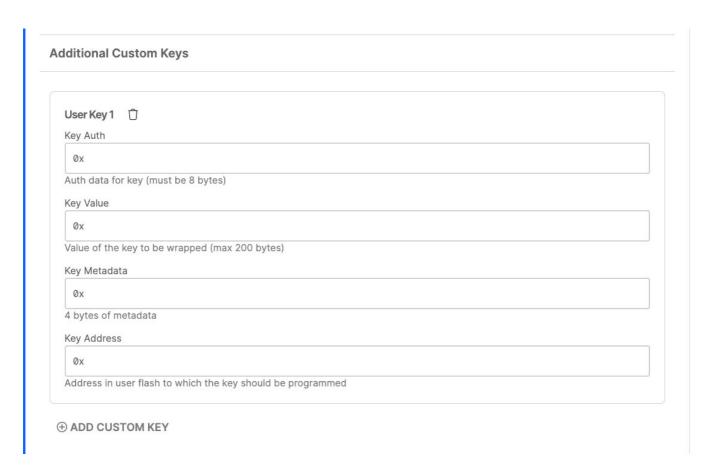

Additional Custom Keys

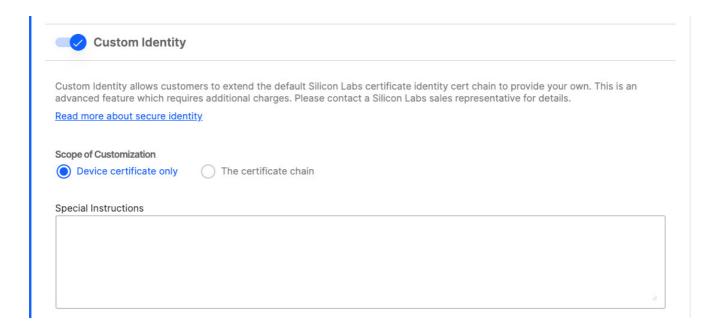

**Custom Certificates**

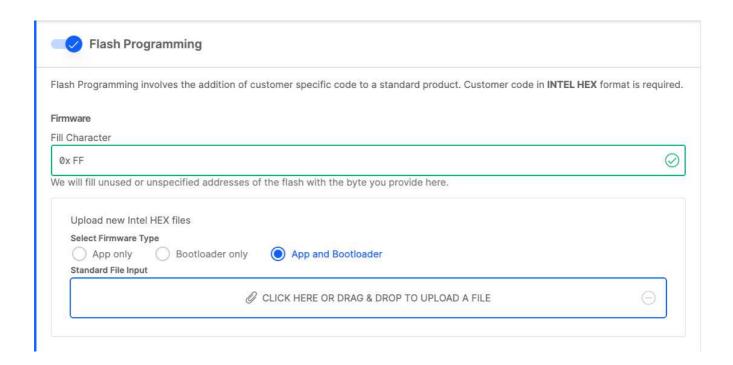

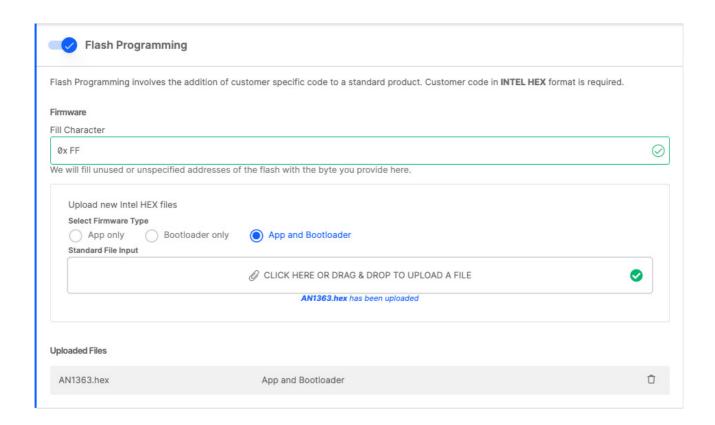

Configure Device for Untrusted Environment Example

Import Custom Wrapped Keys Example

### PKI Recommendations

### **Using IoT Security Features**

# Using Silicon Labs IoT Security Features

Silicon Labs offers a range of security features depending on the part you are using and your application and production needs.

The content on these pages is intended for those who want to implement security features as part of your IoT device management. If you are looking for an introduction to Silicon Labs Security features and to security issues that confront those implementing IoT systems, see the Silabs.com Security page.

For details about this release: Links to release notes are available on the silabs.com Gecko SDK page as part of the Gecko Platform release notes.

For background on security issues in general: IoT Security Fundamentals explains some security basics.

To get started with implementing security: See the Getting Started page for help determining what features you want to implement based on the series 2 part you are working with. Series 2 devices are the preferred choice for secure system implementation.

If you are already in development: See the Developer's Guide for details. Security APIs are documented in the Gecko Platform API Reference.

For detailed information about implementing some security features with specific protocols: See the protocol-specific pages. An extensive body of other protocol-specific content can be accessed through the docs.silabs.com homepage.

### **Getting Started**

# Getting Started with Silicon Labs IoT Security Features on Series 2 Devices

Protecting IoT devices against security threats is central to a quality product. Silicon Labs offers several security options to help developers build secure devices, secure application software, and secure paths of communication to manage those devices. Silicon Labs' security offerings were significantly enhanced by the introduction of the Series 2 products that included a Secure Engine. The Secure Engine is a tamper-resistant component used to securely store sensitive data and keys, and to execute cryptographic functions and secure services.

On Series 1 devices, the security features are implemented by the TRNG (if available) and CRYPTO peripherals.

On Series 2 devices, the security features are implemented by the Secure Engine and CRYPTOACC (if available). The Secure Engine may be hardware-based or virtual (software-based). Here the following abbreviations are used:

- HSE Hardware Secure Engine

- VSE Virtual Secure Engine

- SE Secure Engine (either HSE or VSE)

Additional security features are provided by Secure Vault. Three levels of Secure Vault feature support are available, depending on the part and SE implementation, as reflected in the following table:

| Security Level (1)         | SE Support            | MCU                                                                       | Wireless SoC (2)                             |

|----------------------------|-----------------------|---------------------------------------------------------------------------|----------------------------------------------|

| Secure Vault<br>Base (SVB) | N/A                   | EFM32JG1, EFM32PG1, EFM32JG12, EFM32PG12, EFM32GG11, EFM32GG12, EFM32TG11 | EFR32xG1, EFR32xG12,<br>EFR32xG13, EFR32xG14 |

| Secure Vault<br>Mid (SVM)  | VSE (VSE-<br>SVM)     | EFM32PG22                                                                 | EFR32xG22                                    |

| п                          | HSE (HSE-<br>SVM)     | EFM32PG23A                                                                | EFR32xG21A, EFR32xG23A,<br>EFR32xG24A        |

| Secure Vault<br>High (SVH) | HSE only<br>(HSE-SVH) | EFM32PG23B                                                                | EFR32xG21B, EFR32xG23B,<br>EFR32xG24B        |

#### Note:

- 1. The features of different Secure Vault levels can be found in https://www.silabs.com/security.

- 2. The x is a letter B, F, M, or Z.

Secure Vault Mid consists of two core security functions:

- Secure Boot: Process where the initial boot phase is executed from an immutable memory (such as ROM) and where code is authenticated before being authorized for execution.

- Secure Debug access control: The ability to lock access to the debug ports for operational security, and to securely unlock them when access is required by an authorized entity.

Secure Vault High offers additional security options:

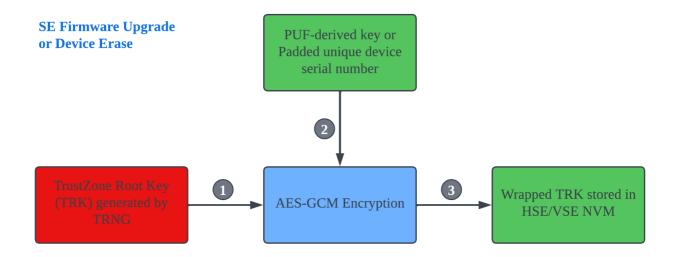

- Secure Key Storage: Protects cryptographic keys by "wrapping" or encrypting the keys using a root key known only to the HSE-SVH.

- Anti-Tamper protection: A configurable module to protect the device against tamper attacks.

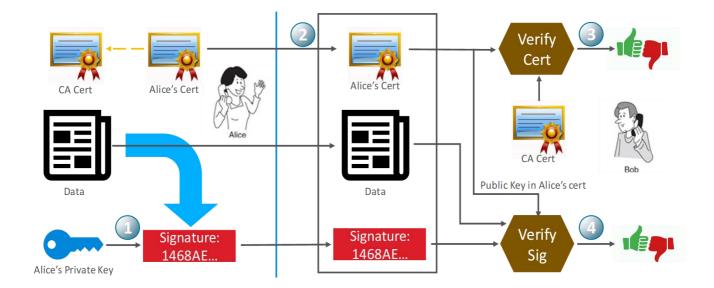

- Device authentication: Functionality that uses a secure device identity certificate along with digital signatures to verify the source or target of device communications.

A Secure Engine Manager and other tools allow users to configure and control their devices both in-house during testing and manufacturing, and after the device is in the field.

Silicon Labs strongly recommends installing the latest SE firmware on Series 2 devices to support the required security features. The latest SE firmware image (.seu and .hex) and release notes can be found in these Windows folders of the GSDK.

C:\Users\<UserName>\SimplicityStudio\SDKs\gecko\_sdk\util\se\_release\public

If you have not already installed the GSDK, instructions for doing so with Simplicity Studio are available in the Getting Started section of the Simplicity Studio 5 User's Guide.

Refer to AN1222: Production Programming of Series 2 Devices for guidance on the SE firmware upgrade procedure. The latest SE firmware shipped with Series 2 devices and modules (if available) at the time of this writing are listed in the following table:

| MCU Series 2 and Wireless SoC Series 2 | SE      | Shipped SE Firmware Version (Device and Module) |

|----------------------------------------|---------|-------------------------------------------------|

| EFR32xG21A                             | HSE-SVM | 1.2.13                                          |

| EFM32PG23A                             | HSE-SVM | 2.1.7                                           |

| EFR32xG23A                             | HSE-SVM | 2.1.2 (Rev B), 2.1.7 (Rev C)                    |

| EFR32xG24A                             | HSE-SVM | 2.1.7                                           |

| EFR32xG21B                             | HSE-SVH | 1.2.13                                          |

| EFM32PG23B                             | HSE-SVH | 2.1.7                                           |

| EFR32xG23B                             | HSE-SVH | 2.1.2 (Rev B), 2.1.7 (Rev C)                    |

| EFR32xG24B                             | HSE-SVH | 2.1.7                                           |

| EFM32PG22 and EFR32xG22                | VSE-SVM | 1.2.12                                          |

In support of these products Silicon Labs offers whitepapers, webinars, and documentation. The following table summarizes the key security documents:

| Document                                                                                                   | Summary                                                                                                                                                                                                                               | Applicability            |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Series 2 Secure Debug                                                                                      | How to lock and unlock Series 2 debug access, including background information about the Secure Engine                                                                                                                                | Series 2                 |

| Series 2 Secure Boot with RTSL                                                                             | Describes the secure boot process on Series 2 devices using Secure Engine. For information on bootloading with Silicon Labs products, see Silicon Labs Gecko Bootloader User's Guide for GSDK 4.0 and Higher (series 1 and 2 devices) | Series 2                 |

| Anti-Tamper Protection Configuration and Use                                                               | How to program, provision, and configure the anti-tamper module                                                                                                                                                                       | Series 2<br>with SVH     |

| Authenticating Silicon Labs Devices using Device Certificates                                              | How to authenticate a device using secure device certificates and signatures, at any time during the life of the product                                                                                                              | Series 2<br>with SVH     |

| Secure Key Storage                                                                                         | How to securely "wrap" keys so they can be stored in non-volatile storage                                                                                                                                                             | Series 2<br>with SVH     |

| AN1222: Production Programming of Series 2 Devices                                                         | How to program, provision, and configure security information using Secure Engine during device production                                                                                                                            | Series 2                 |

| AN1303: Programming Series 2 Devices Using the Debug Challenge Interface (DCI) and Serial Wire Debug (SWD) | How to provision and configure Series 2 devices through the DCI and how to program their internal flash memory through the SWD                                                                                                        | Series 2                 |

| AN1311: Integrating Crypto<br>Functionality Using PSA Crypto<br>Compared to Mbed TLS                       | How to integrate crypto functionality into applications using Silicon<br>Labs implementation of PSA Crypto compared to Mbed TLS                                                                                                       | Series 1 and<br>Series 2 |

### **IoT Endpoint Security Fundamentals**

# IoT Endpoint Security Fundamentals

NOTE: This section replaces *UG103.05*: *IoT Endpoint Security Fundamentals*. Further updates to this user guide will be provided here.

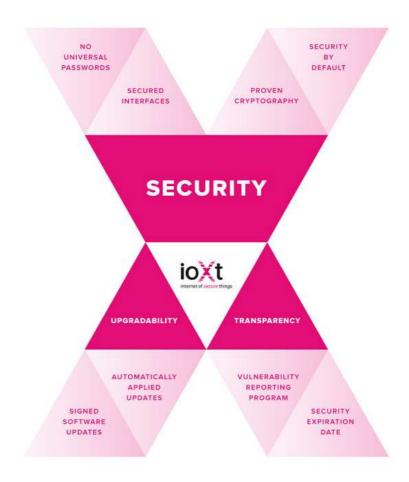

This guide introduces the security concepts that must be considered when implementing an Internet of Things (IoT) system. Using the ioXt Alliance's eight security principles as a structure, this guide clearly delineates the solutions Silicon Labs provides to support endpoint security and what you must do outside of the Silicon Labs framework. Where appropriate, Silicon Labs' approach to our own security is offered as an example. This guide is designed for product developers and managers.

Silicon Labs' Fundamentals series covers topics that project managers, application designers, and developers should understand before beginning to work on an embedded networking solution using Silicon Labs chips, networking stacks such as EmberZNet PRO or Silicon Labs Bluetooth, and associated development tools. These guides can be used as a starting place for anyone needing an introduction to developing wireless networking applications, or who is new to the Silicon Labs development environment.

### **Overview**

# Overview

Securing the IoT is challenging. It is also mission-critical. Threats are continuously evolving, and the demand on product developers to keep up can be burdensome – particularly in low-cost, resource-constrained IoT products. Protecting your product in a connected world is a necessity, as customer data and modern online business models are increasingly targets for costly hacks that jeopardize end-user privacy and corporate brand damage. Silicon Labs is committed to working with the security community, customers, and other experts to bring state-of-the-art technology to help protect your connected portfolio.

Silicon Labs is a member of the ioXt (Internet of Secure Things) Alliance. The ioXt Alliance was formed to bring together wireless carriers, leading consumer product manufacturers, standards groups, compliance labs and government organizations to align baseline security requirements, to set the stage for testing and compatibility certification, and to work together building global standards for the IoT world.

The ioXt alliance has produced the ioXt Security Pledge (https://www.ioxtalliance.org/s/ioXt-SecurityPledge-booklet-final.pdf) The pledge covers eight principles in the areas of Security, Upgradability, and Transparency. Silicon Labs has adopted these principles in our own operations as well as in the products we provide. Our approach to these principles is described in this document.

The above image and all pledge language is reproduced from *The ioXt Security Pledge: 8 Principles for Consumer Product Design and Manufacturing to Ensure Security, Upgradability & Transparency (2019).*

### No Universal Passwords

# No Universal Passwords

The product shall not have a universal password; unique security credentials will be required for operation. Universal passwords allow an attacker to easily gain access to any device. Therefore, products shall either have a unique password or require the user to enter a new password immediately upon first use.

It is your responsibility to ensure that your product enforces the creation of a unique password before activation.

Silicon Labs' products are designed to be configured by the manufacturer before being delivered to customers, and therefore passwords are outside of our scope. However, Silicon Labs tools are designed to support the various levels of security provided by the protocol in question. Most protocols offer different security levels, with tradeoffs between security level and other features such as ease of network formation. You need to review and decide on the level required by your application. For example:

- The EmberZNet Pro SDK supports a highly secure centralized trust-center-controlled method that replaces a device's factory-programmed link key with a key that is unique to each device on the network.

- Z-Wave 700 products come with a factory-programmed unique S2 keypair on first power-up, and support SmartStart commissioning through a package QR code containing the public key.

- Bluetooth options range from an unsecured "Just Works" approach to a LE Secure Connections Pairing model. Application designers can implement additional device authentication methods, such as through the companion smartphone app, to help ensure secure pairing even for devices without a user interface.

### **Secured Interfaces**

# Secured Interfaces

All product interfaces shall be appropriately secured by the manufacturer.

The interfaces to be secured will vary by product configuration. For example, in an NCP topology the NCP interface must be secured. Debug interfaces should always be locked. Wireless interfaces should be secured by using strong pairing and commissioning methods and by enabling encrypted and authenticated transmissions.

While securing the interfaces is in the end your responsibility, Silicon Labs provides the tools to enable that security.

Both Series 1 and Series 2 devices are designed to support securing debug access. For Series 1 devices, that functionality is provided through writing a Debug Lock word to the device. Unlocking the device erases the main application and the key material stored in the Lockbits page. For Series 2 devices, securing debug access is done through the device's Secure Engine. Both allow the developer to lock the debug port itself. See Silicon Labs Gecko Bootloader User's Guide for Series 3 and Higher, Silicon Labs Gecko Bootloader User's Guide for GSDK 4.0 and Higher (series 1 and 2 devices), or *UG266:* Silicon Labs Gecko Bootloader User's Guide for GSDK 3.2 and Lower for an overview of securing debug access, and Series 2 Secure Debug for details on the Series 2 implementation. *UG104: Testing and Debugging Applications for the Silicon Labs EFR32MG Platforms* provides an overview of the various application testing stages and the debug access (hardware and software) required in each.

For more information on Wireless interface security in the different protocols, see the following:

- Zigbee Security

- Bluetooth LE Fundamentals and relevant KBAs

- AN1037: Apple HomeKit Over Bluetooth®

- UG235.03: Architecture of the Silicon Labs Connect Stack v2.x

- UG435.03: Architecture of the Silicon Labs Connect Stack v3.x

### **Proven Cryptography**

# Proven Cryptography

Product security shall use strong, proven, updatable cryptography using open, peer-reviewed methods and algorithms.

An important aspect of any IoT device is how secure the device is when it communicates with other devices, gateways, or the cloud. This standard mandates using proven cryptographic methods rather than attempting to implement your own.

Developers commonly secure communications such as TCP/IP connections, Bluetooth, Zigbee, or Z-Wave using the standardized and proven cryptographic methods native to the protocol. However, if a microcontroller sends sensitive information over a simple interface such as a UART to another microcontroller, it is important to realize that data should also be secured to prevent someone from snooping the UART line.

Silicon Labs offers a hardware CRYPTO module that provides an efficient acceleration of common cryptographic operations and allows these to be used efficiently with low CPU overhead. The CRYPTO module includes hardware accelerators for the Advanced Encryption Standard (AES), Secure Hash Algorithm SHA-1 and SHA-2 (SHA-224 and SHA-256), and modular multiplication used in ECC (Elliptic Curve Cryptography) and GCM (Galois Counter Mode). The CRYPTO module can autonomously execute and iterate a sequence of instructions to aid software and speed up complex cryptographic functions like ECC, GCM, and CCM (Counter with CBC-MAC).

In addition to the CRYPTO module, Silicon Labs includes mbed TLS as part of the Gecko Platform SDK. mbed TLS is open source software licensed by ARM Limited. It provides an SSL library that makes it easy to use cryptography and SSL/TLS in applications. mbed TLS supports software implementations of all crypto algorithms that are supported by TLS 1.2 as well as a build API that allows hardware drivers to replace the software implementations when cipher accelerators are supported by the platform. Its modular framework allows for subcomponents like the crypto libraries to be incorporated into a design independently of the SSL/TLS components, saving valuable code space and runtime RAM. mbed TLS supports SSLv3 up to TLSv1.2 communication by providing the following:

- TCP/IP communication functions: listen, connect, accept, read/write.

- SSL/TLS communication functions: init, handshake, read/write.

- X.509 functions: CRT, CRL and key handling

- Random number generation

- Hashing

- Encryption/decryption

These functions are split up into logical interfaces. They can be used separately to provide any of the above functions or to mix-and-match into an SSL server/client solution that utilizes a X.509 PKI. Examples of such implementations are provided with the source code. Components or plugins and APIs provide configuration interfaces accessible through the various SDK installations.

For more information, see the latest MCU and Peripheral Software Documentation for the target part at https://docs.silabs.com.

### **Security by Default**

# Security by Default

Product security shall be appropriately enabled by default by the manufacturer.

The state in which a product is shipped is up to the manufacturer. This standard mandates that any security features provided with the product be enabled before shipping. Customers should not have to turn security on; rather they should actively have to disable it. For example, Silicon Labs Z-Wave end-nodes and gateway SDKs ship with S2 cryptography and SmartStart network formation enabled by default.

Silicon Labs believes that product security should be considered during product design, and not as an afterthought. Within development environments, all Silicon Labs application security features may be enabled or disabled as appropriate during application development. Security must also be considered during device design and testing. Bringing Up Custom Devices for the EFR32MG and EFR32FG Families describes the security tokens (keys, certificates, and so on) that can be programmed into a custom device to support various types of security, including that provided by the Gecko Bootloader (see Signed Software Updates).

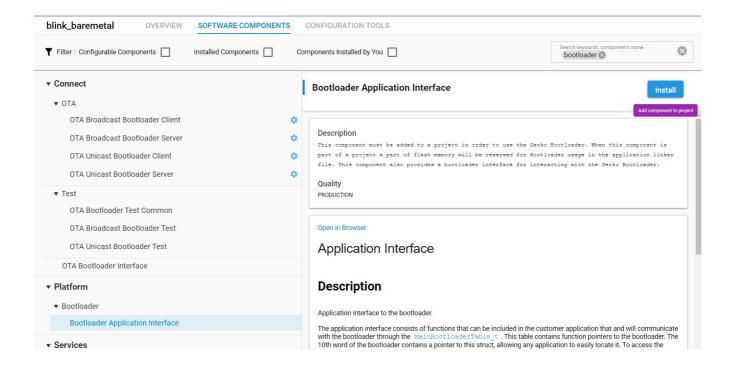

### Signed Software Updates

# Signed Software Updates

The product shall only support signed software updates. While it is critical that all products be updatable, it is just as critical that these update images be secured. A manufacturer must cryptographically sign update images to prevent tampering during deployment. The product must not use unsigned updates, as they could be fraudulent.

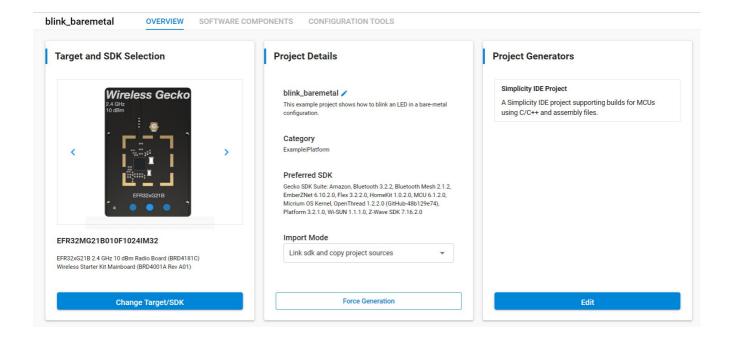

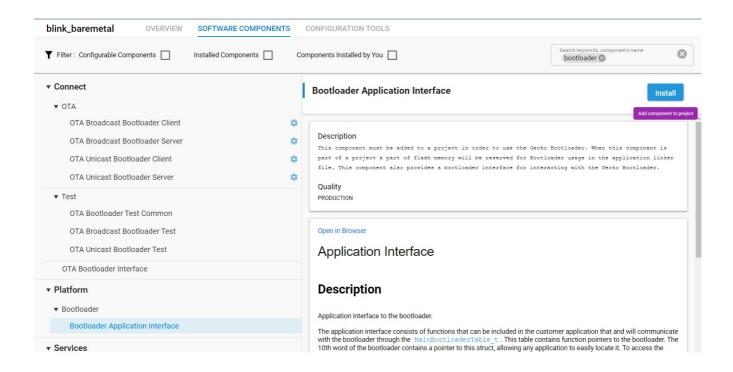

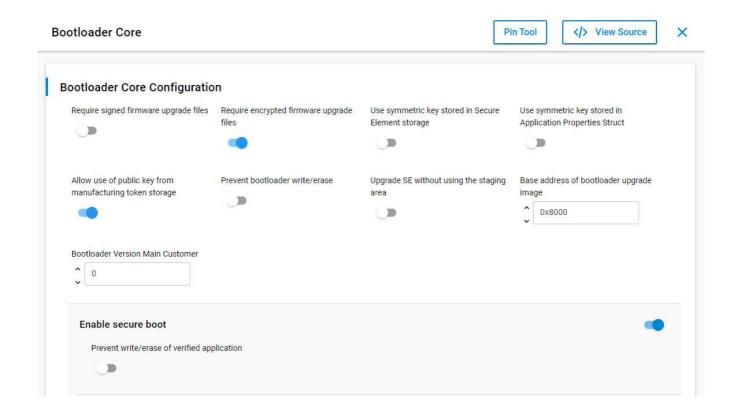

Silicon Labs development tools support building signed upgrade images and securely updating devices in the field, through the Silicon Labs Gecko Bootloader. The Gecko Bootloader can be configured to perform a variety of functions, from device initialization to firmware upgrades. Key features of the bootloader are:

- Useable across Silicon Labs Gecko microcontroller and wireless microcontroller families

- In-field upgradeable

- Configurable

- Enhanced security features, including:

- Secure Boot: When Secure Boot is enabled, the bootloader enforces cryptographic signature verification of the application image on every boot, using asymmetric cryptography. This ensures that the application was created and signed by a trusted party.

- Signed upgrade image file: The Gecko Bootloader supports enforcing cryptographic signature verification of the upgrade image file. This allows the bootloader and application to verify that the application or bootloader upgrade comes from a trusted source before starting the upgrade process, ensuring that the image file was created and signed by a trusted party.

- Encrypted upgrade image file: The image file can also be encrypted to prevent eavesdroppers from acquiring the plaintext firmware image.

On Series 1 devices, the Gecko Bootloader has a two-stage design, first stage and main stage, where a minimal first stage bootloader is used to upgrade the main bootloader. The first stage bootloader only contains functionality to read from and write to fixed addresses in internal flash. To perform a main bootloader upgrade, the running main bootloader verifies the integrity and authenticity of the bootloader upgrade image file. The running main bootloader then writes the upgrade image to a fixed location in internal flash and issues a reboot into the first stage bootloader. The first stage bootloader verifies the integrity of the main bootloader firmware upgrade image, by computing a CRC32 checksum before copying the upgrade image to the main bootloader location.

On Series 2 devices, the Gecko Bootloader consists only of the main stage bootloader. The main bootloader is upgradable through the hardware peripheral Secure Engine. The Secure Engine provides functionality to install an image to address 0x0 in internal flash, by copying from a configurable location in internal flash. To perform a main bootloader upgrade, the running main bootloader verifies the integrity and authenticity of the bootloader upgrade image file. The running main bootloader then writes the upgrade image to the upgrade location in flash and requests that the Secure Engine install it. The Secure Engine is also capable of verifying the authenticity of the main bootloader update image against a root of trust. The Secure Engine itself is upgradable using the same mechanism.

In summary, Series 2 devices support a hardware root of trust and a Secure Boot process that verifies the authenticity and integrity of Gecko Bootloader, whereas in Series 1 devices, the authenticity and integrity of Gecko Bootloader are assumed trusted and are not explicitly checked.

The Gecko Bootloader can enforce application image security on two levels:

- Secure Boot refers to the verification of the authenticity of the application image in main flash on every boot of the device. When Secure Boot is enabled, the cryptographic signature of the application image in flash is verified on every boot, before the application is allowed to run. Secure Boot is not enabled by default in the example configurations provided by Silicon Labs, but enabling it is highly recommended to ensure the validity and integrity of firmware images.

- Secure Firmware Upgrade refers to the verification of the authenticity of an upgrade image before performing a bootload, and optionally enforcing that upgrade images are encrypted. The Secure Firmware Upgrade process uses symmetric

encryption to encrypt the upgrade image, and asymmetric cryptography to sign the upgrade image in order to ensure its integrity and authenticity.

For more information on Silicon Labs' support for software update security, refer to the following:

Bootloaders in general: Bootloader Fundamentals

The Gecko Bootloader in general: Silicon Labs Gecko Bootloader User's Guide for Series 3 and Higher, Silicon Labs Gecko Bootloader User's Guide for GSDK 4.0 and Higher (series 1 and 2 devices), or *UG266: Silicon Labs Gecko Bootloader User's Guide for GSDK 3.2 and Lower.*

Using the Gecko Bootloader with specific protocols:

- Using the Gecko Bootloader with EmberZNet

- Using the Gecko Bootloader with Silicon Labs Connect

- Using the Gecko Bootloader with Silicon Labs Bluetooth Applications

Secure Boot on Series 2 devices: Series 2 Secure Boot with RTSL

### **Automatically Applied Updates**

# **Automatically Applied Updates**

The manufacturer will act quickly to apply timely security updates. Whenever a security vulnerability is detected, the manufacturer will automatically apply a patch to the product. No user intervention will be required.

It is the manufacturer's responsibility to develop and implement automatic security updates. The design and methodology of such systems, for example through a Cloud-connected infrastructure or by direct intervention by a service representative, is up to you.

Silicon Labs will notify you of any security-related updates, as described in Vulnerability Reporting Program. Your responsibility is to evaluate the level of risk that vulnerability poses for your particular product and to integrate the update into your platform as appropriate so that your end users are protected. Updated components might include the protocol libraries, Secure Engine firmware inside the Series 2 family, or an SDK module such as the Gecko Bootloader that enforces secure OTA updates and secure boot functionality.

Silicon Labs recommends the following:

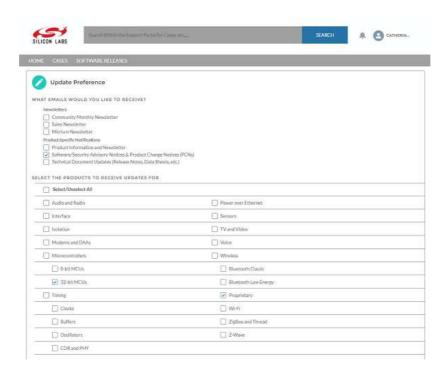

Subscribe to security updates through our Salesforce portal. To review or change your subscriptions, log in to the portal, click HOME to go to the portal home page and then click the Manage Notifications tile. Make sure that Software/Security Advisory Notices & Product Change Notices (PCNs) is checked, and that you are subscribed at minimum for your platform and protocol. Click Save to save any changes.

• Do not turn off Simplicity Studio's update notification. Within Simplicity Studio, you can download updates and easily access product release notes.

### **Vulnerability Reporting Program**

# Vulnerability Reporting Program

The manufacturer shall implement a vulnerability reporting program, which will be addressed in a timely manner. All companies that offer Internet-connected devices and services shall provide a public point of contact as part of a vulnerability disclosure policy in order that security researchers and others are able to report issues. Disclosed vulnerabilities should be acted on in a timely manner.

Manufacturers are responsible for implementing their own program. For any individual vulnerability, you will need to weigh the value of transparency with your customers against the risk of malicious use of the information to exploit a vulnerability before it can be addressed. Silicon Labs makes similar decisions about how broadly to report security vulnerabilities discovered in our products.

Silicon Labs customers and security researchers can report security vulnerabilities in Silicon Labs hardware and software products on the Silicon Labs website: https://www.silabs.com/security/product-security.

Silicon Labs' Security Vulnerability Disclosure Policy may be found here:

#### https://www.silabs.com/documents/public/miscellaneous/PS1012-Security\_Vulnerability\_Disclosure\_Policy.pdf

Silicon Labs has a Product Security Incident Response Team (PSIRT) that is dedicated to the case management of reported security vulnerabilities. The PSIRT works with other Silicon Labs groups including Applications, Developers, Sales, and Marketing to assess reported vulnerabilities, perform technical analysis and determine an appropriate response. The key processes for addressing vulnerabilities include:

- Triage: Determines what is needed to reproduce the vulnerability.

- Technical Analysis and Disposition: Confirms the validity of the security vulnerability, its scope, and its impact, and provides a resolution or disposition decision. Silicon Labs scores incidents according to CVSS 3.1 (Common Vulnerability Scoring System): low, medium, high, critical.

- Output: Communicates with our customers. The level and method of disclosure beyond the reporting entity depends on the severity and scope of the vulnerability.

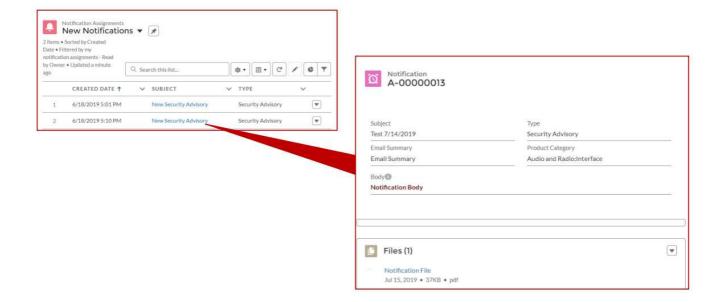

Silicon Labs' provides broad vulnerability reporting to customers subscribed through our Salesforce portal (see Automatically Applied Updates for information on how to subscribe). A subscribed customer will see Security Advisory notifications something like the following:

### **Security Expiration Date**

# Security Expiration Date

The manufacturer shall be transparent about the period of time that security updates will be provided. Like a manufacturer's product warranty, there shall be transparency around the support period of security updates.

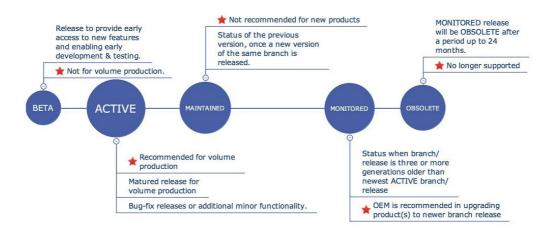

Manufacturers should provide details about product support at various stages and publish security expiration dates. Z-Wave's Protocol Lifecycle provides an example.

The Lifecycle details in what phases updates will be applied, and to what product branch. For details on the various phases and how the lifecycle is implemented for specific Z-Wave products, see:

https://www.silabs.com/products/development-tools/software/z-wave/embedded-sdk/life-cycle

### **Next Steps**

# **Next Steps**

The Silicon Labs Security web page (https://www.silabs.com/security) contains links to a variety of general security-related resources. You may wish to bookmark the page, as it will be continually updated with new content, new tools, and new flows.

If you are already in development, we strongly recommend that you implement the standards described here as you develop, test, and release your product to customers.

If you are in the early stages of your product design and have not already selected a device or development environment, we recommend that you include security considerations in your decision. Silicon Labs provides information about the security features of our devices and development environments. Section EFR32 Series 2 Device Security Features highlights the features and their documentation references. In addition, protocol-specific security information is available in the following documents.

- Zigbee Security

- AN1302: Bluetooth® Low Energy Application Security Design Considerations in SDK v3.x and Higher

- AN1329: Using Silicon Labs Secure Vault Features with OpenThread

- Bluetooth LE Fundamentals and relevant Knowledge Base Articles (KBAs)

- UG235.03: Architecture of the Silicon Labs Connect Stack v2.x

- UG435.03: Architecture of the Silicon Labs Connect Stack v3.x

### **Series 2 Device Security Features**

# Series 2 Device Security Features

Protecting IoT devices against security threats is central to a quality product. Silicon Labs offers several security options to help developers build secure devices, secure application software, and secure paths of communication to manage those devices. Silicon Labs' security offerings were significantly enhanced by the introduction of the Series 2 products that included a Secure Engine. The Secure Engine is a tamper-resistant component used to securely store sensitive data and keys, and to execute cryptographic functions and secure services.

On Series 1 devices, the security features are implemented by the TRNG (if available) and CRYPTO peripherals.

On Series 2 devices, the security features are implemented by the Secure Engine and CRYPTOACC (if available). The Secure Engine may be hardware-based, or virtual (software-based). Throughout this document, the following abbreviations are used:

- HSE: Hardware Secure Engine

- VSE: Virtual Secure Engine

- SE: Secure Engine (either HSE or VSE)

Additional security features are provided by Secure Vault. Three levels of Secure Vault feature support are available, depending on the part and SE implementation, as reflected in the following table:

| Security Level (1)         | SE Support         | MCU                                                                                | Wireless SoC (2)                                                                                            |

|----------------------------|--------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Secure Vault Base (SVB)    | N/A                | EFM32JG1, EFM32PG1,<br>EFM32JG12, EFM32PG12,<br>EFM32GG11, EFM32GG12,<br>EFM32TG11 | EFR32xG1, EFR32xG12,<br>EFR32xG13, EFR32xG14                                                                |

| Secure Vault Mid (SVM)     | VSE (VSE-SVM)      | EFM32PG22C                                                                         | EFR32xG22C, EFR32xG27C (3)                                                                                  |

| Secure Vault Mid<br>(SVM)  | HSE (HSE-SVM)      | -                                                                                  | EFR32xG21A, EFR32xG21A (Rev<br>C), EFR32MR21A (Rev C),<br>EFR32xG23A, EFR32xG24A,<br>EFR32xG25A, EFR32xG28A |

| Secure Vault High<br>(SVH) | HSE only (HSE-SVH) | EFM32PG23B, EFM32PG28B                                                             | EFR32xG21B, EFR32xG12B (Rev<br>C) EFR32xG23B, EFR32xG24B,<br>EFR32xG25B, EFR32xG28B                         |

#### Notes:

- 1. The features of different Secure Vault levels can be found in https://www.silabs.com/security.

- 2. The x is a letter B, F, M, or Z.

- 3. Unlike other VSE-SVM parts, the EFR32xG27C device has a built-in PUF.

Secure Vault Mid consists of two core security functions:

- Secure Boot: Process where the initial boot phase is executed from an immutable memory (such as ROM) and where code is authenticated before being authorized for execution.

- Secure Debug access control: The ability to lock access to the debug ports for operational security, and to securely unlock them when access is required by an authorized entity.

Secure Vault High offers additional security options:

- Secure Key Storage: Protects cryptographic keys by "wrapping" or encrypting the keys using a root key known only to the HSE-SVH.

- Anti-Tamper protection: A configurable module to protect the device against tamper attacks.

**Device authentication**: Functionality that uses a secure device identity certificate along with digital signatures to verify the source or target of device communications.

A Secure Engine Manager and other tools allow users to configure and control their devices both in-house during testing and manufacturing, and after the device is in the field.

Silicon Labs strongly recommends installing the latest SE FW image on Series 2 devices and updating to the latest GSDK to mitigate security vulnerabilities. The latest SE FW image can be found in this Windows folder for GSDK v4.x:

C:\Users\<PC USER NAME>\SimplicityStudio\SDKs\gecko\_sdk\util\se\_release\public

Refer to AN1222: Production Programming of Series 2 Devices for guidance on the SE firmware upgrade procedure. The latest SE firmware shipped with Series 2 devices and modules (if available) at the time of this writing are listed in the following table:

#### :::custom-table{30%,}

| Series 2 MCU and Wireless SoC VSE - SVM | Shipped SE Firmware Version |

|-----------------------------------------|-----------------------------|

| EFM32PG22C                              | 1.2.12                      |

| EFR32xG22C                              | 1.2.12                      |

| EFR32xG22C (Rev D)                      | 1.2.14                      |

| EFR32xG27C                              | 2.2.1                       |

| :::                                     |                             |

#### :::custom-table{30%,}

| Series 2 Wireless SoC HSE - SVM | Shipped SE Firmware Version |

|---------------------------------|-----------------------------|

| EFR32xG21A                      | 1.2.13                      |

| EFR32MR21A (Rev C)              | 1.2.16                      |

| EFR32xG21A (Rev C)              | 1.2.16                      |

| EFR32xG23A                      | 2.1.7                       |

| EFR32xG24A                      | 2.1.7                       |

| EFR32xG25A                      | 2.2.1                       |

| EFR32xG28A                      | 2.2.2                       |

| :::                             |                             |

#### :::custom-table{30%,}

| Series 2 MCU and Wireless SoC HSE - SVH | Shipped SE Firmware Version |

|-----------------------------------------|-----------------------------|

| EFR32xG21B                              | 1.2.13                      |

| EFR32xG21B (Rev C)                      | 1.2.16                      |

| EFM32PG23B                              | 2.1.7                       |

| EFR32xG23B                              | 2.1.7                       |

| EFR32xG24B                              | 2.1.7                       |

| EFR32xG25B                              | 2.2.1                       |

| EFM32PG28B                              | 2.2.2                       |

| EFR32xG28B                              | 2.2.2                       |

| ::                                      |                             |

In support of these products Silicon Labs offers whitepapers, webinars, and documentation. The following table summarizes the key security documents:

:::custom-table{30%,50%,20%}

| Document                                                                                                         | Summary                                                                                                                                 | Applicability            |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Document                                                                                                         | Summary                                                                                                                                 | Applicability            |

| Series 2 Secure Debug                                                                                            | How to lock and unlock Series 2 debug access, including background information about the Secure Engine                                  | Series 2                 |

| Series 2 Secure Boot with RTSL                                                                                   | Describes the secure boot process on Series 2 devices using Secure Engine.                                                              | Series 2                 |

| Anti-Tamper Protection Configuration and Use                                                                     | How to program, provision, and configure the anti-tamper module                                                                         | Series 2<br>with SVH     |

| Authenticating Silicon Labs Devices using Device Certificates                                                    | How to authenticate a device using secure device certificates and signatures, at any time during the life of the product                | Series 2<br>with SVH     |

| Secure Key Storage                                                                                               | How to securely "wrap" keys so they can be stored in non-volatile storage                                                               | Series 2<br>with SVH     |

| AN1222: Production Programming of Series 2<br>Devices                                                            | How to program, provision, and configure security information using Secure Engine during device production                              | Series 2                 |

| AN1303: Programming Series 2 Devices Using<br>the Debug Challenge Interface (DCI) and<br>Serial Wire Debug (SWD) | How to provision and configure Series 2 devices through<br>the DCI and how to program their internal flash memory<br>through the SWD    | Series 2                 |

| AN1311: Integrating Crypto Functionality Using PSA Crypto Compared to Mbed TLS                                   | How to integrate crypto functionality into applications using Silicon Labs implementation of PSA Crypto compared to Mbed TLS            | Series 1 and<br>Series 2 |

| Series 2 TrustZone                                                                                               | Describes the basics of TrustZone, secure and privileged programming model, and shows how to upgrade existing application to TrustZone. | Series 2                 |

### **Overview**

# Silicon Labs IoT Security Developer's Guide

The IoT Security Developer's Guide offers detailed information on how to implement each of the device security features. This content is applicable to any protocol that supports the feature described. Additional protocol-specific information for Bluetooth, Bluetooth Mesh, OpenThread, and Zigbee is available in the protocol-specific section.

- Series 2 Secure Debug: Describes how to lock and unlock the debug access of EFR32 Gecko Series 2 devices. Many aspects of the debug access, including the secure debug unlock are described. The Debug Challenge Interface (DCI) and Secure Engine (SE) Mailbox Interface for locking and unlocking debug access are also included.

- Series 2 TrustZone: Covers the basics of ARMv8-M TrustZone, describes how TrustZone is implemented on Series 2 devices, and provides application examples.

- Production Programming of Series 2 Devices (PDF): Provides details on programming, provisioning, and configuring Series 2 devices in production environments. Covers Secure Engine Subsystem of Series 2 devices, which runs easily upgradeable Secure Engine (SE) or Virtual Secure Engine (VSE) firmware.

- Anti-Tamper Protection Configuration and Use: Shows how to program, provision, and configure the anti-tamper module on EFR32 Series 2 devices with Secure Vault.

- Authenticating Silicon Labs Devices using Device Certificates: Describes how to authenticate an EFR32 Series 2 device with Secure Vault, using secure device certificates and signatures.

- Secure Key Storage: Explains how to securely "wrap" keys in EFR32 Series 2 devices with Secure Vault, so they can be stored in non-volatile storage.

- Programming Series 2 Devices Using the Debug Challenge Interface (DCI) and Serial Wire Debug (SWD) (PDF): Describes how to provision and configure Series 2 devices through the DCI and SWD.

- Integrating Crypto Functionality Using PSA Crypto Compared to Mbed TLS (PDF): Describes how to integrate crypto functionality into applications using PSA Crypto compared to Mbed TLS.

### **Series 2 Secure Debug**

# Series 2 Secure Debug

NOTE: This section replaces AN1190: Series 2 Secure Debug. Further updates to this application note will be provided here.

This application note describes how to lock and unlock the debug access of Series 2 devices. Many aspects of the debug access, including the secure debug unlock, are discussed. The Debug Challenge Interface (DCI) and Mailbox Interface for locking and unlocking debug access are also included.

The debug locks and unlocks for the Cortex-M33 debug interface are implemented through the Secure Engine on Series 2 devices.

### **Key Points**

- Basic overview of the Secure Engine.

- Debug port access by Debug Challenge Interface (DCI) or Mailbox Interface.

- New locking and unlocking features for Series 2 devices.

- Examples for provisioning and Secure Debug Unlock.

### **Series 2 Device Security Features**

# Series 2 Device Security Features

Protecting IoT devices against security threats is central to a quality product. Silicon Labs offers several security options to help developers build secure devices, secure application software, and secure paths of communication to manage those devices. Silicon Labs' security offerings were significantly enhanced by the introduction of the Series 2 products that included a Secure Engine. The Secure Engine is a tamper-resistant component used to securely store sensitive data and keys and to execute cryptographic functions and secure services.

On Series 1 devices, the security features are implemented by the TRNG (if available) and CRYPTO peripherals.

On Series 2 devices, the security features are implemented by the Secure Engine and CRYPTOACC (if available). The Secure Engine may be hardware-based, or virtual (software-based). Throughout this document, the following abbreviations are used:

- HSE Hardware Secure Engine

- VSE Virtual Secure Engine

- SE Secure Engine (either HSE or VSE)

Additional security features are provided by Secure Vault. Three levels of Secure Vault feature support are available, depending on the part and SE implementation, as reflected in the following table:

| Level (1)               | SE Support         | Part (2)                                                                       |

|-------------------------|--------------------|--------------------------------------------------------------------------------|

| Secure Vault High (SVH) | HSE only (HSE-SVH) | Refer to IoT Endpoint Security Fundamentals for details on supporting devices. |

| Secure Vault Mid (SVM)  | HSE (HSE-SVM)      | п                                                                              |

| п                       | VSE (VSE-SVM)      | п                                                                              |

| Secure Vault Base (SVB) | N/A                | п                                                                              |

#### Notes

- 1. The features of different Secure Vault levels can be found in https://www.silabs.com/security.

- 2. IoT Endpoint Security Fundamentals.

Secure Vault Mid consists of two core security functions:

- Secure Boot: Process where the initial boot phase is executed from an immutable memory (such as ROM) and where code is authenticated before being authorized for execution.

- Secure Debug access control: The ability to lock access to the debug ports for operational security, and to securely unlock them when access is required by an authorized entity.

Secure Vault High offers additional security options:

- Secure Key Storage: Protects cryptographic keys by "wrapping" or encrypting the keys using a root key known only to the HSE-SVH.

- Anti-Tamper protection: A configurable module to protect the device against tamper attacks.

- Device authentication: Functionality that uses a secure device identity certificate along with digital signatures to verify the source or target of device communications.

A Secure Engine Manager and other tools allow users to configure and control their devices both in-house during testing and manufacturing, and after the device is in the field.

### **User Assistance**

In support of these products, Silicon Labs offers whitepapers, webinars, and documentation. The following table summarizes the key security documents:

| Document                                                      | Summary                                                                                                                  | Applicability             |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Series 2 Secure Debug (this application note)                 | How to lock and unlock Series 2 debug access, including background information about the SE                              | Secure Vault Mid and High |

| Series 2 Secure Boot with RTSL                                | Describes the secure boot process on Series 2 devices using SE                                                           | Secure Vault Mid and High |

| Anti-Tamper Protection Configuration and Use                  | How to program, provision, and configure the anti-<br>tamper module                                                      | Secure Vault High         |

| Authenticating Silicon Labs Devices using Device Certificates | How to authenticate a device using secure device certificates and signatures, at any time during the life of the product | Secure Vault High         |

| Secure Key Storage                                            | How to securely 'wrap' keys so they can be stored in non-volatile storage.                                               | Secure Vault High         |

| AN1222: Production Programming of Series 2 Devices            | How to program, provision, and configure security information using SE during device production                          | Secure Vault Mid and High |

### **Key Reference**

Public/Private keypairs along with other keys are used throughout Silicon Labs security implementations. Because terminology can sometimes be confusing, the following table lists the key names, their applicability, and the documentation where they are used.

| Key Name                                                   | Customer Programmed | Purpose                                                                     |

|------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|

| Public Sign key (Sign Key Public)                          | Yes                 | Secure Boot binary authentication and/or OTA upgrade payload authentication |

| Public Command key (Command<br>Key Public)                 | Yes                 | Secure Debug Unlock or Disable Tamper command authentication                |

| OTA Decryption key (GBL<br>Decryption key) aka AES-128 Key | Yes                 | Decrypting GBL payloads used for firmware upgrades                          |

| Attestation key aka Private Device<br>Key                  | No                  | Device authentication for secure identity                                   |

### **SE Firmware**

Silicon Labs strongly recommends installing the latest SE firmware on Series 2 devices to support the required security features. Refer to AN1222 for the procedure to upgrade the SE firmware and IoT Endpoint Security Fundamentals for the latest SE Firmware shipped with Series 2 devices and modules.

### **Introduction To Secure Debug**

# Introduction to Secure Debug

### **Debug Lock**

All devices require the capability to lock out debug access to the device. This prevents attackers from using the debug interface to perform the following illegal operations:

- Reprogramming the device

- Interrogating the device

- · Interfering with the operation of the device

A fairly standard practice during the board-level test in production is to program, test, and lock the parts.

Three different locks can be enabled on the Series 2 debug interface:

- Standard-debug-lock

- Permanent-debug-lock

- Secure-debug-lock

Silicon Labs provides Custom Part Manufacturing Service (CPMS) to securely configure the debug port of the chip to one of the three possible locks before the devices leave the factory.

### **Debug Unlock**

Users need to unlock parts under a number of circumstances:

- Code development

- Field failure diagnosis

- Product field service

- Existing inventory reprogramming

Two different unlocks can run on the Series 2 debug interface:

- Standard-debug-unlock

- Secure-debug-unlock

### **Secure Engine Subsystem**

# Secure Engine Subsystem

#### Overview

The HSE refers to a separate security co-processor that provides hardware isolation between security functions and the host processor.

The VSE refers to a collection of security functions available to the host processor in Root mode if a separate security coprocessor is not provided.

The SE is used to perform a series of cryptographic operations and other secure system operations as described in the following table.

| Operation                | VSE-SVM | HSE-SVM | HSE-SVH | Description                                        |

|--------------------------|---------|---------|---------|----------------------------------------------------|

| Unique ID                | Υ       | Υ       | Υ       | Software can identify every device.                |

| Secure Boot with RTSL    | Υ       | Υ       | Υ       | Only boot authenticated firmware.                  |

| Secure Debug             | Υ       | Υ       | Υ       | Allow enhanced failure analysis.                   |

| Crypto Engine (1)        | -       | Υ       | Υ       | Up to 256-bit ciphers and elliptic curves.         |

| TRNG (1)                 | -       | Υ       | Υ       | Generate keys for cryptography.                    |

| DPA Countermeasures      | -       | Υ       | Υ       | Resist side channel attacks.                       |

| Secure Key Storage       | -       | -       | Υ       | Protected by PUF technology.                       |

| Secure Key<br>Management | -       | -       | Υ       | Isolate encrypted keys from application code.      |

| Secure Attestation       | -       | -       | Υ       | Ensure integrity and authenticity.                 |

| Anti-Tamper              | -       | -       | Υ       | Detect tamper and protect keys/data.               |

| Advanced Crypto          | -       | -       | Υ       | Up to 512-bit ciphers and 521-bit elliptic curves. |

#### Note:

1. On VSE-SVM devices, the crypto engine and TRNG (True Random Number Generator) are implemented by the CRYPTOACC (Cryptographic Accelerator) peripheral.

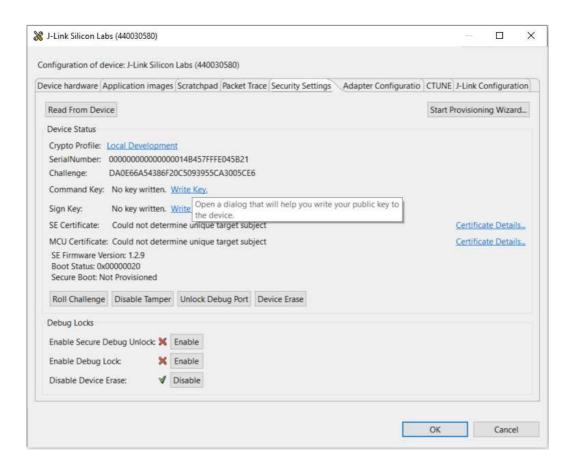

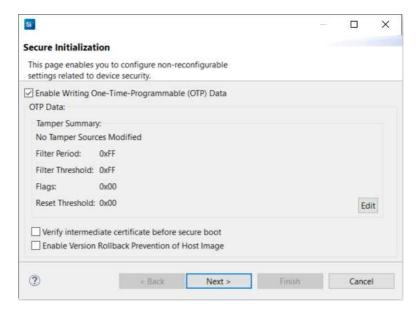

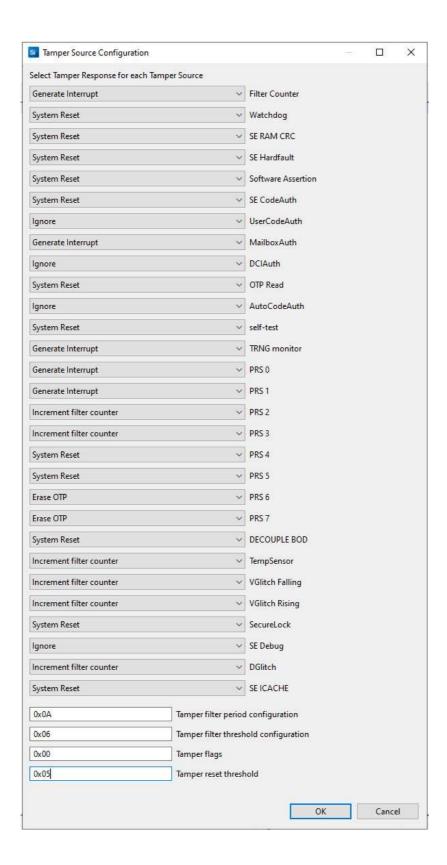

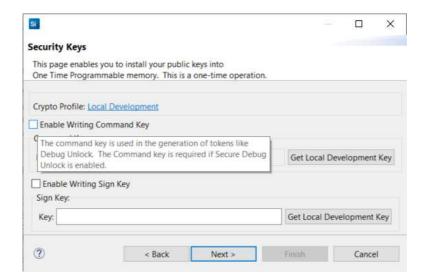

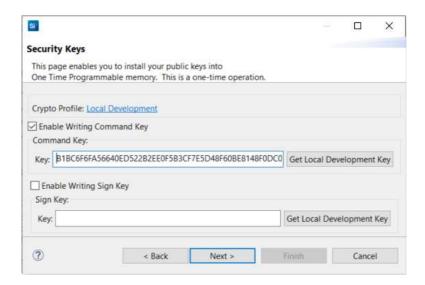

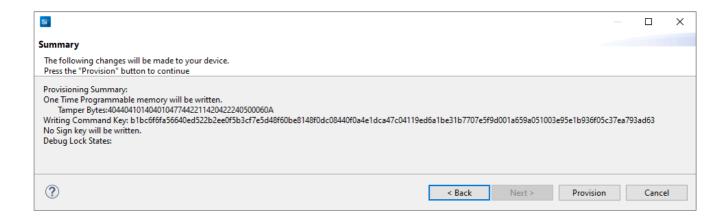

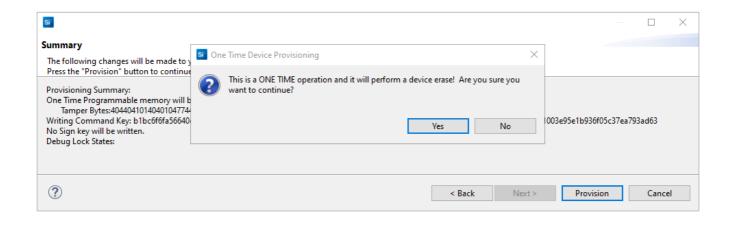

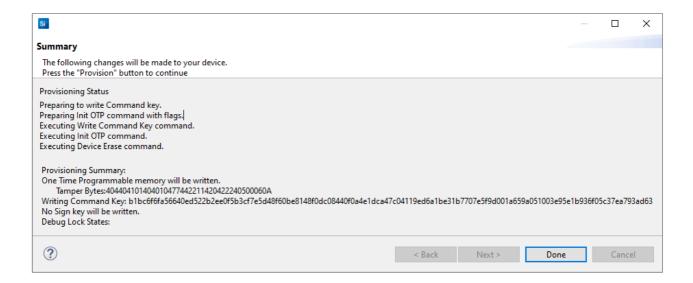

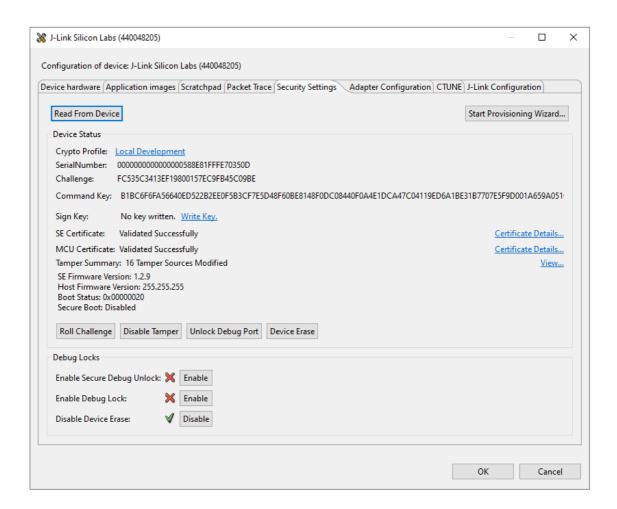

To start using the secure debug unlock functionality, the device needs to be provisioned. These steps include writing one-time-programmable (OTP) settings to the SE to determine which functionality is enabled, and uploading the Public Command Key to validate a secure debug attempt.

This application note describes how the different device debug locks and unlocks are implemented through the SE on Series 2 devices.

The secure debug feature is implemented by Root code executed by the HSE Core or by the Cortex-M33 operating in VSE (Root mode).

Silicon Labs strongly recommends installing the latest SE firmware on Series 2 devices to support the required security features. The latest SE firmware image (.seu and .hex) and release notes can be found in the Windows folder below.

For GSDK v3.2 and lower:

$C:\label{linear_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_control_cont$

For GSDK v4.0 and higher:

$\hbox{C:} \verb|Users|<| PC USER NAME>| Simplicity Studio| SDKs| gecko_sdk| util| se_release| public to the content of the content$

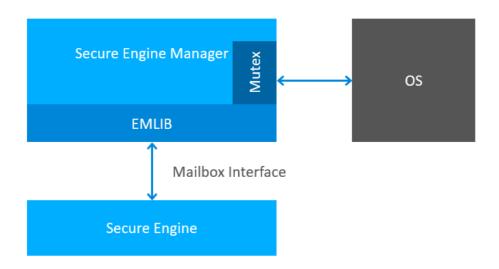

#### **Command Interface**

Interaction with the SE is performed over a command interface. The command interface is available through a dedicated Debug Challenge Interface (DCI) as well as through a mailbox interface from the Cortex-M33.

Some commands may not be available at all times and may not be accessible over both interfaces. The DCI typically only contains operations for setting up a new device and for locking it down (meant for production processes), while the mailbox interface also contains commands to support cryptographic operations in HSE.

#### **Mailbox**

Mailbox operations should not be performed directly, but rather should be executed through the appropriate functions in em\_se.c of emlib. The em\_se.c provides an abstraction of the mailbox interface, allowing message construction and DMA transfer setup.

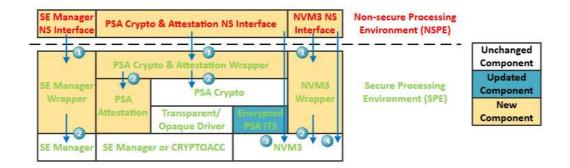

On top of emlib, the Secure Engine Manager (SE Manager) provides an abstraction of the Secure Engine's command set. The SE Manager also provides APIs for cryptographic operations and thread synchronization. The SE Manager is available in GSDK v3.0 or later.

**Note**: Some functions in em\_se.c of emlib are deprecated in **GSDK v3.0** and will be removed in a future version of emlib . All high-level functionality has been moved to the SE Manager.

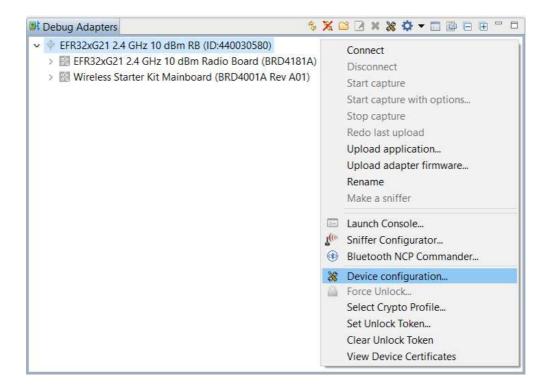

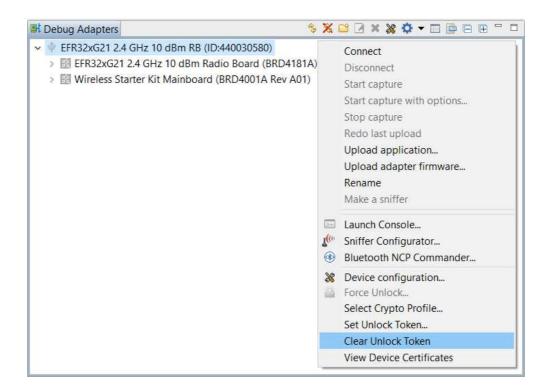

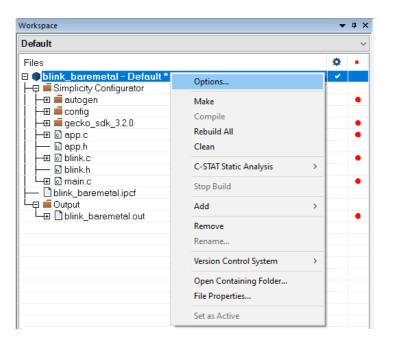

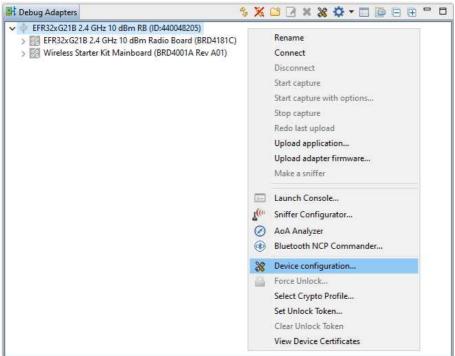

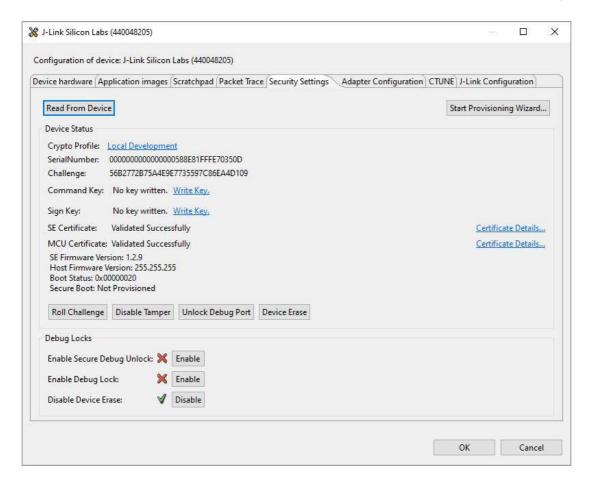

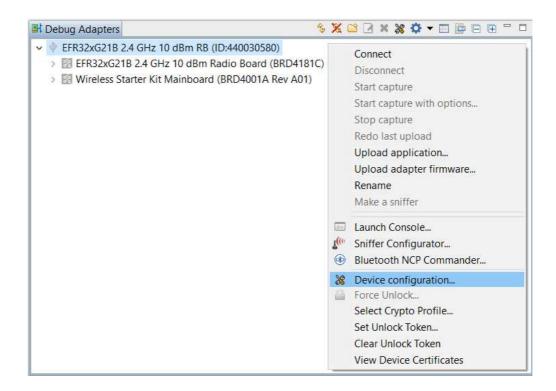

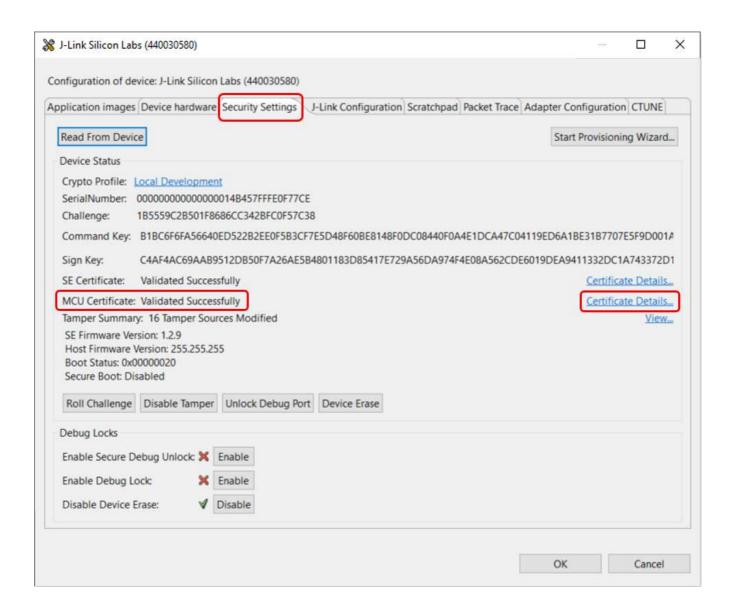

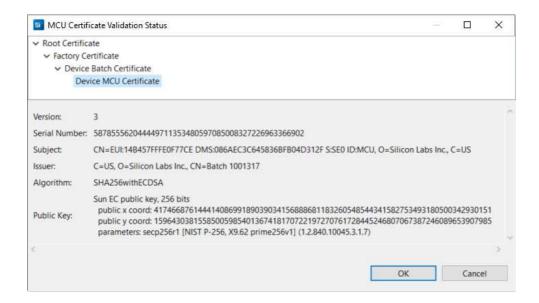

### **Debug Challenge Interface (DCI)**

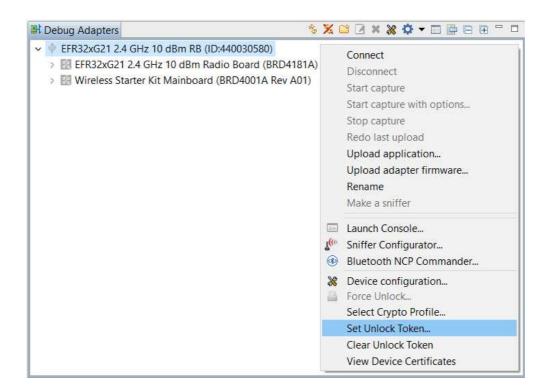

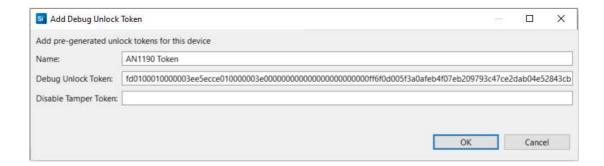

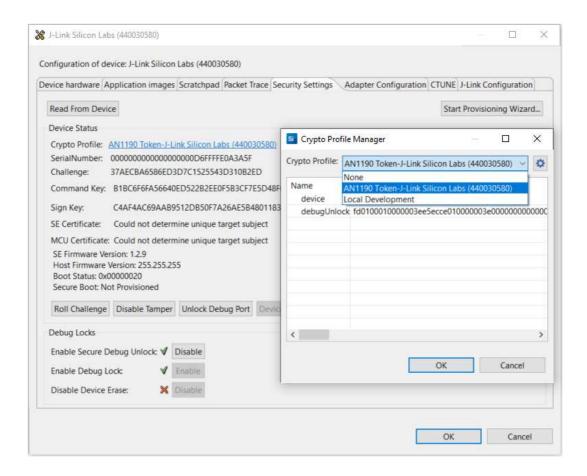

The Debug Challenge Interface (DCI) is made available through commands in Simplicity Studio and Simplicity Commander. This is the easiest way to access and set up the different security options.

For more information about DCI, see AN1303: Programming Series 2 Devices using the Debug Challenge Interface (DCI) and Serial Wire Debug (SWD).

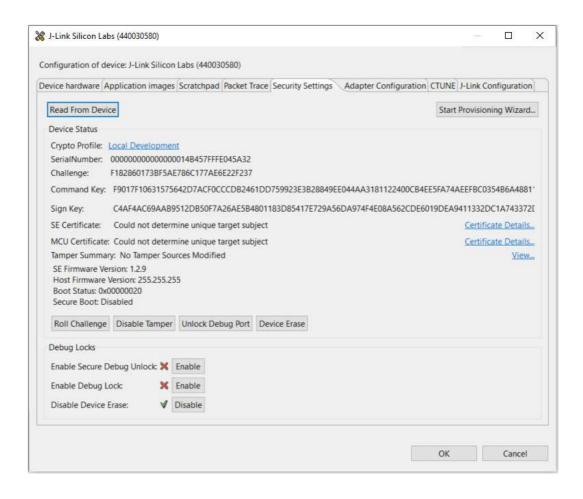

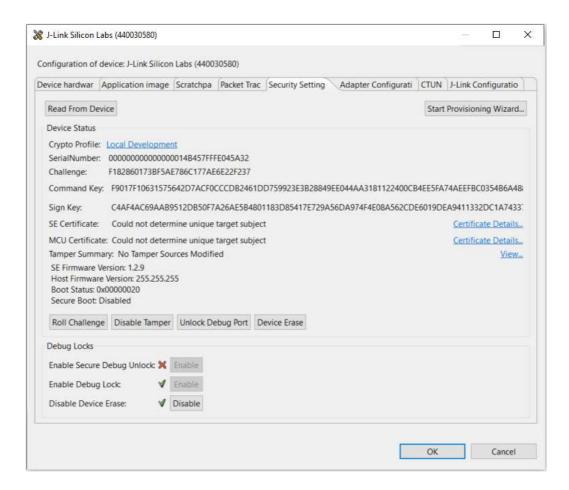

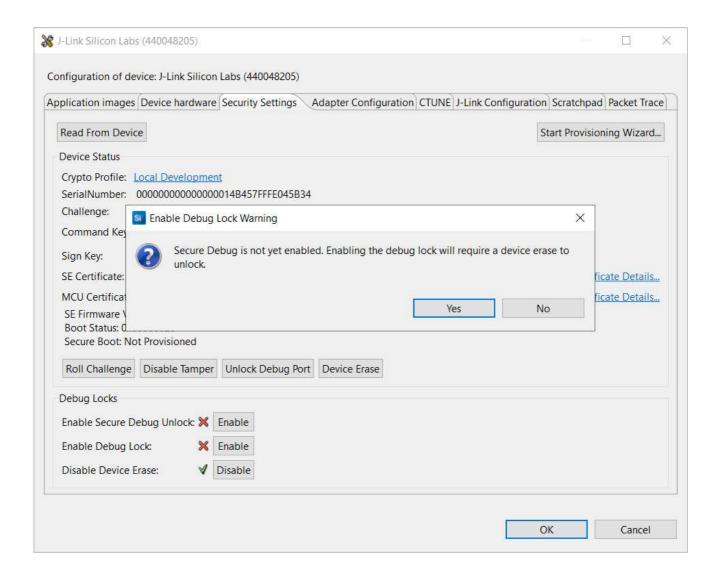

### **Debug Lock**

# Debug Lock

#### Overview

The debug access port connected to the Series 2 device's Cortex-M33 processor can be closed by issuing commands to the SE, either from a debugger over DCI or through the mailbox interface. These three debug lock properties govern the behavior of the debug lock.

| Property     | Description If Set                     | Default Value    |

|--------------|----------------------------------------|------------------|

| Debug Lock   | The debug port is kept locked on boot. | False (Disabled) |

| Device Erase | The Erase Device command is available. | True (Enabled)   |

| Secure Debug | Secure debug unlock is available.      | False (Disabled) |

The following sections describe how to interact with these properties and how to enable debug locks using the SE command interface either over DCI or the mailbox interface. The status of the debug lock can be inspected using the Read Lock Status command.

### **Standard Debug Unlock**

The device is in standard debug unlock state if the debug lock properties are in default values.

| Secure Debug | Device Erase | Debug Lock        | Description                       |

|--------------|--------------|-------------------|-----------------------------------|

| Disabled     | Enabled      | Disabled (Unlock) | All debug operations are allowed. |

# **Standard Debug Lock**

With the default properties in the table above, the device can be locked using the Apply Lock command. The typical flow for this configuration is simply to issue the Apply Lock command after the device has been programmed, either using a DCI command from the programming debugger or through the mailbox interface.

| Secure Debug | Device Erase | Debug Lock         | Description                                                                                                |

|--------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------|

| Disabled     | Enabled      | Enabled (Standard) | The Erase Device command will wipe the main flash and RAM, and then a reset will yield an unlocked device. |

The standard debug lock behaves similarly to Series 1 devices. The access port can be closed, but issuing a device erase wipes the device and opens the debug port again.

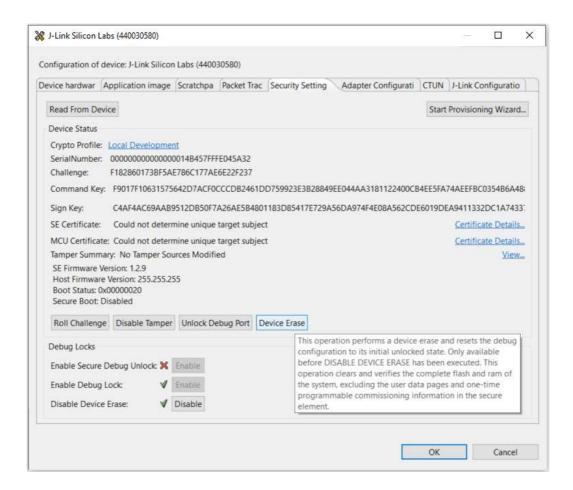

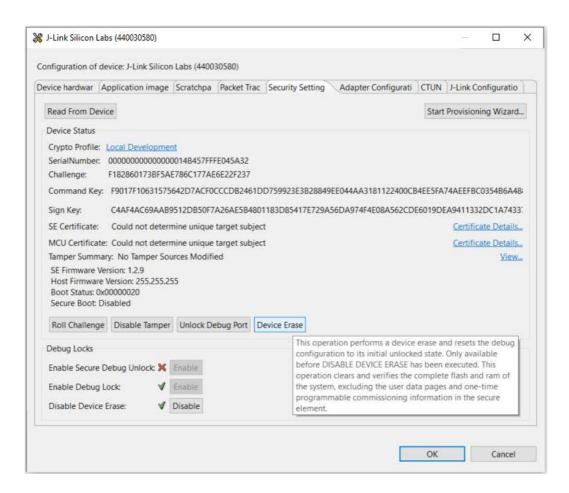

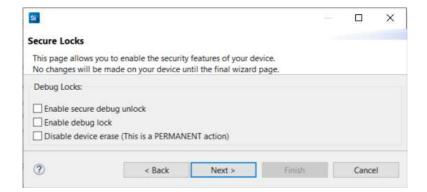

# **Permanent Debug Lock**

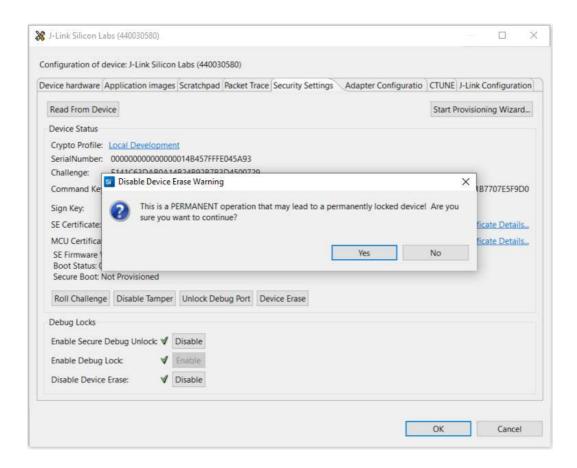

The Erase Device command can be disabled, which permanently enables the debug lock. This can be done at any time by issuing the Disable Device Erase command, even after the debug lock has been enabled.

| Secure Debug | Device Erase | Debug Lock          | Description                                                                                                     |

|--------------|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------|

| Disabled     | Disabled     | Enabled (Permanent) | The part cannot be unlocked. Devices with Permanent Debug Lock engaged cannot be returned for failure analysis. |

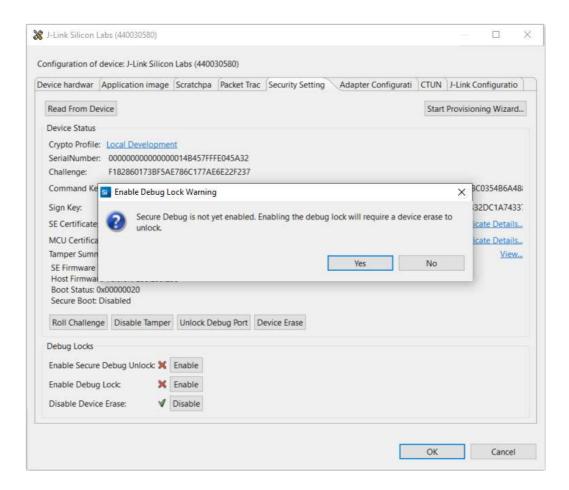

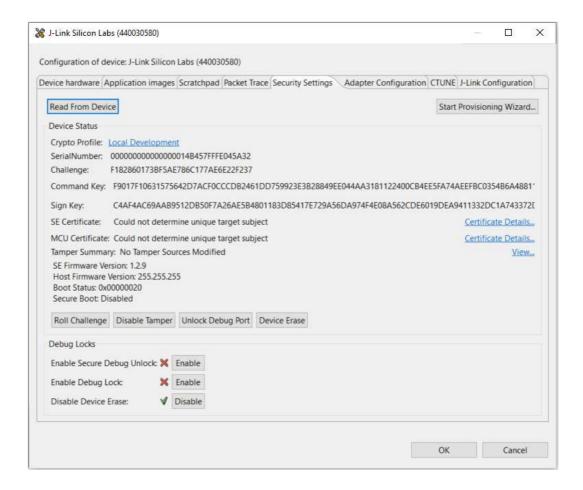

# **Secure Debug Lock**

For secure debug lock, the debug interface can be temporarily enabled by answering a challenge if the Secure debug property is enabled before locking.

| Secure Debug | Device Erase | Debug Lock       | Description                                                                                                                                |

|--------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Enabled (1)  | Disabled (2) | Enabled (Secure) | Secure debug unlock is enabled, which makes it possible to securely open the debug lock temporarily to reprogram or debug a locked device. |

#### Note:

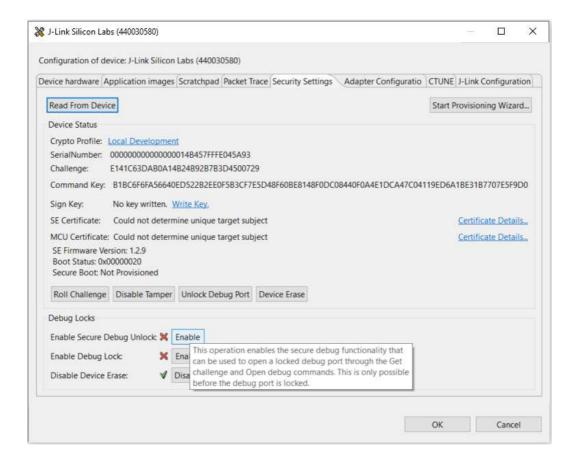

- 1. Secure debug is enabled in two steps before the debug lock is enabled:

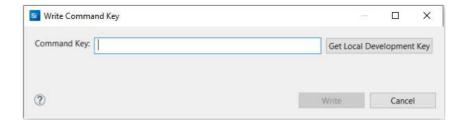

- a. Install the Public Command Key using Simplicity Studio or Simplicity Commander or directly through the SE Manager API.

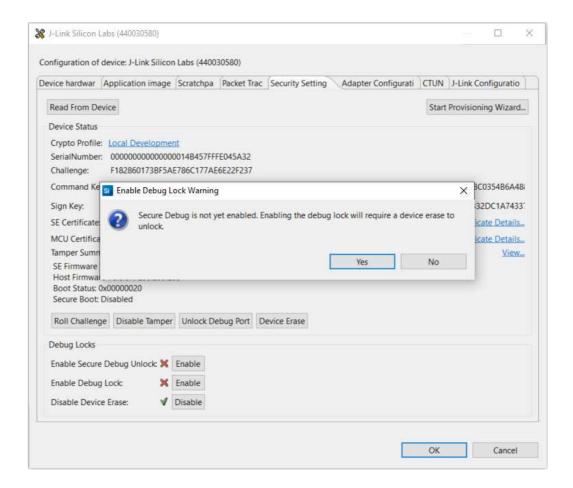

- b. Enable secure debug using Simplicity Studio or Simplicity Commander or directly through the SE Manager API.

- 2. Disable the device erase using Simplicity Studio or Simplicity Commander or directly through the SE Manager API. This is an IRREVERSIBLE action and should be disabled AFTER the secure debug is enabled.

### **Debug Lock State Transition**

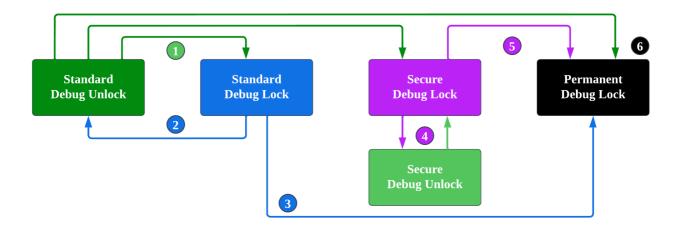

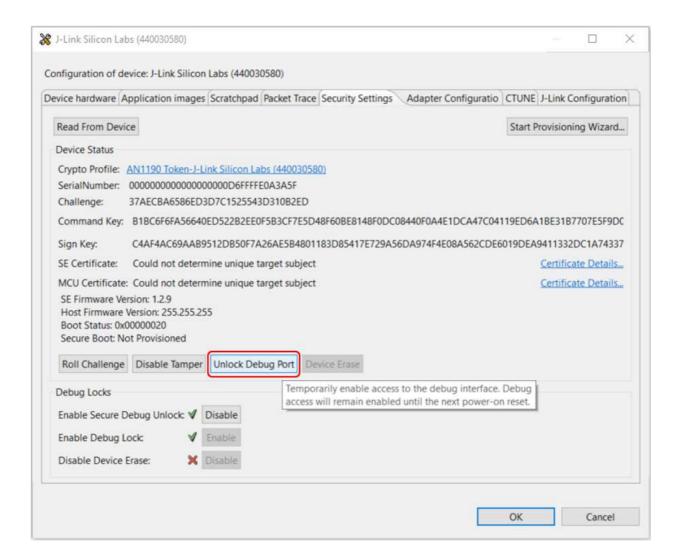

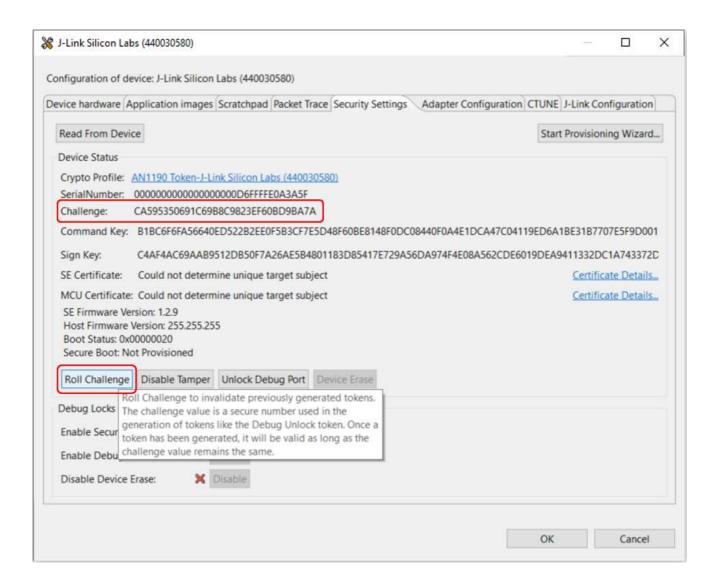

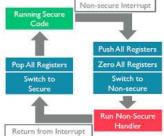

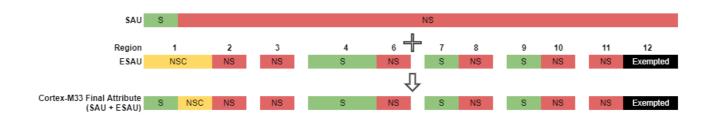

The following figure describes the transitions between different debug lock states.

- 1. Standard debug unlock can transit to any debug lock state.

- 2. Standard debug lock can revert to standard debug unlock via an Erase Device command (erase the main flash and RAM).

After the device is reset, debug port remains unlocked until it is explicitly locked again.

- 3. Standard debug lock can transit to permanent debug lock by disabling the Device Erase property but cannot transit to secure debug lock.

- 4. Secure debug lock can use Debug Unlock Token to temporary transit to secure debug unlock, which does not erase the main flash and RAM but enables debug operations. The device reverts to the secure debug lock through a power-on or pin reset.

- 5. Secure debug lock can transit to permanent debug lock by disabling the Secure Debug property but cannot transit to standard debug lock.

- 6. Permanent debug lock is a terminal state and cannot transit to any debug lock or unlock state.

### **Debug Lock Command Reference**

The commands for debug lock are described in the following table.

| DCI Command (1) | Mailbox (SE Manager) API (2) | Description                          | Availability             |

|-----------------|------------------------------|--------------------------------------|--------------------------|

| Apply Lock      | sl_se_apply_debug_lock       | Enables the debug lock for the part. | While debug is unlocked. |

| DCI Command (1)      | Mailbox (SE Manager) API (2) | Description                                                                                                                                                          | Availability                                                            |

|----------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Read Lock Status     | sl_se_get_debug_lock_status  | Returns the current debug lock status and configuration.                                                                                                             | Always.                                                                 |

| Disable Device Erase | sl_se_disable_device_erase   | Disables the Erase Device command. This command does not lock the debug interface to the part, but it is an IRREVERSIBLE action for the part.                        | Always.                                                                 |

| Disable Secure Debug | sl_se_disable_secure_debug   | Disables the secure debug functionality that can be used to open a locked debug port.                                                                                | While secure debug is enabled.                                          |

| Enable Secure Debug  | sl_se_enable_secure_debug    | Enables the secure debug functionality that can be used to open a locked debug port.                                                                                 | While debug is<br>unlocked and<br>Public<br>Command Key<br>is uploaded. |

| Set debug options    | sl_se_set_debug_options      | Configures the TrustZone access permissions of the debug interface. (3)                                                                                              | While debug is unlocked.                                                |

| Init Pub Key         | sl_se_init_otp_key           | Used to provision a single public key during device initialization. The public key cannot be changed once written, and the command will be unavailable for that key. | Available once for each key.                                            |

| Read Pub Key         | sl_se_read_pubkey            | Reads the stored public key.                                                                                                                                         | Always.                                                                 |

| Get Challenge        | sl_se_roll_challenge         | Used to roll the current challenge value (16 bytes) to revoke secure debug access. (4)                                                                               | While Public<br>Command Key<br>is uploaded.                             |

#### Notes:

- 1. Performing these commands over DCI is implemented in Simplicity Studio and Simplicity Commander.

- 2. The sl\_se\_apply\_debug\_lock, sl\_se\_get\_debug\_lock\_status, sl\_se\_init\_otp\_key, and sl\_se\_read\_pubkey are available on all Series 2 devices. Other APIs are only available on HSE devices. The SE Manager API document can be found at https://docs.silabs.com/gecko-platform/latest/service/api/group-sl-se-manager.

- 3. For more information about debug options, see TrustZone Debug Authentication.

- 4. A new challenge will only be generated if the current one has been successfully used at least once.

### **Debug Unlock**

# Debug Unlock

#### Overview

The debug access port connected to the Series 2 device's Cortex-M33 processor can be opened by issuing commands to the SE, either from a debugger over DCI or through the mailbox interface.

New on the Series 2 devices is the addition of secure debug unlock functionality. When enabled, it is possible to request a challenge from the device and, by answering the challenge, disable the debug lock until the next power-on or pin reset.

The status of the debug lock can be inspected using the Read Lock Status command.

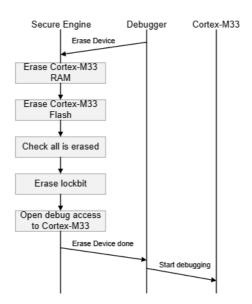

### **Standard Debug Unlock**

With the properties of the standard debug lock or secure debug lock with Device Erase enabled, the device can be returned to the standard debug unlock state using the Erase Device command. This command will wipe the main flash and RAM and verify they are empty before opening the debug lock. It will not wipe user data and provisioned SE settings.

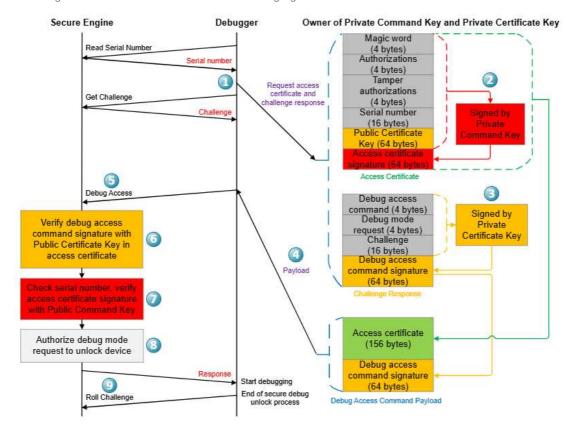

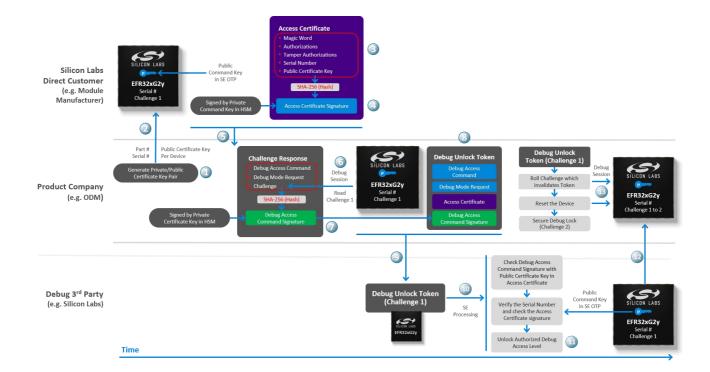

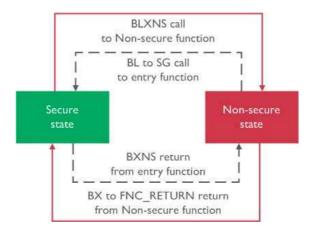

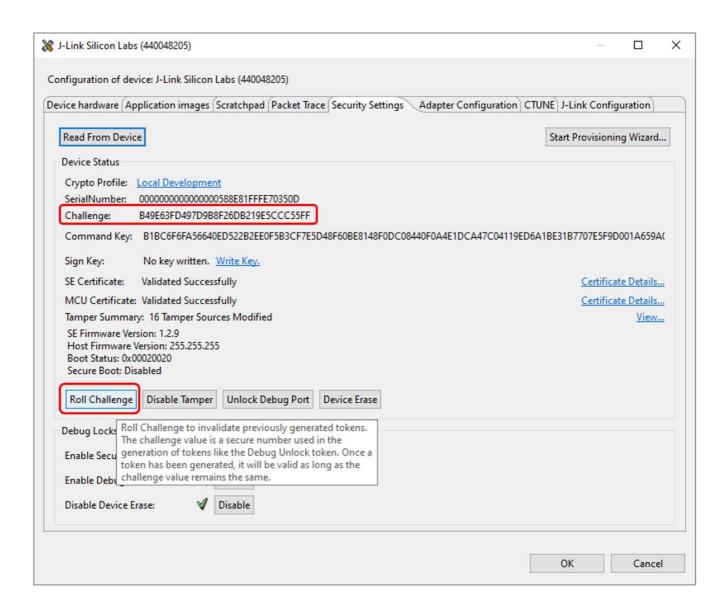

### **Secure Debug Unlock**

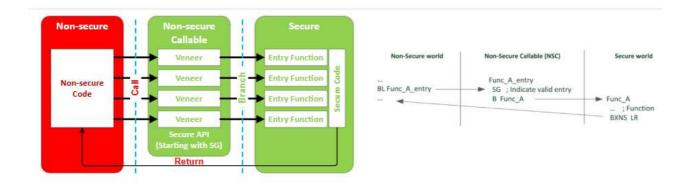

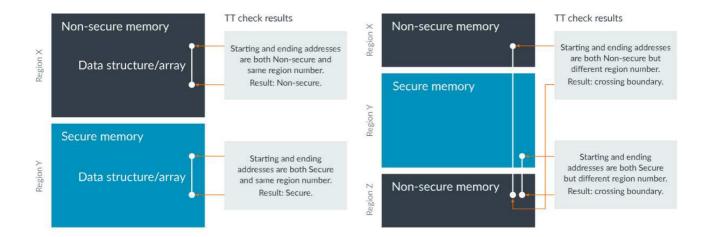

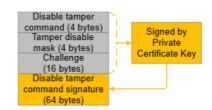

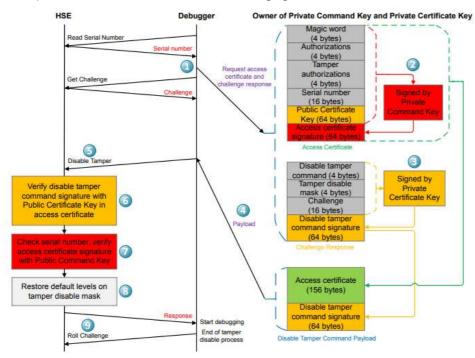

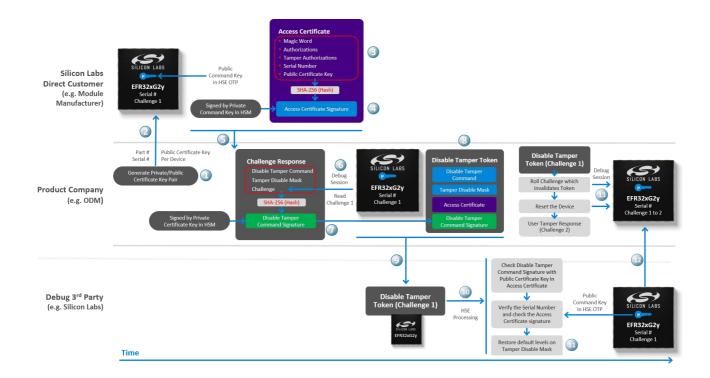

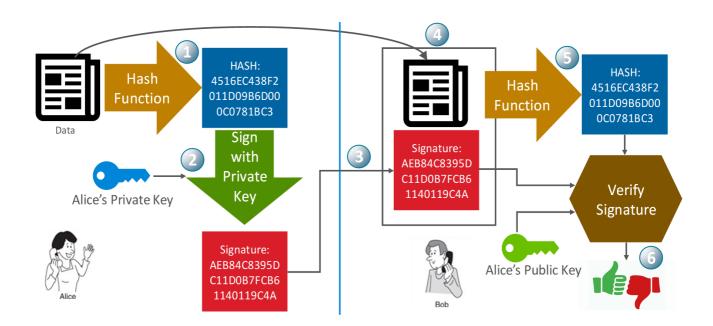

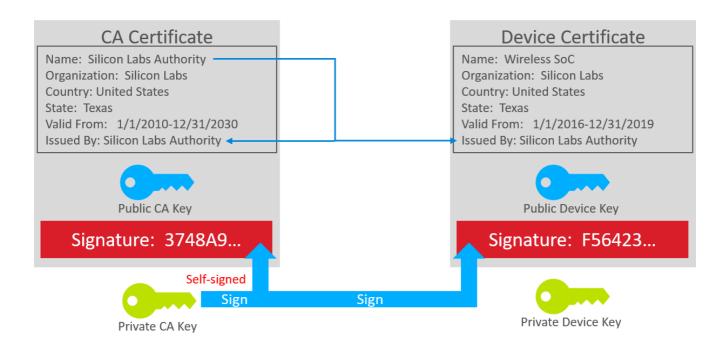

In a secure debug unlock scenario, the customer, who has control over the Private Command Key for a SE, has programmed a Public Command Key into the device. The Public Command Key is used to verify the signature on a certificate, telling the SE what authorization has been given by the owner of the key (customer) to the one issuing the command (customer or delegate). Authorization can be granted, for example, to unlock only the debug port on the Cortex-M33, or to restore only specific tamper signals on HSE-SVH devices.

This mode is particularly useful in failure analysis scenarios because it allows devices to be unlocked without losing flash and RAM contents.

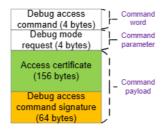

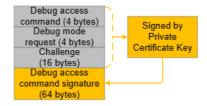

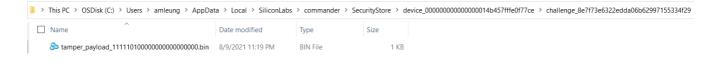

#### **Debug Unlock Token**

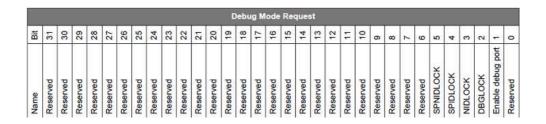

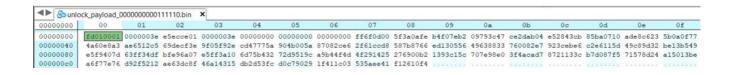

The elements of the Debug Unlock Token are described in the following figures and table.

| Element                            | Value            | Description                                        |

|------------------------------------|------------------|----------------------------------------------------|

| Debug access command               | 0xfd010001       | The command word of the Debug Unlock Token.        |

| Debug mode request                 | Device-dependent | The command parameter of the debug access command. |

| Access certificate (1)             | Device-dependent | See section Access Certificate.                    |

| Debug access command signature (1) | Device-dependent | See section Challenge Response.                    |

#### Note:

1. The debug access command payload consists of an access certificate and a debug access command signature.

#### Notes:

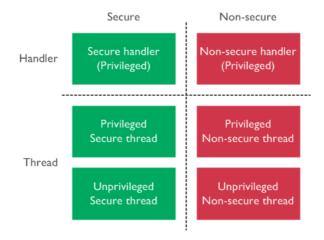

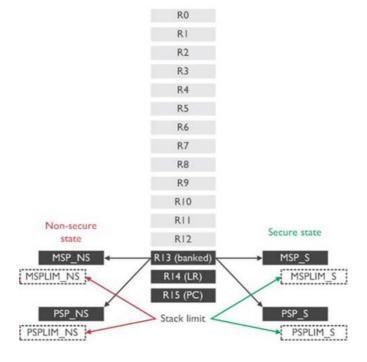

- Enable debug port Debug port enabled if set.

- DBGLOCK (Non-secure, Invasive debug lock) The Invasive debug features for the Non-secure state are unlocked if set.

- NIDLOCK (Non-secure, Non-invasive debug lock) The Non-invasive debug features for the Non-secure state are unlocked if set

- SPIDLOCK (Secure, Invasive debug lock) The Invasive debug features for the Secure state are unlocked if set.

- SPNIDLOCK (Secure, Non-Invasive debug lock) The Non-invasive debug features for the Secure state are unlocked if set.

- All reserved bits should be 0, and bit 1 must be 1 to access the debug port.

- For the TrustZone-unaware debugging, bits 2 to 5 are irrelevant, so bits 1 to 5 are usually set (0x0000003e) to match with the Authorizations in the access certificate.

- For the TrustZone-aware debugging, bits 2 to 5 are relevant. Refer to Trust Zone Debug Authentication for details about these debug options.

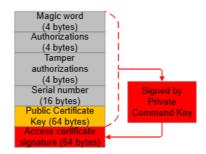

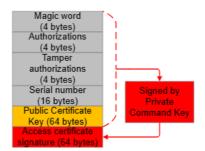

#### **Access Certificate**

The elements of the access certificate are described in the following figures and table.

| Element                      | Value                        | Description                                                                                                                                 |

|------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Magic word                   | 0xe5ecce01                   | A constant value used to identify the access certificate.                                                                                   |

| Authorizations               | 0x0000003e (1)               | A value used to authorize which bit in the debug mode request can be enabled for secure debug.                                              |

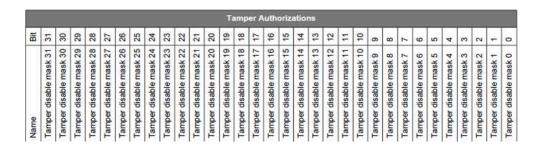

| Tamper Authorizations        | 0x00000000 or 0xffffffb6 (2) | A value used to authorize which bit in the tamper disable mask can be set to disable the tamper response.                                   |

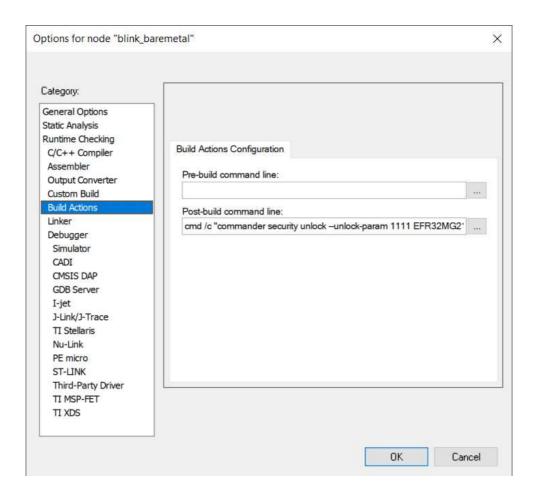

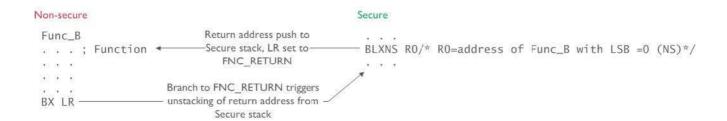

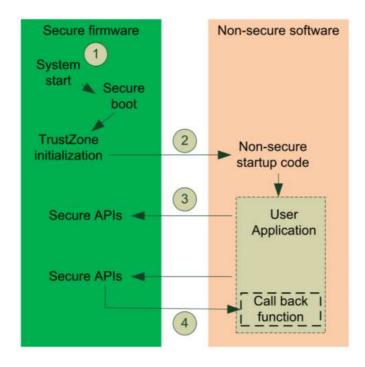

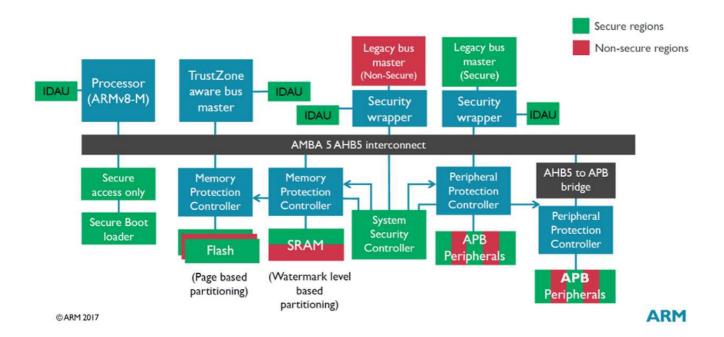

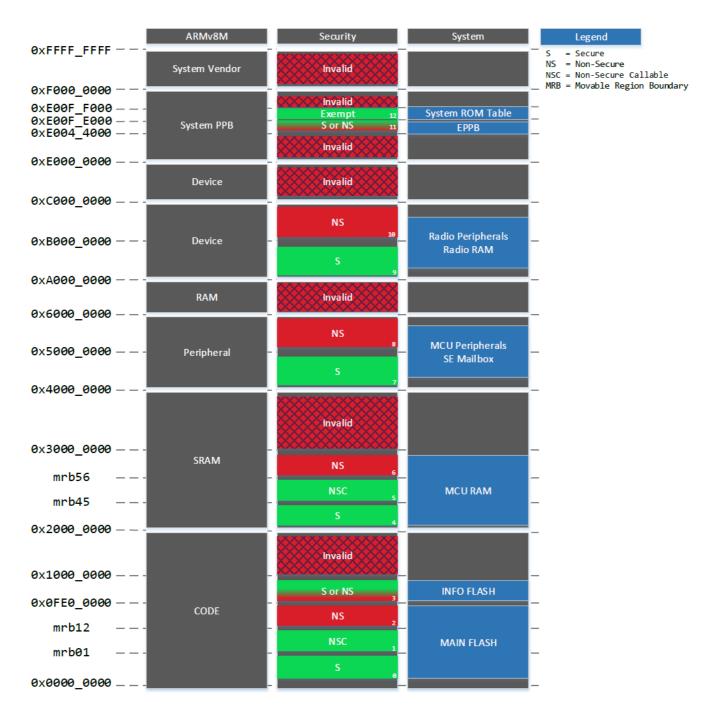

| Serial number                | Device-dependent             | A number used to compare against the on-chip serial number for secure debug or tamper disable.                                              |