Rev: 00

| Product       | Bluetooth Module |  |

|---------------|------------------|--|

| Model         | GCC-BTM002S      |  |

| Date of issue | 2023-XX-XX       |  |

| Revision      | 00               |  |

| Issued by   | Signature | Date |

|-------------|-----------|------|

|             |           |      |

| Reviewed by | Signature | Date |

|             |           |      |

**Revision History**

| - 10 - 101 | • • • • • • • • • • • • • • • • • • • • |                    |

|------------|-----------------------------------------|--------------------|

| Rev        | Date                                    | Change Description |

|            |                                         |                    |

Rev: 00

## **Table of Contents**

| 1. | Intro | oduction                       | 3  |

|----|-------|--------------------------------|----|

| 1  | .1    | Naming Declaration             | 3  |

| 1  | .2    | Block Diagram                  | 3  |

| 1  | .3    | Features                       | 5  |

| 1  | .4    | Applications                   | 5  |

| 2. | Gen   | neral Specification            | 5  |

| 3. | Pin   | Configuration                  | 7  |

| 4. | Pin   | Definition                     | 8  |

| 5. | Rec   | commended Operating Conditions | 11 |

| 6  | War   | mina                           | 12 |

Rev: 00

## 1. Introduction

GCC-BTM002S is a Bluetooth low energy (BLE) module supporting BT5.0 (BLE only). This module makes it easy for customers to add Bluetooth low energy to their products. Customers can easily establish wireless connections with the module. It supports Bluetooth low energy (Bluetooth 5), ANT and 2.4GHz proprietary protocol stacks.

# 1.1 Naming Declaration

| New Naming Old Naming |    | Description                     |  |

|-----------------------|----|---------------------------------|--|

| GCC-BTM002S           | No | Module with antenna and shield. |  |

# 1.2 Block Diagram

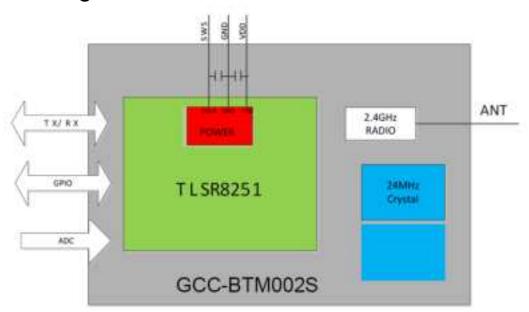

Fig. 1. Module Block Diagram.

Rev: 00

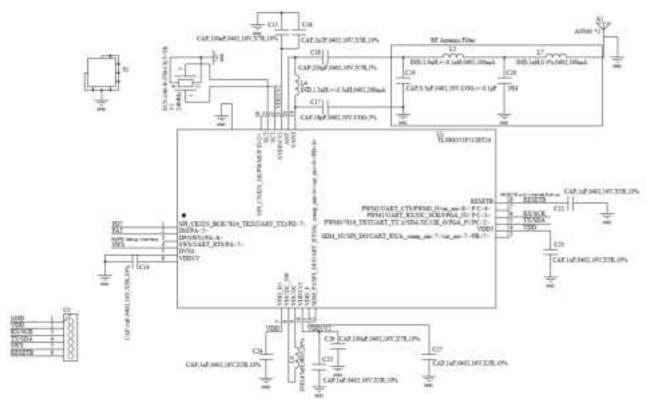

Fig. 2. Schematic Diagram.

The GCC-BTM002S module integrates a 32-bit BLE MCU TLSR8251 , 24MHZ crystal, PCB antenna, Uart and some GPIOs.

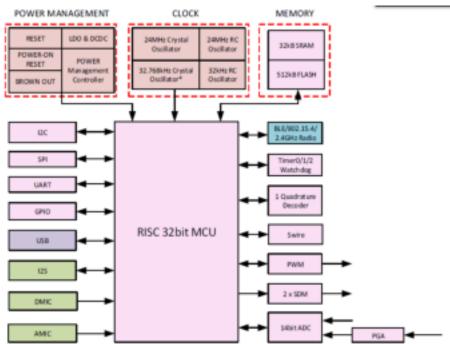

Fig. 3. TLSR8251 Block Diagram.

Rev: 00

The TLSR8251 integrates a power-balanced 32-bit MCU, BLE/802.15.4/2.4GHz Radio, 32kB SRAM, 512kB internal Flash, 14bit ADC with PGA, analog and digital microphone input, stereo audio output, 6-channel PWM (1-channel IR/IR FIFO/IR DMA FIFO), one quadrature decoder (QDEC), abundant and flexible GPIO interfaces, and nearly all the peripherals needed for IoT (Internet of Things) and HID (Human Interface Devices) application development (e.g. Bluetooth Low Energy and IEEE 802.15.4). The TLSR8251 also includes multi-stage power management design allowing ultra-low power operation and making it the ideal candidate for wearable and power-constraint applications.

With the high integration level of TLSR8251, few external components are needed to satisfy customers' ultralow cost requirements.

## 1.3 Features

- BT5. 0( BLE only) , up to 2Mbps

- -96dbm sensitivity, Tx power 10dBm

- Include ATT. GATT. SMP. L2CAP. GAP

- AES HW encryption with Easy DMa

- ANT, 2. 4GHz,

- 32bit mcu with 32KB RAM 512KB FLASH

- 14 bits Adc

- UART SPL2CQDEC. PDM

- SWD Debug interface

- Size 20mm x 16mm

- Operating temperature : -40°Cto+85°C

## 1.4 Applications

Smart home: heating control and lighting control

Health sensors: blood pressure, thermometer and glucose meters

Sports and fitness sensors: heart rate, runner speed and cadence, cycle speed and cadence

HID Devices: keyboards, mice, touchpads, remote controls

## 2. General Specification

| Bluetooth Specification |                                 |  |

|-------------------------|---------------------------------|--|

| Standard                | Bluetooth 5.0 (1Mbps only)      |  |

| Protocols Supported     | ATT. GATT. SMP. L2CAP. GAP. etc |  |

| Evaguancy Rand Antonna  | 2.402GHz~2.480GHz               |  |

| Frequency Band Antenna  | PCB antenna (1.87dbi)           |  |

| High System Clock       | 24MHZ                           |  |

| Interface a             | UART PIO. SPAIO. 2S. PDM.ADC    |  |

Rev: 00

| Sensitivity                                  | -96dBm |  |  |

|----------------------------------------------|--------|--|--|

| RF TX Power 10 dBm                           |        |  |  |

| Power                                        |        |  |  |

| Power Supply Voltage 1.7~3.6VDC              |        |  |  |

| Deep Sleep current 0. 3uA in system off mode |        |  |  |

| Operating Environment                        |        |  |  |

| -40~85°C Temperature                         |        |  |  |

| Dimension                                    |        |  |  |

| GCC-BTM002S 20mm×16mm                        |        |  |  |

| Weight                                       |        |  |  |

| GCC-BTM002S                                  | 50g    |  |  |

Rev: 00

# 3. TLSR8251 Pin Configuration

Fig. 4. Pin Configuration.

Rev: 00

# 4. TLSR8251 Pin Definition

| No. | Pin Name                                                          | Туре        | Description                                                                                                                    |  |  |

|-----|-------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | SPI_CK/I2S_BCK/7816_TRX<br>(UART_TX)/PD<7>                        | Digital I/O | SPI clock (I2C_SCK) / I2S bit clock / UART 781<br>TRX (UART_TX) / GPIO PD[7]                                                   |  |  |

| 2   | DMIC_DI/PWMO_N/UART_RX/<br>PA<0>                                  | Digital I/O | DMIC data input / PWM0 inverting output / UART_RX / GPIO PA[0]                                                                 |  |  |

| 3   | DMIC_CLK/7816_CLK/I2S_CLK/<br>PA<1>                               | Digital I/O | DMIC clock / UART 7816 clock<br>/ I2S clock / GPIO PA[1]                                                                       |  |  |

| 4   | DO/UART_TX/PWM0/PA<2>                                             | Digital I/O | SPI data output / UART_TX / PWM0 output / GPIO PA[2]                                                                           |  |  |

| 5   | DI/UART_CTS/PWM1/PA<3>                                            | Digital I/O | SPI data input (I2C_SDA) / UART_CTS / PWM1 output / GPIO PA[3]                                                                 |  |  |

| 6   | CK/UART_RTS/PWM2/PA<4>                                            | Digital I/O | SPI clock (I2C_SCK) / UART_RTS / PWM2<br>output / GPIO PA[4]                                                                   |  |  |

| 7   | DM/PA<5>                                                          | Digital I/O | USB data minus / GPIO PA[5]                                                                                                    |  |  |

| 8   | DP(SWS)/PA<6>                                                     | Digital I/O | USB data positive (Single wire slave) / GPIO<br>PA[6]                                                                          |  |  |

| 9   | SWS/UART_RTS/PA<7>                                                | Digital I/O | Single wire slave/ UART_RTS / GPIO PA[7]                                                                                       |  |  |

| 10  | PWM3/UART_RX/ATSEL1/<br>sar_aio<0>/PB<0>                          | Digital I/O | PWM3 output / UART_RX / Antenna select<br>pin 1 / SAR ADC input / GPIO PB[0]                                                   |  |  |

| 11  | PWM4/UART_TX/ATSEL2/lc_comp<br>_ain<1>/sar_aio<1>/PB<1>           | Digital I/O | PWM4 output / UART_TX / Antenna select pin<br>2 / Low power comparator input / SAR ADC<br>input / GPIO PB[1]                   |  |  |

| 12  | DVSS                                                              | GND         | Digital LDO ground                                                                                                             |  |  |

| 13  | VDD1V                                                             | PWR         | Internal LDO generated power supply input<br>for digital core                                                                  |  |  |

| 14  | DVSS                                                              | GND         | Digital LDO ground                                                                                                             |  |  |

| 15  | VDD_IO                                                            | PWR         | External 3.3V power supply input for IO                                                                                        |  |  |

| 16  | VDCDC_SW                                                          | Analog      | Connect with VDCDC via external inductor                                                                                       |  |  |

| 17  | VDCDC                                                             | Analog      | Connect with VDCDC_SW via external inductor                                                                                    |  |  |

| 18  | VDD1V2                                                            | PWR         | Internal DCDC generated power supply.  Connect to GND via external capacitor. Route this 1.2V voltage power supply to AVDD1V2. |  |  |

| 19  | VDD_F                                                             | PWR         | Internally generated power supply to flash.  Connect to GND via external capacitor.                                            |  |  |

| 20  | PWM5/UART_CTS/RX_CYC2LNA/<br>lc_comp_ain<2>/sar_aio<2>/<br>PB<2>  | Digital I/O | PWM5 output / UART_CTS / Control external<br>LNA / Low power comparator input / SAR ADC<br>input / GPIO PB[2]                  |  |  |

| 21  | PWM0_N/UART_RTS/TX_CYC2PA/<br>lc_comp_ain<3>/sar_aio<3>/<br>PB<3> | Digital I/O | PWM0 inverting output / UART_RTS / Control<br>external PA / Low power comparator input /<br>SAR ADC input / GPIO PB[3]         |  |  |

| 22  | SDM_P0/PWM4/lc_comp_ain<4>/<br>sar_aio<4>/P8<4>                   | Digital I/O | SDM positive output 0 / PWM4 output / Low<br>power comparator input / SAR ADC input /<br>GPIO PB[4]                            |  |  |

Rev: 00

| _   | _                                                              |             |                                                                                                                                              |

|-----|----------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Pin Name                                                       | Туре        | Description                                                                                                                                  |

| 23  | SDM_N0/PWM5/lc_comp_ain<5>/<br>sar_aio<5>/PB<5>                | Digital I/O | SDM negative output 0 / PWM5 output / Low<br>power comparator input / SAR ADC input /<br>GPIO PB[5]                                          |

| 24  | SDM_P1/SPI_DI/UART_RTS/<br>lc_comp_ain<6>/sar_aio<6>/<br>P8<6> | Digital I/O | SDM positive output 1 / SPI data input<br>(I2C_SDA) / UART_RTS / Low power<br>comparator input / SAR ADC input /<br>GPIO PB[6]               |

| 25  | SDM_N1/SPI_DO/UART_RX/<br>lc_comp_ain<7>/sar_aio<7>/<br>PB<7>  | Digital I/O | SDM negative output 1 / SPI data output /<br>UART_RX / Low power comparator input /<br>SAR ADC input / GPIO PB[7]                            |

| 26  | VDD3                                                           | PWR         | Connect to an external 3.3V power supply                                                                                                     |

| 27  | VDDIO_AMS                                                      | PWR         | External 3.3V power supply input for<br>analog/mixed signal circuitry.                                                                       |

| 28  | I2C_SDA/PWM4_N/UART_RTS/<br>PGA_P0/PC<0>                       | Digital I/O | I2C serial data / PWM4 inverting output / UART_RTS / PGA left channel positive input / GPIO PC[0]                                            |

| 29  | I2C_SCK/PWM1_N/PWM0/<br>PGA_N0/PC<1>                           | Digital I/O | 12C serial clock / PWM1 inverting output / PWM0 output / PGA left channel negative input / GPIO PC[1]                                        |

| 30  | PWM0/7816_TRX(UART_TX)/I2C_<br>SDA/XC32K_O/PGA_P1/PC<2>        | Digital I/O | PWMO output / UART 7816 TRX (UART_TX) /  12C serial data / (optional) 32kHz crystal  output / PGA right channel positive input /  GPIO PC[2] |

| 31  | PWM1/UART_RX/I2C_SCK/XC32K_<br>I/PGA_N1/PC<3>                  | Digital I/O | PWM1 output / UART_RX / I2C serial clock /<br>(optional) 32kHz crystal input / PGA right<br>channel negative input / GPIO PC[3]              |

| 32  | PWM2/UART_CTS/PWM0_N/<br>sar_aio<8>/PC<4>                      | Digital I/O | PWM2 output / UART_CTS / PWM0 inverting<br>output / SAR ADC input / GPIO PC[4]                                                               |

| 33  | PWM3_N/UART_RX/ATSELO/<br>sar_aio<9>/PC<5>                     | Digital I/O | PWM3 inverting output / UART_RX / Antenna<br>select pin 0 / SAR ADC input / GPIO PC[5]                                                       |

| 34  | RX_CYC2LNA/ATSEL1/PWM4_N/<br>PC<6>                             | Digital I/O | Control external LNA / Antenna select pin 1 /<br>PWM4 inverting output / GPIO PC[6]                                                          |

| 35  | TX_CYC2PA/ATSEL2/PWM5_N/<br>PC<7>                              | Digital I/O | Control external PA / Antenna select pin 2 /<br>PWM5 inverting output / GPIO PC[7]                                                           |

| 36  | RESETB                                                         | RESET       | Power on reset, active low                                                                                                                   |

| 37  | VANT                                                           | PWR         | Internally generated voltage output to bias<br>internal PA. Connect to ANT using an external<br>inductor.                                    |

| 38  | ANT                                                            | Analog      | RF antenna, connect to VANT using external inductor                                                                                          |

| 39  | AVDD1V2                                                        | PWR         | Power supply input for internal RF Modules. Route from VDD1V2. Connect to GND via external capacitor.                                        |

| 40  | XC1                                                            | Analog      | Connect 24MHz crystal                                                                                                                        |

| 41  | XC2                                                            | Analog      | Connect 24MHz crystal                                                                                                                        |

Rev: 00

| No. | Pin Name                                   | Туре        | Description                                                                             |

|-----|--------------------------------------------|-------------|-----------------------------------------------------------------------------------------|

| 42  | RX_CYC2LNA/7816_TRX<br>(UART_TX)/PD<0>     | Digital I/O | Control external LNA / UART 7816 TRX<br>(UART_TX) / GPIO PD[0]                          |

| 43  | TX_CYC2PA/UART_CTS/PD<1>                   | Digital I/O | Control external PA / UART_CTS / GPIO PD[1]                                             |

| 44  | SPI_CN/I2S_LR/PWM3/PD<2>                   | Digital I/O | SPI chip select (Active low) / I2S left right channel select / PWM3 output / GPIO PD[2] |

| 45  | PWM1_N/I2S_SDI/7816_TRX<br>(UART_TX)/PD<3> | Digital I/O | PWM1 inverting output / I2S serial data input<br>/ UART 7816 TRX (UART_TX) / GPIO PD[3] |

| 46  | SWM/I2S_SDO/PWM2_N/<br>PD<4>               | Digital I/O | Single wire master / I2S serial data output /<br>PWM2 inverting output / GPIO PD[4]     |

| 47  | PWM0/PWM0_N/PD<5>                          | Digital I/O | PWM0 output / PWM0 inverting output /<br>GPIO PD[5]                                     |

| 48  | CN/UART_RX/ATSELO/PD<6>                    | Digital I/O | SPI chip select (Active low) / UART_RX / Antenna select pin 0 / GPIO PD[6]              |

# 5. Module Placement Recommendations

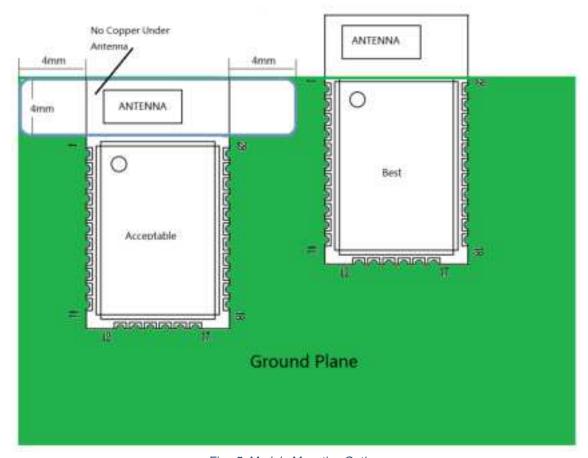

Fig. 5. Module Mounting Options

Rev: 00

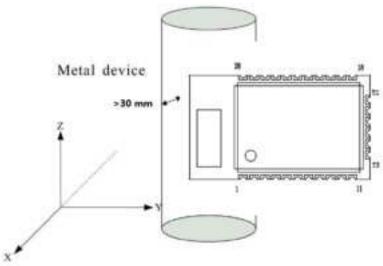

# 6. Effect of Metals Nearby

Another significant source of issues for RF is the presence of metal near the antenna. Metal also produces an effect on the electric field and change the radiation pattern or create nulls where no signal is received. Any nearby metal may affect the antenna significantly and reduce the range. It's therefore critical to keep any metal way at least 30mm from the module. Your design should place any metal as far away as possible

Leave 30mm Clearance Space from the Module Built-in Antenna

Fig. 6. Keep Any Metal Away At Least 30mm From The Module

# 7. Recommended Operating Conditions

The operating conditions are the physical parameters that the chip can operate within

| Symbol   | Parameter                                 | Min | Nom | Max | Unit       |

|----------|-------------------------------------------|-----|-----|-----|------------|

| VDD      | Supply voltage independent of DCDC enable | 1.7 | 3   | 3.6 | V          |

| t(R_VDD) | Supply rise time (ov to 1.7V)             |     |     | 60  | ms         |

| TA       | Operating temperature                     | -40 | 25  | 85  | $^{\circ}$ |

Rev: 00

## 8. Model Information

# 9. Warning

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions:

- (1) This device may not cause harmful interference.

- (2) This device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause

harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- —Reorient or relocate the receiving antenna.

- —Increase the separation between the equipment and receiver.

- —Connect the equipment into an

- outlet on a circuit different from that to which the receiver is connected.

- —Consult the dealer or an experienced radio/TV technician for help.

MODIFICATION: Any changes or modifications not expressly approved by the grantee of this device could void the user's authority to operate the device.

To satisfy FCC exterior labeling requirements, the following text must be placed on the exterior of the end product. "Contains Transmitter module FCC ID: 2A979GCC-BTM002S