# External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP User Guide

Updated for Intel® Quartus® Prime Design Suite: 23.1

IP Version: 3.0.0

ID: **772538**

Version: 2023.04.03

# **Contents**

| 1. | About the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP          |    |

|----|--------------------------------------------------------------------------------|----|

| 2  | Intel Agilex 7 M-Series FPGA EMIF IP - Introduction                            |    |

|    | 2.1. Intel Agilex 7 M-Series EMIF IP Protocol and Feature Support              |    |

|    | 2.2. Intel Agilex 7 M-Series EMIF IP Protocol and reactive Support             |    |

|    | 2.3. Intel Agilex 7 M-Series EMIF IP Design Checklist                          |    |

| _  |                                                                                |    |

| 3. | Intel Agilex 7 M-Series FPGA EMIF IP – Product Architecture                    |    |

|    | 3.1. Intel Agilex 7 M-Series EMIF Architecture: Introduction                   |    |

|    | 3.1.1. Intel Agilex 7 M-Series EMIF Architecture: I/O Subsystem                |    |

|    | 3.1.2. Intel Agilex 7 M-Series EMIF Architecture: I/O SSM                      |    |

|    | 3.1.3. Intel Agilex 7 M-Series EMIF Architecture: I/O Bank                     |    |

|    | 3.1.4. Intel Agilex 7 M-Series EMIF Architecture: I/O Lane                     |    |

|    | 3.1.5. Intel Agilex 7 M-Series EMIF Architecture: Input DQS Clock Tree         |    |

|    | 3.1.6. Intel Agilex 7 M-Series EMIF Architecture: PHY Clock Tree               |    |

|    | 3.1.7. Intel Agilex 7 M-Series EMIF Architecture: PLL Reference Clock Networks |    |

|    | 3.1.8. Intel Agilex 7 M-Series EMIF Architecture: Clock Phase Alignment        |    |

|    | 3.2. Intel Agilex 7 M-Series EMIF Sequencer                                    |    |

|    | 3.2.1. Intel Agilex 7 M-Series Mailbox Structure and Register Definitions      |    |

|    | 3.3. Intel Agilex 7 M-Series EMIF Controller                                   |    |

|    | 3.3.1. Hard Memory Controller                                                  | 30 |

| 4. | Intel Agilex 7 M-Series FPGA EMIF IP - End-User Signals                        |    |

|    | 4.1. Intel Agilex 7 M-Series EMIF IP for DDR4 Interfaces                       |    |

|    | 4.1.1. ref_clk for EMIF                                                        | 33 |

|    | 4.1.2. core_init_n for EMIF                                                    |    |

|    | 4.1.3. usr_async_clk for EMIF                                                  |    |

|    | 4.1.4. usr_clk for EMIF                                                        |    |

|    | 4.1.5. usr_rst_n for EMIF                                                      |    |

|    | 4.1.6. s0_axi4 for EMIF                                                        |    |

|    | 4.1.7. mem for EMIF                                                            |    |

|    | 4.1.8. oct for EMIF                                                            |    |

|    | 4.1.9. s0_axil_clk for EMIF                                                    |    |

|    | 4.1.10. s0_axil_rst_n for EMIF                                                 |    |

|    | 4.1.11. s0_axil for EMIF                                                       |    |

|    | 4.2. Intel Agilex 7 M-Series EMIF IP for DDR5 Interfaces                       |    |

|    | 4.2.1. ref_clk for EMIF                                                        |    |

|    | 4.2.2. core_init_n for EMIF                                                    |    |

|    | 4.2.3. usr_async_clk for EMIF                                                  |    |

|    | 4.2.4. usr_clk for EMIF                                                        |    |

|    | 4.2.5. usr_rst_n for EMIF                                                      |    |

|    | 4.2.6. s0_axi4 for EMIF                                                        |    |

|    | 4.2.7. mem for EMIF                                                            |    |

|    | 4.2.8. oct for EMIF                                                            |    |

|    | 4.2.9. s0_axil_clk for EMIF                                                    |    |

|    | 4.2.10. s0_axil_rst_n for EMIF                                                 |    |

|    | 4.2.11. s0 axil for EMIF                                                       | 42 |

|            | 4.3. Intel Agilex 7 M-Series EMIF IP for LPDDR5 Interfaces                                           |     |

|------------|------------------------------------------------------------------------------------------------------|-----|

|            | 4.3.1. ref_clk for EMIF                                                                              | 43  |

|            | 4.3.2. core_init_n for EMIF                                                                          | 43  |

|            | 4.3.3. usr_async_clk for EMIF                                                                        | 43  |

|            | 4.3.4. usr_clk for EMIF                                                                              | 44  |

|            | 4.3.5. usr_rst_n for EMIF                                                                            | 44  |

|            | 4.3.6. s0_axi4 for EMIF                                                                              | 44  |

|            | 4.3.7. mem for EMIF                                                                                  | 45  |

|            | 4.3.8. oct for EMIF                                                                                  | 46  |

|            | 4.3.9. s0_axil_clk for EMIF                                                                          | 46  |

|            | 4.3.10. s0_axil_rst_n for EMIF                                                                       | 46  |

|            | 4.3.11. s0_axil for EMIF                                                                             | 47  |

| <b>.</b> . | ntel Agilex 7 M-Series FPGA EMIF IP – Simulating Memory IP                                           | 10  |

| J. 1       |                                                                                                      |     |

|            | 5.1. Simulation Walkthrough                                                                          |     |

|            | 5.1.1. Calibration                                                                                   |     |

|            | 5.1.2. Simulation Scripts                                                                            |     |

|            | 5.1.3. Functional Simulation with Verilog HDL                                                        |     |

|            | 5.1.4. Simulating the Design Example                                                                 |     |

| 6. I       | ntel Agilex 7 M-Series FPGA EMIF IP – DDR4 Support                                                   | 52  |

|            | 6.1. Intel Agilex 7 M-Series FPGA EMIF IP Parameters for DDR4                                        |     |

|            | 6.1.1. Intel Agilex 7 M-Series FPGA EMIF Memory Device Description IP (DDR4)                         |     |

|            | Parameter Descriptions                                                                               | 52  |

|            | 6.1.2. Intel Agilex 7 M-Series FPGA EMIF IP Parameter Descriptions (DDR4)                            |     |

|            | 6.2. Intel Agilex 7 M-Series FPGA EMIF IP Pin and Resource Planning                                  | 59  |

|            | 6.2.1. Intel Agilex 7 M-Series FPGA EMIF IP Interface Pins                                           |     |

|            | 6.2.2. Intel Agilex 7 M-Series FPGA EMIF IP Resources                                                |     |

|            | 6.2.3. Pin Guidelines for Intel Agilex 7 M-Series FPGA EMIF IP                                       | 62  |

|            | 6.2.4. Pin Placements for Intel Agilex 7 M-Series FPGA DDR4 EMIF IP                                  | 63  |

|            | 6.3. DDR4 Board Design Guidelines                                                                    | 71  |

|            | 6.3.1. Terminations for DDR4 with Intel Agilex 7 M-Series Devices                                    | 72  |

|            | 6.3.2. General Layout Routing Guidelines                                                             | 73  |

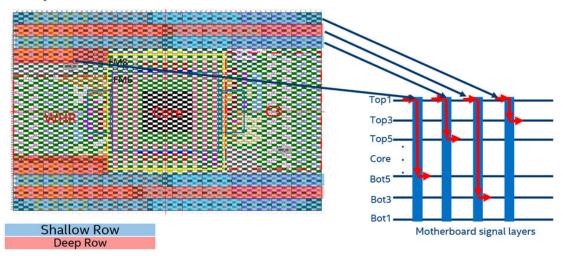

|            | 6.3.3. Reference Stackup                                                                             | 77  |

|            | 6.3.4. Intel Agilex 7 M-Series EMIF-Specific Routing Guidelines for Various DDR4                     |     |

|            | Topologies                                                                                           |     |

|            | 6.3.5. DDR4 Routing Guidelines: Discrete (Component) Topologies                                      | 83  |

| 7 1        | intel Agilex 7 M-Series FPGA EMIF IP – DDR5 Support                                                  | 97  |

| <i>,</i>   | 7.1. Intel Agilex 7 M-Series FPGA EMIF IP Parameters for DDR5                                        |     |

|            |                                                                                                      | 97  |

|            | 7.1.1. Intel Agilex 7 M-Series FPGA EMIF Memory Device Description IP (DDR5)  Parameter Descriptions | 97  |

|            | 7.1.2. Intel Agilex 7 M-Series FPGA EMIF IP Parameter Descriptions (DDR5)                            |     |

|            | 7.1.2. Intel Agilex 7 M-Series FPGA EMIF IP Parameter Descriptions (DDRS)                            |     |

|            | 7.2.1 Intel Agilex 7 M-Series FPGA EMIF IP Fill and Resource Planning                                |     |

|            | 7.2.1. Intel Agilex 7 M-Series FPGA EMIF IP Interface Firs                                           |     |

|            | 7.2.3. Pin Guidelines for Intel Agilex 7 M-Series FPGA EMIF IP                                       |     |

|            | 7.2.3. Fill Guidelines for Triter Agriex / M-Series Froa EMIF IP                                     | 100 |

| 8. 1       | ntel Agilex 7 M-Series FPGA EMIF IP – LPDDR5 Support                                                 | 113 |

|            | 8.1. Intel Agilex 7 M-Series FPGA EMIF IP Parameters for LPDDR5                                      | 113 |

|            | 8.1.1. Intel Agilex 7 M-Series FPGA EMIF Memory Device Description IP                                |     |

|            | (LPDDR5) Parameter Descriptions                                                                      | 113 |

|            |                                                                                                      |     |

| 8.1.2. Intel Agilex 7 M-Series FPGA External Memory Interfaces (EMIF) IP       | 110  |

|--------------------------------------------------------------------------------|------|

| Parameter Descriptions for LPDDR5                                              |      |

| 8.2. Intel Agilex 7 M-Series FPGA EMIF IP Pin and Resource Planning            |      |

| 8.2.1. Intel Agilex 7 M-Series FPGA EMIF IP Interface Pins                     |      |

| 8.2.2. Intel Agilex 7 M-Series FPGA EMIF IP Resources                          |      |

| 8.2.3. PIN Guidelines for Intel Agriex / M-Series FPGA EMIF IP                 | 125  |

| 9. Intel Agilex 7 M-Series FPGA EMIF IP - Timing Closure                       | 128  |

| 9.1. Timing Closure                                                            | 128  |

| 9.1.1. Timing Analysis                                                         |      |

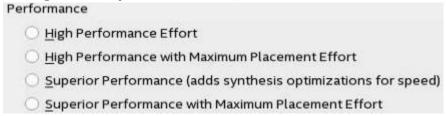

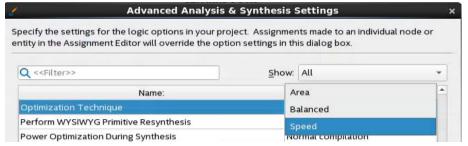

| 9.2. Optimizing Timing                                                         | 129  |

| 10. Intel Agilex 7 M-Series FPGA EMIF IP – Controller Optimization             | 131  |

| 10.1. Interface Standard                                                       |      |

| 10.2. Bank Management Efficiency                                               |      |

| 10.3. Data Transfer                                                            |      |

| 10.4. Improving Controller Efficiency                                          |      |

| 10.4.1. Frequency of Operation                                                 |      |

| 10.4.2. Series of Reads or Writes                                              |      |

| 11. Intel Agilex 7 M-Series FPGA EMIF IP – Debugging                           | 134  |

| 11.1. Interface Configuration Performance Issues                               |      |

| 11.1.1. Interface Configuration Bottleneck and Efficiency Issues               |      |

| 11.2. Functional Issue Evaluation.                                             |      |

| 11.2.1. Intel IP Memory Model                                                  | 135  |

| 11.2.2. Vendor Memory Model                                                    | 136  |

| 11.2.3. Transcript Window Messages                                             | 136  |

| 11.3. Timing Issue Characteristics                                             |      |

| 11.3.1. Evaluating FPGA Timing Issues                                          | 138  |

| 11.3.2. Evaluating External Memory Interface Timing Issues                     | 139  |

| 11.4. Verifying Memory IP Using the Signal Tap Logic Analyzer                  | 140  |

| 11.5. Generating Traffic with the Test Engine IP                               | 140  |

| 12. Document Revision History for External Memory Interfaces Intel Agilex 7 M- |      |

| Sories EDGA TD User Guide                                                      | 1/12 |

# 1. About the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

#### 1.1. Release Information

IP versions are the same as the Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

The IP version (X.Y.Z) number may change from one Intel Quartus Prime software version to another. A change in:

- X indicates a major revision of the IP. If you update your Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

#### Table 1.

| Item                | Description |

|---------------------|-------------|

| IP Version          | 3.0.0       |

| Intel Quartus Prime | 23.1        |

| Release Date        | 2023.04.03  |

*Note:* This documentation is preliminary and subject to change.

Notice:

Device support for Intel Agilex<sup>®</sup> 7 M-series FPGAs and SoCs in the Intel Quartus Prime Pro Edition software version 23.1 is restricted. To enable M-series device support in your instance of the Intel Quartus Prime Pro Edition software, contact your regional Intel FPGA sales representative.

# 2. Intel Agilex 7 M-Series FPGA EMIF IP - Introduction

Intel's fast, efficient, and low-latency external memory interface (EMIF) intellectual property (IP) cores interface with today's higher speed memory devices.

You can implement the EMIF IP core functions through the Intel Quartus Prime software.

The External Memory Interfaces Intel Agilex 7 M-Series FPGA IP (referred to hereafter as the Intel Agilex 7 M-Series EMIF IP) provides the following components:

- A physical layer interface (PHY) which builds the data path and manages timing transfers between the FPGA and the memory device.

- A memory controller which implements all the memory commands and protocollevel requirements.

For information on the maximum speeds supported by the external memory interface IP, refer to the *External Memory Interface Spec Estimator*, available here: https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/external-memory-interfaces-support/emif.html.

# 2.1. Intel Agilex 7 M-Series EMIF IP Protocol and Feature Support

- The Intel Agilex 7 M-Series FPGA EMIF IP supports DDR4 with hard memory controller and hard PHY.

- The Intel Agilex 7 M-Series FPGA EMIF IP supports DDR5 with hard memory controller and hard PHY.

- The Intel Agilex 7 M-Series FPGA EMIF IP supports LPDDR5 with hard memory controller and hard PHY.

# 2.2. Intel Agilex 7 M-Series EMIF IP Design Flow

Intel recommends creating an example top-level file with the desired pin outs and all interface IPs instantiated. This enables the Intel Quartus Prime software to validate the design and resource allocation before PCB and schematic sign off.

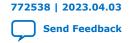

The following figure shows the design flow to provide the fastest out-of-the-box experience with the EMIF IP.

Figure 1. EMIF IP Design Flow

# 2.3. Intel Agilex 7 M-Series EMIF IP Design Checklist

Refer to the following checklist as a quick reference for information about steps in the EMIF design flow.

# **Table 2. EMIF Design Checklist**

| Design Step                            | Description                                                                                                                                                                                                                                                                                           | Resources                                                                                                                                              |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select an FPGA                         | Not all Intel FPGAs support all memory types and configurations. To help with the FPGA selection process, refer to the resources listed in the right column.                                                                                                                                          | External Memory Interfaces Support<br>Center     External Memory Interface Spec<br>Estimator                                                           |

| Parameterize the IP                    | Correct IP parameterization is important for good EMIF IP operation. The resources listed in the right column define the memory parameters during IP generation.                                                                                                                                      | DDR4 Parameter Descriptions     DDR5 Parameter Descriptions     LPDDR5 Parameter Descriptions                                                          |

| Generate initial IP and example design | After you have parameterized the EMIF IP, you can generate the IP, along with an optional example design. Refer to the Quick-Start Guide for a walkthrough of this process.                                                                                                                           | External Memory Interfaces Intel Agilex<br>7 M-Series FPGA IP Design Example<br>User Guide                                                             |

| Perform functional simulation          | Simulation of the EMIF design helps to determine correct operation. The resources listed in the right column explain how to perform simulation and what differences exist between simulation and hardware implementation.                                                                             | External Memory Interfaces Intel Agilex     7 M-Series FPGA IP Design Example     User Guide     Simulating Memory IP                                  |

| Make pin assignments                   | For guidance on pin placement, refer to the resources listed in the right column.                                                                                                                                                                                                                     | <ul> <li>DDR4 Parameter Descriptions</li> <li>DDR5 Parameter Descriptions</li> <li>LPDDR5 Parameter Descriptions</li> <li>Device Pin Tables</li> </ul> |

| Perform board simulation               | Board simulation helps determine optimal settings for signal integrity, drive strength, as well as sufficient timing margins and eye openings. For guidance on board simulation, refer to the resources listed in the right column.                                                                   | Board Design Guidelines     Timing Closure                                                                                                             |

| Verify timing closure                  | For information regarding compilation, system-<br>level timing closure and timing reports refer to<br>the Timing Closure section of this User Guide.                                                                                                                                                  | Timing Closure                                                                                                                                         |

| Run the design on<br>hardware          | For instructions on how to program a FPGA refer to the Quick-Start section of the Design Example User Guide.                                                                                                                                                                                          | External Memory Interfaces Intel Agilex     7 M-Series FPGA IP Design Example     User Guide                                                           |

| Debug issues with preceding steps      | Operational problems can generally be attributed to one of the following: interface configuration, pin/resource planning, signal integrity, or timing. The resources listed in the right column contain information on typical debug procedures and available tools to help diagnose hardware issues. | Debugging     External Memory Interfaces Support Center                                                                                                |

# 3. Intel Agilex 7 M-Series FPGA EMIF IP – Product Architecture

This chapter describes the Intel Agilex 7 M-Series FPGA EMIF IP product architecture.

# 3.1. Intel Agilex 7 M-Series EMIF Architecture: Introduction

The Intel Agilex 7 M-Series EMIF architecture contains many new hardware features designed to meet the high-speed requirements of emerging memory protocols, while consuming the smallest amount of core logic area and power.

Note:

The current version of the External Memory Interfaces Intel Agilex 7 M-Series FPGA IP supports the DDR4, DDR5, and LPDDR5 memory protocols.

The following are key hardware features of the Intel Agilex 7 M-Series EMIF architecture:

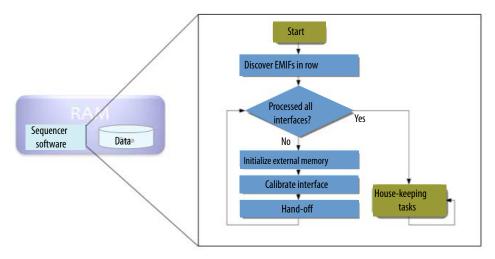

#### **Hard Sequencer**

The sequencer employs a hard Nios<sup>®</sup> II processor, and can perform memory calibration for a wide range of protocols. For Intel Agilex 7 M-Series devices, the sequencer and calibration are localized to each I/O bank.

Note:

You cannot use the hard Nios II processor for any user applications after calibration is complete.

#### **Hard PHY**

The PHY circuitry in Intel Agilex 7 M-Series devices is hardened in the silicon, which simplifies the challenges of achieving timing closure and minimizing power consumption.

#### **Hard Memory Controller**

The hard memory controller reduces latency and minimizes core logic consumption in the external memory interface. The hard memory controller supports the DDR4, DDR5, and LPDDR5 memory protocols.

#### **High-Speed PHY Clock Tree**

Dedicated high speed PHY clock networks clock the I/O buffers in Intel Agilex 7 M-Series EMIF IP. The PHY clock trees exhibit low jitter and low duty cycle distortion, maximizing the data valid window.

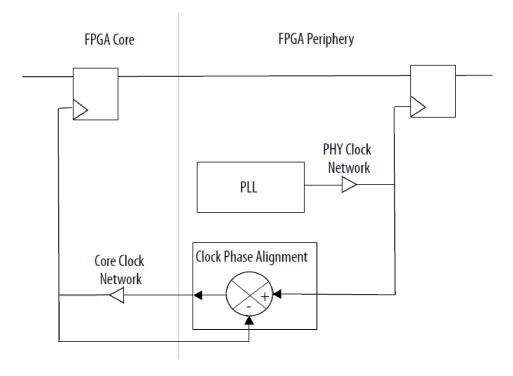

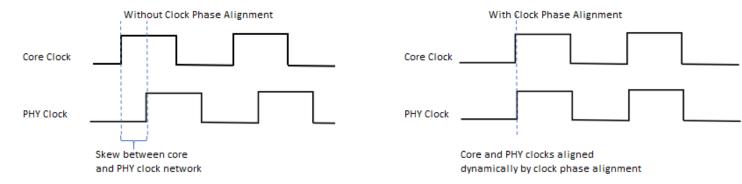

#### **Automatic Clock Phase Alignment**

Automatic clock phase alignment circuitry dynamically adjusts the clock phase of core clock networks to match the clock phase of the PHY clock networks. The clock phase alignment circuitry minimizes clock skew that can complicate timing closure in transfers between the FPGA core and the periphery.

#### Network-on-Chip (NoC) Interface

The Intel Agilex 7 M-Series EMIF IP supports a new Network-on-Chip (NoC) interface. Each IO96 bank contains two 256-bit AXI4 targets and one 32-bit AXI4-Lite target that connect to the NoC. NoC segments span one FPGA clock sector and consists of three AXI4 initiators on the FPGA fabric side. A network of switches transfer packets horizontally across the high-speed interconnect NoC and connect the initiators and targets. Refer to the *NoC User Guide* for additional information.

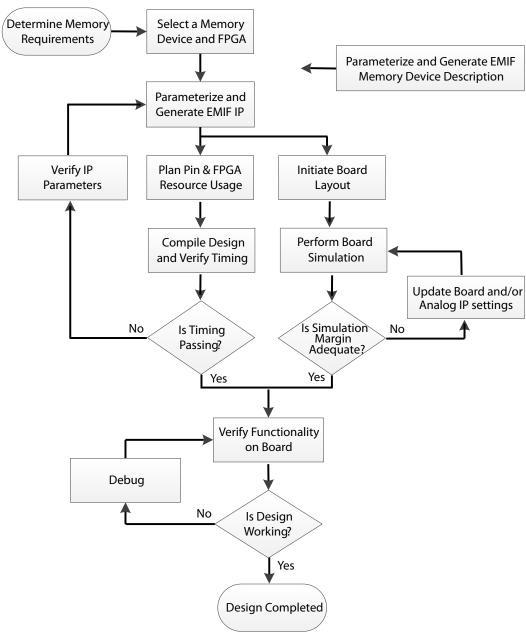

#### 3.1.1. Intel Agilex 7 M-Series EMIF Architecture: I/O Subsystem

In Intel Agilex 7 M-Series devices, the I/O subsystem consists of two rows at the edge of the core.

The I/O subsystem provides the following features:

- General-purpose I/O registers and I/O buffers

- · Compensation Block (Comp block)

- On-chip termination control (OCT)

- I/O PLLs

- I/O Bank I/O PLL for external memory interfaces and user logic

- Fabric-feeding for non-EMIF/non-LVDS SERDES IP applications

- True differential signaling

- External memory interface components, as follows:

- A Primary hard memory controller, which has connectivity to 8 lanes (up to 4 byte lanes for data, and optionally one additional lane for out-of-band ECC data)

- A Secondary hard memory controller, which has connectivity to 4 lanes (up to 2 byte lanes for data)

- Hard PHY

- Hard Nios processor and calibration logic

- DLL

#### 3.1.2. Intel Agilex 7 M-Series EMIF Architecture: I/O SSM

Each I/O bank includes one I/O subsystem manager (I/O SSM), which contains a hardened Nios II processor with dedicated memory. The I/O SSM is responsible for calibration of all the EMIFs in the I/O bank.

The I/O SSM includes dedicated memory which stores both the calibration algorithm and calibration run-time data. The hardened Nios II processor and the dedicated memory can be used only by an external memory interface, and cannot be employed for any other use.

The on-chip configuration network clocks the I/O SSM, and therefore the I/O SSM does not consume a PLL.

Each EMIF instance must be connected to the I/O SSM through the External Memory Interfaces Calibration IP. The Calibration IP exposes a calibration bus master port, which must be connected to the slave calibration bus port on every EMIF instance.

# 3.1.3. Intel Agilex 7 M-Series EMIF Architecture: I/O Bank

Each I/O row contains up to four I/O banks; the exact number of banks depends on device size and pin package.

Each I/O bank consists of two sub-banks, and each sub-bank contains the following components:

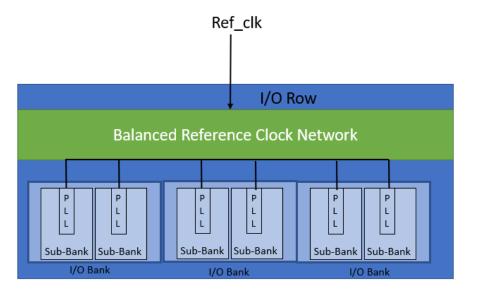

- I/O PLL and PHY clock trees

- DLL

- Input DQS clock trees

- 48 pins, organized into four I/O lanes of 12 pins each

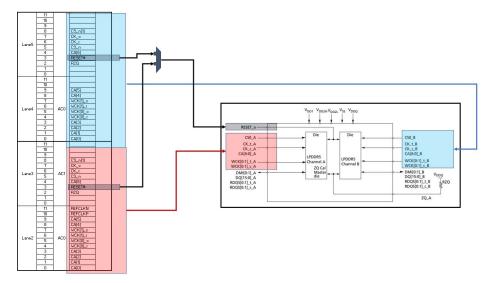

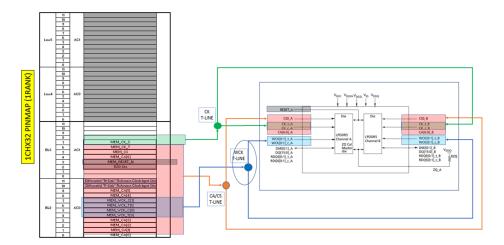

Figure 3. I/O Bank Architecture in Intel Agilex 7 M-Series Devices

Within an I/O bank, the top sub-bank is pin indexes P95:P48, and the bottom sub-bank is pin indexes P47:P0.

Intel Agilex 7 M-Series devices have two hard memory controllers: primary and secondary. The primary hard memory controller has access to all 96 pins in an I/O bank. The secondary hard memory controller has access only to the top sub-bank. In the above figure, the yellow signals highlight the connections for the secondary hard

memory controller, while the red signals show the connections for the primary hard memory controller. The green signals show where both hard memory controllers are bypassed to provide access to the PHY from the core logic.

#### 3.1.3.1. DDR4 Pin Placement

Table 3. DDR4 Pin Placement

| Lane Number Pin Index |    | x32+ECC *    | x 32         | x16 + ECC *  | <b>x16</b> |

|-----------------------|----|--------------|--------------|--------------|------------|

| BL7                   | 95 | MEM_DQ[39]*  |              |              |            |

|                       | 94 | MEM_DQ[38] * |              |              |            |

|                       | 93 | MEM_DQ[37] * |              |              |            |

|                       | 92 | MEM_DQ[36] * |              |              |            |

|                       | 91 |              |              |              |            |

|                       | 90 | MEM_DM_N[4]  |              |              |            |

|                       | 89 | MEM_DQS_C[4] |              |              |            |

|                       | 88 | MEM_DQS_T[4] |              |              |            |

|                       | 87 | MEM_DQ[35] * |              |              |            |

|                       | 86 | MEM_DQ[34] * |              |              |            |

|                       | 85 | MEM_DQ[33] * |              |              |            |

|                       | 84 | MEM_DQ[32] * |              |              |            |

| BL6                   | 83 | MEM_DQ[31]   | MEM_DQ[31]   |              |            |

|                       | 82 | MEM_DQ[30]   | MEM_DQ[30]   |              |            |

|                       | 81 | MEM_DQ[29]   | MEM_DQ[29]   |              |            |

|                       | 80 | MEM_DQ[28]   | MEM_DQ[28]   |              |            |

|                       | 79 |              |              |              |            |

|                       | 78 | MEM_DM_N[3]  | MEM_DM_N[3]  |              |            |

|                       | 77 | MEM_DQS_C[3] | MEM_DQS_C[3] |              |            |

|                       | 76 | MEM_DQS_T[3] | MEM_DQS_T[3] |              |            |

|                       | 75 | MEM_DQ[27]   | MEM_DQ[27]   |              |            |

|                       | 74 | MEM_DQ[26]   | MEM_DQ[26]   |              |            |

|                       | 73 | MEM_DQ[25]   | MEM_DQ[25]   |              |            |

|                       | 72 | MEM_DQ[24]   | MEM_DQ[24]   |              |            |

| BL5                   | 71 | MEM_DQ[23]   | MEM_DQ[23]   | MEM_DQ[23] * |            |

|                       | 70 | MEM_DQ[22]   | MEM_DQ[22]   | MEM_DQ[22] * |            |

|                       | 69 | MEM_DQ[21]   | MEM_DQ[21]   | MEM_DQ[21] * |            |

|                       | 68 | MEM_DQ[20]   | MEM_DQ[20]   | MEM_DQ[20] * |            |

|                       | 67 |              |              |              |            |

|                       | 66 | MEM_DM_N[2]  | MEM_DM_N[2]  | MEM_DM_N[2]  |            |

| Lane Number | Pin Index | x32+ECC *                                               | x 32                                                    | x16 + ECC *                                             | x16                                                     |

|-------------|-----------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

|             | 65        | MEM_DQS_C[2]                                            | MEM_DQS_C[2]                                            | MEM_DQS_C[2]                                            |                                                         |

|             | 64        | MEM_DQS_T[2]                                            | MEM_DQS_T[2]                                            | MEM_DQS_T[2]                                            |                                                         |

|             | 63        | MEM_DQ[19]                                              | MEM_DQ[19]                                              | MEM_DQ[19] *                                            |                                                         |

|             | 62        | MEM_DQ[18]                                              | MEM_DQ[18]                                              | MEM_DQ[18] *                                            |                                                         |

|             | 61        | MEM_DQ[17]                                              | MEM_DQ[17]                                              | MEM_DQ[17] *                                            |                                                         |

|             | 60        | MEM_DQ[16]                                              | MEM_DQ[16]                                              | MEM_DQ[16] *                                            |                                                         |

| BL4         | 59        | MEM_DQ[15]                                              | MEM_DQ[15]                                              | MEM_DQ[15]                                              | MEM_DQ[15]                                              |

|             | 58        | MEM_DQ[14]                                              | MEM_DQ[14]                                              | MEM_DQ[14]                                              | MEM_DQ[14]                                              |

|             | 57        | MEM_DQ[13]                                              | MEM_DQ[13]                                              | MEM_DQ[13]                                              | MEM_DQ[13]                                              |

|             | 56        | MEM_DQ[12]                                              | MEM_DQ[12]                                              | MEM_DQ[12]                                              | MEM_DQ[12]                                              |

|             | 55        |                                                         |                                                         |                                                         |                                                         |

|             | 54        | MEM_DM_N[1]                                             | MEM_DM_N[1]                                             | MEM_DM_N[1]                                             | MEM_DM_N[1]                                             |

|             | 53        | MEM_DQS_C[1]                                            | MEM_DQS_C[1]                                            | MEM_DQS_C[1]                                            | MEM_DQS_C[1]                                            |

|             | 52        | MEM_DQS_T[1]                                            | MEM_DQS_T[1]                                            | MEM_DQS_T[1]                                            | MEM_DQS_T[1]                                            |

|             | 51        | MEM_DQ[11]                                              | MEM_DQ[11]                                              | MEM_DQ[11]                                              | MEM_DQ[11]                                              |

|             | 50        | MEM_DQ[10]                                              | MEM_DQ[10]                                              | MEM_DQ[10]                                              | MEM_DQ[10]                                              |

|             | 49        | MEM_DQ[9]                                               | MEM_DQ[9]                                               | MEM_DQ[9]                                               | MEM_DQ[9]                                               |

|             | 48        | MEM_DQ[8]                                               | MEM_DQ[8]                                               | MEM_DQ[8]                                               | MEM_DQ[8]                                               |

| BL3         | 47        | MEM_BG[0]                                               | MEM_BG[0]                                               | MEM_BG[0]                                               | MEM_BG[0]                                               |

|             | 46        | MEM_BA[1]                                               | MEM_BA[1]                                               | MEM_BA[1]                                               | MEM_BA[1]                                               |

|             | 45        | MEM_BA[0]                                               | MEM_BA[0]                                               | MEM_BA[0]                                               | MEM_BA[0]                                               |

|             | 44        | MEM_A[17]                                               | MEM_A[17]                                               | MEM_A[17]                                               | MEM_A[17]                                               |

|             | 43        | MEM_A[16]                                               | MEM_A[16]                                               | MEM_A[16]                                               | MEM_A[16]                                               |

|             | 42        | MEM_A[15]                                               | MEM_A[15]                                               | MEM_A[15]                                               | MEM_A[15]                                               |

|             | 41        | MEM_A[14]                                               | MEM_A[14]                                               | MEM_A[14]                                               | MEM_A[14]                                               |

|             | 40        | MEM_A[13]                                               | MEM_A[13]                                               | MEM_A[13]                                               | MEM_A[13]                                               |

|             | 39        | MEM_A[12]                                               | MEM_A[12]                                               | MEM_A[12]                                               | MEM_A[12]                                               |

|             | 38        | RZQ Site                                                | RZQ Site                                                | RZQ Site                                                | RZQ Site                                                |

|             | 37        | Differential "N-<br>Side" Reference<br>Clock Input Site |

|             | 36        | Differential "P-<br>Side" Reference<br>Clock Input Site |

| BL2         | 35        | MEM_A[11]                                               | MEM_A[11]                                               | MEM_A[11]                                               | MEM_A[11]                                               |

|             | 34        | MEM_A[10]                                               | MEM_A[10]                                               | MEM_A[10]                                               | MEM_A[10]                                               |

|             | 33        | MEM_A[9]                                                | MEM_A[9]                                                | MEM_A[9]                                                | MEM_A[9]                                                |

|             | 32        | MEM_A[8]                                                | MEM_A[8]                                                | MEM_A[8]                                                | MEM_A[8]                                                |

|             |           |                                                         |                                                         |                                                         | continued                                               |

| Lane Number | Pin Index | x32+ECC *      | x 32           | x16 + ECC *    | <b>x16</b>     |

|-------------|-----------|----------------|----------------|----------------|----------------|

|             | 31        | MEM_A[7]       | MEM_A[7]       | MEM_A[7]       | MEM_A[7]       |

|             | 30        | MEM_A[6]       | MEM_A[6]       | MEM_A[6]       | MEM_A[6]       |

|             | 29        | MEM_A[5]       | MEM_A[5]       | MEM_A[5]       | MEM_A[5]       |

|             | 28        | MEM_A[4]       | MEM_A[4]       | MEM_A[4]       | MEM_A[4]       |

|             | 27        | MEM_A[3]       | MEM_A[3]       | MEM_A[3]       | MEM_A[3]       |

|             | 26        | MEM_A[2]       | MEM_A[2]       | MEM_A[2]       | MEM_A[2]       |

|             | 25        | MEM_A[1]       | MEM_A[1]       | MEM_A[1]       | MEM_A[1]       |

|             | 24        | MEM_A[0]       | MEM_A[0]       | MEM_A[0]       | MEM_A[0]       |

| BL1         | 23        | MEM_PAR[0]     | MEM_PAR[0]     | MEM_PAR[0]     | MEM_PAR[0]     |

|             | 22        | MEM_CS_N[1]    | MEM_CS_N[1]    | MEM_CS_N[1]    | MEM_CS_N[1]    |

|             | 21        | MEM_CK_C[0]    | MEM_CK_C[0]    | MEM_CK_C[0]    | MEM_CK_C[0]    |

|             | 20        | MEM_CKT[0]     | MEM_CKT[0]     | MEM_CKT[0]     | MEM_CKT[0]     |

|             | 19        | MEM_CKE[1]     | MEM_CKE[1]     | MEM_CKE[1]     | MEM_CKE[1]     |

|             | 18        | MEM_CKE[0]     | MEM_CKE[0]     | MEM_CKE[0]     | MEM_CKE[0]     |

|             | 17        | MEM_ODT[1]     | MEM_ODT[1]     | MEM_ODT[1]     | MEM_ODT[1]     |

|             | 16        | MEM_ODT[0]     | MEM_ODT[0]     | MEM_ODT[0]     | MEM_ODT[0]     |

|             | 15        | MEM_ACT_N[0]   | MEM_ACT_N[0]   | MEM_ACT_N[0]   | MEM_ACT_N[0]   |

|             | 14        | MEN_CS_N[0]    | MEN_CS_N[0]    | MEN_CS_N[0]    | MEN_CS_N[0]    |

|             | 13        | MEM_RESET_N[0] | MEM_RESET_N[0] | MEM_RESET_N[0] | MEM_RESET_N[0] |

|             | 12        | MEM_BG[1]      | MEM_BG[1]      | MEM_BG[1]      | MEM_BG[1]      |

| BL0         | 11        | MEM_DQ[7]      | MEM_DQ[7]      | MEM_DQ[7]      | MEM_DQ[7]      |

|             | 10        | MEM_DQ[6]      | MEM_DQ[6]      | MEM_DQ[6]      | MEM_DQ[6]      |

|             | 9         | MEM_DQ[5]      | MEM_DQ[5]      | MEM_DQ[5]      | MEM_DQ[5]      |

|             | 8         | MEM_DQ[4]      | MEM_DQ[4]      | MEM_DQ[4]      | MEM_DQ[4]      |

|             | 7         |                |                |                |                |

|             | 6         | MEM_DM_N[0]    | MEM_DM_N[0]    | MEM_DM_N[0]    | MEM_DM_N[0]    |

|             | 5         | MEM_DQS_C[0]   | MEM_DQS_C[0]   | MEM_DQS_C[0]   | MEM_DQS_C[0]   |

|             | 4         | MEM_DQS_T[0]   | MEM_DQS_T[0]   | MEM_DQS_T[0]   | MEM_DQS_T[0]   |

|             | 3         | MEM_DQ[3]      | MEM_DQ[3]      | MEM_DQ[3]      | MEM_DQ[3]      |

|             | 2         | MEM_DQ[2]      | MEM_DQ[2]      | MEM_DQ[2]      | MEM_DQ[2]      |

|             | 1         | MEM_DQ[1]      | MEM_DQ[1]      | MEM_DQ[1]      | MEM_DQ[1]      |

|             | 0         | MEM_DQ[0]      | MEM_DQ[0]      | MEM_DQ[0]      | MEM_DQ[0]      |

3.1.3.2. DDR5 Pin Placement

Table 4. DDR5 Pin Placement

| Lane Number | Pin Index | x32+ECC *   | x 32 | 2ch x16                | x16 + ECC * | <b>x16</b> |

|-------------|-----------|-------------|------|------------------------|-------------|------------|

| BL7         | 95        |             |      | MEM_1_MEM_<br>DQ[15]   |             |            |

|             | 94        |             |      | MEM_1_MEM_<br>DQ[14]   |             |            |

|             | 93        |             |      | MEM_1_MEM_<br>DQ[13]   |             |            |

|             | 92        |             |      | MEM_1_MEM_<br>DQ[12]   |             |            |

|             | 91        |             |      |                        |             |            |

|             | 90        |             |      | MEM_1_MEM_<br>DM_N[1]  |             |            |

|             | 89        |             |      | MEM_1_MEM_<br>DQS_C[1] |             |            |

|             | 88        |             |      | MEM_1_MEM_<br>DQS_T[1] |             |            |

|             | 87        |             |      | MEM_1_MEM_<br>DQ[11]   |             |            |

|             | 86        |             |      | MEM_1_MEM_<br>DQ[10]   |             |            |

|             | 85        |             |      | MEM_1_MEM_<br>DQ[9]    |             |            |

|             | 84        |             |      | MEM_1_MEM_<br>DQ[8]    |             |            |

| BL6         | 83        | MEM_DQ[39]* |      | MEM_1_MEM_<br>DQ[7]    |             |            |

|             | 82        | MEM_DQ[38]* |      | MEM_1_MEM_<br>DQ[6]    |             |            |

|             | 81        | MEM_DQ[37]* |      | MEM_1_MEM_<br>DQ[5]    |             |            |

|             | 80        | MEM_DQ[36]* |      | MEM_1_MEM_<br>DQ[4]    |             |            |

|             | 79        |             |      |                        |             |            |

|             | 78        | MEM_DM_N[4] |      | MEM_1_MEM_<br>DM_N[0]  |             |            |

|             | 77        | MEM_DQS_C[4 |      | MEM_1_MEM_<br>DQS_C[0] |             |            |

|             | 76        | MEM_DQS_T[4 |      | MEM_1_MEM_<br>DQS_T[0] |             |            |

|             | 75        | MEM_DQ[35]* |      | MEM_1_MEM_<br>DQ[3]    |             |            |

|             | 74        | MEM_DQ[34]* |      | MEM_1_MEM_<br>DQ[2]    |             |            |

|             | 73        | MEM_DQ[33]* |      | MEM_1_MEM_<br>DQ[1]    |             |            |

| Lane Number | Pin Index | x32+ECC *   | x 32         | 2ch x16                                         | x16 + ECC *      | <b>x16</b> |

|-------------|-----------|-------------|--------------|-------------------------------------------------|------------------|------------|

|             | 72        | MEM_DQ[32]* |              | MEM_1_MEM_<br>DQ[0]                             |                  |            |

| BL5         | 71        | MEM_DQ[31]  | MEM_DQ[31]   | MEM_1_CK_C[<br>1]                               |                  |            |

|             | 70        | MEM_DQ[30]  | MEM_DQ[30]   | MEM_1_CK_T[<br>1]                               |                  |            |

|             | 69        | MEM_DQ[29]  | MEM_DQ[29]   | MEM_1_MEM_<br>CS_N[0]                           |                  |            |

|             | 68        | MEM_DQ[28]  | MEM_DQ[28]   | MEM_1_MEM_<br>CS_N[1]                           |                  |            |

|             | 67        |             |              | MEM_1_CK_C[<br>0]                               |                  |            |

|             | 66        | MEM_DM_N[3] | MEM_DM_N[3]  | MEM_1_CK_T[<br>0]                               |                  |            |

|             | 65        | MEM_DQS_C[3 | MEM_DQS_C[3  | MEM_1_MEM_<br>CA[12]                            |                  |            |

|             | 64        | MEM_DQS_T[3 | MEM_DQS_T[3] | MEM_1_MEM_<br>CA[11]                            |                  |            |

|             | 63        | MEM_DQ[27]  | MEM_DQ[27]   | MEM_1_RESET<br>_N                               |                  |            |

|             | 62        | MEM_DQ[26]  | MEM_DQ[26]   | OCT_1_OCT_R<br>ZQIN                             |                  |            |

|             | 61        | MEM_DQ[25]  | MEM_DQ[25]   | MEM_1_ALERT<br>_N                               |                  |            |

|             | 60        | MEM_DQ[24]  | MEM_DQ[24]   | MEM_1_MEM_<br>CA[10]                            |                  |            |

| BL4         | 59        | MEM_DQ[23]  | MEM_DQ[23]   | Differential "NSide" Reference Clock Input Site | MEM_DQ[23]*      |            |

|             | 58        | MEM_DQ[22]  | MEM_DQ[22]   | Differential "PSide" Reference Clock Input Site | MEM_DQ[22]*      |            |

|             | 57        | MEM_DQ[21]  | MEM_DQ[21]   | MEM_1_MEM_<br>CA[9]                             | MEM_DQ[21]*      |            |

|             | 56        | MEM_DQ[20]  | MEM_DQ[20]   | MEM_1_MEM_<br>CA[8]                             | MEM_DQ[20]*      |            |

|             | 55        |             |              | MEM_1_MEM_<br>CA[7]                             |                  |            |

|             | 54        | MEM_DM_N[2] | MEM_DM_N[2]  | MEM_1_MEM_<br>CA[6]                             | MEM_DM_N[2]      |            |

|             | 53        | MEM_DQS_C[2 | MEM_DQS_C[2] | MEM_1_MEM_<br>CA[5]                             | MEM_DQS_C[2      |            |

|             | 52        | MEM_DQS_T[2 | MEM_DQS_T[2] | MEM_1_MEM_<br>CA[4]                             | MEM_DQS_T[2<br>] |            |

|             |           |             |              |                                                 |                  | continued  |

| Lane Number | Pin Index | x32+ECC *                                                     | x 32                                                          | 2ch x16                                         | x16 + ECC *                                                   | x16                                                           |

|-------------|-----------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

|             | 51        | MEM_DQ[19]                                                    | MEM_DQ[19]                                                    | MEM_1_MEM_<br>CA[3]                             | MEM_DQ[19]*                                                   |                                                               |

|             | 50        | MEM_DQ[18]                                                    | MEM_DQ[18]                                                    | MEM_1_MEM_<br>CA[2]                             | MEM_DQ[18]*                                                   |                                                               |

|             | 49        | MEM_DQ[17]                                                    | MEM_DQ[17]                                                    | MEM_1_MEM_<br>CA[1]                             | MEM_DQ[17]*                                                   |                                                               |

|             | 48        | MEM_DQ[16]                                                    | MEM_DQ[16]                                                    | MEM_1_MEM_<br>CA[0]                             | MEM_DQ[16]*                                                   |                                                               |

| BL3         | 47        | MEM_CK_C[1]                                                   | MEM_CK_C[1]                                                   | MEM_0_CK_C[<br>1]                               | MEM_CK_C[1]                                                   | MEM_CK_C[1]                                                   |

|             | 46        | MEM_CK_T[1]                                                   | MEM_CK_T[1]                                                   | MEM_0_CK_T[<br>1]                               | MEM_CK_T[1]                                                   | MEM_CK_T[1]                                                   |

|             | 45        | MEM_CS_N[0]                                                   | MEM_CS_N[0]                                                   | MEM_0_MEM_<br>CS_N[0]                           | MEM_CS_N[0]                                                   | MEM_CS_N[0]                                                   |

|             | 44        | MEM_CS_N[1]                                                   | MEM_CS_N[1]                                                   | MEM_0_MEM_<br>CS_N[1]                           | MEM_CS_N[1]                                                   | MEM_CS_N[1]                                                   |

|             | 43        | MEM_CK_C[0]                                                   | MEM_CK_C[0]                                                   | MEM_0_CK_C[<br>0]                               | MEM_CK_C[0]                                                   | MEM_CK_C[0]                                                   |

|             | 42        | MEM_CK_T[0]                                                   | MEM_CK_T[0]                                                   | MEM_0_CK_T[<br>0]                               | MEM_CK_T[0]                                                   | MEM_CK_T[0]                                                   |

|             | 41        | MEM_CA[12]                                                    | MEM_CA[12]                                                    | MEM_0_MEM_<br>CA[12]                            | MEM_CA[12]                                                    | MEM_CA[12]                                                    |

|             | 40        | MEM_CA[11]                                                    | MEM_CA[11]                                                    | MEM_0_MEM_<br>CA[11]                            | MEM_CA[11]                                                    | MEM_CA[11]                                                    |

|             | 39        | MEM_RESET_<br>N[0]                                            | MEM_RESET_<br>N[0]                                            | MEM_0_RESET<br>_N                               | MEM_RESET_<br>N[0]                                            | MEM_RESET_<br>N[0]                                            |

|             | 38        | RZQ Site                                                      | RZQ Site                                                      | OCT_0_OCT_R<br>ZQIN                             | RZQ Site                                                      | RZQ Site                                                      |

|             | 37        | MEM_ALERT_<br>N[0]                                            | MEM_ALERT_<br>N[0]                                            | MEM_0_ALERT<br>_N                               | MEM_ALERT_<br>N[0]                                            | MEM_ALERT_<br>N[0]                                            |

|             | 36        | MEM_CA[10]                                                    | MEM_CA[10]                                                    | MEM_0_MEM_<br>CA[10]                            | MEM_CA[10]                                                    | MEM_CA[10]                                                    |

| BL2         | 35        | Differential "N-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "N-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "NSide" Reference Clock Input Site | Differential "N-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "N-<br>Side"<br>Reference<br>Clock Input<br>Site |

|             | 34        | Differential "P-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "P-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "PSide" Reference Clock Input Site | Differential "P-<br>Side"<br>Reference<br>Clock Input<br>Site | Differential "P-<br>Side"<br>Reference<br>Clock Input<br>Site |

|             | 33        | MEM_CA[9]                                                     | MEM_CA[9]                                                     | MEM_0_MEM_<br>CA[9]                             | MEM_CA[9]                                                     | MEM_CA[9]                                                     |

|             | 32        | MEM_CA[8]                                                     | MEM_CA[8]                                                     | MEM_0_MEM_<br>CA[8]                             | MEM_CA[8]                                                     | MEM_CA[8]                                                     |

|             | 31        | MEM_CA[7]                                                     | MEM_CA[7]                                                     | MEM_0_MEM_<br>CA[7]                             | MEM_CA[7]                                                     | MEM_CA[7]                                                     |

|             |           |                                                               |                                                               |                                                 |                                                               | continued                                                     |

| Lane Number | Pin Index | x32+ECC *    | x 32         | 2ch x16                | x16 + ECC *  | x16          |

|-------------|-----------|--------------|--------------|------------------------|--------------|--------------|

|             | 30        | MEM_CA[6]    | MEM_CA[6]    | MEM_0_MEM_<br>CA[6]    | MEM_CA[6]    | MEM_CA[6]    |

|             | 29        | MEM_CA[5]    | MEM_CA[5]    | MEM_0_MEM_<br>CA[5]    | MEM_CA[5]    | MEM_CA[5]    |

|             | 28        | MEM_CA[4]    | MEM_CA[4]    | MEM_0_MEM_<br>CA[4]    | MEM_CA[4]    | MEM_CA[4]    |

|             | 27        | MEM_CA[3]    | MEM_CA[3]    | MEM_0_MEM_<br>CA[3]    | MEM_CA[3]    | MEM_CA[3]    |

|             | 26        | MEM_CA[2]    | MEM_CA[2]    | MEM_0_MEM_<br>CA[2]    | MEM_CA[2]    | MEM_CA[2]    |

|             | 25        | MEM_CA[1]    | MEM_CA[1]    | MEM_0_MEM_<br>CA[1]    | MEM_CA[1]    | MEM_CA[1]    |

|             | 24        | MEM_CA[0]    | MEM_CA[0]    | MEM_0_MEM_<br>CA[0]    | MEM_CA[0]    | MEM_CA[0]    |

| BL1         | 23        | MEM_DQ[7]    | MEM_DQ[7]    | MEM_0_MEM_<br>DQ[7]    | MEM_DQ[7]    | MEM_DQ[7]    |

|             | 22        | MEM_DQ[6]    | MEM_DQ[6]    | MEM_0_MEM_<br>DQ[6]    | MEM_DQ[6]    | MEM_DQ[6]    |

|             | 21        | MEM_DQ[5]    | MEM_DQ[5]    | MEM_0_MEM_<br>DQ[5]    | MEM_DQ[5]    | MEM_DQ[5]    |

|             | 20        | MEM_DQ[4]    | MEM_DQ[4]    | MEM_0_MEM_<br>DQ[4]    | MEM_DQ[4]    | MEM_DQ[4]    |

|             | 19        |              |              |                        |              |              |

|             | 18        | MEM_DM_N[0]  | MEM_DM_N[0]  | MEM_0_MEM_<br>DM_N[0]  | MEM_DM_N[0]  | MEM_DM_N[0]  |

|             | 17        | MEM_DQS_C[0] | MEM_DQS_C[0] | MEM_0_MEM_<br>DQS_C[0] | MEM_DQS_C[0] | MEM_DQS_C[0] |

|             | 16        | MEM_DQS_T[0] | MEM_DQS_T[0] | MEM_0_MEM_<br>DQS_T[0] | MEM_DQS_T[0] | MEM_DQS_T[0] |

|             | 15        | MEM_DQ[3]    | MEM_DQ[3]    | MEM_0_MEM_<br>DQ[3]    | MEM_DQ[3]    | MEM_DQ[3]    |

|             | 14        | MEM_DQ[2]    | MEM_DQ[2]    | MEM_0_MEM_<br>DQ[2]    | MEM_DQ[2]    | MEM_DQ[2]    |

|             | 13        | MEM_DQ[1]    | MEM_DQ[1]    | MEM_0_MEM_<br>DQ[1]    | MEM_DQ[1]    | MEM_DQ[1]    |

|             | 12        | MEM_DQ[0]    | MEM_DQ[0]    | MEM_0_MEM_<br>DQ[0]    | MEM_DQ[0]    | MEM_DQ[0]    |

| BL0         | 11        | MEM_DQ[15]   | MEM_DQ[15]   | MEM_0_MEM_<br>DQ[15]   | MEM_DQ[15]   | MEM_DQ[15]   |

|             | 10        | MEM_DQ[14]   | MEM_DQ[14]   | MEM_0_MEM_<br>DQ[14]   | MEM_DQ[14]   | MEM_DQ[14]   |

|             | 9         | MEM_DQ[13]   | MEM_DQ[13]   | MEM_0_MEM_<br>DQ[13]   | MEM_DQ[13]   | MEM_DQ[13]   |

|             | 8         | MEM_DQ[12]   | MEM_DQ[12]   | MEM_0_MEM_<br>DQ[12]   | MEM_DQ[12]   | MEM_DQ[12]   |

|             | 7         |              |              |                        |              |              |

|             | ·         | •            | ·<br>        | •                      | ·            | continued    |

| Lane Number | Pin Index | x32+ECC *    | x 32         | 2ch x16                | x16 + ECC *  | x16          |

|-------------|-----------|--------------|--------------|------------------------|--------------|--------------|

|             | 6         | MEM_DM_N[1]  | MEM_DM_N[1]  | MEM_0_MEM_<br>DM_N[1]  | MEM_DM_N[1]  | MEM_DM_N[1]  |

|             | 5         | MEM_DQS_C[1  | MEM_DQS_C[1  | MEM_0_MEM_<br>DQS_C[1] | MEM_DQS_C[1  | MEM_DQS_C[1  |

|             | 4         | MEM_DQS_T[1] | MEM_DQS_T[1] | MEM_0_MEM_<br>DQS_T[1] | MEM_DQS_T[1] | MEM_DQS_T[1] |

|             | 3         | MEM_DQ[11]   | MEM_DQ[11]   | MEM_0_MEM_<br>DQ[11]   | MEM_DQ[11]   | MEM_DQ[11]   |

|             | 2         | MEM_DQ[10]   | MEM_DQ[10]   | MEM_0_MEM_<br>DQ[10]   | MEM_DQ[10]   | MEM_DQ[10]   |

|             | 1         | MEM_DQ[9]    | MEM_DQ[9]    | MEM_0_MEM_<br>DQ[9]    | MEM_DQ[9]    | MEM_DQ[9]    |

|             | 0         | MEM_DQ[8]    | MEM_DQ[8]    | MEM_0_MEM_<br>DQ[8]    | MEM_DQ[8]    | MEM_DQ[8]    |

Note: The presence of an asterisk (\*) in the above table indicates an ECC byte location.

# 3.1.3.3. LPDDR5 Pin Placement

Table 6. LPDDR5 Pin Placement

| Lane Number | Pin Index | x32           | 2 Channel x16       |

|-------------|-----------|---------------|---------------------|

| BL7         | 95        | MEM_DQ[31]    | MEM_1_MEM_DQ[15]    |

|             | 94        | MEM_DQ[30]    | MEM_1_MEM_DQ[14]    |

|             | 93        | MEM_DQ[29]    | MEM_1_MEM_DQ[13]    |

|             | 92        | MEM_DQ[28]    | MEM_1_MEM_DQ[12]    |

|             | 91        |               |                     |

|             | 90        | MEM_DMI[3]    | MEM_1_MEM_DMI[1]    |

|             | 89        | MEM_RDQS_C[3] | MEM_1_MEM_RDQS_C[1] |

|             | 88        | MEM_RDQS_T[3] | MEM_1_MEM_RDQS_T[1] |

|             | 87        | MEM_DQ[27]    | MEM_1_MEM_DQ[11]    |

|             | 86        | MEM_DQ[26]    | MEM_1_MEM_DQ[10]    |

|             | 85        | MEM_DQ[25]    | MEM_1_MEM_DQ[9]     |

|             | 84        | MEM_DQ[24]    | MEM_1_MEM_DQ[8]     |

| BL6         | 83        | MEM_DQ[23]    | MEM_1_MEM_DQ[7]     |

|             | 82        | MEM_DQ[22]    | MEM_1_MEM_DQ[6]     |

|             | 81        | MEM_DQ[21]    | MEM_1_MEM_DQ[5]     |

|             | 80        | MEM_DQ[20]    | MEM_1_MEM_DQ[4]     |

|             | 79        |               |                     |

|             | 78        | MEM_DMI[2]    | MEM_1_MEM_DMI[0]    |

|             | 77        | MEM_RDQS_C[2] | MEM_1_MEM_RDQS_C[0] |

|             |           |               | continued           |

| Lane Number | Pin Index | x32           | 2 Channel x16                                      |

|-------------|-----------|---------------|----------------------------------------------------|

|             | 76        | MEM_RDQS_T[2] | MEM_1_MEM_RDQS_T[0]                                |

|             | 75        | MEM_DQ[19]    | MEM_1_MEM_DQ[3]                                    |

|             | 74        | MEM_DQ[18]    | MEM_1_MEM_DQ[2]                                    |

|             | 73        | MEM_DQ[17]    | MEM_1_MEM_DQ[1]                                    |

|             | 72        | MEM_DQ[16]    | MEM_1_MEM_DQ[0]                                    |

| BL5         | 71        |               |                                                    |

|             | 70        |               |                                                    |

|             | 69        |               |                                                    |

|             | 68        |               | MEM_1_MEM_CS[1]                                    |

|             | 67        |               | MEM_1_CK_C                                         |

|             | 66        |               | MEM_1_CK_T                                         |

|             | 65        |               | MEM_1_MEM_CS[0]                                    |

|             | 64        |               | MEM_1_MEM_CA[6]                                    |

|             | 63        |               | MEM_1_RESET_N                                      |

|             | 62        |               | OCT_1_OCT_RZQIN                                    |

|             | 61        |               |                                                    |

|             | 60        |               |                                                    |

| BL4         | 59        |               | Differential "NSide"<br>Reference Clock Input Site |

|             | 58        |               | Differential "PSide"<br>Reference Clock Input Site |

|             | 57        |               | MEM_1_MEM_CA[5]                                    |

|             | 56        |               | MEM_1_MEM_CA[4]                                    |

|             | 55        |               | MEM_1_MEM_WCK_C[1]                                 |

|             | 54        |               | MEM_1_MEM_WCK_T[1]                                 |

|             | 53        |               | MEM_1_MEM_WCK_C[0]                                 |

|             | 52        |               | MEM_1_MEM_WCK_T[0]                                 |

|             | 51        |               | MEM_1_MEM_CA[3]                                    |

|             | 50        |               | MEM_1_MEM_CA[2]                                    |

|             | 49        |               | MEM_1_MEM_CA[1]                                    |

|             | 48        |               | MEM_1_MEM_CA[0]                                    |

| BL3         | 47        |               |                                                    |

|             | 46        |               |                                                    |

|             | 45        |               |                                                    |

|             | 44        | MEM_CS[1]     | MEM_0_MEM_CS[1]                                    |

|             | 43        | MEM_CK_C      | MEM_0_CK_C                                         |

|             | 42        | MEM_CK_T      | MEM_0_CK_T                                         |

|             |           |               | continued                                          |

| Lane Number | Pin Index | x32                                                 | 2 Channel x16                                      |

|-------------|-----------|-----------------------------------------------------|----------------------------------------------------|

|             | 41        | MEM_CS[0]                                           | MEM_0_MEM_CS[0]                                    |

|             | 40        | MEM_CA[6]                                           | MEM_0_MEM_CA[6]                                    |

|             | 39        | MEM_RESET_N                                         | MEM_0_RESET_N                                      |

|             | 38        | RZQ Site                                            | OCT_0_OCT_RZQIN                                    |

|             | 37        |                                                     |                                                    |

|             | 36        |                                                     |                                                    |

| BL2         | 35        | Differential "N-Side"<br>Reference Clock Input Site | Differential "NSide"<br>Reference Clock Input Site |

|             | 34        | Differential "P-Side"<br>Reference Clock Input Site | Differential "PSide"<br>Reference Clock Input Site |

|             | 33        | MEM_CA[5]                                           | MEM_0_MEM_CA[5]                                    |

|             | 32        | MEM_CA[4]                                           | MEM_0_MEM_CA[4]                                    |

|             | 31        | MEM_WCK_C[1]                                        | MEM_0_MEM_WCK_C[1]                                 |

|             | 30        | MEM_WCK_T[1]                                        | MEM_0_MEM_WCK_T[1]                                 |

|             | 29        | MEM_WCK_C[0]                                        | MEM_0_MEM_WCK_C[0]                                 |

|             | 28        | MEM_WCK_T[0]                                        | MEM_0_MEM_WCK_T[0]                                 |

|             | 27        | MEM_CA[3]                                           | MEM_0_MEM_CA[3]                                    |

|             | 26        | MEM_CA[2]                                           | MEM_0_MEM_CA[2]                                    |

|             | 25        | MEM_CA[1]                                           | MEM_0_MEM_CA[1]                                    |

|             | 24        | MEM_CA[0]                                           | MEM_0_MEM_CA[0]                                    |

| BL1         | 23        | MEM_DQ[15]                                          | MEM_0_MEM_DQ[15]                                   |

|             | 22        | MEM_DQ[14]                                          | MEM_0_MEM_DQ[14]                                   |

|             | 21        | MEM_DQ[13]                                          | MEM_0_MEM_DQ[13]                                   |

|             | 20        | MEM_DQ[12]                                          | MEM_0_MEM_DQ[12]                                   |

|             | 19        |                                                     |                                                    |

|             | 18        | MEM_DMI[1]                                          | MEM_0_MEM_DMI[1]                                   |

|             | 17        | MEM_RDQS_C[1]                                       | MEM_0_MEM_RDQS_C[1]                                |

|             | 16        | MEM_RDQS_T[1]                                       | MEM_0_MEM_RDQS_T[1]                                |

|             | 15        | MEM_DQ[11]                                          | MEM_0_MEM_DQ[11]                                   |

|             | 14        | MEM_DQ[10]                                          | MEM_0_MEM_DQ[10]                                   |

|             | 13        | MEM_DQ[9]                                           | MEM_0_MEM_DQ[9]                                    |

|             | 12        | MEM_DQ[8]                                           | MEM_0_MEM_DQ[8]                                    |

| BL0         | 11        | MEM_DQ[7]                                           | MEM_0_MEM_DQ[7]                                    |

|             | 10        | MEM_DQ[6]                                           | MEM_0_MEM_DQ[6]                                    |

|             | 9         | MEM_DQ[5]                                           | MEM_0_MEM_DQ[5]                                    |

|             | 8         | MEM_DQ[4]                                           | MEM_0_MEM_DQ[4]                                    |

|             | 7         |                                                     |                                                    |

|             |           | •                                                   | continued                                          |

| Lane Number | Pin Index | x32           | 2 Channel x16       |

|-------------|-----------|---------------|---------------------|

|             | 6         | MEM_DMI[0]    | MEM_0_MEM_DMI[0]    |

|             | 5         | MEM_RDQS_C[0] | MEM_0_MEM_RDQS_C[0] |

|             | 4         | MEM_RDQS_T[0] | MEM_0_MEM_RDQS_T[0] |

|             | 3         | MEM_DQ[3]     | MEM_0_MEM_DQ[3]     |

|             | 2         | MEM_DQ[2]     | MEM_0_MEM_DQ[2]     |

|             | 1         | MEM_DQ[1]     | MEM_0_MEM_DQ[1]     |

|             | 0         | MEM_DQ[0]     | MEM_0_MEM_DQ[0]     |

#### 3.1.3.4. I/O Sub-Bank Usage

The pins in an I/O bank can serve as address and command pins, data pins, or clock and strobe pins for an external memory interface.

A given sub-bank cannot be shared between multiple EMIFs.

All the sub-banks are capable of functioning as the address and command bank.

#### 3.1.4. Intel Agilex 7 M-Series EMIF Architecture: I/O Lane

An I/O bank contains two sub-banks. Each sub-bank contains 48 I/O pins, organized into four I/O lanes of 12 pins each. You can identify where a pin is located within an I/O bank based on its Index within I/O Bank in the device pinout.

Table 8. Pin Index Mapping

| Pin Index | Lane | Sub-bank Location |

|-----------|------|-------------------|

| 0-11      | 0    | Bottom            |

| 12-23     | 1    |                   |

| 24-35     | 2    |                   |

| 36-47     | 3    |                   |

| 48-59     | 4    | Тор               |

| 60-71     | 5    |                   |

| 72-83     | 6    |                   |

| 84-95     | 7    |                   |

Each I/O lane can implement one x8/x9 read capture group (DQS group), with two pins functioning as the read capture clock/strobe pair (DQS/DQS#), and up to 10 pins functioning as data pins (DQ and DM pins). To implement a x18 group, you can use multiple lanes within the same sub-bank.

It is also possible to implement a pair of x4 groups in a lane. In this case, four pins function as clock/strobe pair, and 8 pins function as data pins. DM is not available for x4 groups. There must be an even number of x4 groups for each interface.

For x4 groups, you must place DQS0 and DQS1 in the same I/O lane as a pair. Similarly, DQS2 and DQS3 must be paired. In general, DQS(x) and DQS(x+1) must be paired in the same I/O lane.

For DQ and DQS pin assignments for various configurations, refer to the Intel Agilex 7 M-Series device pin tables.

**Table 9.** Lanes Used Per DQS Group

| Group Size | Number of Lanes Used | Maximum Number of Data Pins per<br>Group |

|------------|----------------------|------------------------------------------|

| x8 / x9    | 1                    | 10                                       |

| x18        | 2                    | 22                                       |

| pair of x4 | 1                    | 4 per group, 8 per lane                  |

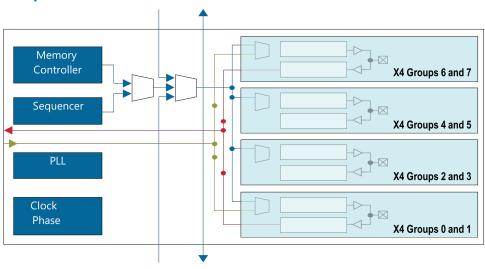

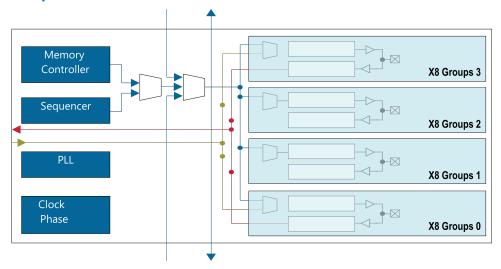

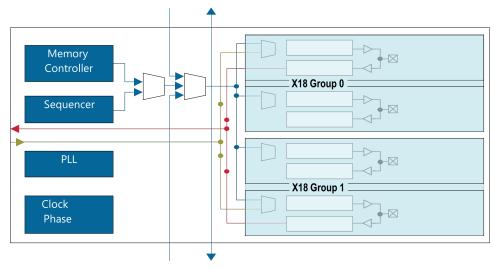

Figure 4. x4 Group

Figure 5. x8 Group

Figure 6. x18 Group

# 3.1.5. Intel Agilex 7 M-Series EMIF Architecture: Input DQS Clock Tree

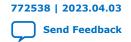

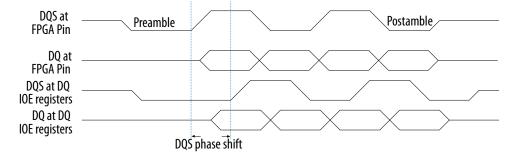

The input DQS clock tree is a balanced clock network that distributes the read capture clock (such as QK/QK# which are free-running read clocks) and strobe (such as DQS\_T/DQS\_C) from the external memory device to the read capture registers inside the I/Os.

You can configure an input DQS clock tree in x4 mode, x8/x9 mode, or x18 mode.

Within every bank, only certain physical pins at specific locations can drive the input DQS clock trees. The pin locations that can drive the input DQS clock trees vary, depending on the size of the group.

Table 10. Pins Usable as Read Capture Clock / Strobe Pair

| <b>Group Size</b> | Index of Lanes<br>Spanned by Clock<br>Tree <sup>1</sup> | Sub-Bank |       | Index of Pins Usable as Read Capture<br>Clock / Strobe Pair |  |  |

|-------------------|---------------------------------------------------------|----------|-------|-------------------------------------------------------------|--|--|

|                   | Tree -                                                  |          | DQS_T | DQS_C                                                       |  |  |

| x4                | 0A                                                      | Bottom   | 4     | 5                                                           |  |  |

| x4                | 0B                                                      |          | 6     | 7                                                           |  |  |

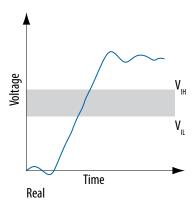

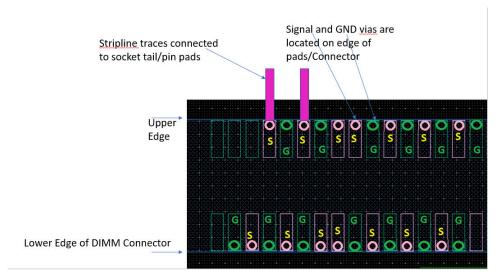

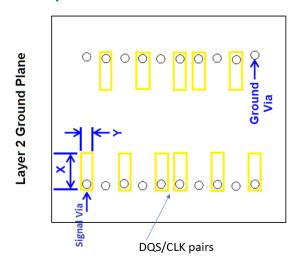

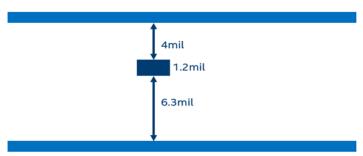

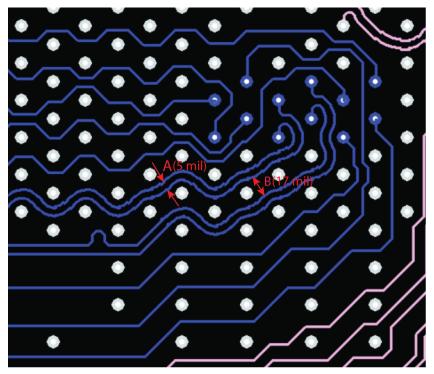

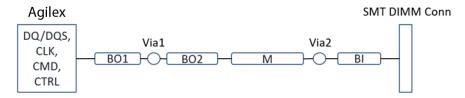

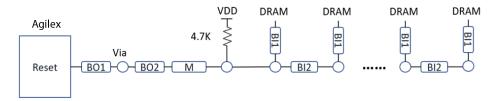

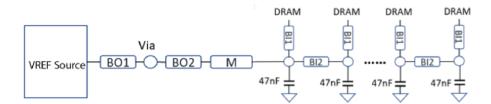

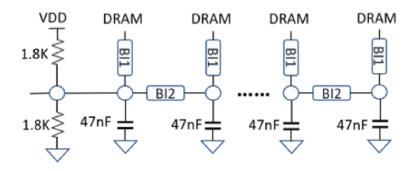

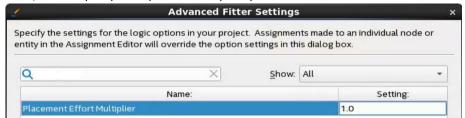

| x4                | 1A                                                      | ]        | 16    | 17                                                          |  |  |