# Intel Agilex® 7 M-Series FPGA Network-on-Chip (NoC) User Guide

Updated for Intel® Quartus® Prime Design Suite: 23.2

# **Answers to Top FAQs:**

- What is the NoC?

- A General NoC Architecture on page 5

- Which applications benefit from NoC?

- A Example NoC Applications on page 6

- - A High-Level NoC Architecture on page 8

- What protocols does NoC support?

- A NoC Protocol Support on page 17

- **Q** How do I implement the NoC?

- A NoC Design Flow on page 26

- Can I start from a design example?

- A NoC Example Designs on page 28

- What IP does NoC require?

- A NoC Building Blocks on page 29

- How do I simulate my NoC design?

- A Simulating NoC Designs on page 62

- How do I estimate power for NoC designs?

- A NoC Power Estimation on page 65

# **Contents**

| 1. Network-on-Chip (NoC) Overview                                       | 4  |

|-------------------------------------------------------------------------|----|

| 1.1. Introduction to Intel Agilex® 7 M-Series FPGAs                     |    |

| 1.2. Terminology for Intel Agilex 7 M-Series FPGAs                      |    |

| 1.3. General NoC Architecture and Applications                          |    |

| 1.3.1. General NoC Architecture                                         |    |

| 1.3.2. Example NoC Applications                                         |    |

| 2. Hard Memory NoC in Intel Agilex 7 M-Series FPGAs                     |    |

| 2.1. High-Level Architecture                                            |    |

| 2.2. NoC Segments                                                       |    |

| 2.2.1. UIB Segments                                                     |    |

| 2.2.2. GPIO-B Segments                                                  |    |

| 2.2.3. GPIO-B and HPS Segment                                           |    |

| 2.2.4. SDM Segment                                                      |    |

| 2.2.5. PLL and SSM Segment                                              |    |

| 2.3. NoC Switch and Link Detail                                         | 13 |

| 2.4. Fabric NoC                                                         | 16 |

| 2.5. NoC Protocol Support                                               | 17 |

| 2.5.1. AXI4 Protocol Support                                            | 17 |

| 2.5.2. AXI4 Handshaking Support                                         |    |

| 2.5.3. Quality of Service (QoS) Support                                 |    |

| 2.5.4. Transaction Ordering Support                                     |    |

| 2.5.5. AXI4 Lite Protocol Support                                       |    |

| 2.6. NoC Design Considerations                                          |    |

| 2.6.1. Determining the Number of NoC Targets                            |    |

| 2.6.2. Determining the Number of NoC Initiators                         |    |

| 2.6.3. Fabric NoC Considerations                                        |    |

| 2.6.4. Latency Considerations                                           |    |

| 2.6.5. Initiator and Target Bandwidth Considerations                    |    |

| 2.6.7. GPIO-B Bypass Mode and Initiators                                |    |

|                                                                         |    |

| 3. NoC Design Flow in Intel Quartus Prime Pro Edition                   |    |

| 3.1. Hard Memory NoC Design Flow Overview                               |    |

| 3.1.1. NoC Design Flow Options                                          |    |

| 3.2. Using NoC Example Designs                                          |    |

| 3.3.1. NoC Initiators for Hard Processor Systems                        |    |

| 3.3.2. NoC Targets for Hard Processor Systems                           |    |

| 3.3.3. NoC Initiators for Fabric AXI4 Managers                          |    |

| 3.3.4. NoC Targets for Fabric AXI4 Managers                             |    |

| 3.3.5. NoC Clock Control                                                |    |

| 3.4. Connecting NoC IP                                                  |    |

| 3.4.1. General NoC IP Connectivity Guidelines                           |    |

| 3.4.2. Connectivity Guidelines: NoC Initiators for Fabric AXI4 Managers |    |

| 3.4.3. Connectivity Guidelines: NoC Targets for Fabric AXI4 Managers    |    |

| 3.4.4. Connectivity Guidelines: NoC Clock Control                       |    |

| 3.4.5. Connectivity Guidelines: NoC Initiators for HPS                  |    |

| 3.4.6. Connectivity Guidelines: NoC Targets for HPS                                      | 39 |

|------------------------------------------------------------------------------------------|----|

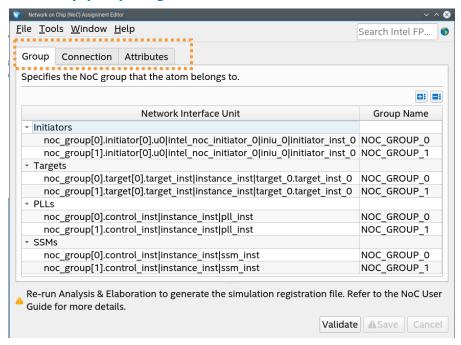

| 3.5. Making NoC Logical Assignments                                                      |    |

| 3.5.1. Creating NoC Assignments for Compilation                                          | 40 |

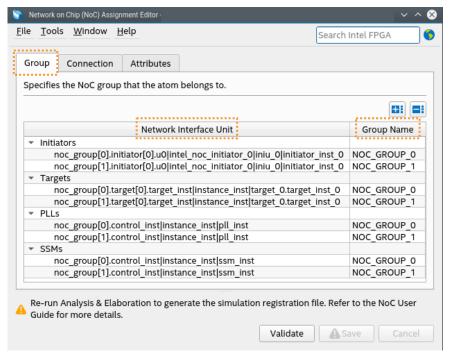

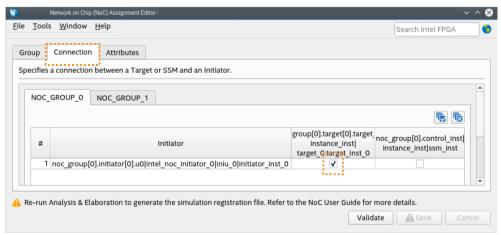

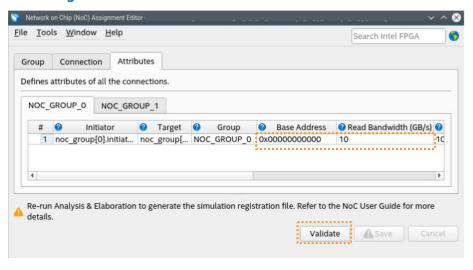

| 3.5.2. Using the NoC Assignment Editor                                                   |    |

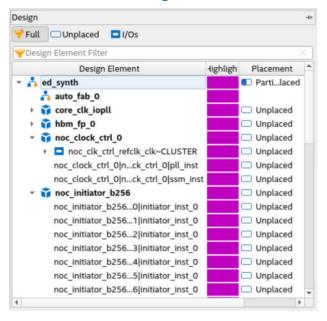

| 3.6. (Recommended) Make NoC Physical Assignments Using Interface Planner                 |    |

| 3.6.1. Using Interface Planner                                                           | 49 |

| 3.6.2. Recommended Placement Order for NoC Elements in Interface Planner                 |    |

| 3.6.3. Hard Memory NoC Locations in Interface Planner                                    |    |

| 3.6.4. NoC Performance Reports in Interface Planner                                      |    |

| 3.7. Compiling the NoC Design                                                            |    |

| 3.7.1. Fitter NoC Reports                                                                |    |

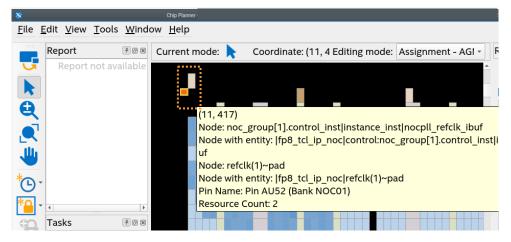

| 3.7.2. Viewing NoC Elements in Chip Planner                                              | 60 |

| 4. NoC Real-time Performance Monitoring                                                  | 61 |

| 5. Simulating NoC Designs                                                                | 62 |

| 5.1. Adding NoC Connectivity and Address Mapping to the Simulation Netlist               | 62 |

| 5.2. Generating a Simulation Registration Include File (NoC Assignment Editor            |    |

| Connection Flow)                                                                         |    |

| 5.3. Generating a Simulation Registration Include File (Platform Designer Connection Flo | ,  |

| 5.4. Contents of Simulation Registration Include File                                    | 64 |

| 6. NoC Power Estimation                                                                  | 65 |

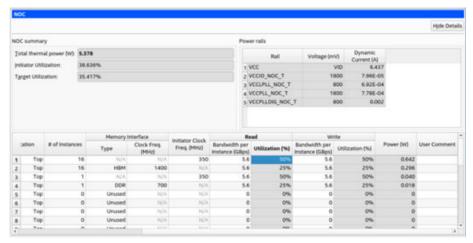

| 6.1. Using the Intel FPGA PTC to Estimate NoC Power                                      | 65 |

| 7. Hard Memory NoC IP Reference                                                          | 68 |

| 7.1. NoC Initiator Intel FPGA IP                                                         | 68 |

| 7.1.1. NoC Initiator Intel FPGA IP Parameters                                            |    |

| 7.1.2. NoC Initiator Intel FPGA IP Interfaces                                            |    |

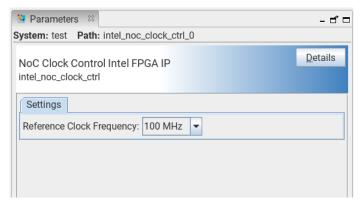

| 7.2. NoC Clock Control Intel FPGA IP                                                     |    |

| 7.2.1. NoC Clock Control Intel FPGA IP Parameters                                        |    |

| 7.2.2. NoC Clock Control Intel FPGA IP Interfaces                                        |    |

| 7.2.3. NoC Clock Control Intel FPGA IP Platform Designer-only Signals                    | 78 |

| 8. Document Revision History of Intel Agilex 7 M-Series FPGA Network-on-Chip             |    |

| (NoC) User Guide                                                                         | 80 |

# 1. Network-on-Chip (NoC) Overview

# 1.1. Introduction to Intel Agilex® 7 M-Series FPGAs

Intel Agilex<sup>®</sup> 7 M-Series FPGAs introduce an integrated Network-on-Chip (NoC) to facilitate high-bandwidth data movement between the FPGA core logic and memory resources, such as HBM2e and external memories, such as DDR5.<sup>(1)</sup> The Intel Agilex 7 M-Series FPGA implements the NoC as two independent hard memory NoCs running horizontally along the top edge and bottom edge of the die. These horizontal networks spread memory bandwidth across the edge of the device, making it easier to saturate the memory bandwidth while avoiding routing congestion. An additional feature known as the fabric NoC allows you to store read data from external memory directly in M20K memory blocks in the FPGA fabric, further reducing congestion along the die edge.

This document provides the following information about these NoC devices:

- An introduction to NoC structures and typical applications.

- Details on the NoC subsystem in Intel Agilex 7 M-Series FPGAs.

- How to create NoC designs in the Intel Quartus Prime Pro Edition software.

- How to use NoC subsystem features to monitor performance during operation.

- How to simulate designs using the NoC subsystem.

- How to estimate power for designs using the NoC subsystem.

# 1.2. Terminology for Intel Agilex 7 M-Series FPGAs

Table 1. Intel Agilex 7 M-Series FPGA Terminology

| Term            | Description                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NoC             | Network-on-Chip based communications structure between elements only in Intel Agilex 7 M-Series FPGAs.                                                       |

| Hard Memory NoC | The NoC subsystem implemented as a hard block in the Intel Agilex 7 M-Series FPGA for interfacing with high-bandwidth memory and external memory interfaces. |

| NoC Initiator   | The bridge between the AXI4 manager in user logic and the hard memory NoC.                                                                                   |

| NoC Target      | The bridge between the AXI4 subordinate IP in the periphery and the hard memory NoC.                                                                         |

| Fabric NoC      | An optional implementation of the NoC initiator where the read response data is written directly to M20K memory blocks.                                      |

| HBM2e           | The in-package, high-bandwidth memory available in Intel Agilex 7 M-Series FPGAs.                                                                            |

|                 | continued                                                                                                                                                    |

<sup>(1)</sup> The Intel® Quartus® Prime Pro Edition software version 23.2 restricts device support for Intel Agilex 7 M-series FPGAs and SoCs. To enable M-series device support in your instance of the Intel Quartus Prime Pro Edition software, contact your regional Intel FPGA sales representative.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

| Term             | Description                                                          |

|------------------|----------------------------------------------------------------------|

| AXI4 Manager     | Function that initiates transactions on an AXI4 interconnect.        |

| AXI4 Subordinate | Function that responds to transactions on an AXI4 interconnect.      |

| GPIO-B Blocks    | General purpose I/O bank available in Intel Agilex 7 M-Series FPGAs. |

| NoC PLL          | Dedicated phase lock loop (PLL) for the hard memory NoC.             |

| NoC SSM          | Sub-system manager for the hard memory NoC.                          |

# 1.3. General NoC Architecture and Applications

#### 1.3.1. General NoC Architecture

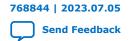

The NoC subsystem comprises a network of switches connected with high-speed data links. The NoC initiators and NoC targets connect into these switches. Initiators are bridges that interface with manager logic in your design that initiates read or write transactions.

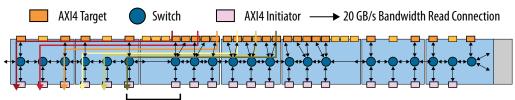

Figure 1. General NoC Architecture Abstraction illustrates an example of a high-bandwidth, high-speed Network-on-Chip (NoC) interconnect architecture.

Figure 1. General NoC Architecture Abstraction

NoC targets are bridges that interface with subordinate IP that respond to these read or write transactions. Some subordinate IP, such as the High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA IP, may connect to multiple targets. The NoC initiators and targets translate between the AXI4 and the internal NoC format.

In a typical transaction, an AXI manager posts transactions that the initiator block then converts into the internal format of the NoC. These transaction steps then reverse when the transaction translates back to AXI upon arrival at the subordinate memory IP. Multiple managers can issue read or write transactions simultaneously to different subordinates. The switch network routes each request independently, arbitrating between traffic, as necessary.

You can use the hardened NoC architecture to transport transactions to external memory. The hardened NoC infrastructure applies the advantages of large-scale networks to FPGAs. The NoC subsystem provides highly structured, flexible, and scalable on-chip memory access solutions for bandwidth demanding applications, such as real-time audio and video, network processing, high-performance computing, and other applications.

#### 1.3.2. Example NoC Applications

This section describes some applications that can benefit from NoC technology. These applications typically feature high bandwidth requirements between core logic and memory resources.

#### 1.3.2.1. Parallel Computing NoC Application

In a parallel computing system you may use several types of processors and accelerators to optimally execute a computational effort, using task-based and data-based parallelism. Interconnect and memory performance play a key role in a parallel computing system where the NoC subsystem can provide high-bandwidth and low-latency communication between the processing elements and memories.

A parallel computing system may have data that transfers between an external host and the FPGA over a PCI Express\* (PCIe) link. Once you bring data into the FPGA fabric, you can then store this data in HBM2e or external memory, for example DDR5, over the NoC subsystem.

Every processing element connected to a NoC can access all channels of the global memories attached to that NoC, regardless of the physical location of these channels. Processing elements often have highly sequential memory read access patterns that benefit from use of a feature in Intel Agilex 7 M-series devices known as the fabric NoC. This feature allows the NoC to deliver read results via M20K memories that are located close to the PE logic in the FPGA core fabric.

#### 1.3.2.2. SmartNIC NoC Application

Network Interface Cards (NICs) connect computers and servers to an Ethernet network. SmartNICs are network adapters that have programmability and flexibility to accelerate and offload certain functions from the server CPU, such as packet processing that traditional NICs are incapable of handling.

SmartNICs can increase server performance in data centers by offloading network processing workloads and tasks from the CPU. This offloading frees up server CPU cores to work on computationally intensive business-critical tasks at the network flow and packet level. Offloading functions such as storage, encryption, and sophisticated routing enables SmartNICs to deliver back to the host the CPU cycles usually spent processing these workloads. This offloading can result in improved server performance and reduced overall power consumption.

The support different processing engines, such as filtering, switching, routing, packet buffering, and flow control, requires external high-bandwidth and high-capacity memories, such as HBM2e and DDR5. Additionally, the interface between the SmartNIC and external memory must meet the bandwidth requirement of the switching Ethernet traffic. The NoC subsystem available in Intel Agilex 7 M-Series FPGAs provides the high-bandwidth interconnect between these programmable offload engines and the external memory that SmartNIC applications require.

#### **Related Information**

- High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 M-Series FPGA IP User Guide

- External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide

- External Memory Interfaces Intel Agilex 7 M-Series FPGA IP Design Example User Guide

- High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 M-Series FPGA IP Design Example User Guide

# 2. Hard Memory NoC in Intel Agilex 7 M-Series FPGAs

# 2.1. High-Level Architecture

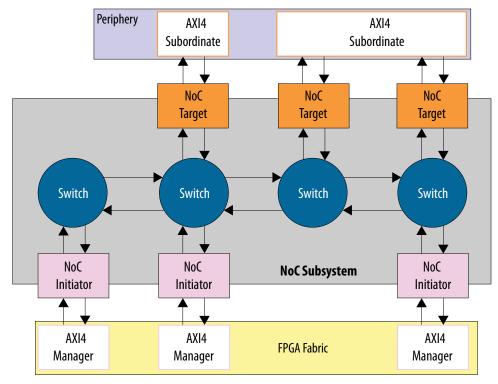

Intel Agilex 7 M-Series FPGAs provide two hard memory NoC subsystems that run horizontally along the top and bottom edges of the FPGA die. These subsystems are completely independent, and each subsystem interfaces with a separate set of peripherals. These horizontal networks spread memory bandwidth across the edge of the device, making it easier to saturate the memory bandwidth while avoiding routing congestion. Because the NoC is hard logic, it also reduces the need for soft interconnect logic, leaving more room for other IP functions.

The clock control segment contains a PLL for clock generation and a sub-system manager (SSM) for configuration. Other NoC segments interface with general purpose I/O (GPIO-B) banks where you can implement external memory interfaces. There are also segments to interface with the Universal Interface Bus (UIB) that connects to inpackage high-bandwidth memory. The NoC segments contain switches, NoC initiators, and NoC targets. For details on each segment, refer to NoC Segments.

High-speed 512-bit links interconnect the switches within the NoC segments. There are separate sets of links carrying traffic left-to-right, and right-to-left, within the hard memory NoC. Each set of links has separate links for transaction requests and transaction responses.

NoC initiators connect AXI4 managers in the FPGA fabric to the hard memory NoC. NoC targets connect subordinate hardened memory controllers to the hard memory NoC.

You can choose to have the initiator return read data to M20K memory cells in a column adjacent to the NoC initiator using a configuration known as a fabric NoC. Because the data transfers directly into the FPGA fabric, this fabric NoC configuration reduces congestion at the edge of the device. Additionally, this configuration doubles the AXI4 read data width, enabling your design to fully utilize the high bandwidth memory and external memory interfaces while running at a lower operating frequency.

HBM2e memory connects to targets through the Universal Interface Bus (UIB). All access between the FPGA fabric and HBM2e memory is through the hard memory NoC. Refer to the *High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA IP User Guide* for details on the HBM2e memory.

You can implement external memory protocols, such as DDR5, in GPIO-B I/O blocks. You can also use GPIO-B blocks for implementing other I/O functions.

You have the option of accessing external memory interfaces using the hard memory NoC, or directly from the FPGA fabric bypassing the NoC, depending on memory speeds, protocols and your design needs. Refer to the *External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide* for details on external memory protocols supported in GPIO-B blocks and when to use the hard memory NoC or bypass mode.

Other I/O functions that you implement in GPIO-B blocks do not connect to the hard memory NoC and always bypass it directly in the FPGA fabric. Note that functions that bypass the hard memory NoC may prevent the use of certain NoC initiator locations. For more information refer to GPIO-B Bypass Mode and Initiators.

The hard memory NoC along the top edge of the die also connects to a multi-port front end (MPFE) for the Hard Processor System (HPS). The MPFE is located in the segment immediately next to the HPS and allows the HPS to initiate transactions on the hard memory NoC. The NoC initiators in the MPFE are similar to the NoC initiators that interface to the FPGA fabric, but do not have the option to use the fabric NoC configuration which transfers read data directly into M20K memory blocks. Refer to the Intel Agilex 7 Hard Processor System Technical Reference Manual for details on the HPS.

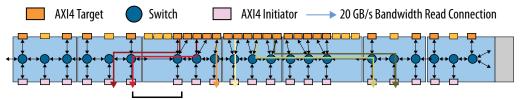

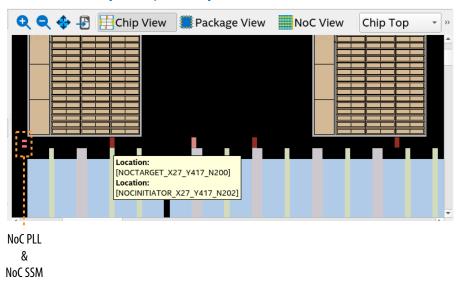

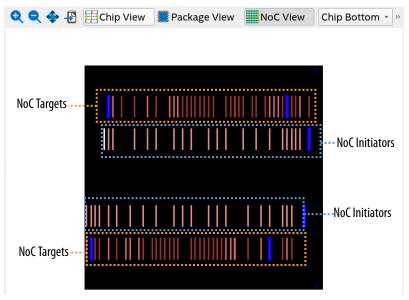

Figure 2. Intel Agilex 7 M-Series Device Layout

Each hard memory NoC subsystem consists of several NoC segments connected horizontally by high-speed networks. Figure 2. Intel Agilex 7 M-Series Device Layout shows the high-level layout of hard memory NoC elements in Intel Agilex 7 M-Series devices. Along the top and bottom edge of the die are GPIO-B blocks for implementing external memory interfaces and UIB blocks for interfacing to HBM2e memory. Adjacent to these are the NoC GPIO-B and UIB segments that make up the hard

memory NoC. NoC PLL and SSM segments are in the upper left and lower left corners. The vertical arrows extending from these segments into the die represent the optional fabric NoCs using M20K memory blocks.

Additionally, there is a service network within the hard memory NoC segments that runs in parallel to the main switch network. This service network connects the NoC SSM and the HPS AXI4 Lite initiator to AXI4 Lite targets. You can use this service network for sideband configuration and monitoring.

The following document sections describe the hard memory NoC segments and the fabric NoCs.

#### **Related Information**

- High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 M-Series FPGA IP User Guide

- External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide

- Intel Agilex 7 Hard Processor System Technical Reference Manual

### 2.2. NoC Segments

Aside from the NoC PLL and SSM, the hard memory NoC also consists of segments containing initiators, targets, and switches. The structure of segments within the hard memory NoC depend on the interfaces with which they interact. Figure 2. Intel Agilex 7 M-Series Device Layout shows the arrangement of these segments within each hard memory NoC.

The following section describes the individual NoC segments. The hard memory NoC along the top edge of the device contains 20 NoC initiators facing the FPGA fabric and 2 NoC initiators in the MPFE to interact with the HPS. The hard memory NoC along the bottom edge of the device contains 22 NoC initiators facing the FPGA fabric.

There is an additional service network running parallel to the main switch network within each hard memory NoC. This service network connects NoC SSM and the HPS AXI4 Lite initiator to AXI4 Lite targets. Fabric-facing NoC initiators can send transactions over the main network to the NoC SSM to access the service network for sideband configuration and system monitoring. The NoC Segment diagrams do not show this service network.

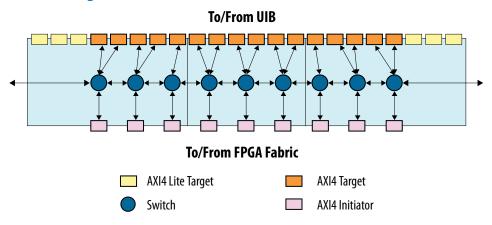

#### 2.2.1. UIB Segments

UIB segments are NoC segments that interface with the UIB to connect to HBM2e memory. These UIB segments consist of three subsegments, each aligned with an FPGA clock sector. Overall, the UIB segment consists of the following:

- Nine AXI4 initiators on the FPGA fabric side.

- Sixteen AXI4 targets on the UIB side.

- Six AXI4 Lite targets on the UIB side.

- A network of switches that transfer packets laterally along the hard memory NoC and connect to the AXI4 initiators and target.

Figure 3. NoC UIB Segment

Note:

There is an additional service network running parallel to the main switch network. This service network connects the NoC SSM to the AXI4 Lite initiators and targets. NoC initiators can send transactions over the main network to the NoC SSM to access the service network for sideband configuration and system monitoring. Figure 3. NoC UIB Segment does not show this network.

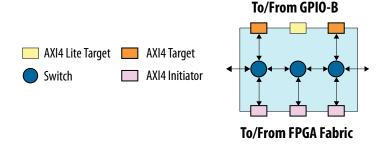

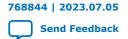

#### 2.2.2. GPIO-B Segments

GPIO-B segments are NoC segments that interface with GPIO-B blocks, span one FPGA clock sector, and consist of the following:

- Three AXI4 initiators on the FPGA fabric side.

- Two AXI4 targets on the GPIO-B block side.

- One AXI4 Lite target on the GPIO-B block side.

- A network of switches that transfer packets laterally along the hard memory NoC and connect to the AXI4 initiators and targets.

Figure 4. GPIO-B Segments

Note:

There is an additional service network running parallel to the main switch network. This service network connects the NoC SSM to the AXI4 Lite initiators and targets. NoC initiators can send transactions over the main network to the NoC SSM to access the service network for sideband configuration and system monitoring. Figure 4. GPIO-B Segments does not show this service network.

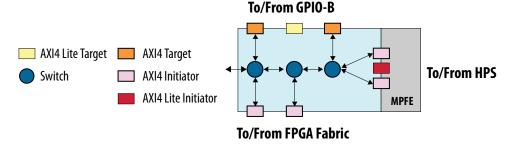

# 2.2.3. GPIO-B and HPS Segment

The GPIO-B and HPS segment is a segment of the top NOC adjacent to the HPS which interfaces with the HPS and also interfaces with the GPIO-B block. This segment is similar to the GPIO-B segments, except that a connection to the HPS MPFE replaces one of the NoC initiators facing the FPGA fabric. The HPS segment consists of the following:

- Two AXI4 initiators on the FPGA fabric side.

- Two AXI4 targets on the GPIO-B side.

- One AXI4 Lite target on the GPIO-B side.

- Two AXI4 initiators and one AXI4 Lite initiator on the HPS MPFE side.

- A network of switches that transfer packets laterally along the hard memory NoC and connect to the AXI4 initiators and targets.

Figure 5. NoC GPIO-B/HPS Segment

Note:

There is an additional service network running parallel to the main switch network. This service network connects the NoC SSM to the AXI4 Lite initiators. NoC initiators can send transactions over the main network to the NoC SSM to access the service network for sideband configuration and system monitoring.

#### 2.2.4. SDM Segment

The hard memory NoC on the bottom edge of the device also has a segment that spans the Secure Device Manager (SDM). There is no connection between the SDM and the hard memory NoC, and all signals from the SDM bypass the hard memory NoC. This NoC segment spans one clock sector and consists of the following:

- One AXI4 initiator on the FPGA fabric side.

- A switch that transfers packets laterally along the hard memory NoC and connects to the AXI4 initiator.

Figure 6. NoC SDM Segment

# AXI4 Initiator Switch SDM

Note:

There is an additional service network running parallel to the main switch network. This service network connects the NoC SSM to the AXI4 Lite initiators and targets. NoC initiators can send transactions over the main network to the NoC SSM to access the service network for sideband configuration and system monitoring. Figure 6. NoC SDM Segment does not show this network.

### 2.2.5. PLL and SSM Segment

The end NoC segment for each hard memory NoC contains the NoC PLL and the NoC subsystem manager (SSM). The NoC PLL generates the clocking for the hard memory NoC. The NoC SSM connects to a service network to configure the hard memory NoC and to read status registers for observability and debug purposes. The NoC SSM uses a non-user accessible AXI4 Lite initiator to connect to the service network.

Figure 7. NoC PLL and SSM Segment

Note:

Figure 7. NoC PLL and SSM Segment does not show the reference clock for the PLL nor the clocks generated by the PLL.

The NoC SSM segment provides a transparent bridge between the hard memory NoC and service network. This bridge enables fabric AXI4 initiators to access AXI4 Lite targets.

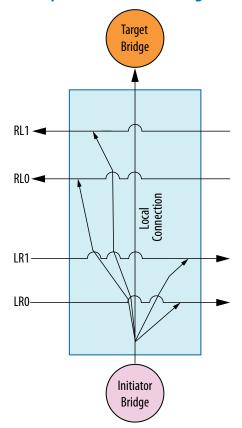

#### 2.3. NoC Switch and Link Detail

The NoC segment diagrams in the NoC Segments section show a simplified view of the switches and high-speed links that comprise the hard memory NoC. To simplify the explanation, these diagrams show the high-speed links as a single, bidirectional bus connecting the switch network.

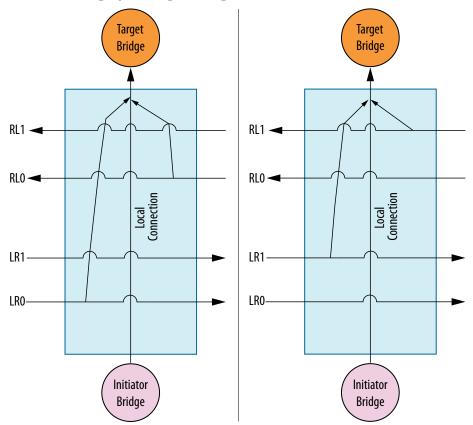

However, the single bidirectional link in these diagrams actually represent four, highspeed links:

- Two links (LR0 and LR1) carry traffic left-to-right.

- The other two links (RLO and RL1) carry traffic right-to-left.

Each of the NoC initiator bridges connect with all four high-speed links. However, the NoC target bridges connect to only two of the links, one in each direction. The target connections alternate:

- One NoC target bridge connects to LRO and RLO.

- The adjacent NoC target bridge connects to LR1 and RL1.

Refer to Figure 13. Horizontal Link Allocation for Top-Edge NoC and Figure 14. Horizontal Link Allocation for Bottom-Edge NoC for NoC target bridge link connection details.

Additionally, the switches in the NoC Segments section diagrams represent multiple switches to connect to each of the horizontal links. Again, the NoC initiator bridges can connect to all four of the horizontal links, while the NoC target bridges connect to only two horizontal links, one in each direction. Additionally, each NoC initiator bridge has local connections to up to two NoC target bridges. These connections are known as "local" because they do not use the horizontal links at all.

Figure 8. Example NoC Initiator Bridge Connectivity shows example connectivity for a NoC initiator bridge. This bridge connects to all four of the horizontal links. This bridge also connects to one NoC target bridge through a local connection without using the horizontal link. For simplicity, additional target bridge connections do not appear.

Figure 8. Example NoC Initiator Bridge Connectivity

Figure 9. Example NoC Target Bridge Connectivity with Local Connection to One NoC Initiator Bridge per Target Bridge shows example connectivity for NoC target bridges where there is one local connection between one initiator bridge per target bridge. The NoC target bridge on the left connects to the RLO and LRO horizontal links. The NoC target bridge on the right connects to the RLO and LRO horizontal links. For simplicity, additional initiator bridge connections do not appear.

Figure 9. Example NoC Target Bridge Connectivity with Local Connection to One NoC Initiator Bridge per Target Bridge

Figure 10. Example NoC Target Bridge Connectivity with Local Connection to One NoC Initiator Bridge for Two Target Bridges shows example connectivity for NoC target bridges where adjacent target bridges have local connections to the same NoC initiator bridge. The NoC target bridge on the left connects to the RL1 and LR1 horizontal links. The NoC target bridge on the right connects to the RL0 and LR0 horizontal links. For simplicity, additional initiator bridge connections do not appear.

Figure 10. Example NoC Target Bridge Connectivity with Local Connection to One NoC Initiator Bridge for Two Target Bridges

#### 2.4. Fabric NoC

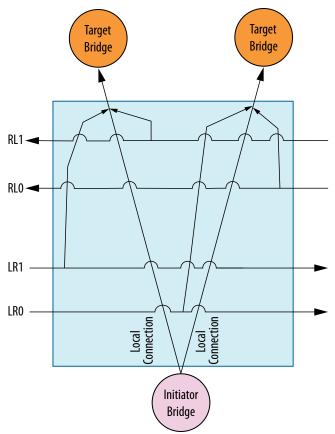

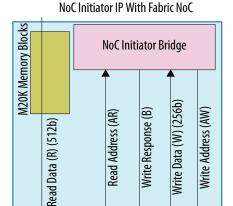

If you configure the NoC initiator with a 512-bit or 576-bit wide read data path, the NoC initiator implements a feature known as the fabric NoC. The fabric NoC is a hardware extension to the NoC initiator that delivers read data through a group of 16 M20K blocks in the adjacent memory column. The read data width of the NoC initiator doubles (from 256 to 512), which enables the saturation of read bandwidth of HBM2e or external memory at easily obtainable core frequencies. The NoC initiator Intel FPGA IP uses the M20K memories as internal FIFOs, which continues to provide an AXI4 interface for use by your design.

NoC initiators implemented with the fabric NoC consume 16 M20K memory blocks but also result in less congestion for routing resources along the die edge. Also note that NoC initiators with 512-bit or 576-bit wide read data paths do not support narrow or unaligned AXI4 transfers.

Figure 11. NoC Initiators With and Without Fabric NoC shows the AXI4 subordinate interface of the NoC initiator. The NoC initiator on the left is shows configuration without the fabric NoC option. All five AXI4 channels (AW, W, B, AR and R) interface to core logic at the die edge. The NoC initiator on the right shows the configuration with

the fabric NoC option. The AW, W, B, and AR AXI4 channels still interface to core logic at the die edge, but the read data transfers through the M20K memory blocks into the fabric, reducing routing congestion along the die edge.

Figure 11. NoC Initiators With and Without Fabric NoC

Read Data (R) (256b)

Read Address (AR)

Write Response (B)

Write Data (W) (256b)

NoC Initiator IP Without Fabric NoC

# 2.5. NoC Protocol Support

The hard memory NoC in Intel Agilex 7 M-Series FPGAs supports the following transaction protocols:

- AMBA AXI4 protocol—used by the memory controller targets, fabric initiators, and the two HPS AXI4 initiators.

- AMBA AXI4 Lite protocol—used by targets handling sideband operation, the HPS AXI4 Lite initiator, and by fabric initiators to communicate with AXI4 Lite targets through the NoC SSM.

# 2.5.1. AXI4 Protocol Support

Intel Agilex 7 M-Series FPGAs use AXI4 protocol for NoC initiators and NoC targets processing user read and write transaction requests and responses. The AMBA AXI4 in the hard memory NoC is fully compliant with the AXI4 specification, except for the following functions because there are no caches in the hard memory NoC or associated memory controllers.:

- Axregion

- AxCACHE

- AxLOCK is ignored

- Only two AxQOS bits are honored

- AxPROT is ignored

- AxREGION and AxCACHE do not need to be provided by a compliant AXI4 implementation

- For AxBURST, NoC targets, such as HBM2e and external memory controllers, support incrementing burst only. Refer to NoC Initiator Intel FPGA IP Interfaces.

## 2.5.2. AXI4 Handshaking Support

Since the NoC initiators are located along the top and bottom edges of the die, timing closure on the valid and ready signals at the interface between user logic and the NoC Initiator Intel FPGA IP can be a challenge without pipelining registers within the NoC Initiator Intel FPGA IP. This IP offers two AXI handshake pipelining schemes. The default AXI4 handshaking scheme optimizes for interface frequency and includes pipeline registers. Alternatively, you can select low area handshaking logic that may have an Fmax penalty.

Both handshaking schemes are fully AXI compliant. The schemes only differ in their internal trade-off between area and frequency.

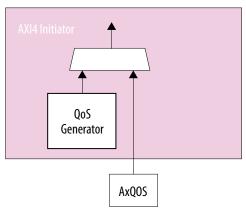

### 2.5.3. Quality of Service (QoS) Support

Quality of Service (QoS) is a technique that the hard memory NoC uses to provide control of arbitration choices that satisfy performance requirements. You can also use QoS to prioritize some traffic. You can change this prioritization dynamically, or set this prioritization during configuration. To achieve system goals, system architects can use the QoS settings to specify the relative priority of traffic flows.

One can categorize initiator generated traffic into the following groups, according to sensitivity to latency:

**Table 2.** Initiator-Generated Traffic Types

| Traffic Type         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-Time            | NoC initiators in this group are very sensitive to long-term and short-term latency, and fail when their buffers become empty. Examples include video display traffic and real-time applications. A video display engine must be able to fetch graphic data within a bounded amount of time to display images correctly on a monitor. Failing to meet real-time requirements may result in corrupt pixels or degradation of image sharpness or loss of screen synchronization. |

| Latency<br>Sensitive | The performance of this application type is directly linked to the latency of access. For example, in a CPU, processing can stop for many cycles when there is a cache miss.                                                                                                                                                                                                                                                                                                   |

| Best Effort          | NoC initiators in this group can tolerate delays that other traffic causes and are insensitive to latency. These NoC initiators consume the remaining bandwidth, and must not interfere with real-time or latency-sensitive traffic. For example, file transfer or file download applications can stall without compromising the experience.                                                                                                                                   |

AXI QoS determines the associated NoC QoS. Urgency level is the priority of traffic within the NoC subsystem. A system can have multiple priority levels for traffic going to and from the memory.

You can configure the NoC Initiator Intel FPGA IP to use AXI4 QoS signals to determine the associated NoC QoS, or to send all NoC traffic with a fixed priority. If you configure the NoC Initiator Intel FPGA IP to use a fixed NoC priority, you can specify separate priorities for read and write traffic.

You can choose to specify the QoS Generator priority levels when parameterizing the NoC Initiator Intel FPGA IP. The priority levels are not run-time programmable. For more information on the QoS Generator in the NoC Initiator Intel FPGA IP, refer to NoC Initiator Intel FPGA IP.

Figure 12. Options for Generating Quality of Service: QoS Generator vs. AxQOS

Table 3. Memory Priority Versus QoS Settings shows the mapping of QoS signals to the urgency value of the corresponding packets. The NoC subsystem has four priority levels (urgency = 0, 1, 2 or 3). Within the NoC subsystem, traffic with priority level zero (0) has the lowest priority, while traffic with priority level 3 has the highest priority. While the external memory interface Hard Memory Controller supports up to four priority levels, HBM2e Hard Memory Controller supports only two priority levels. Best effort traffic should have a default urgency level of zero (0), with higher urgency levels reserved for real-time and latency-sensitive traffic. Note that only the top two bits of the AXI command QoS (argos or awgos) map to a NoC quality-of-service option. The remaining bits are unused.

**Table 3.** Memory Priority Versus QoS Settings

| QoS[1:0] | Urgency Level | External Memory Priority<br>Level | HBM2e Priority Level |

|----------|---------------|-----------------------------------|----------------------|

| 2′b00    | 0             | 0                                 | 0                    |

| 2'b01    | 1             | 1                                 | 0                    |

| 2′b10    | 2             | 2                                 | 1                    |

| 2'b11    | 3             | 3                                 | 1                    |

#### 2.5.4. Transaction Ordering Support

The NoC subsystem is compliant with the AXI4 ordering model specification that is based on the use of the AxID AXI transaction identifier. Read transactions from the same NoC Initiator Intel FPGA IP that have the same ID complete in order, and similarly write transactions with the same ID complete in order. The AXI4 ordering model does not impose any order between reads and writes that have the same AXI ID. Transactions from the same NoC Initiator Intel FPGA IP that have different IDs have no reordering restriction.

## 2.5.5. AXI4 Lite Protocol Support

You use the AXI4 Lite protocol to access the control and status registers of subsystems, such as the UIB and GPIO-B. AXI4 Lite is a lightweight interface compared to AXI4, but is lower performance and higher latency without bursting support and other features.

# 2.6. NoC Design Considerations

Each hard memory NoC has several target and initiator locations available. The number and location of targets and initiators depends on several factors that this section describes in detail.

#### 2.6.1. Determining the Number of NoC Targets

The number of NoC targets in your design and their associated bandwidth depends on the type of memory resource that your design uses. Refer to the *High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA IP User Guide* or the *External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide* for details.

#### 2.6.2. Determining the Number of NoC Initiators

The number of NoC initiators in your design depends on the memory bandwidth requirements of the user logic functions. Calculate the bandwidth that an individual NoC initiator can support by multiplying the width of its data bus by the clock frequency of the logic driving the NoC initiator. Higher operating frequencies may require fewer NoC initiators but can encounter more difficulty when closing timing. Using the 512/576b fabric NoC option reduces shoreline congestion and allows timing closure at faster clock rates.

The NoC subsystems along the top and bottom edges of the FPGA die are independent. Therefore, plan the number of NoC initiators for each subsystem separately, based on the memory resources that you use along each die edge.

Note:

You can configure the NoC Initiator Intel FPGA IP to share a NoC initiator bridge between an AXI4 interface and up to four AXI4-Lite interfaces, unless you are using the fabric NoC on the same bridge.

#### 2.6.3. Fabric NoC Considerations

If you configure the NoC Initiator Intel FPGA IP with an AXI4 read data width of 512 or 576 bits, the IP implements the fabric NoC feature.

When you use this configuration, instead of delivering read data directly to the initiator read port, read data is written to a column of M20K memory blocks below the NoC initiator, as Figure 11. NoC Initiators With and Without Fabric NoC shows.

This configuration is ideal for applications that rely on high sequential read throughput. Usage of the fabric NoC feature for read data reduces pressure on fabric routing resources near the NoC initiator along the edge of the die.

Additionally, if you configure the NoC Initiator Intel FPGA IP with an AXI4 write data width of 512 or 576 bits, you can choose to implement the IP with a separate clock for the 256-bit wide initiator hardware. That clock can run as fast as 660 MHz for -1 speed grades, 630 MHz for -2 speed grades, and 430 MHz for -3 speed grade devices. With this option you can achieve up to 90% of sustained HBM2e write throughput. These 512-bit interfaces only support transactions that transfer multiples of 64 bytes, and target addresses that are aligned on 64-byte boundaries.

### 2.6.4. Latency Considerations

When choosing locations for NoC initiators and NoC targets, you must consider the impact of latency. The hard memory NoC consists of a horizontal array of switches that you attach to initiators and targets, as the diagrams in NoC Segments show.

Transactions between an initiator and target that are far apart laterally must transfer through many switches, increasing the minimum latency. Transactions between initiators and targets that connect to the same switch have the lowest latency. Figure 13. Horizontal Link Allocation for Top-Edge NoC and Figure 14. Horizontal Link Allocation for Bottom-Edge NoC show initiators and targets that connect to the same switch designated with Local connections.

## 2.6.5. Initiator and Target Bandwidth Considerations

On the FPGA fabric side of the hard memory NoC, you can calculate maximum initiator bandwidth by multiplying the user clock frequency by the width of the initiator data bus that is typically 32 Byte.

The bandwidth for NoC targets depends on the type and configuration of memory you use, such as HBM2e or DDR5 memory.

Refer to the *High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA IP User Guide* for HBM2e specifications. Refer to the *External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide* for external memory specifications (such as DDR4, DDR5, and LPDDR5).

#### **Related Information**

- High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 M-Series FPGA IP User Guide

- External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide

#### 2.6.6. Horizontal Bandwidth Considerations

The horizontal network of switches that comprise the hard memory NoC connect with 512-bit wide links. Within each hard memory NoC, there are two 512-bit links carrying request transactions (AW, W, AR) left-to-right, and an additional two 512-bit links carrying request transactions right-to-left. Similarly, there are two 512-bit links carrying response transactions (R, B) left-to-right, and two 512-bit links carrying response transactions right-to-left.

You can calculate the maximum bandwidth of each bus by multiplying the NoC operating frequency with the width of the bus. For example, if the hard memory NoC is operating at 1.4 GHz, then each 64-byte bus contributes 89.6 GB/s. Table 4. Hard Memory NoC Horizontal Bandwidth summarizes the total bandwidth in each direction for each transaction type. Note that the **Link Fmax** and **Max Bandwidth** are lower on speed-grade 3 devices.

Table 4. Hard Memory NoC Horizontal Bandwidth

| Transaction Type    | Direction         | Link<br>Count | Link<br>Width<br>(bit) | -1, -2<br>Speed<br>Grade<br>Link<br>Fmax<br>(GHz) | -1, -2 Speed<br>Grade Max<br>Bandwidth<br>(GB/s) | -3 Speed<br>Grade<br>Link<br>Fmax<br>(GHz) | -3 Speed<br>Grade Max<br>Bandwidth<br>(GB/s) |

|---------------------|-------------------|---------------|------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------|----------------------------------------------|

| Request (AW, W, AR) | Left-to-<br>Right | 2             | 512                    | 1.4                                               | 179.2                                            | 1.0                                        | 128                                          |

|                     | Right-to-<br>Left | 2             | 512                    | 1.4                                               | 179.2                                            | 1.0                                        | 128                                          |

| Response (R, B)     | Left-to-<br>Right | 2             | 512                    | 1.4                                               | 179.2                                            | 1.0                                        | 128                                          |

|                     | Right-to-<br>Left | 2             | 512                    | 1.4                                               | 179.2                                            | 1.0                                        | 128                                          |

Figure 13. Horizontal Link Allocation for Top-Edge NoC shows the links that connect to each NoC target. For each hard memory NoC along the top edge and bottom edge of the device, there are 24 NoC target interface bridges for connecting to HBM2e or external memory controllers. Again, for request transactions, there are two links in each direction. Each of these links connects to alternating NoC targets. LR0 and LR1 are the two links that carry traffic left-to-right. RL0 and RL1 are the two links that carry traffic right-to-left. Some of the connections are Local, which indicates that the initiator and target connect to the same switch. Traffic between such an initiator and target need not transfer horizontally.

Figure 13. Horizontal Link Allocation for Top-Edge NoC (AXI4 Lite Targets Not Shown)

|              | NoC Segment           | GPIC  | )-B_0 | GPIC  | )-B_1 |       |       | UIB_L |       |       |       |       | UIE   | B_M   |       |       | UIB_R |       |       |       |       | GPIO-B_2 GPIO-B/HPS |       |       |       |  |

|--------------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|-------|-------|-------|--|

| NoC Segment  | Target→<br>Initiator↓ | T0    | T2    | T0    | T2    | T3    | T4    | T5    | T6    | T7    | T0    | T1    | T2    | T3    | T4    | T5    | T0    | T1    | T2    | T3    | T4    | T0                  | T2    | T0    | T2    |  |

|              | 10                    | Local | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

| GPIO-B_0     | I1                    | RLO   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | Local | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 10                    | RLO   | RL1   | Local | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

| GPIO-B_1     | l1                    | RLO   | RL1   | RLO   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | RL1   | RLO   | Local | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 10                    | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

| UIB_L        | I1                    | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 10                    | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | Local | Local | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

| UIB_M        | I1                    | RLO   | RL1   | RLO   | Local | Local | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | RL1   | RLO   | Local | Local | LR1   | LR0   | LR1   | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 10                    | RLO   | RL1   | RLO   | Local | LR0   | LR1   | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

| UIB_R        | I1                    | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | RL1   | Local | Local | LR0                 | LR1   | LR0   | LR1   |  |

|              | 10                    | RLO   | RL1   | RL0   | RL1   | Local               | LR1   | LR0   | LR1   |  |

| GPIO-B_2     | l1                    | RLO   | RL1   | RLO                 | LR1   | LR0   | LR1   |  |

|              | 12                    | RLO   | RL1   | RLO                 | Local | LR0   | LR1   |  |

|              | 10(fabric)            | RLO   | RL1   | RLO                 | RL1   | Local | LR1   |  |

| CDIO D/ILIDO | 11(fabric)            | RLO   | RL1   | RLO                 | RL1   | RLO   | LR1   |  |

| GPIO-B/HPS   | IO(MPFE)              | RLO   | RL1   | RLO                 | RL1   | RLO   | Local |  |

|              | I2(MPFE)              | RLO   | RL1   | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | RL0   | RL1   | RLO   | RL1   | RLO                 | RL1   | RLO   | Local |  |

Figure 14. Horizontal Link Allocation for Bottom-Edge NoC (AXI4 Lite Targets Not Shown)

|             | NoC Segment             | GPIC  | )-B_0 | GPIC  | )-B_1 |       |       | UIB_L |       |       |     |       | UIE   | B_M   |       |       |       |       | UIB_F |       |       | GPIO  | )-B_2 | GPIO- | -B_3  |

|-------------|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NoC Segment | Target →<br>Initiator ↓ | T0    | T2    | T0    | T2    | T3    | T4    | T5    | T6    | T7    | T0  | T1    | T2    | T3    | T4    | T5    | T0    | T1    | T2    | T3    | T4    | T0    | T2    | T0    | T2    |

| SDM         | 10                      | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | Local | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

| GPIO-B_0    | l1                      | RLO   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | I2                      | RLO   | Local | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | RLO   | RL1   | Local | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

| GPIO-B_1    | l1                      | RLO   | RL1   | RLO   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 12                      | RLO   | RL1   | RLO   | Local | LR0   | LR1   | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

| UIB_L       | l1                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 12                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | LR1 | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   |     | Local | LR1   | LR0   | LR1   |

| UIB_M       | l1                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | Local | Local | LR1   | LR0   | LR1   |

|             | 12                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | Local | Local | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RL0   | RL1   | RLO   | RL1   | RLO   | Local | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

| UIB_R       | l1                      | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0   | LR1   | LR0   | LR1   |

|             | 12                      | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RL0   | RL1 | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | Local | LR0   | LR1   | LR0   | LR1   |

|             | 10                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RL0   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | LR1   | LR0   | LR1   |

| GPIO-B_2    | l1                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | LR1   | LR0   | LR1   |

|             | 12                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | Local | LR0   | LR1   |

|             | 10                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | Local | LR1   |

| GPIO-B_3    | l1                      | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RLO   | LR1   |

|             | I2                      | RLO   | RL1   | RL0   | RL1   | RLO   | RL1   | RL0   | RL1   | RL0   | RL1 | RLO   | RL1   | RLO   | RL1   | RLO   | RL1   | RL0   | RL1   | RL0   | RL1   | RLO   | RL1   | RLO   | Local |

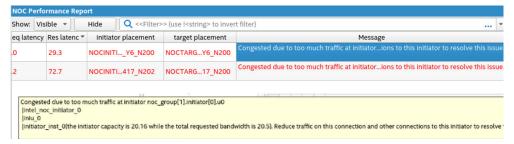

When placing NoC initiators and NoC targets, placing some initiators to the left of their targets and some initiators to the right of their targets can reduce congestion on the hard memory NoC. Because there are separate links for carrying traffic right-to-left versus left-to-right, connections where the initiator is to the left of the target do not compete for bandwidth with connections where the initiator is to the right of the target. Also, because separate links service consecutive targets (for example RLO versus RL1), traffic to one target does not compete for bandwidth with traffic to an adjacent target.

For example, two initiators on the right side of the die with high bandwidth requirements for targets on the left side of the die can require communication over the same links if the  $\mathtt{RL0}$  link services both targets.

If the RL0 link services one of the targets, while the RL1 link services the other target, the two connections do not compete for bandwidth. Alternatively, if one of the initiators moves to the left of its target, the read traffic then uses one of the left-to-right links (for example LR0), and does not compete for bandwidth with other traffic using the right-to-left links (such as RL0).

Figure 15. Example NoC Exceeding Horizontal Bandwidth Limits shows an example of the top-edge hard memory NoC with targets in the UIB segment sending read data to initiators to the left side.

Figure 15. Example NoC Exceeding Horizontal Bandwidth Limits

Maximum Read Bandwidth Requirement LR0 link = 120 GB/s > 89.6 GB/s Bandwidth Capacity

Note:

In Figure 15. Example NoC Exceeding Horizontal Bandwidth Limits if each of these connections carries 20 GB/s of data, the maximum demand on the horizontal link is 120 GB/s. This maximum demand is greater than the 89.6 GB/s capacity of the link. Note that this example only shows targets that the LRO horizontal link services. The LR1 link services other targets and does not compete for bandwidth with these initiator-target connections.

You can alleviate such bandwidth overload by placing some high bandwidth initiators to the left of their targets, and other high bandwidth initiators to the right of their targets.

Note:

Transactions between initiators and targets that connect directly to the same switch route locally, and need not transfer horizontally along these links. Therefore, the horizontal bandwidth that these local connections use does not count against the horizontal bandwidth limits.

In Figure 16. Example NoC Within Horizontal Bandwidth Limits, the locations of initiators from the previous example change. Some initiators are to the left of their targets (using the LR0 horizontal link), some initiators are to the right of their targets (using the RL0 horizontal link), and some initiators are directly across from their targets (represented by a vertical arrow using local connections instead of the horizontal links).

Figure 16. Example NoC Within Horizontal Bandwidth Limits

Maximum Read Bandwidth Requirement on LRO link = 40 GB/s < 89.6 GB/s Bandwidth Capacity

#### 2.6.7. GPIO-B Bypass Mode and Initiators

Another consideration for hard memory NoC target and initiator placement is the use of GPIO-B blocks to implement low-speed memory configurations or GPIO functions. This technique bypasses the hard memory NoC. Due to device routing limitations, you cannot simultaneously use GPIO-B blocks implementing functions in bypass mode, and all of the NoC initiators directly opposite these GPIO-B blocks. Thus, using GPIO-B blocks in bypass mode prevents placement of NoC initiators in certain locations. Conversely, initiator placement can prevent certain GPIO-B blocks from implementing functions using bypass mode.

Figure 17. Routing Choice: NoC Initiator Usage Versus NoC Bypass Usage

Use the Interface Planner in the Intel Quartus Prime Pro Edition software to obtain an accurate view of the placement restrictions. Place GPIO-B functions that bypass the hard memory NoC first, preferably using a GPIO-B at an extreme end of one of the hard memory NoCs. Use Interface Planner to generate legal locations for placement of initiators. Interface Planner displays the NoC initiator locations that are available and the locations that are unavailable.

For additional details on using the Interface Planner tool to plan periphery functions in Intel Agilex 7 M-Series FPGAs, refer to Making Physical Assignments Using Interface Planner.

For general information on using the Interface Planner tool, refer to *Intel Quartus Prime Pro Edition User Guide: Design Constraints*.

#### **Related Information**

Intel Quartus Prime Pro Edition User Guide: Design Constraints

# 3. NoC Design Flow in Intel Quartus Prime Pro Edition

# 3.1. Hard Memory NoC Design Flow Overview

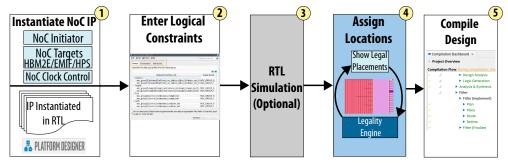

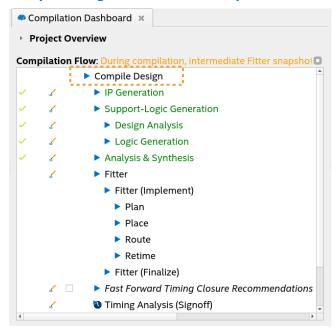

Creating a hard memory NoC design in the Intel Quartus Prime software consists of the following high level steps that this chapter describes in detail:

**Hard Memory NoC Design Flow** Figure 18.

1. Instantiate and configure NoC-related IP, including the NoC Initiator Intel FPGA IP, the HBM2E IP or external memory IP that contain the NoC targets, the NoC Clock Control Intel FPGA IP, and (if using) the Hard Processor System Intel Agilex 7/ Agilex 9 FPGA IP in your design using Platform Designer or directly in design RTL.

Note: If your design includes the Hard Processor System Intel Agilex 7 / Agilex 9 FPGA IP, you must configure and instantiate this IP using Platform Designer.

- 2. Define logical constraints for NoC grouping, connectivity, addressing, and performance targets.

- 3. (Optional) Perform RTL simulation of the NoC design, as Simulating NoC Designs describes.

- 4. (Recommended) Run Analysis & Synthesis and then assign physical locations for NoC elements and other periphery elements, as Make Physical Assignments Using Interface Planner describes. Otherwise, the Intel Quartus Prime Fitter makes the physical assignments during design compilation.

- 5. Compile your design and review the placement and performance reports, as Compiling the NoC Design describes.

#### 3.1.1. NoC Design Flow Options

The Intel Quartus Prime software supports the following two flows for NoC design:

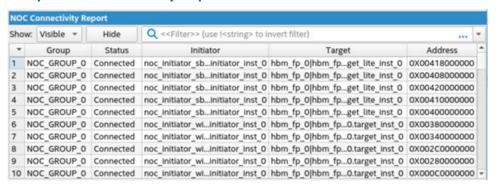

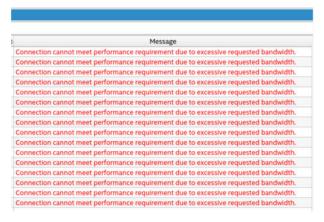

- Platform Designer Connection Flow—you use Platform Designer to configure and instantiate your NoC-related IP. You also use Platform Designer to make connections between NoC initiator bridges and NoC target bridges and to define the addressing mapping for these connections. Once you generate HDL for your Platform Designer system, your design is ready for RTL simulation. You must use the NoC Assignment Editor to create additional assignments, such as specifying NoC groupings and optional performance targets. You can use Interface Planner to make physical location assignments for your NoC elements. Then you compile your design and review the results.

- NoC Assignment Editor Connection Flow—you can configure and instantiate

your NoC-related IP in either Platform Designer or directly in RTL. You then use

the NoC Assignment Editor to make all NoC assignments including grouping,

connectivity, address mapping, and optional performance targets. After completing

the assignments and rerunning Analysis & Elaboration, your design is ready for

RTL simulation. You can use Interface Planner to make physical location

assignments for your NoC elements. Then compile your design and review the

results.

The NoC design flow that you select impacts the NoC design entry method, how you specify NoC connectivity and addressing assignments, and at what stage you can perform RTL simulation of the NoC. Subsequent stages of the design flow, such as assigning physical locations, compiling, and reviewing results, are the same in both flows.

Table 5. Comparison of Platform Design Connection Flow and NoC Assignment Editor Connection Flow

| Design Steps                                         | Platform Designer Connection Flow                   | NoC Assignment Editor<br>Connection Flow                                        |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Configure NoC-related IP                             | Parameter Editor launched from<br>Platform Designer | Parameter Editor launched from<br>either Platform Designer or IP<br>Catalog     |  |  |  |  |

| Instantiate NoC-related IP in your design            | Platform Designer only                              | Either Platform Designer or<br>directly in RTL                                  |  |  |  |  |

| Connect NoC initiator bridges and NoC target bridges | Platform Designer                                   | NoC Assignment Editor                                                           |  |  |  |  |

| Define address maps for NoC connections              | Platform Designer                                   | NoC Assignment Editor                                                           |  |  |  |  |

| Specify NoC grouping                                 | NoC Assign                                          | ment Editor                                                                     |  |  |  |  |

| Specify NoC performance targets                      | NoC Assign                                          | ment Editor                                                                     |  |  |  |  |

| Assign physical locations                            | Interface                                           | e Planner                                                                       |  |  |  |  |

| Compile design and review results                    | Intel Quartus Pi                                    | rime Pro Edition                                                                |  |  |  |  |

| Ready for RTL simulation                             | After generating HDL in<br>Platform Designer        | After completing NoC<br>Assignment Editor and running<br>Analysis & Elaboration |  |  |  |  |

#### **Related Information**

- Creating NoC Assignments for Compilation on page 40

- Generating a Simulation Registration Include File (Platform Designer Connection Flow) on page 63

# 3.2. Using NoC Example Designs

To quickly start a design from a complete, pre-verified design example that uses the hard memory NoC, you can access a design example from within the Intel Quartus Prime Pro Edition software. These design examples include the following:

- A complete Intel Quartus Prime project that contains a Platform Designer system that instantiates and connects the hard memory NoC IP, including the following IP:

- NoC Initiator Intel FPGA IP connected to traffic generators.

- Targets within the memory IP (HBM2e Intel FPGA IP or External Memory Controller (EMIF) IP).

- Clock Control Intel FPGA IP.

- Assignments to implement connectivity and address mapping for the use case.

- Simulation models and testbench.

The following steps summarize the process to create a hard memory NoC user design based on an available design example in the Intel Quartus Prime Pro Edition software. These example designs specify NoC connectivity and addressing using the NoC Assignment Editor. Because these example design simulation testbenches include the necessary registration statements, you can perform RTL simulation before running Analysis & Elaboration.

- In the Intel Quartus Prime software IP Catalog or Platform Designer IP Catalog, double-click the appropriate memory IP:

- High Bandwidth Memory (HBM2e) Interface Intel Agilex 7 FPGA IP

Or

- External Memory Interfaces (EMIF) IP

- 2. In the IP parameter editor, configure the desired parameters for your use case on the **General** tab. On the **Example Design** tab, configure the options related to your hard memory NoC implementation.

- 3. Click the **Generate Example Design** button. Specify a location and file name to generate and open the example design.

For details on characteristics and accessing HBM2e and eternal memory Intel FPGA IP example designs, refer to the following resources.

#### **Related Information**

- External Memory Interfaces Intel Agilex 7 M-Series FPGA IP Design Example User Guide

- High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 M-Series FPGA IP Design Example User Guide

- Intel Quartus Prime Pro Edition User Guide: Getting Started

# 3.3. NoC Building Blocks

Creating a hard memory NoC design involves the following building blocks that you configure using corresponding Intel FPGA IP:

- NoC Initiators—for fabric-facing initiators, configure using the NoC Initiator Intel FPGA IP. If you are using the Hard Processor System Intel Agilex 7 /Agilex 9 FPGA IP, this IP includes the HPS-facing initiators.

- NoC Targets—for memory resources that the FPGA fabric uses, you configure the

targets using the High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA

IP and External Memory Interfaces (EMIF). For memory resources that the HPS

uses, you configure the targets using the External Memory Interfaces for HPS Intel

FPGA IP.

- NoC Clock Control—configure the NoC PLL and NoC SSM using the NoC Clock Control Intel FPGA IP.

#### **Related Information**

Hard Memory NoC IP Reference on page 68

# 3.3.1. NoC Initiators for Hard Processor Systems

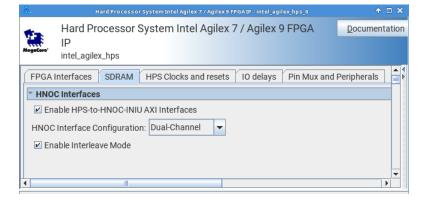

Configure NoC initiators for hard processor systems (HPS) using the Hard Processor System Intel Agilex 7 / Agilex 9 FPGA IP. To enable NoC initiators for HPS when parameterizing the Hard Processor System Intel Agilex 7 / Agilex 9 FPGA IP, follow these steps:

- 1. Click the **SDRAM** tab in the IP Parameter Editor.

- 2. Turn on the Enable HPS-to-HNOC-INIU AXI Interfaces option.

- 3. Select one of the following **HNOC Interface Configuration** options:

- Single-Channel—this configuration instantiates one initiator in the MPFE.

Select Single-Channel configuration for memory capacity up to 64 GB when you do not require interleaving.

- Dual-Channel—this configuration instantiates two initiators in the MPFE. You

can also turn on the Enable Interleave Mode option to enable logic in the

MPFE to interleave between the HPS-EMIF channels. Select Dual-Channel

configuration for memory capacity above 64 GB or when enabling interleaving.

Figure 19. SDRAM Tab of Hard Processor System Intel Agilex 7 / Agilex 9 FPGA IP Parameter Editor

NoC initiators for HPS can only connect to NoC targets in External Memory Interfaces for HPS Intel FPGA IP. For further information on HPS, refer to the *Intel Agilex 7 Hard Processor System Component Reference Manual*.

#### **Related Information**

Intel Agilex 7 Hard Processor System Component Reference Manual

#### 3.3.2. NoC Targets for Hard Processor Systems

Configure NoC targets for HPS using the External Memory Interfaces for HPS Intel FPGA IP. This IP always uses the NoC and does not have a bypass mode available. NoC targets for HPS can only connect to NoC initiators in Hard Processor System Intel Agilex 7 / Agilex 9 FPGA IP. For details on the External Memory Interfaces for HPS Intel FPGA IP, refer to the External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide.

#### **Related Information**

External Memory Interfaces Intel Agilex 7 M-Series FPGA IP User Guide

# 3.3.3. NoC Initiators for Fabric AXI4 Managers

Configure hard memory NoC initiators for fabric AXI4 managers using the NoC Initiator Intel FPGA IP in either IP Catalog or Platform Designer. Access the NoC Initiator Intel FPGA IP in the IP Catalog by expanding the **Intel FPGA Interconnect** category, and then expanding the **NoC** subcategory.

The NoC Initiator Intel FPGA IP allows the creation of multiple AXI4 and AXI4 Lite interfaces using the same configuration that interfaces to the same hard memory NoC subsystem. If your design requires NoC initiators with different configurations, or if your design uses both hard memory NoC subsystems along the top edge and bottom edge of the die, this configuration requires separate NoC Initiator Intel FPGA IP. Each AXI4 interface in the NoC Initiator Intel FPGA IP maps to one hard memory NoC initiator bridge.

In the IP parameter editor, you specify the following parameters for the IP instance:

- Specify a value for the Number of AXI4 interfaces and Number of AXI4 Lite interfaces. Each AXI4 interface is associated with its own physical NoC initiator bridge. AXI4 Lite interfaces, used to access control and status registers of NoC peripherals, are associated with the first physical NoC initiator bridge. If an instance of the NoC initiator IP has the number of AXI4 interfaces set to 0, that instance uses only one NoC initiator bridge that carries the AXI Lite transactions from all the exposed AXI Lite interfaces.

- Specify whether the AXI4 and AXI4 Lite interfaces have per-interface clock and reset signals, or whether the interfaces share these signals. If you do not configure for per-interface clock and reset signals, the IP exposes a single shared clock sink and reset sink interface for all AXI4 interfaces, and exposes a separate shared clock sink and reset sink for all AXI4 Lite interfaces.

- Select the data width for read and write interfaces using the AXI4 Data Mode

parameter. Selections with read data width of 512 or 576 bits implement the fabric

NoC to transport read response data directly into M20K memory blocks. If you

select data widths of 288 or 576 bits, the AXI4 WUSER and RUSER signals carry the

extra data bits.

- If using a 512 or 576 bit wide data mode, additionally specify whether the wide interfaces use an independent clock from the 256-bit NoC initiator hardware. Enable this option for best system-level performance when using wide data modes.

- Use the AXI4 interface handshaking parameter to optimize the interface handshaking for either f<sub>MAX</sub> or area. AXI4 Handshaking Support on page 18 describes this option.

- Use the NoC QoS Mode parameter to specify whether AXI4 priority applies

individually on each AXI4 transaction (AXI QoS option), or hard codes a single

priority level into each interface (NOC Bridge generated option). For QoS

details, refer to Quality of Service (QoS). If using the NoC Bridge generated

option, additionally select the hard-coded values for NoC priority for Reads and

NoC priority for Writes.

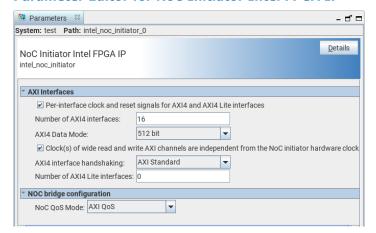

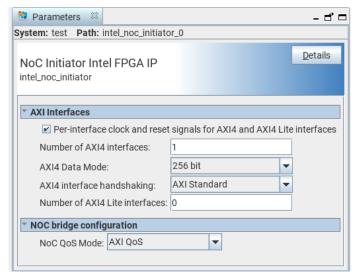

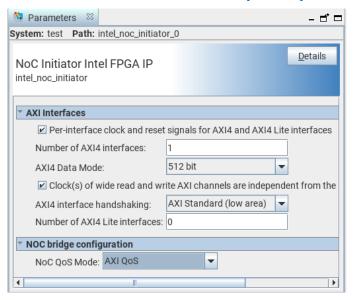

For example, Figure 20. Parameter Editor for NoC Initiator Intel FPGA IP shows the following NoC Initiator Intel FPGA IP configuration:

- The IP instance has 16 AXI4 interfaces and 0 AXI4 Lite interfaces.

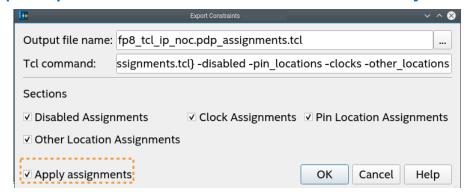

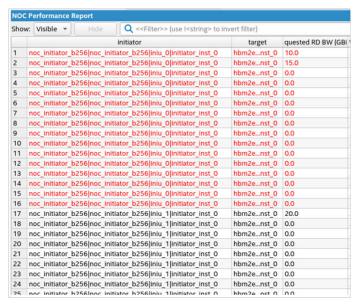

- The AXI4 read and write channels are configured for 512-bit wide transactions. Since the interface is symmetrical, one AXI interface is exposed, which includes all 5 AXI channels (R, AR, W, AW, B).