## **Jetson Thor Series Modules**

Design Guide

## **Document History**

### DG-12084-001\_v1.1

| Version | Date          | Description of Change                  |

|---------|---------------|----------------------------------------|

| 1.0     | June 18, 2025 | Initial release                        |

| 1.1     | July 3, 2025  | Updated the following:                 |

|         |               | > Removed DMIC5                        |

|         |               | > Figure 5-2, Figure 5-8               |

|         |               | > Note under Figure 5-3 and Figure 5-5 |

|         |               | > Section 5.1.1                        |

|         |               | > Added section 5.1.3                  |

### Table of Contents

| Chapter   | 1.    | Introduction                                               | 1  |

|-----------|-------|------------------------------------------------------------|----|

| 1.1       | Ref   | erences                                                    | 1  |

| 1.2       | Att   | achments                                                   | 2  |

| 1.3       | Abb   | previations and Definitions                                | 2  |

| Chapter 2 | 2.    | Introduction                                               | 4  |

| Chapter 3 | 3.    | Main Connector Details                                     | 5  |

| 3.1       | Cor   | nector Pin Orientations                                    | 6  |

| 3.2       | Мо    | dule to Carrier Board Standoff                             | 7  |

| 3.3       | Мо    | dule to Carrier Board Standoff Height Recommendations      | ٤  |

| 3.4       | Мо    | dule Installation and Removal                              | 10 |

| Chapter 4 | 4.    | Reference Design Considerations                            | 11 |

| Chapter ! | 5.    | Power                                                      | 13 |

| 5.1       | Pov   | ver Sequencing                                             | 16 |

| 5.1.1     | 1     | Power-On Sequence                                          | 16 |

| 5.1.2     | 2     | Power Down Sequence by Power Button Press                  | 17 |

| 5.1.3     | 3     | Power Down Sequence by Software Shutdown                   | 18 |

| 5.1.4     | 4     | Power Down Sequence by an Event                            | 19 |

| 5.2       | SYS   | S_VIN_HV Input                                             | 21 |

| 5.3       | Pov   | ver-On                                                     | 21 |

| 5.3.      | 1     | Auto Power-on                                              | 22 |

| 5.3.2     | 2     | Power Button Supervisor MCU Circuit                        | 22 |

| 5.3       | 3.2.1 | Defined Behaviors                                          | 23 |

| 5.3       | 3.2.2 | Power-OFF -> Power-ON (Power Button Case)                  | 24 |

| 5.3       | 3.2.3 | Power-OFF -> Power-ON (Auto-Power-On Case)                 | 25 |

| 5.3       | 3.2.4 | Power-ON -> Power-OFF (Power Button Held Low > 10 Seconds) | 26 |

| 5.4       | Pov   | ver Discharge                                              | 27 |

| 5.5       | Pov   | ver Loss Detection                                         | 27 |

| 5.6       | Dee   | ep Sleep or SC7                                            | 27 |

| Chapter 6 | 6.    | General Routing Guidelines                                 | 28 |

| 6.1       | Sigi  | nal Name Conventions                                       | 28 |

| 6.2       | Ro  | uting Guideline Format                  | 29  |

|-----------|-----|-----------------------------------------|-----|

| 6.3       | Sig | nal Routing Conventions                 | 29  |

| 6.4       | Ro  | uting Guidelines                        | 29  |

| 6.5       | Ge  | neral PCB Routing Guidelines            | 30  |

| Chapter 7 | 7.  | USB, PCIe, and MGBE                     | 32  |

| 7.1       | US  | В                                       | 35  |

| 7.1.1     |     | USB 2.0 Design Guidelines               | 39  |

| 7.1.2     |     | USB 3.2 Design Guidelines               | 40  |

| 7.1.3     | }   | Common USB Routing Guidelines           | 44  |

| 7.2       | РС  | l Express                               | 45  |

| 7.2.1     |     | PCIe Design Guidelines up to Gen5       | 52  |

| 7.2.2     |     | Ethernet via PCIe                       | 57  |

| 7.3       | MC  | BBE                                     | 60  |

| 7.3.1     |     | 10 GbE MGBE Design Guidelines           | 62  |

| 7.3.2     |     | 25 GbE MGBE Design Guidelines           | 67  |

| 7.3.3     | }   | Reference Clock Oscillator Requirements | 68  |

| 7.3.4     | Ļ   | Camera Over Ethernet                    | 70  |

| Chapter 8 | 3.  | Storage                                 | 71  |

| Chapter 9 | 9.  | Display                                 | 72  |

| 9.1       | DP  |                                         | 75  |

| 9.1.1     |     | DP Routing Guidelines                   | 78  |

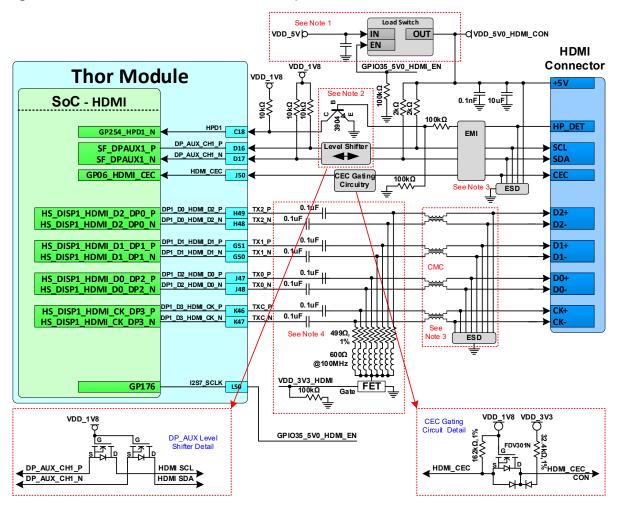

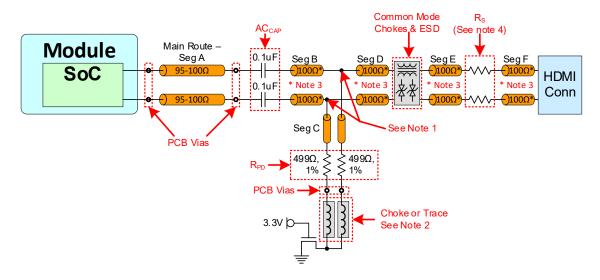

| 9.2       | HD  | MI                                      | 82  |

| 9.2.1     |     | HDMI Design Guidelines                  | 84  |

| Chapter 1 | 0.  | Video Input                             | 89  |

| 10.1      | CS  | I D-PHY Design Guidelines               | 97  |

| 10.2      | CS  | I C-PHY Design Guidelines               | 97  |

| Chapter 1 | 1.  | Audio                                   | 100 |

| 11.1      | 125 | Design Guidelines                       | 102 |

| 11.2      | DN  | IIC Design Guidelines                   | 103 |

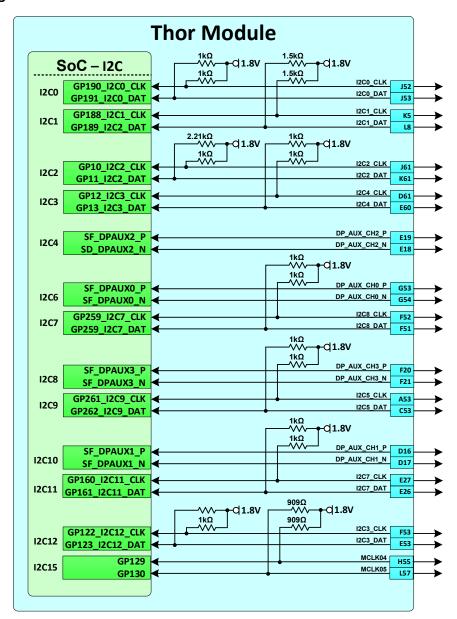

| Chapter 1 | 2.  | 12C                                     | 104 |

| 12.1      | 120 | Design Guidelines                       | 107 |

| 122       | Do  | hounce                                  | 100 |

| Chapter 1 | 13. | SPI                                                    | 109 |

|-----------|-----|--------------------------------------------------------|-----|

| 13.1      | SP  | l Design Guidelines                                    | 111 |

| Chapter 1 | 14. | UART                                                   | 112 |

| 14.1      | UΔ  | RT Design Guidelines                                   | 113 |

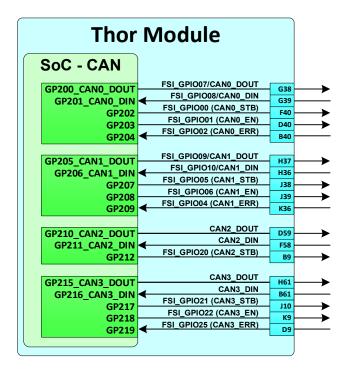

| Chapter 1 | 15. | CAN                                                    | 115 |

| 15.1      | CA  | N Design Guidelines                                    | 117 |

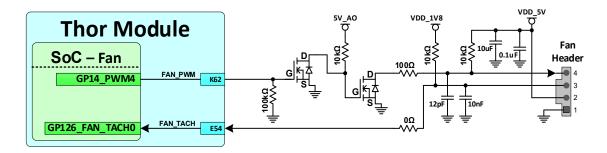

| Chapter 1 | 16. | Fan                                                    | 118 |

| Chapter 1 | 17. | Debug                                                  | 120 |

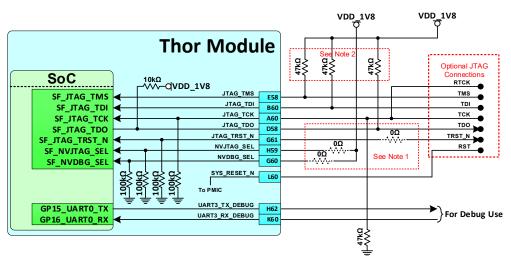

| 17.1      | US  | B Recovery Mode                                        | 120 |

| 17.2      | JT  | AG and Debug UART                                      | 120 |

| 17.2      | .1  | JTAG                                                   | 121 |

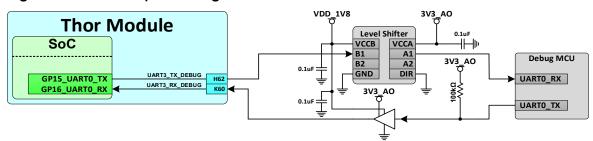

| 17.2      | .2  | Debug UART                                             | 123 |

| Chapter 1 | 18. | Strapping Pins                                         | 124 |

| Chapter 1 | 19. | Pads                                                   | 126 |

| 19.1      | MF  | PIO Pad Behavior when Associated Power Rail is Enabled | 126 |

| 19.2      | Sc  | hmitt Trigger Usage                                    | 126 |

| 19.3      | Pir | ns Pulled and Driven During Power-on                   | 127 |

| Chapter 2 | 20. | Unused Interface Terminations                          | 128 |

| 20.1      | Un  | used MPIO Interfaces                                   | 128 |

| 20.2      | Un  | used SFIO Interface Pins                               | 129 |

| Chapter 2 | 21. | General Layout Guidelines                              | 130 |

| 21.1      | Via | a Guidelines                                           | 130 |

| 21.1      | .1  | Via Count and Trace Width                              | 130 |

| 21.1      | .2  | Via Placement                                          | 130 |

| 21.1      | .3  | Via Placement and Power and Ground Corridors           | 131 |

| 21.2      | Со  | nnecting Vias                                          | 132 |

| 21.3      | Tra | ace Guidelines                                         | 132 |

| 21.3      | .1  | Layer Stack-Up                                         | 132 |

| 21.3      | .2  | Trace Length or Delay                                  | 132 |

| Chapter 2 | 22. | Stack-Ups                                              | 133 |

| 22.1      | Re  | ference Design Stack-ups                               | 133 |

| 22.1      | .1  | Importance of Stack-up Definition                      | 133 |

| 22.1.2      | Impact of Stack-up Definition on Design   | 133 |

|-------------|-------------------------------------------|-----|

| Chapter 23. | USB 3.2 and Wireless Coexistence          | 134 |

| 23.1 M      | itigation Techniques                      | 134 |

| Chapter 24. | Transmission Line Primer                  | 136 |

| 24.1 Ba     | asic Board Level Transmission Line Theory | 136 |

| 24.1.1      | Characteristics                           | 136 |

| 24.2 Pł     | nysical Transmission Line Types           | 137 |

| 24.2.1      | Microstrip Transmission Line              | 137 |

| 24.2.2      | Stripline Transmission Line               | 137 |

| 24.3 Dr     | iver Characteristics                      | 138 |

| 24.4 Re     | eceiver Characteristics                   | 138 |

| 24.5 Tr     | ansmission Lines and Reference Planes     | 139 |

| Chapter 25. | Design Guideline Glossary                 | 142 |

# List of Figures

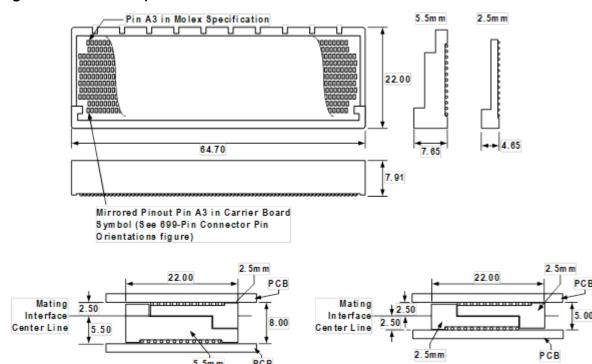

| Figure 3-1.  | 699-pin Connector Dimensions                                  | 5   |

|--------------|---------------------------------------------------------------|-----|

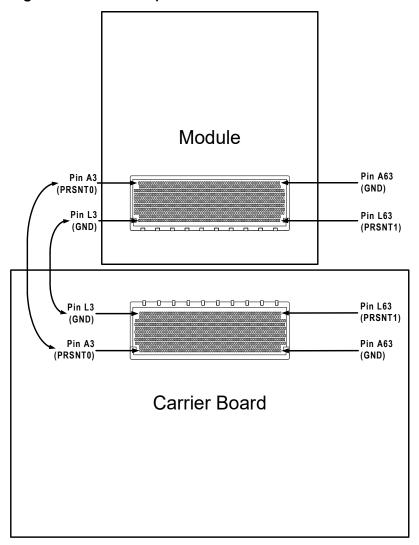

| Figure 3-2.  | 699-pin Connector Pin Orientation                             | 6   |

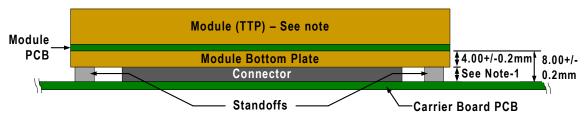

| Figure 3-3.  | 5.5 mm Height on Carrier Board                                | 7   |

| Figure 3-4.  | 2.5 mm Height on Carrier Board                                | 7   |

| Figure 3-5.  | Module Removal                                                | 10  |

| Figure 5-1.  | Power Block Diagram                                           | 15  |

| Figure 5-2.  | Power-On Sequence (Power Button Case)                         | 17  |

| Figure 5-3.  | Power Down Sequence - Button Press Shutdown Case              | 18  |

| Figure 5-4.  | Power Down Sequence - User Initiated - Software Shutdown Case | 19  |

| Figure 5-5.  | Power Down Sequence - Shutdown Due to an Event Case           | 20  |

| Figure 5-6.  | Simplified Microfit Connector Connections                     | 21  |

| Figure 5-7.  | Power-On Button Circuit                                       | 23  |

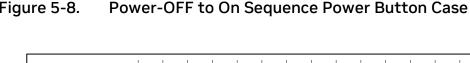

| Figure 5-8.  | Power-OFF to On Sequence Power Button Case                    | 24  |

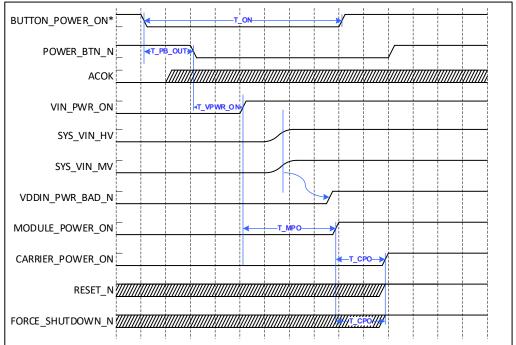

| Figure 5-9.  | Power-OFF to On Sequence Auto Power-On Case                   | 25  |

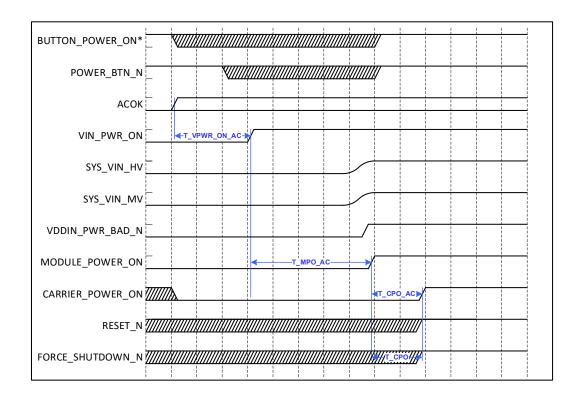

| Figure 5-10. | Power-ON to OFF Power Button Held Low > 10 Seconds            | 26  |

| Figure 5-11. | Power Discharge                                               | 27  |

| Figure 5-12. | VIN Loss Detection Circuit                                    | 27  |

| Figure 6-1.  | Signal Routing Example                                        | 30  |

| Figure 7-1.  | Simple USB Type A Connection Example with HUB                 | 36  |

| Figure 7-2.  | Simple USB Type A Connection Example without HUB              | 36  |

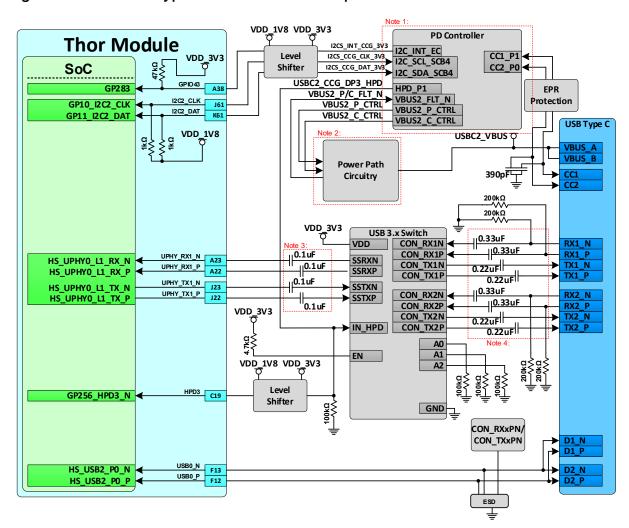

| Figure 7-3.  | USB Type-C Connection Example                                 | 37  |

| Figure 7-4.  | USB Type-C Dual Mode Circuitry Sample Connections             | 38  |

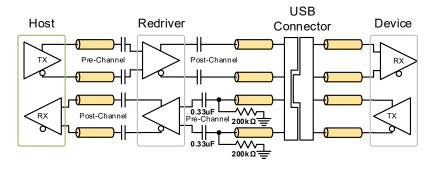

| Figure 7-5.  | USB3.x Path Model With Redriver                               | 44  |

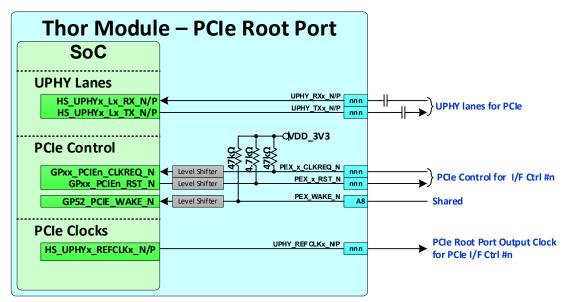

| Figure 7-6.  | PCIe Signal Connections (Root Port)                           | 46  |

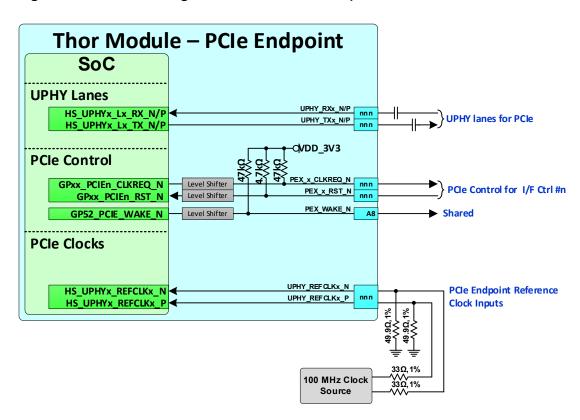

| Figure 7-7.  | PCIe Signal Connections (Endpoint)                            | 47  |

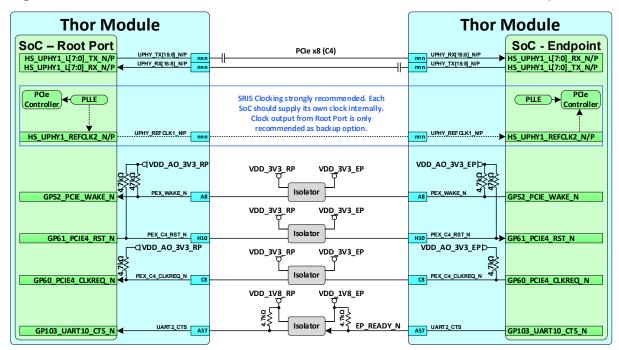

| Figure 7-8.  | PCIe Jetson Thor RP to Jetson Thor EP connection Example      | 51  |

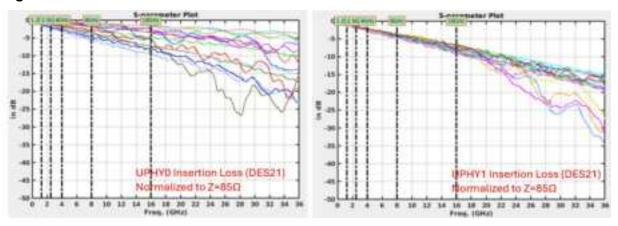

| Figure 7-9.  | Insertion Loss S-Parameter Plot (DES21)                       | 56  |

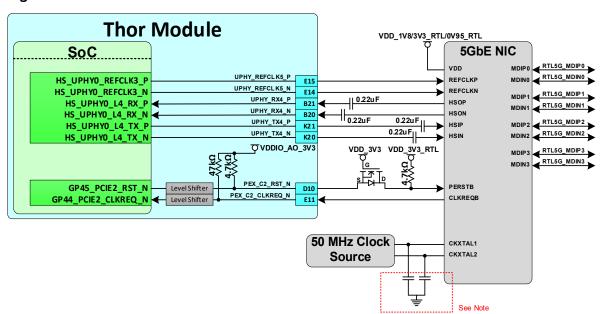

| Figure 7-10. | Ethernet Connections                                          | 58  |

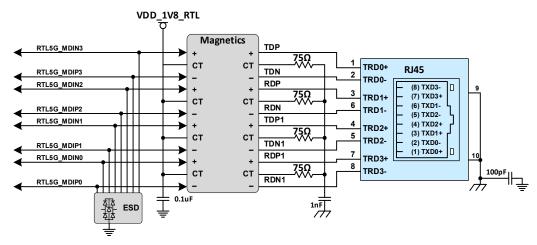

| Figure 7-11. | Ethernet Magnetics and RJ45 Connections                       | 58  |

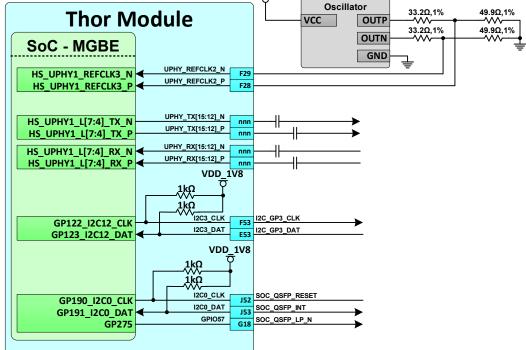

| Figure 7-12. | QSFP Connection Example                                       | 60  |

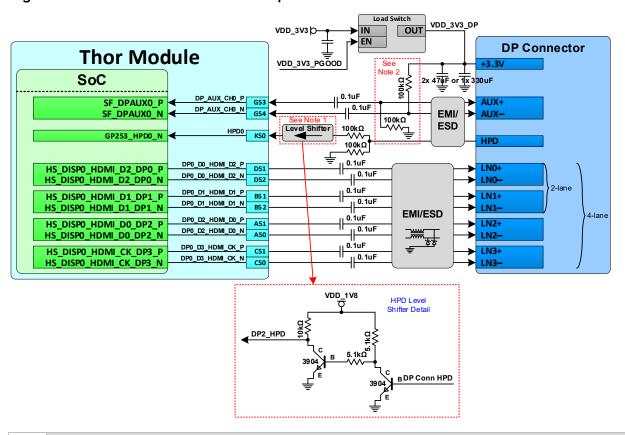

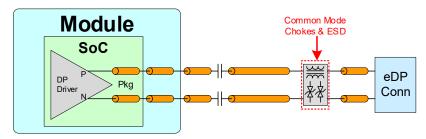

| Figure 9-1.  | DP Connection Example                                         | 75  |

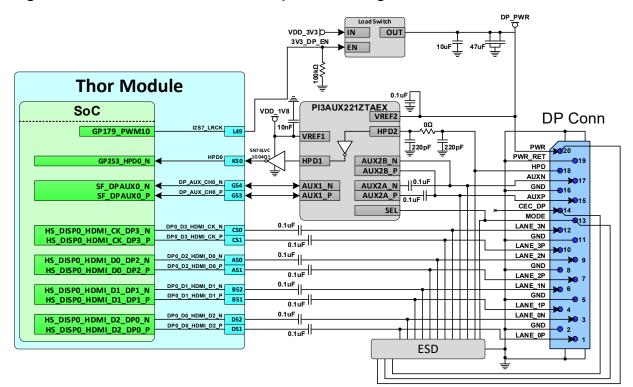

| Figure 9-2.  | DP Connection Example with Integrated PI3AUX221 Device        | 76  |

| Figure 9-3.  | DP Differential Main Link Topology                            | 78  |

| Figure 9-4.  | HDMI Connection Example                                       |     |

| Figure 9-5.  | HDMI CLK and Data Topology                                    | 84  |

| Figure 10-1. | Camera CSI D-PHY Connections                                  | 94  |

| Figure 10-2. | Camera CSI C-PHY Connections                                  | 95  |

| Figure 11-1. | Audio Device Connections                                      | 101 |

| Figure 12-1. | I2C Connections                                           | 106    |

|--------------|-----------------------------------------------------------|--------|

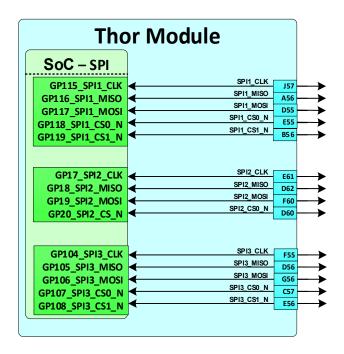

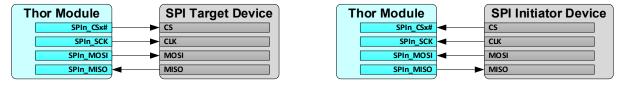

| Figure 13-1. | Jetson Thor SPI Connections                               | 110    |

| Figure 13-2. | Basic SPI Connections                                     | 110    |

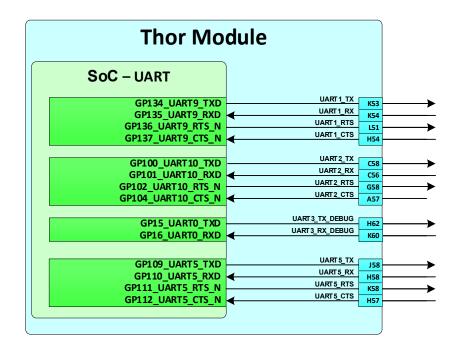

| Figure 13-3. | SPI Topologies                                            | 111    |

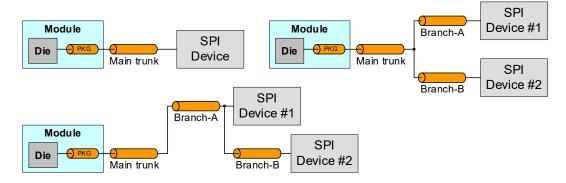

| Figure 14-1. | Jetson Thor UART Connections                              | 113    |

| Figure 15-1. | Jetson Thor CAN Connections                               | 116    |

| Figure 16-1. | Jetson Thor Fan Connection Example                        | 118    |

| Figure 17-1. | JTAG and UART Debug Connections                           | 120    |

| Figure 17-2. | Simple Debug UART Header Connections                      | 121    |

| Figure 18-1. | Jetson Thor Module Strap Pins                             | 125    |

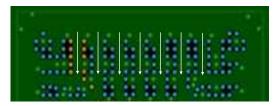

| Figure 21-1. | Via Placement for Good Power Distribution                 | 131    |

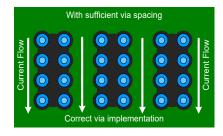

| Figure 21-2. | Good Current Flow Resulting from Correct Via Placement    | 131    |

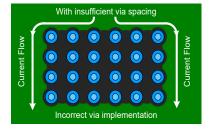

| Figure 21-3. | Poor Current Flow Resulting from Incorrect Via Placement  | 131    |

| Figure 24-1. | Typical Transmission Line Circuit                         | 136    |

| Figure 24-2. | Microstrip Transmission Line                              |        |

| Figure 24-3. | Stripline Transmission Line                               | 137    |

| Figure 24-4. | Transmission Line Height                                  | 139    |

| Figure 24-5. | Crosstalk on Reference Plane                              | 139    |

| Figure 24-6. | Power Plane Cuts Example                                  | 140    |

| Figure 24-7. | Power Plane Cuts Example when Decouple Capacitors are Abu | ındant |

|              |                                                           |        |

| Figure 24-8. | Switching Reference Planes                                |        |

| Figure 24-9. | Reference Plane Switch Using Via                          | 141    |

### List of Tables

| Table 1-1. Ab  | breviations and Definitions                                  | 2  |

|----------------|--------------------------------------------------------------|----|

| Table 1-2. Inc | lustry Standards                                             | 3  |

| Table 2-1. Jet | tson Thor Features                                           | 4  |

| Table 3-1. Sta | andoff Height Calculations for 5.5 mm Height Connector Case  | 8  |

| Table 3-2. Sta | andoff Height Calculations for 2.5 mm Height Connector Case  | 9  |

| Table 5-1. Po  | wer and System Pin Descriptions                              | 13 |

| Table 5-2. Po  | wer Button Supervisor Control Signals                        | 22 |

| Table 5-3. Po  | wer-OFF to On Timing Power Button Case                       | 24 |

| Table 5-4. Po  | wer-OFF to On Timing Auto Power-On Case                      | 26 |

| Table 5-5. Po  | wer-ON to OFF Timing Power Button Held Low > 10 Seconds      | 26 |

| Table 6-1. Sig | nal Type Codes                                               | 28 |

| Table 7-1. So  | C UPHYO Data Lane Pin Descriptions (USB 3.2 and PCle)        | 32 |

| Table 7-2. So  | C UPHY1 Data Lane Pin Descriptions (PCIe and MGBE (XFI))     | 33 |

| Table 7-3. UP  | HYO Mapping Options (USB and PCIe)                           | 34 |

| Table 7-4. UP  | HY1 Mapping Options (PCIe and MGBE (XFI))                    | 34 |

| Table 7-5. US  | B 2.0 Pin Descriptions                                       | 35 |

| Table 7-6. US  | B Control Pin Descriptions                                   | 35 |

| Table 7-7. US  | B 2.0 Signal Connections                                     | 38 |

| Table 7-8. US  | B 3.2 Signal Connections                                     | 38 |

| Table 7-9. US  | B 2.0 Interface Signal Routing Requirements                  | 39 |

| Table 7-10.    | USB 3.2 Interface Signal Routing Requirements                | 40 |

| Table 7-11.    | Recommended USB Observation Test Points for Initial Boards   | 44 |

| Table 7-12.    | PCIe Clock Pin Descriptions                                  | 45 |

| Table 7-13.    | PCIe Control Pin Descriptions                                | 45 |

| Table 7-14.    | PCIe Signal Connections Module I/Fs Configured as Root Ports | 48 |

| Table 7-15.    | PCIe Signal Connections Module I/F Configured as Endpoint    | 50 |

| Table 7-16.    | PCIe Signal Connections Jetson Thor RP to Jetson Thor EP     | 51 |

| Table 7-17.    | PCIe Interface Signal Routing Requirements up to Gen5        | 52 |

| Table 7-18.    | Recommended PCIe Observation Test Points for Initial Boards  | 56 |

| Table 7-19.    | Jetson Thor Module Gigabit Ethernet Pin Descriptions         | 57 |

| Table 7-20.    | Ethernet Signal Connections                                  | 59 |

| Table 7-21.    | MGBE Signal Connections                                      | 61 |

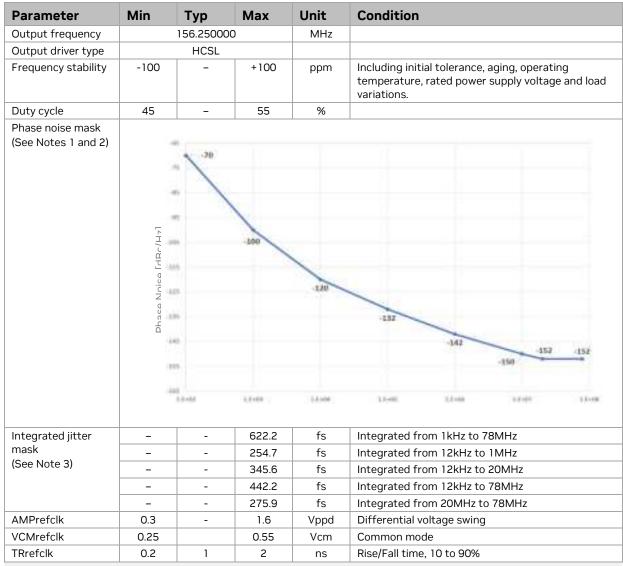

| Table 7-22.    | MGBE Interface Reference Clock Oscillator Requirements       | 61 |

| Table 7-23.    | MGBE 10GbE Interface Signal Routing Requirements             | 62 |

| Table 7-24.    | MGBE 25GbE Interface Signal Routing Requirements             | 67 |

| Table 7-25.    | MGBE Reference Clock Routing Requirements                    | 68 |

| Table 7-26.    | MGBE Interface Reference Clock Oscillator Requirements       | 69 |

| Table 9-1. Jet | tson Thor HDMI and DP Pin Description                        | 72 |

| Table 9-2. Ba | sic DP Signal Connections                            | 77  |

|---------------|------------------------------------------------------|-----|

| Table 9-3. DF | Signal Connections for Integrated PI3AUX221 Solution | 77  |

| Table 9-4. DF | P Main Link Signal Routing Requirements              | 78  |

| Table 9-5. Re | commended DP Test Points for Initial Boards          | 81  |

|               | DMI Signal Connections                               |     |

| Table 9-7. HD | OMI Interface Signal Routing Requirements            | 84  |

| Table 9-8. Re | commended HDMI and DP Test Points for Initial Boards | 88  |

| Table 10-1.   | Jetson Thor CSI Pin Description                      | 89  |

| Table 10-2.   | CSI Configurations for D-PHY                         |     |

| Table 10-3.   | CSI Configurations for C-PHY -x2 and x4              |     |

| Table 10-4.   | CSI Configurations C-PHY – x3 and x1                 | 93  |

| Table 10-5.   | MIPI CSI Signal Connections                          | 96  |

| Table 10-6.   | MIPI CSI D-PHY Interface Signal Routing Requirements | 97  |

| Table 10-7.   | MIPI CSI C-PHY Interface Signal Routing Requirements | 97  |

| Table 10-8.   | Recommended CSI Test Points for Initial Boards       | 98  |

| Table 10-9.   | Connector Specification                              | 99  |

| Table 11-1.   | Jetson Thor Audio Pin Description                    | 100 |

| Table 11-2.   | Audio Interface Signal Connections                   | 101 |

| Table 11-3.   | I2S Interface Signal Routing Requirements            | 102 |

| Table 11-4.   | DMIC Interface Signal Routing Requirements           | 103 |

| Table 12-1.   | Jetson Thor I2C Pin Description                      | 104 |

| Table 12-2.   | I2C Interface Mapping                                |     |

| Table 12-3.   | I2C Signal Connections                               |     |

| Table 12-4.   | I2C Interface Signal Routing Requirements            | 107 |

| Table 12-5.   | De-bounce Settings                                   | 108 |

| Table 13-1.   | Jetson Thor SPI Pin Description                      | 109 |

| Table 13-2.   | SPI Signal Connections                               | 110 |

| Table 13-3.   | SPI Interface Signal Routing Requirements            | 111 |

| Table 13-4.   | Recommended SPI Test Points for Initial Boards       | 111 |

| Table 14-1.   | Jetson Thor UART Pin Description                     | 112 |

| Table 14-2.   | UART Signal Connections                              | 113 |

| Table 14-3.   | UART Interface Signal Routing Requirements           | 113 |

| Table 15-1.   | Jetson Thor CAN Pin Descriptions                     | 115 |

| Table 15-2.   | CAN Signal Connections                               | 116 |

| Table 15-3.   | CAN Interface Signal Routing Requirements            | 117 |

| Table 16-1.   | Jetson Thor Fan Pin Descriptions                     | 118 |

| Table 16-2.   | Fan Signal Connections                               | 119 |

| Table 17-1.   | Thor Module JTAG Pin Description                     | 121 |

| Table 17-2.   | JTAG Signal Connections                              | 122 |

| Tahla 17-3    | Dehug HART Connections                               | 123 |

| Table 18-1. | Power-ON Strapping Breakdown    | 124 |

|-------------|---------------------------------|-----|

| Table 20-1. | Unused MPIO Pins and Pin Groups | 128 |

| Table 20-2. | Unused SFIO Pin Terminations    | 129 |

## **Chapter 1. Introduction**

This design guide contains recommendations and guidelines for engineers to follow and create a product that is optimized to achieve the best performance from the interfaces supported by the NVIDIA® Jetson™ Thor series module, hereafter referred to as "Thor Module."

This design guide provides detailed information on the capabilities of the hardware module, which may differ from supported configurations by provided software. Refer to the software release documentation for information on supported capabilities.

### References 1 1

Refer to the following documents or models listed for more information. Always use the latest revision of all documents.

- > Jetson Thor Series Data Sheet (DS-11945-001)

- Jetson Thor Developer Kit Carrier Board Specification (SP-12334-001)

- > Jetson Thor Series Pinmux Configuration Template

- > Jetson Thor Series Thermal Design Guide (TDG-12271-001)

- > Jetson Thor Developer Kit Carrier Board Reference Design Files

- Jetson Thor Series Supported Component List (DA-12429-001)

### **Attachments** 1.2

The following files are attached to this design guide.

- > Jetson\_Thor\_Series\_Pin\_Descriptions\_v1.0.nvxlsx

- Jetson\_Thor\_Series\_Schematic\_Checklist\_v1.0.nvxlsx

- Jetson\_Thor\_Series\_Layout\_Checklist\_v1.0.nvxlsx

- Jetson\_Thor\_Series\_Bringup\_Checklist\_v1.0.nvxlsx

To access the attached files, click the **Attachment** icon on the toolbar on this PDF (using Adobe Acrobat Reader or Adobe Acrobat). Select the file and use the Tool Bar options (Open, Save) to retrieve the documents.

Note that Excel files with the .nvxlsx extension will need to be saved as .xlsx.

### **Abbreviations and Definitions** 1.3

Table 1-1 lists abbreviations that may be used throughout this design guide and their definitions.

**Abbreviations and Definitions** Table 1-1.

| Abbreviation | Definition                                                  |

|--------------|-------------------------------------------------------------|

| CEC          | Consumer Electronic Control                                 |

| CAN          | Controller Area Network                                     |

| DP           | VESA® DisplayPort® (output)                                 |

| GPIO         | General Purpose Input Output                                |

| HDI          | High-Density Interconnect                                   |

| HDMI™        | High-Definition Multimedia Interface                        |

| I2C          | Inter IC                                                    |

| I2S          | Inter IC Sound Interface                                    |

| LDO          | Low Dropout (voltage regulator)                             |

| LPDDR5X      | Low Power Double Data Rate DRAM, Fifth generation, extended |

| MGBE         | Multi-Gigabit Ethernet                                      |

| MTS          | Multi-Stream Transport                                      |

| NVMe         | Non-Volatile Memory Express                                 |

| PCIe (PEX)   | Peripheral Component Interconnect Express Interface         |

| PDM          | Pulse-Density Modulation                                    |

| PHY          | Physical Layer                                              |

| PMIC         | Power Management Integrated Circuit                         |

| RTC          | Real Time Clock                                             |

| SC7          | System Core State 7 (Sleep)                                 |

| Abbreviation | Definition                                  |

|--------------|---------------------------------------------|

| SPI          | Serial Peripheral Interface                 |

| UART         | Universal Asynchronous Receiver-Transmitter |

| USB          | Universal Serial Bus                        |

#### **Industry Standards** Table 1-2.

| Interface   | Specification                                                       |

|-------------|---------------------------------------------------------------------|

| CAN         | Version 2.0/ISO11898                                                |

| DP          | Version 1.4a                                                        |

| ETHER_QOS   | RGMII Version 2.0                                                   |

| HDMI        | Version 2.1                                                         |

| I2C         | NXP 3.0                                                             |

| MGBE        | IEEE 802.3-2015                                                     |

| MIPI CSI    | C-PHY Revision 2.0 / D-PHY 2.1                                      |

| PCI Express | PCI Express Base Specification Revision 5.0, Version 1.0            |

| USB         | Universal Serial Bus Specification Revision 2.0, 3.2; Gen1 and Gen2 |

| XFI         | SFF INF-8077i, Revision 4.5, 2005                                   |

Note: All occurrences of USB 3.2 refer to "USB 3.2 Gen 1x1: SuperSpeed USB 5 Gbps" and "USB 3.2 Gen 2x1: SuperSpeed USB 10 Gbps" only. Also note that Gen 1x1 and Gen 2x1 are referred to simply as Gen1 and Gen2 in this design guide.

# **Chapter 2. Introduction**

The NVIDIA Jetson Thor series modules reside at the center of the embedded system solution and Jetson Thor SoC:

- > Power (Power Sequencer, Regulators)

- > DRAM (LPDDR5X)

- > QSPI NOR

- > Power Monitors

- > Thermal Sensor

Table 2-1. **Jetson Thor Features**

| Category      | Function                                       | Category | Function                                                                                         |

|---------------|------------------------------------------------|----------|--------------------------------------------------------------------------------------------------|

| USB           | USB 2.0<br>USB 3.2 Gen2x1 (10 Gbps)            | Display  | HDMI / DP (4x- see note). DP supports multi-head operation through Multi-Stream Transport (MST). |

| PCIe          | Root Port and Endpoint supported up to Gen5    | SPI      | Initiator and Target                                                                             |

| Camera        | CSI (6x2 or 4x4) D-PHY and C-<br>PHY           | Fan      | PWM and TACH                                                                                     |

| LAN           | 5 Gigabit Ethernet: PCle<br>MGBE Ethernet: XFI | Debug    | JTAG and UART                                                                                    |

| Audio         | I2S, Digital Mic                               | System   | Power control, Reset, Alerts                                                                     |

| Miscellaneous | CAN, I2C, UART                                 | Power    | Main Inputs (HV, MV, and SV)                                                                     |

Note: HDMI and DP share the same pins. See Chapter 9 for display details.

# **Chapter 3. Main Connector Details**

The main 699-pin connector on the Jetson Thor is from the Molex Mirror Mezz family. See the Jetson Thor Series Supported Components List (DA-12429-001) for compatible module connectors to use on the carrier board. Refer to the Molex Mirror Mezz connector specification for details.

Refer to the Jetson\_Thor\_Series\_Pin\_Descriptions in the attachment for the 699-pin map.

Figure 3-1. 699-pin Connector Dimensions

囯

Note: Various documents related to the Molex Mirror Mezz connector can be found at: Mirror Mezz Connectors - Molex

The *Molex Application Guide* for Mirror Mezz<sup>™</sup>, which includes details for connector mounting can be found at: <a href="https://www.molex.com/pdm\_docs/as/2028280001-AS-">https://www.molex.com/pdm\_docs/as/2028280001-AS-</a> 000.pdf

### 3.1 **Connector Pin Orientations**

The symbol pinout for the 699-pin connector on the carrier board is mirrored such that the pin numbers match when the module and carrier board connectors are mated (see Figure 3-2). The orientation shown matches the carrier board in the upright position as well as the layout file.

Caution: Note that the 699-pin connector pinout on the carrier board is a mirror image of the Molex pinout. Designers should verify the pinout of their designs against the Jetson Thor reference layout.

Figure 3-2. 699-pin Connector Pin Orientation

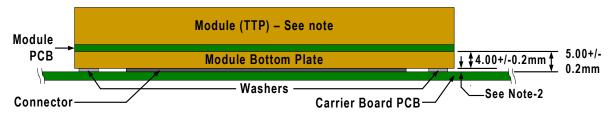

### Module to Carrier Board Standoff 3.2

The spacing between the module PCB and the carrier board PCB are shown in Figure 3-3 and Figure 3-4 to illustrate the following two cases:

- > 5.5 mm connector on the carrier board (8 mm nominal spacing).

- 2.5 mm connector (5 mm nominal spacing).

The standoffs to support the module are located between the carrier board and the bottom plate.

Figure 3-3. 5.5 mm Height on Carrier Board

Figure 3-4. 2.5 mm Height on Carrier Board

### Notes:

- 1. See Section 3.3 for standoff heights recommendations.

- 2. If the 2.5 mm height connector is used, there can be no components under the module on the carrier board due to the extremely limited clearance.

### Module to Carrier Board Standoff 3.3 Height Recommendations

Standoffs and spacers are required between the module bottom plate and the carrier board. The height should be chosen to meet the connector board-to-board spacing requirements and accommodate the tolerances in the bottom plate and the standoff itself. If the standoff is too short, the carrier board PCB may warp as the mounting screws are tightened. If too tall, the connectors will not mate fully. The two cases (5.5 mm and 2.5 mm connector on the carrier board) are described in this section and are accompanied by tables that show the possible permutations of tolerances of the bottom plate and spacers. The platform designer can determine if a different height would be more appropriate but should consider both the PCB warpage (standoff height too short) and connector contact overlap length to find the best balance.

The following examples are based on Molex parts using spacer heights and spacer tolerances to produce a workable solution.

### 5.5 mm height – 8.00+/-0.15 mm board to board spacing case

For this case, a standoff height of 4.2 mm is used. This is based on a standoff with ±0.13 mm height tolerance. The tolerance for the bottom plate is ±0.1 mm and ±0.1 mm for the solder balls between the bottom plate and the module PCB. The following table shows example calculations using the connector board spacing, module bottom plate height, and example standoff height with tolerances mentioned.

| Table 3-1. Standoff | Height Ca | iculations t | or 5.5 mm Hei | ght Connector Case |

|---------------------|-----------|--------------|---------------|--------------------|

|---------------------|-----------|--------------|---------------|--------------------|

| Board to Board<br>Spacing (mm) | Bottom Plate<br>Height (mm)    | Board to Bottom<br>Plate Gap (mm) | Standoff<br>Height (mm) | Space Beyond Ideal<br>Mating Spec. (mm) |

|--------------------------------|--------------------------------|-----------------------------------|-------------------------|-----------------------------------------|

| 8                              | 3.8                            | 4.2                               | 4.07                    | -0.13                                   |

| 8                              | 3.8                            | 4.2                               | 4.33                    | 0.13                                    |

| 8                              | 4.2                            | 3.8                               | 4.07                    | 0.27                                    |

| 8                              | 4.2                            | 3.8                               | 4.33                    | 0.53                                    |

| Margin to -0.15 mm             | Margin to -0.15 mm Conn. Spec. |                                   |                         | 0.02                                    |

| Nominal connector sweep range  |                                |                                   | 1.5                     |                                         |

| Worst case remainir            | ng sweep/contact (mr           | n)                                |                         | 0.97                                    |

#### Notes:

- 1. Positive values mean no PCB warpage but less sweep. Negative values can result in PCB warpage.

- 2. The mating connector height tolerance comes from the Molex connector specification.

- 3. The connector contact sweep range can be found on the Molex website in the Mirror Mezz area.

- 4. The module bottom plate height/tolerance can be found in the Jetson Thor Data Sheet.

### 2.5 mm height - 5.00+/-0.15 mm board to board spacing case

For this case, a standoff height of 1.2 mm is used. This is based on a standoff with ±0.13 mm height tolerance. The tolerance for the bottom plate is ±0.1 mm and ±0.1 mm for the solder balls between the bottom plate and the module PCB. The following table shows example calculations using the connector board spacing, module bottom plate height, and example standoff height with tolerances mentioned.

Table 3-2. Standoff Height Calculations for 2.5 mm Height Connector Case

| Board to Board<br>Spacing (mm) | Bottom Plate<br>Height (mm)   | Board to Bottom<br>Plate Gap (mm) | Standoff Height (mm) | Space Beyond<br>Ideal Mating<br>Spec. (mm) |  |

|--------------------------------|-------------------------------|-----------------------------------|----------------------|--------------------------------------------|--|

| 5                              | 3.8                           | 1.2                               | 1.07                 | -0.13                                      |  |

| 5                              | 3.8                           | 1.2                               | 1.33                 | 0.13                                       |  |

| 5                              | 4.2                           | 0.8                               | 1.07                 | 0.27                                       |  |

| 5                              | 4.2                           | 0.8                               | 1.33                 | 0.53                                       |  |

| Margin to -0.15mm (            | Margin to -0.15mm Conn. Spec. |                                   |                      |                                            |  |

| Nominal connector s            | 1.5                           |                                   |                      |                                            |  |

| Worst case remainin            | g sweep/contact (mm)          |                                   |                      | 0.97                                       |  |

### Notes:

- 1. Positive values mean no PCB warpage but less sweep. Negative values can result in PCB warpage.

- 2. See additional notes in the "Notes" section of Table 3-1.

### Module Installation and Removal 34

To install the Jetson Thor correctly, follow the sequence and mounting hardware instructions below:

- 1. Connectors should be parallel with respect to each other during mating.

- 2. Use a smooth motion during mating (no mechanical shock, knocking, hammering).

- 3. The top and bottom PCB are to be bolted to enhance reliability.

- 4. Secure with M3 screws (4x) from the top of the module. Torque the screws to 4.5 inlbf.

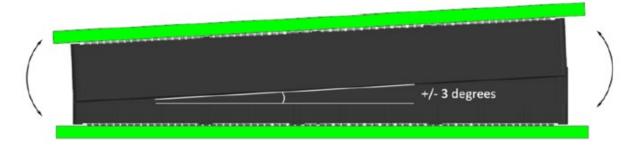

If a fixture is used to do the mating, then that fixture should hold the mating connectors parallel to within ± 2 degrees. Also, the fixture should allow the connectors to become parallel as the mating process progresses.

To remove the Jetson Thor correctly, follow the sequence and mounting hardware instructions below:

- 1. The PCB design needs to have enough finger reachability and space required to hold the board for un-mating.

- 2. Remove mounting screws (4x) from the top of the module.

- 3. Rock the top board a few times, no more than ± 3 degrees, to gradually disengage the connectors.

**Module Removal** Figure 3-5.

# Chapter 4. Reference Design **Considerations**

The Jetson Thor Developer Kit Carrier Board Reference design files are provided as a reference design. This chapter provides the necessary details for designers to replicate certain features if desired. In addition, aspects of the design that are specific to the NVIDIA developer kit usage, but not useful or supported on a custom carrier board, are identified.

Most of the features implemented on the Jetson Thor Developer Kit can be duplicated by copying the connections from the Jetson Thor Carrier Board Reference Design Files. These listed features have aspects that would require additional information.

- Button Power MCU: The developer kit carrier board implements a button power MCU (EFM8SB10F2G - U79). This device is programmed with firmware that is available on the Jetson Download Center. The posting is titled NVIDIA Jetson Carrier Board Power Button Supervisor Firmware. The connections used on the reference design must be followed exactly and the firmware provided must be used to ensure correct functionality.

- > USB Type-C<sup>®</sup> (USB-C<sup>®</sup>) PD Controller: Designs that intend to follow the NVIDIA carrier board design and include the USB-C PD Controller (CYPD8225 - U237) must replicate the circuitry on the latest carrier board exactly. The firmware binary is used to program the Cypress CYPD8225 controller and is available on the Jetson Download Center. The posting is titled Cypress Firmware Binary for USB Type-C PD controller (CYPD8225). The customer should get the flashing instructions from Cypress. No support or source code is provided for this firmware. If modifications or source code is required, contact Cypress directly for support. This firmware binary is released under the L4T firmware EULA.

- > Power Monitoring: There is a power monitoring IC (INA238 U280) that monitors the input power to trigger throttling when the power consumption exceeds the power supply capacity.

The following list is the Jetson Thor Developer Kit carrier board features that should not be copied as they are not required or useful for a custom carrier board design. They will not be supported by NVIDIA.

- > The ID EEPROM (AT24C02D U501) is a feature that is used for NVIDIA internal purposes, but not useful on a custom design. A similar function may be desired for a custom design, but the NVIDIA software will not interact with these devices and the I2C address used by the developer kit carrier board ID EEPROM on the I2C1 interface (7'h56) should be avoided.

- > Debug MCU (ATSAMD21G16B-AU U136), circuit, and associated USB connector (J90): These features are used at NVIDIA for internal debugging and development purposes. These are not required, and support will not be provided if implemented. Designers have the option to implement something similar on their custom carrier boards but should develop their own circuit to meet their needs.

# **Chapter 5. Power**

This chapter describes the power specifications for the Jetson Thor.

Caution: The Jetson Thor module is not hot-pluggable. Before installing or removing the module, the main power supplies (SYS\_VIN\_SV , SYS\_VIN\_HV and SYS\_VIN\_MV) must be disconnected and the power rails allowed to discharge to <0.6V.

**Power and System Pin Descriptions** Table 5-1.

| Pin#        | Module Pin Name | Usage/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Direction | Pin Type                   |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------|

| See<br>note | SYS_VIN_HV      | System Voltage Input – High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input     | Power:<br>7V to 20V        |

| below       | SYS_VIN_MV      | System Voltage Input - Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input     | Power:<br>5.0V             |

| L53         | SYS_VIN_SV      | Safety Logics Voltage Input: Must be tied to 3.3V. See power sequencing for timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input     | Power: 3.3V                |

| D37         | PMIC_BBATT      | Real-Time Clock: Optionally used to provide back-<br>up power for RTC in the Power Sequencer.<br>Connects to Lithium Cell or similar power source,<br>which provides power to RTC when the system is<br>disconnected from power. Rechargeable cells or<br>super capacitors are not supported.                                                                                                                                                                                                                                                         | Input     | Power:<br>1.85V to<br>5.5V |

| L60         | SYS_RESET_N     | System Reset: Asserted by power sequencer in the module during power-on. Can be asserted by the carrier board to reset the SoC, Boot devices, etc., but not the power sequencer.  A $10k\Omega$ pull-up to $1.8V$ is on the module.                                                                                                                                                                                                                                                                                                                   | Bidir     | Open Drain,<br>1.8V        |

| L55         | VDDIN_PWR_BAD_N | VDD_IN Power Bad: Carrier board asserts low when SYS_VIN_HV and SYS_VIN_MV are not valid. Carrier board should stop asserting this signal and allow the signal to be pulled high by the internal pull-up on the module when SYS_VIN_HV and SYS_VIN_MV are stable and have reached required voltage levels. This prevents the SoC from powering up until the main input supply voltages are stable. It also can be driven by module if critical condition makes this necessary such as thermal shutdown. A $10k\Omega$ pull-up to 5V is on the module. | Bidir     | Open-drain,<br>5.0V        |

| Pin# | Module Pin Name        | Usage/Description                                                                                                                                                                                                                                                                                            | Direction        | Pin Type            |

|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|

| L54  | MODULE_<br>POWER_ON    | <b>Module Power On</b> : Signal asserted to the module to start power-on sequence. This signal should be driven low by the carrier board initially and then driven high when the module is to be powered on.                                                                                                 | Input            | CMOS, 5.0V          |

| L62  | CARRIER_<br>POWER_ON   | Carrier Power On: Asserted by the module when module power up sequence is complete. This signal high indicates that it is safe for the carrier board to power up.  A $10k\Omega$ pull-up to $3.3V$ is on module.                                                                                             | Output           | Open-drain,<br>3.3V |

| L61  | POWER_BTN_N            | Power Button: Can be configured by software to be used to power system off or enter and exit sleep mode (SC7). Level shifter between module pin (3.3V) and SoC pin (1.8V) on module.                                                                                                                         | Bidir            | Open-drain,<br>3.3V |

| L58  | PERIPHERAL_<br>RESET_N | Peripheral Reset: Driven from carrier board and AND'd with SYS_RESET_N to drive the Thor SF_SYS_RST_N pin. When PERIPHERAL_RESET_N is asserted, the SoC and QSPI are reset (not Power Sequencer).                                                                                                            | Input            | CMOS -<br>1.8V      |

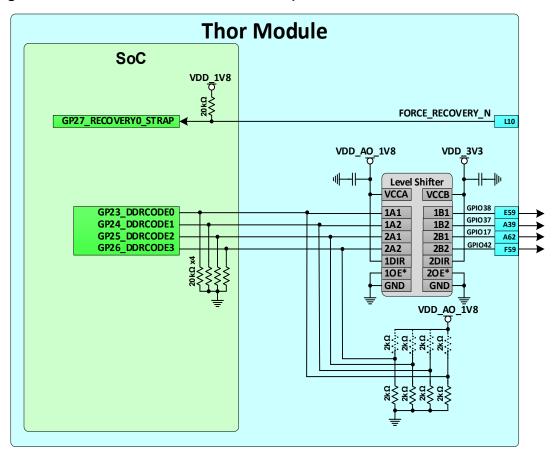

| L10  | FORCE_<br>RECOVERY_N   | A 10kΩ pull-up to 1.8V is on the module.  Force Recovery strap pin: Held low when SYS_RESET_N goes inactive (power-on or reset button press) to enter force recovery mode.                                                                                                                                   | Input            | CMOS -<br>1.8V      |

| J60  | MODULE_SLEEP_N         | Sleep Acknowledge: Indicates module is in sleep mode (SC7 state).                                                                                                                                                                                                                                            | Output           | CMOS -<br>1.8V      |

| L56  | THERM_ALERT_N          | Thermal Alert: Thermal alert assertion. System needs to actively cool down the module once the signal is asserted low.                                                                                                                                                                                       | Output           | Open-drain,<br>3.3V |

| A61  | SYSTEM_OC_N            | System Over-current Thermal warning: Optionally, the signal can be asserted by external events (e.g., low battery) to trigger hardware clock throttling.                                                                                                                                                     | Input            | CMOS, 1.8V          |

| L52  | MODULE_SHDN_N          | Module Shutdown indicator: Used to inform carrier board that a shutdown request has occurred onmodule (thermal shutdown).  A $10k\Omega$ pull-up to $1.8V$ is on the module.                                                                                                                                 | Output           | CMOS –<br>1.8V      |

| A3   | PRSNTO                 | Present 0: Tied with PRSNT1 on module. Used to detect when the module is connected to the carrier board. Can be used to keep the carrier board from powering the module until the module is installed fully in the carrier board. Tied to GND on the carrier board if implemented to match reference design. | N/A              | N/A                 |

| L63  | PRSNT1                 | Present 1: Tied to one side of the power button on the carrier board. Refer to the Jetson Thor Carrier Board Reference Design files for the detailed connection.                                                                                                                                             |                  |                     |

| K40  | MID0                   | Module ID #0                                                                                                                                                                                                                                                                                                 | Not<br>connected | N/A                 |

| Pin#                                                                     | Module Pin Name | Usage/Description | Direction   | Pin Type |  |

|--------------------------------------------------------------------------|-----------------|-------------------|-------------|----------|--|

| H40                                                                      | MID1            | Module ID #1      | Tied to GND | N/A      |  |

| Note: Refer to the Jetson Thor Series Pin Descriptions in the attachment |                 |                   |             |          |  |

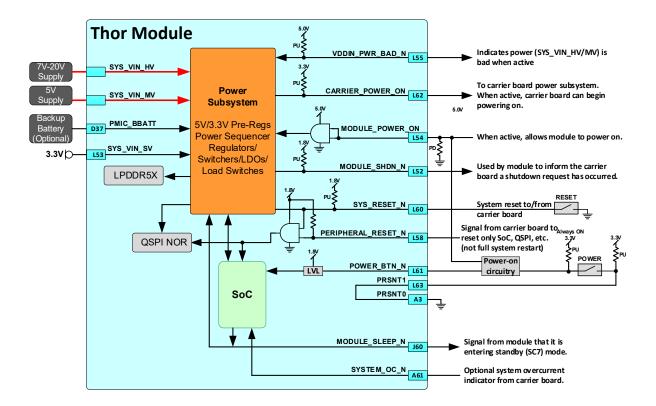

Figure 5-1. **Power Block Diagram**

### 5.1 Power Sequencing

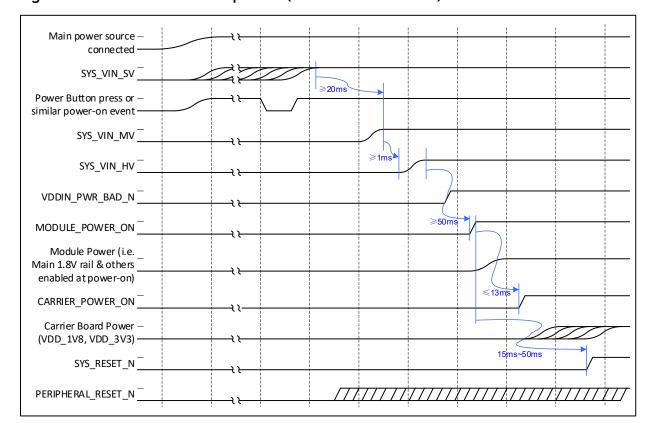

### Power-On Sequence 5.1.1

The basic power-ON sequencing requirements is as follows:

- > The main power source for the system is applied. The SYS\_VIN\_SV, SYS\_VIN\_HV, and SYS\_VIN\_MV are derived from this power source. SYS\_VIN\_SV must be powered up first or it may have remained powered from the previous power cycle. Optionally, SYS\_VIN\_SV, SYS\_VIN\_HV, and SYS\_VIN\_MV supplies can be gated and only enabled to the module when a signal (such as VIN\_PWR\_ON) is enabled. This can help avoid damage if the module is inserted when main power is on.

- > VDDIN\_PWR\_BAD\_N will stay active (low) until SYS\_VIN\_HV is valid (and not gated).

- > MODULE\_POWER\_ON can be set active (high) once VDDIN\_PWR\_BAD\_N is inactive (hiah).

- > As the module powers on, one of the last supplies is the 3.3V supply always-on supply. **CARRIER\_POWER\_ON** is pulled up to the powergood pin of the 3.3V supply. Once this signal is active (high), the carrier board supplies associated with the module (1.8V, 3.3V) can power on.

- > SYS\_RESET\_N is driven by the power sequencer on the module during power-on. It does not need to be controlled by the carrier board. If the carrier board supplies required for powering on require additional time, the **PERIPHERAL\_RESET\_N** signal can be held low. This will keep the SoC and other boot devices in reset.

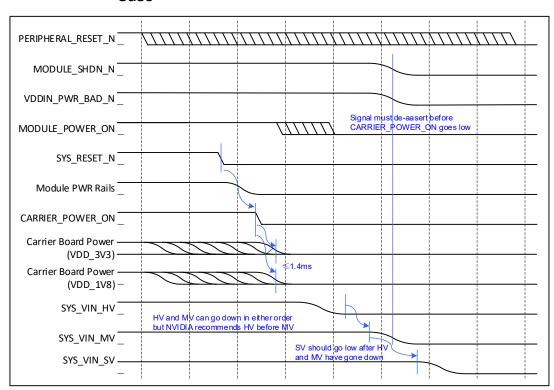

Figure 5-2. Power-On Sequence (Power Button Case)

### Notes:

- 1. PERIPHERAL\_RESET\_N is optionally kept High during the power-up sequence. If Carrier Board Power is not up yet by the time SYS\_RESET\_N is de-asserted, PERIPHERAL\_RESET\_N must be held Low until the carrier board is ready to bring Thor out of RESET.

- 2. MODULE\_POWER\_ON must be driven low by the carrier board initially before driving it high to power on the module during the power-on sequence.

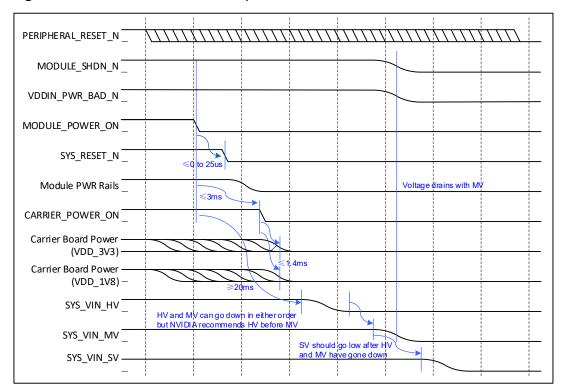

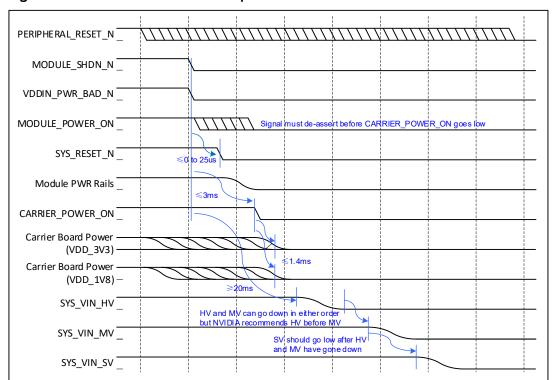

### 5.1.2 Power Down Sequence by Power Button Press

- 1. MODULE\_SHDN\_N and VDDIN\_PWR\_BAD\_N do not play a role in this power down sequence; they drain with the MV rail going down at the end.

- 2. User presses a button that causes MODULE\_POWER\_ON to go low. If a button MCU is being used, the user holds the Power Button for X-amount of time (see the 5.3.2 Power Button Supervisor MCU section).

- 3. The power sequencer on the module starts the power down sequence from the moment MODULE\_POWER\_ON goes low.

Figure 5-3. Power Down Sequence - Button Press Shutdown Case

### Notes:

- 1. Once CARRIER\_POWER\_ON is de-asserted by the module, backdrive into Thor I/O from the carrier board must be eliminated by this point.

- 2. VDD\_3V3 and VDD\_1V8 on the carrier board should be discharged earlier than the module power. Refer to section 5.4 Power Discharge for discharging.

- 3. SYS\_VIN\_MV must go below 100 mV before the system can be powered on again. Any undefined low voltage is considered as OV.

### Power Down Sequence by Software 5.1.3 Shutdown

- 1. MODULE\_SHDN\_N and VDDIN\_PWR\_BAD\_N do not play a role in this power down sequence.

- 2. SYS\_RESET\_N is the first signal to assert low.

- 3. MODULE\_POWER\_ON signal should go low after CARRIER\_POWER\_ON goes low. With the button MCU solution used on the reference design, MODULE POWER ON will go low after a propagation delay/MCU response time as VDDIN\_PWR\_BAD\_N notifies the Button MCU to go to shutdown state.

- 4. The power sequence on the module starts power sequence from the moment MODULE\_SHDN\_N goes low.

Power Down Sequence - User Initiated - Software Shutdown Figure 5-4.

### **Notes** (see Figure 5-4):

- 1. Once CARRIER\_POWER\_ON is de-asserted by the module, backdrive into Thor I/O from the carrier board must be eliminated by this point.

- 2. VDD\_3V3 and VDD\_1V8 on the carrier board should be discharged earlier than the module power. Refer to 5.4 Power Discharge for discharging.

- 3. SYS\_VIN\_MV must go below 100 mV before the system can be powered on again. Any undefined low voltage is considered as OV.

#### 5.1.4 Power Down Sequence by an Event

MODULE\_SHDN\_N and VDDIN\_PWR\_BAD\_N signals are essentially all tied together.

- > MODULE\_SHDN\_N is a signal to the carrier board indicating the module is shutting down, primarily due to a thermal event.

- VDDIN\_PWR\_BAD\_N is a signal from the carrier board. If the monitored voltage drops below a threshold, this signal is pulled low, initiating a shutdown. It should connect to a circuit on the carrier board that also pulls MODULE\_POWER\_ON low, ensuring both the module and carrier board recognize the shutdown state). This is implemented in the Power Button MCU circuit in the reference design.

Figure 5-5. Power Down Sequence - Shutdown Due to an Event Case

### **Notes** (see Figure 5-4):

- 1. Once CARRIER\_POWER\_ON is de-asserted by the module, backdrive into Thor I/O from the carrier board must be eliminated by this point.

- 2. VDD\_3V3 and VDD\_1V8 on the carrier board should be discharged earlier than the module power. Refer to section 5.4 Power Discharge for discharging.

- 3. SYS\_VIN\_MV must go below 100 mV before the system can be powered on again. Any undefined low voltage is considered as OV.

- 4. If the main power rails (SYS\_VIN\_HV/MV) are not powered off, it is possible for the system to power on again depending on the state of the signals. If the system was powered down due to a shutdown condition that is cleared, the system may power back on. Unless this is desired, a means of keeping the module powered off should be provided. One way is to latch the state of CARRIER\_POWER\_ON when it goes from high to low (module powered off) and using this to keep MODULE\_POWER\_ON inactive (low).

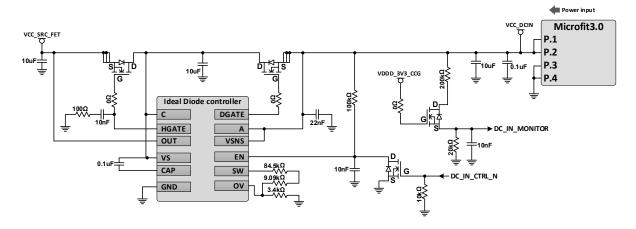

### 5.2 SYS\_VIN\_HV Input

The Jetson Thor Developer Kit carrier board allows the main system power to be supplied either by one of the USB Type-C connectors or a Microfit connector. The details for implementing USB-C for power can be found in the Jetson Thor Carrier Board Reference Design Files. If a design only requires a simple Microfit connector, the circuit in Figure 5-5 can be used.

Note: Designs that intend to follow the NVIDIA carrier board design and include the USB-C PD Controller (CYPD8225 - U237) must replicate the circuitry on the latest Jetson Thor Carrier Board exactly. NVIDIA will provide the binary and the customer should get the flashing instructions from Cypress. Make sure the system gets more than 45W during flashing.

The example shown in Figure 5-5 shows the main system power being supplied to the carrier board by a Microfit connector. This circuit is a simplified example based on the carrier board reference design.

Figure 5-6. **Simplified Microfit Connector Connections**

Note: Designs with a single MOSFET should select a part that DOES NOT limit reverse current.

### 5.3 Power-On

This section provides examples for powering on the Jetson Thor.

- > Auto Power-ON requirements

- Power button supervisor MCU circuit

#### 5.3.1 Auto Power-on

If the system does not require a power button or equivalent, and should power on when the main power source is connected, the following requirements should be met:

- > SYS\_VIN\_SV, SYS\_VIN\_HV, and SYS\_VIN\_MV should be powered on. SYS\_VIN\_SV must be powered up first or it may have remained powered from the previous power cycle. These can be optionally gated and a signal used to enable them when the module is detected mounted correctly using PRSNT[1:0].

- > VDDIN\_PWR\_BAD\_N should be de-asserted (high) once the SYS\_VIN\_HV and **SYS\_VIN\_MV** supplies are enabled and stable.

- > MODULE\_POWER\_ON should be asserted (high)

Note: The design should de-assert (low) MODULE\_POWER\_ON if VDDIN\_PWR\_BAD\_N is asserted (low), CARRIER\_POWER\_ON is de-asserted (low), or MODULE\_SHDN\_N is asserted (low).

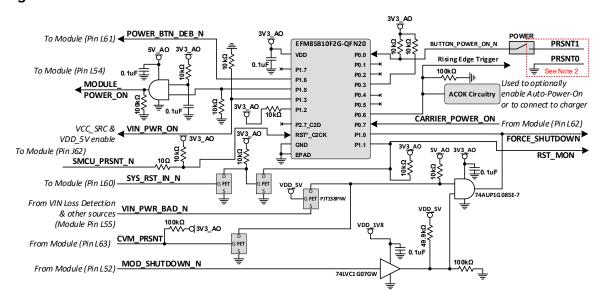

#### 5.3.2 Power Button Supervisor MCU Circuit

The Jetson Thor Developer Kit carrier board implements a power button supervisor (or Button MCU for short). This supervisor is a low power device meant to intercept pushbutton (momentary) switches to control ON or Enable signals to the module Power Sequencer and main processor. This supervisor is always powered and allows close to complete system Power-OFF while providing proper timing for ON and OFF signals to the system. The selected Button MCU to perform this function is the EFM8SB10F2G-QFN20 from Silicon Labs.

Note: Designs that intend to follow the NVIDIA carrier board design and include the EFM8SB10F2G-QFN20 MPU for Button Power Button control need to replicate the circuitry on the latest Jetson Thor Carrier Board. NVIDIA will provide the binary and the customer should get the flashing instructions from Silicon Labs.

Table 5-2. **Power Button Supervisor Control Signals**

| Signal Name           | Associated<br>Module Pin # | I/O Type             | Trigger<br>Level | Drive<br>Mode | Description                      | MCU<br>Pin |

|-----------------------|----------------------------|----------------------|------------------|---------------|----------------------------------|------------|

| BUTTON_POWER_<br>ON_N |                            | Input<br>(debounced) | Level            | OD<br>(HiZ)   | Power Button                     | P0.0       |

| EFM8_ACOK             |                            | Input<br>(debounced) | Edge             | OD<br>(HiZ)   | Determine when power is supplied | P0.6       |

| CARRIER_POWER_<br>ON  | L62                        | Input                | Level            | OD<br>(HiZ)   | Closed loop on power output      | P0.7       |

| SYS_RESET_N           | L60                        | Input                | Edge             | OD<br>(HiZ)   | Monitor / Power Good mask        | P1.1       |

| Signal Name         | Associated<br>Module Pin # | I/O Type | Trigger<br>Level | Drive<br>Mode | Description                            | MCU<br>Pin |

|---------------------|----------------------------|----------|------------------|---------------|----------------------------------------|------------|

| MODULE_SHDN_N       | L52                        | Input    | Level            | OD<br>(HiZ)   | Triggers shutdown sequence             | P1.0       |

| BRD_SEL             |                            | Input    |                  | OD<br>(HiZ)   | Strap pin for board selection          | P1.2       |

| VIN_PWR_ON          |                            | Output   |                  | PP            | Enable power to module                 | P1.3       |

| MODULE_POWER_<br>ON | L54                        | Output   |                  | PP            | Enable input to PMIC                   | P1.5       |

| POWER_BTN_DEB_<br>N | L61                        | Output   |                  | OD            | Buffered output of power button signal | P1.6       |

Note: OD = Open-drain. PP = Push-pull.

Figure 5-7. Power-On Button Circuit

### 囯

### Notes:

- 1. Refer to the carrier board reference design for the latest connection details including different sources for ACOK.

- 2. Optional use of Present pins on module to ensure the power button will only initiate power-on if the module is mounted correctly. The PRSNT[1:0] pins are on opposing corners of the module connector.

#### 5.3.2.1 **Defined Behaviors**

For all actions triggered by BUTTON\_POWER\_ON\* or ACOK, there will be a de-bounce time before triggering any output signal. The minimum I/O delay for these signals is therefore the de-bounce time. De-bounce time is 20 ms. If both signals are triggered within the 20 ms de-bounce time started by the first detected signal, then the de-bounce time for the subsequent signals might extend up to 25 ms.

Figure 5-8.

Note: The time values in the following timing diagrams have an accuracy of ± 10%.

#### Power-OFF -> Power-ON (Power Button Case) 5.3.2.2

Power button press use case: User presses the power button briefly, and the Button MCU sends the power enable signals to the module (VIN\_PWR\_ON) and to the Power Sequencer on the module (MODULE\_POWER\_ON). The signal representing the power button to the Jetson Thor (POWER\_BTN\_N), will have the same (brief) duration of the power button input to the Button MCU. Once the power button is pressed, the power OK input (ACOK) is ignored, as the power-ON sequence is already initiated by the power button.

If power-ON is successful, FORCE\_SHUTDOWN\_N goes high as well as CARRIER\_POWER\_ON.

Table 5-3. Power-OFF to On Timing Power Button Case

| Timing    | Parameter                                 | Min | Typical | Units |

|-----------|-------------------------------------------|-----|---------|-------|

| T_ON      | BUTTON_POWER_ON*                          | 20  |         | ms    |

| T_PB_OUT  | Delay from BUTTON_POWER_ON to POWER_BTN_N |     | 20      | ms    |

| T_VPWR_ON | Delay to first rail ON                    |     | 0       | ms    |

| Timing | Parameter                                                                                                 | Min | Typical | Units |

|--------|-----------------------------------------------------------------------------------------------------------|-----|---------|-------|

| T_SV   | Time delay required after SYS_VIN_SV is up and stable before SYS_VIN_MV and SYS_VIN_HV begin to power up. | 20  |         | ms    |

| T_MPO  | MODULE_POWER_ON (module PMIC enable) delay from power VIN_PWR_ON rising edge                              |     | 80      | ms    |

| T_CPO  | Maximum allocated delay to CARRIER_POWER_ON assertion                                                     |     | 100     | ms    |

#### Power-OFF -> Power-ON (Auto-Power-On Case) 5.3.2.3

When the user connects the main power source, the Button MCU sends the power enable signals to the module (VIN\_PWR\_ON) and enables MODULE\_POWER\_ON. This is accomplished by having the ACOK signal driven high instead of pulled to GND.

The signal representing the power button to the Jetson Thor (POWER\_BTN\_N) will continue following the power button (BUTTON\_POWER\_ON\*) behavior. However, once the power-ON sequence is initiated by the connection of the main power source, and ACOK is driven high (by push-pull driver powered from 3V3\_AO), the power button signals will not affect the Button MCU behavior until the PWR\_GOOD signal verification is complete.

Figure 5-9. Power-OFF to On Sequence Auto Power-On Case

Table 5-4. Power-OFF to On Timing Auto Power-On Case

| Timing       | Parameter                                                                                                | Typical  | Units |

|--------------|----------------------------------------------------------------------------------------------------------|----------|-------|

| T_VPWR_ON_AC | Delay from ACOK detected high with main power source applied to first rail ON (de-bounce only)           | 20       | ms    |

| T_SV         | Time delay required after SYS_VIN_SV is up and stable before SYS_VIN_HV and SYS_VIN_MV begin to power up | 20 (min) | ms    |

| T_MPO_AC     | MODULE_POWER_ON active delay from VIN_PWR_ON rising edge                                                 | 80       | ms    |

| T_CPO_AC     | Maximum allocated delay to CARRIER_POWER_ON active                                                       | 100      | ms    |

# Power-ON -> Power-OFF (Power Button Held Low > 10 5.3.2.4 Seconds)

With the system in power-ON state, the user holds the power button for more than 10 seconds. The same button signal is relayed to the Jetson Thor through the buffered signal POWER\_BTN\_N. The system is forced to shut down at the 10 second mark. ACOK is ignored as the sequence is initiated by the power button.

Figure 5-10. Power-ON to OFF Power Button Held Low > 10 Seconds

Table 5-5. Power-ON to OFF Timing Power Button Held Low > 10 Seconds

| Timing      | Parameter                                                                              | Typical | Units |

|-------------|----------------------------------------------------------------------------------------|---------|-------|

| T_ON        | Power button active duration for forced OFF (T_PWR_ON + T_MPO_ON + T_CPO + T_MPO_OFF1) | > 10    | S     |

| T_VPWR_ON   | Delay to first rail ON (de-bounce only)                                                | 20      | ms    |

| T_MPO_OFF1  | Wait time to force MODULE_POWER_ON OFF                                                 | 10      | S     |

| T_MPO       | Enable delay from VIN_PWR_ON rising edge                                               | 80      | ms    |

| T_CPO       | Maximum allocated delay to detect CARRIER_POWER_ON                                     | 100     | ms    |

| T_VPWR_OFF1 | Delay to first rail OFF                                                                | 10      | ms    |

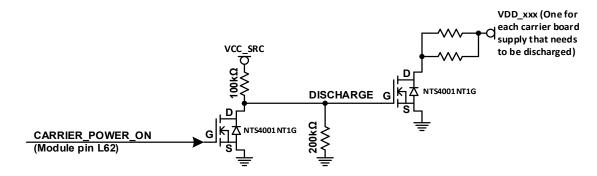

### 54 Power Discharge

To meet the power down requirements, discharge circuitry may be required. Figure 5-10 shows an example of a simplified discharge circuit. The **DISCHARGE** signal is generated, based on a transition of the CARRIER\_POWER\_ON signal or the removal of the main supply (VDD\_SRC). When DISCHARGE is asserted, the various carrier board rails that need to be discharged are pulled to GND.

Figure 5-11. Power Discharge

囯

Note: The resistor values in the discharge circuit for each rail should be tuned to bring the rail down in the proper timeframe.

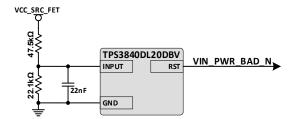

#### 5.5 Power Loss Detection

The circuit in Figure 5-11 is implemented on the Jetson Thor carrier board to detect a loss or unacceptable droop on the main power input (VCC\_SRC).

**VIN Loss Detection Circuit** Figure 5-12.

# 56 Deep Sleep or SC7

Jetson Thor supports a low power state called Deep Sleep or SC7. This can be entered under software control, and exited using various mechanisms, including wake capable pins that are listed in the pin mux. More details related to SC7 can be found in the module data sheet and developer guide.

# **Chapter 6. General Routing Guidelines**

# 6.1 Signal Name Conventions

The following conventions are used in describing the signals for Jetson Thor:

- > Signal names use a mnemonic to represent the function of the signal. For example, Serial Peripheral Interface Chip Select signal is represented as SPI\_CS, with a different font to distinguish it from other text. All active low signals are identified by an underscore followed by capital N (N) after the signal name. For example, SYS\_RESET\_N indicates an active low signal. Active high signals do not have the underscore-N (N) after the signal names. For example, CARRIER\_POWER\_ON indicates an active high signal. Differential signals are identified as a pair with the same names that end with \_P and \_N, just P and N or + and - (for positive and negative, respectively). For example, USB1\_P and USB1\_N indicate a differential signal pair.

- > I/O Type: The signal I/O type is represented as a code to indicate the operational characteristics of the signal.

The following table lists the I/O codes used in the signal description tables.

Table 6-1. Signal Type Codes

| Code     | Definition                              |  |  |

|----------|-----------------------------------------|--|--|

| Α        | Analog                                  |  |  |

| DIFF I/O | Bidirectional Differential Input/Output |  |  |

| DIFF IN  | Differential Input                      |  |  |

| DIFF OUT | Differential Output                     |  |  |

| I/O      | Bidirectional Input/Output              |  |  |

| I        | Input                                   |  |  |

| 0        | Output                                  |  |  |

| OD       | Open Drain Output                       |  |  |

| I/OD     | Bidirectional Input / Open Drain Output |  |  |

| Р        | Power                                   |  |  |

# 6.2 Routing Guideline Format

The routing guidelines have the following format to specify how a signal should be routed.

- > Breakout traces are traces routed from a BGA or other pin array, either to a point beyond the array, or to another layer where full normal spacing guidelines can be met. Breakout trace delay is limited to 12.5 mm unless otherwise specified.

- After breakout, signals should be routed according to specified impedance for differential, single-ended, or both (for example: HDMI). Trace spacing to other signals also specified.

- Follow maximum and minimum trace delays where specified. Trace delays are typically shown in mm or in terms of signal delay in pico-seconds (ps) or both.

- For differential signals, trace spacing to other signals must be larger of specified × dielectric height or inter-pair spacing.

- Spacing to other signals or pairs cannot be smaller than spacing between complementary signals (intra-pair).

- Total trace delay depends on signal velocity, which is different between outer (microstrip) and inner (stripline) layers of a PCB.

# 6.3 Signal Routing Conventions

Throughout this design guide, the following signal routing conventions are used:

SE Impedance (/ Diff Impedance) at x Dielectric Height Spacing

> Single-ended (SE) impedance of trace (along with differential impedance for diff pairs) is achieved by spacing requirement. Spacing requirements are specified as a multiple of dielectric height. Dielectric height is typically different for microstrip and stripline.

Note: Trace spacing requirement applies to SE traces or differential pairs to other SE traces or differential pairs. It does not apply to traces making up a differential pair. For this case, spacing/trace widths are chosen to meet differential impedance requirement.

### 64 **Routing Guidelines**

Pay close attention when routing high-speed interfaces, such as HDMI, DP, USB 3.2. MGBE, PCIe, or CSI. Each of these interfaces has strict routing rules for the trace impedance, width, spacing, total delay, and delay or flight time matching. The following guidelines provide an overview of the routing guidelines and notations used in this design guide.

# Controlled Impedance

Each interface has different trace impedance requirements and spacing to other traces. It is up to the designer to calculate trace width and spacing required to

achieve specified single-ended (SE) and differential (Diff) impedances. Unless otherwise noted, trace impedance values are ±15%.

# Max Trace Lengths and Delays

Trace lengths and delays should include main PCB routing and any additional routing on a flex or secondary PCB segment connected to main PCB. The maximum length or delay should be from the Jetson Thor to the actual connector (i.e., USB, HDMI and so on) or device (i.e., onboard USB device, Display driver IC, camera imager IC, and so on).

# Trace Delay or Flight Time Matching

Signal flight time is the time it takes for a signal to propagate from one end (driver) to the other end (receiver). One way to get the same flight time for a signal within a signal group is to match trace lengths or delays within the specified delay in the signal group.

- Total trace delay = Carrier PCB trace delay only. Do not exceed maximum trace delay specified.

- It is recommended to match trace delays based on flight time of signals. For example, outer-layer signal velocity could be 5.9 ps/mm and inner-layer 6.9 ps/mm. If one signal is routed 250 mm on the outer layer and second signal is routed 250 mm in the inner layer, the difference in flight time between two signals will be 250 ps! That is a big difference if required matching is 15 ps (trace delay matching). To fix this, inner trace needs to be 36 mm shorter or outer trace needs to be 42 mm longer.

- In this design guide, terms such as intra-pair and inter-pair are used when describing differential pair delay. Intra-pair refers to matching traces within differential pair (for example, true to complement trace matching). Inter-pair matching refers to matching differential pairs average delays to other differential pairs average delays. For CSI CPHY, Intra-trio and inter-trio describe relative trio delays. Intra-trio refers to matching traces within the CPHY trios. Inter-trio matching refers to matching trio average delays to other trio average delays.

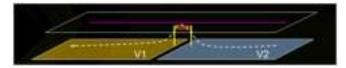

# General PCB Routing Guidelines 6.5

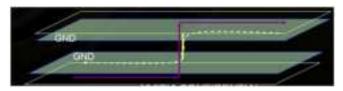

For GSSG stack-up to minimize crosstalk, signals should be routed in such a way that they are not on top of each other in two routing layers, as shown in the following figure.

Signal Routing Example Figure 6-1.

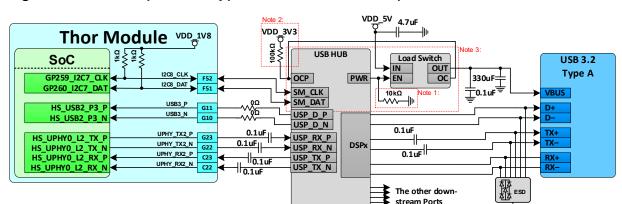

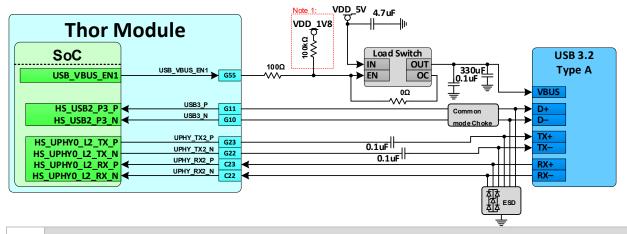

Do not route other signals or power traces and areas directly under or over critical highspeed interface signals.