Figure 2: Position of the connectors on the M.2 board (in mm)

The dimensions (in mm) of the RF connector (Foxconn  $^{\text{TM}}$  KK12011-02-7H) is given below:

Figure 3: RF Connector details

#### 2.1.4 **Power**

Table 5: Power Pads Operational Values

|                     |                      |        |      |           | Typical              | Max Value         |                 |

|---------------------|----------------------|--------|------|-----------|----------------------|-------------------|-----------------|

| Pin                 | Name                 | Supply | Dir. | Min Value | Operational<br>Value | 3GPP RF Compliant | 5<br>Functional |

| 2, 4, 70,<br>72, 74 | VBAT                 | N/A    | In   | 3.2 V     | 3.3 V                | 4.4 V             | 4.6 V           |

| 36                  | SIM_VCC <sup>4</sup> | 1.8 V  | Out  | 1.62 V    | 1.8 V                | 1.98 V            |                 |

| 30                  | SIM_VCC              | 3.0 V  | Out  | 2.7 V     | 3.0 V                | 3.3 V             |                 |

## 2.1.5 (U)SIM

Table 6: (U)SIM Signals

| Pin | Name                    | Supply      | Direction |

|-----|-------------------------|-------------|-----------|

| 30  | SIM_RST                 | 1.8 V/3.0 V | Out       |

| 32  | SIM_CLK                 | 1.8 V/3.0 V | Out       |

| 34  | SIM_IO                  | 1.8 V/3.0 V | In/Out    |

| 36  | SIM_VCC <sup>6</sup>    | 1.8 V/3.0 V | Out       |

| 66  | SIM_DETECT <sup>7</sup> | 1.8 V       | In        |

### 2.1.6 USB

Table 7: USB Signals

| Pin | Name   | Supply | Direction |

|-----|--------|--------|-----------|

| 7   | USB_D+ | 3.3 V  | In/Out    |

| 9   | USB_D- | 3.3 V  | In/Out    |

#### 2.1.7 **UART**

Table 8: UART Signals

| Pin | Name       | Supply | Direction | Pad type 8 | Reset State |

|-----|------------|--------|-----------|------------|-------------|

| 63  | UART0_SOUT | 1.8 V  | Out       | BIDIR_PU   | OUTPUT      |

| 65  | UART0_SIN  | 1.8 V  | Out       | BIDIR_PU   | INPUT       |

<sup>&</sup>lt;sup>4</sup> See also Section (U)SIM.

<sup>&</sup>lt;sup>5</sup> Functional behavior of the module with possible degradation of RF performances.

<sup>&</sup>lt;sup>6</sup> See range of values in Table 5.

<sup>&</sup>lt;sup>7</sup> SIM\_DETECT is active HIGH (HIGH when a card is present, LOW when no card is present)

<sup>8</sup> UART pad types are BIDIR\_PU as detailed in Table 12. All their electrical characteristics are detailed in Table 13.

#### 2.1.8 Non Interfacing Signals

Table 9: Non Interfacing Signals

| Pin | Name                      | Supply                    | Direction | Pin Type  | Output<br>Class | Reset<br>State | Default<br>Setting |

|-----|---------------------------|---------------------------|-----------|-----------|-----------------|----------------|--------------------|

| 6   | MODULE_PWR_EN             | VDD_PWR_EN (see Table 11) | In        | N/A       | N/A             | N/A            | N/A                |

| 10  | NETWORK_LED_N             | 1.8 V                     | Out       | BIDIR_PU  | 4 mA            | INPUT          | INPUT,<br>PULL-UP  |

| 23  | WAKE_ON_WAN_N (see below) | 1.8 V                     | Out       | See below | N/A             | N/A            | N/A                |

| 67  | RESET_N (see below)       | 1.8 V                     | In        | N/A       | N/A             | N/A            | N/A                |

RESET N

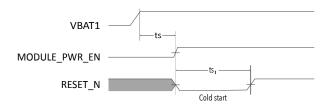

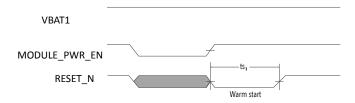

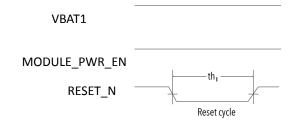

Active low (RESET). This signal is used to reset the module. The following timing requirement applies to the signals VBAT1, MODULE\_PWR\_EN and RESET\_N. It must be respected for proper module behaviour.

Figure 4: VBAT1, MODULE\_PWR\_EN and RESET\_N Signals Timing Requirement for Cold Start

Figure 5: VBAT1, MODULE\_PWR\_EN and RESET\_N Signals Timing Requirement for Warm Start

Figure 6: VBAT1, MODULE\_PWR\_EN and RESET\_N Signals Timing Requirement for Reset Cycle

Minimum values are listed in Table 10

$<sup>^9\,\,</sup>$  Pad types are detailed in Table 12. All their electrical characteristics are detailed in Table 13.

**Table 10:** VBAT1, MODULE\_PWR\_EN and RESET\_N Timing Values

| Symbol | Description        | Minimum Duration | Maximum Duration |

|--------|--------------------|------------------|------------------|

| ts     | VBAT1 setup time   | 0 ms             | -                |

| ts1    | RESET_N setup time | 1 ms             | -                |

| th1    | RESET_N hold time  | 1 μs             | -                |

WAKE\_ON\_WAN\_N

Open drain, active low. This pad wakes up the host. Requires a 10 k $\Omega$  pull-up resistor on host side. If unused, do not connect.

If the host does support USB suspend-resume but not remote wake-up function, the WoWWAN# M.2 signal is needed to wake up the host.

Table 11: DC Characteristics for MODULE\_PWR\_EN, Voltage VDD\_PWR\_EN

| Parameter          | Min. | Nom. | Max. | Unit |

|--------------------|------|------|------|------|

| $V_{ m IL}$        | -0.3 |      | 0.4  | V    |

| Input Low Voltage  |      |      |      |      |

| $V_{\mathrm{IH}}$  | 1.1  |      | VBAT | V    |

| Input High Voltage |      |      |      |      |

## 2.2 Interfaces Description for the LCC Model

Data for the LCC model will be provided in a future edition of this document.

## 2.3 Digital I/O Characteristics

The voltage and current characteristics of the various I/O pads of the CA410 are given in the tables below.

Table 12 details the various pad types listed in CA410 signals list.

Table 12: Pad Types Detail

| Pad Type | Description                                                                                            | Maximum Input High Voltage |

|----------|--------------------------------------------------------------------------------------------------------|----------------------------|

| Analogue | Analogue (or power for powers and ground for grounds)                                                  | Not Applicable             |

| BIDIR_PD | 1.8 V in/out with software controlled internal pulldown. Refer to Table 13 for DC I/O characteristics. | $V_{IH}$ max = 3.6 V       |

| BIDIR_PU | 1.8 V in/out with software controlled internal pullup. Refer to Table 13 for DC I/O characteristics.   | $V_{IH}$ max = 3.6 V       |

| IN       | 1.8V input.                                                                                            | $V_{IH}$ max = 3.6 V       |

| Pad Type | Description                                                                                            | Maximum Input High Voltage |

|----------|--------------------------------------------------------------------------------------------------------|----------------------------|

| IN_PD    | 1.8 V input with software controlled internal pull-down. Refer to Table 13 for DC I/O characteristics. | $V_{IH}$ max = 3.6 V       |

| IN_PU    | 1.8V input with software controlled internal pull-up.                                                  | $V_{IH}$ max = 3.6 V       |

| OUT      | 1.8 V output. Refer to Table 13 for DC I/O characteristics.                                            | $V_{IH}$ max = 3.6 V       |

Refer to CA410 pin list for the type of I/O pad used on every termination.

- The Minimum values for I<sub>OL</sub> and I<sub>OH</sub> should not be exceeded to guarantee that the logical level are not spoiled for each pad type.

- The Nominal values for I<sub>OL</sub> and I<sub>OH</sub> represent the nominal values for the pad type. They are provided for information only.

- ullet The Maximum values for  $I_{OL}$  and  $I_{OH}$  represent the maximal values for the pad type. They are provided for information only.

Table 13: DC Characteristics for Digital I/Os, Voltage 1.8 V

| Parameter C                                                         | rive Strength | Min. | Nom. | Max. | Unit |

|---------------------------------------------------------------------|---------------|------|------|------|------|

| $ m V_{IL}$                                                         |               | -0.3 |      | 0.63 | V    |

| Input Low Voltage                                                   |               |      |      |      |      |

| $V_{\mathrm{IH}}$                                                   |               | 1.17 |      | 3.6  | V    |

| Input High Voltage                                                  |               |      |      |      |      |

| $V_{\mathrm{T}}$                                                    |               | 0.79 | 0.87 | 0.94 | V    |

| Threshold Point                                                     |               |      |      |      |      |

| $V_{T+}$                                                            |               | 1    | 1.12 | 1.22 | V    |

| Schmitt Trigger Low to High Threshold Point                         |               |      |      |      |      |

| V <sub>T</sub> .                                                    |               | 0.61 | 0.71 | 0.8  | V    |

| Schmitt Trigger High to Low Threshold Point                         |               |      |      |      |      |

| $V_{TPU}$                                                           |               | 0.79 | 0.86 | 0.93 | V    |

| Threshold Point with Pull-up Resistor Enabled                       |               |      |      |      |      |

| $V_{TPD}$                                                           |               | 0.8  | 0.87 | 0.95 | V    |

| Threshold Point with Pull-down Resistor Enabled                     |               |      |      |      |      |

| $V_{T+PU}$                                                          |               | 1    | 1.12 | 1.21 | V    |

| Schmitt Trigger Low to High Threshold Point with Pull-up Resi       | stor Enabled  |      |      |      |      |

| V <sub>T-PU</sub>                                                   |               | 0.61 | 0.7  | 0.8  | V    |

| Schmitt Trigger High to Low Threshold Point with Pull-up Resi       | stor Enabled  |      |      |      |      |

| $V_{T+PD}$                                                          |               | 1.01 | 1.13 | 1.23 | V    |

| Schmitt Trigger Low to High Threshold Point with Pull-down Fenabled | Resistor      |      |      |      |      |

| Parameter                                                  | Drive Strength    | Min. | Nom. | Max. | Unit |

|------------------------------------------------------------|-------------------|------|------|------|------|

| V <sub>T-PD</sub>                                          | -                 | 0.62 | 0.72 | 0.81 | V    |

| Schmitt Trigger High to Low Threshold Point with P Enabled | ull-down Resistor |      |      |      |      |

| $I_{\mathrm{I}}$                                           |                   |      |      | ±10  | μΑ   |

| Input Leakage Current @ VI=1.8V or 0V                      |                   |      |      |      |      |

| $I_{OZ}$                                                   |                   |      |      | ±10  | μΑ   |

| Tri-state Output Leakage Current @ VO=1.8V or 0V           |                   |      |      |      |      |

| Input Capacitance                                          |                   |      | 3    |      | pF   |

| R <sub>PU</sub>                                            |                   | 56   | 89   | 148  | kΩ   |

| Pull-up Resistor                                           |                   |      |      |      |      |

| R <sub>PD</sub>                                            |                   | 52   | 90   | 167  | kΩ   |

| Pull-down Resistor                                         |                   |      |      |      |      |

| V <sub>OL</sub>                                            |                   |      |      | 0.45 | V    |

| Output Low Voltage                                         |                   |      |      |      |      |

| V <sub>OH</sub>                                            |                   | 1.35 |      |      | V    |

| Output High Voltage                                        |                   |      |      |      |      |

| $I_{OL}$                                                   | 2 mA              | 1.2  | 2.2  | 3.6  | mA   |

| Low Level Input Current at V <sub>OL</sub> (max)           | 4 mA              | 2.3  | 4.3  | 7.1  | mA   |

|                                                            | 8 mA              | 4.6  | 8.6  | 14.3 | mA   |

| $I_{OH}$                                                   | 2 mA              | 1.0  | 2.4  | 4.6  | mA   |

| High Level Output Current at V <sub>OH</sub> (max)         | 4 mA              | 2.0  | 4.7  | 9.2  | mA   |

|                                                            | 8 mA              | 4.0  | 9.4  | 18.4 | mA   |

# **3** Reliability and Radio performance

## 3.1 Reliability Figures

The reliability test plan for the CA410 comprises the steps below:

| Item                                | DQA Test Stress Conditions                                                                                                                                       | Standards         | Results |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|

| Pro-con                             | (a) Bake: 125°C / 24 h<br>(b) MSL3: 30°C / 60% RH, 192 h<br>(c) SAT (CSAM & TSCAN)<br>(d) X-ray<br>(e) Reflow 3 cycles @ Tp: 250 ± 2°C<br>(f) SAT (CSAM & TSCAN) | JESD22-A113       | *       |

| TC 1000                             | Temperature Cycling (TC): -40°C to +85°C Air to air 23 min Ramp rate 20°C / min 1000 cycles                                                                      | JESD22-A104       | *       |

| ТНВ                                 | Temperature Humidity Bias Test: 85°C, 85% RH<br>Vcc max<br>1000 h +168/-24 h                                                                                     | JESD22-A101       | *       |

| Environmental Testing<br>A Cold     | Environmental Testing - Test A Cold -40 °C, 96 h                                                                                                                 | IEC60068-2-1      | *       |

| Environmental Testing<br>B Dry Heat | Environmental Testing - Test B Dry Heat +85 °C, 1000 h                                                                                                           | IEC60068-2-2      | *       |

| HTOL                                | High Temperature Operation Test: $75^{\circ}\text{C}$ $V_{cc}$ max $Tx: 50\%$ and $Rx: 50\%$ 283 h                                                               | N/A               | *       |

| HTS                                 | High Temperature Storage Test: +85°C, 1000 h                                                                                                                     | IEC60068-2-2      | *       |

| LTS                                 | Low Temperature Storage Test: -40°C, 1000 h                                                                                                                      | IEC60068-2-1      | *       |

| Micro Analysis (MA)                 | Micro analysis X-ray SAT,<br>CSA TC = 0 TC = 1000 cycles                                                                                                         | N/A               | *       |

| Shock                               | Mechanical Shock (MS): Half Sine $500 \text{ m/s}^2$ $11 \text{ ms}$ $6 \text{ shocks (one for each } \pm \text{ axis)}$                                         | DIN<br>IEC68-2-27 | *       |

| Item                     | DQA Test Stress Conditions                                                                                                                                                                                   | Standards                                | Results |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------|

| Drop                     | Drop Test: 1. Height: 80 cm 2. Concrete or steel 3. All surfaces and edges                                                                                                                                   | DIN<br>IEC68-2-31<br>ETS 300019-2-7      | *       |

| Vibration                | Vibration Test (Vib): Sweep-Sine Vibration: Sinusoidal 10 to 500 Hz 1.0 octave/min 10 sweep cycles for 2h on each axis (X, Y, Z)                                                                             | DIN IEC68-2-6<br>EIA/TIA 571<br>§4.1.1.2 | *       |

| Human Body Model ESD     | $TA = 25  ^{\circ}C$ $\pm 1000  V \rightarrow \pm 2000 V$                                                                                                                                                    | JS-001<br>JESD22-A114                    | *       |

| Charged Device Model ESD | $TA = 25 \text{ °C}$ $\pm 250 \text{ V} \rightarrow \pm 500 \text{ V}$                                                                                                                                       | JS-002<br>STM5.3.1                       | *       |

| Dimensions               | Package Physical Dimensions (including 'warpage')                                                                                                                                                            | N/A                                      | *       |

| TCT                      | Temperature Change Test: 10 cycles One cycle follows these steps (roughly 7+ h): Ramp ambient (23°C) to -40°C at 3°C / min 3 h at -40°C Ramp to 85°C at 3°C / min 3 h at 85°C Ramp 85°C to 23°C at 3°C / min | IEC60068-2-14                            | *       |

| Drop (Transportation)    | Free Fall: 1 corner 3 edges and 6 faces at a height of 76 cm.                                                                                                                                                | ASTM D5276                               | *       |

<sup>\*:</sup> All results will be included in a future version of this document.

## 3.2 RF Performance

The RF performance figures of the CA410 M will be given in a future edition of this document.

## 3.3 Power Consumption

The power consumption figures for the CA410 M will be given in a future edition of this document.

**Mechanical Characteristics**

## 4.1 Device Marking

#### Figure 7: CA410 Shield Marking Description

The elements marked on the package are:

- Sequans's logo

- CA410 product name

- Cassiopeia platform name

- RoHS logo

- FCC ID: 2AAGMCA410A

- IC/ISED: 12732A-CA410A

- IMEI as digits and QR code

- The module Serial Number as digits and QR code:

- VVV: 4MA

- YYMMDD: Manufacturing date

- LLLL: tracking batch number

- SSS: three-digits serial number (HEX format 000 to FFF)

- Manufacturing country (VN: Vietnam)

## 4.2 M.2 Device

#### 4.2.1 Mechanical Characteristics

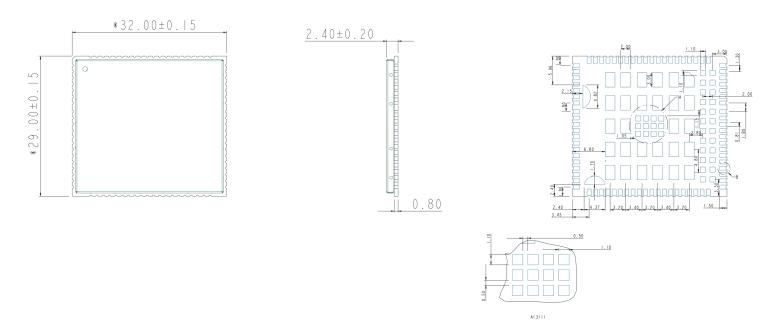

#### Figure 8: Mechanical Description

The dimensions shown in Figure 8 are in millimeters.

The CA410 M.2 complies to the M.2 specification, type 3042-S3-B.

#### 4.2.2 Packing

The CA410 M.2 is delivered in tray. One tray can hold up to 40 pieces. 1 box can contain 10 trays, thus up to 400 pieces. This is represented on Figure 9.

Figure 9: CA410 M.2 Packing

## 4.3 LCC Device

#### 4.3.1 Mechanical Characteristics

Figure 10: Mechanical Description

The dimensions shown in Figure 10 are in millimeters.

#### 4.3.2 Packing

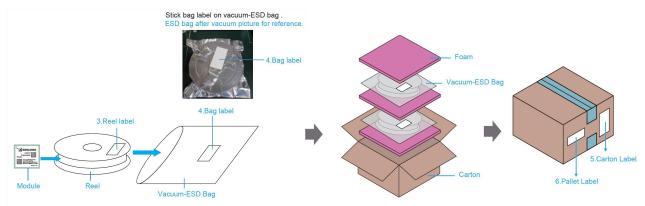

The CA410 LCC is delivered in reels. One reel can hold up to 500 pieces. 1 box can contain 2 reels, thus up to 1000 pieces. This is represented on Figure 11.

Figure 11: CA410 LCC Packing