# Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition User Guide

### **Programmer**

Updated for Intel® Quartus® Prime Design Suite: 20.4

### **Contents**

| 1. In | tel®  | Quartus $^{f g}$ Prime Programmer User Guide                                                    | 4    |

|-------|-------|-------------------------------------------------------------------------------------------------|------|

|       | 1.1.  | Generating Primary Device Programming Files                                                     | 5    |

|       |       | Generating Secondary Programming Files                                                          |      |

|       |       | 1.2.1. Generating Secondary Programming Files (Programming File Generator)                      | 7    |

|       |       | 1.2.2. Generating Secondary Programming Files (Convert Programming File                         |      |

|       |       | Dialog Box)                                                                                     |      |

|       | 1.3.  | Enabling Bitstream Security for Intel Stratix 10 Devices                                        |      |

|       |       | 1.3.1. Enabling Bitstream Authentication (Programming File Generator)                           | 19   |

|       |       | 1.3.2. Specifying Additional Physical Security Settings (Programming File                       |      |

|       |       | Generator)                                                                                      |      |

|       |       | 1.3.3. Enabling Bitstream Encryption (Programming File Generator)                               | . 22 |

|       | 1.4.  | Enabling Bitstream Encryption or Compression for Intel Arria 10 and Intel Cyclone 10 GX Devices | 22   |

|       | 1 5   | Generating Programming Files for Partial Reconfiguration                                        |      |

|       | 1.5.  | 1.5.1. Generating PR Bitstream Files                                                            |      |

|       |       | 1.5.2. Partial Reconfiguration Bitstream Compatibility Checking                                 |      |

|       |       | 1.5.3. Raw Binary Programming File Byte Sequence Transmission Examples                          |      |

|       |       | 1.5.4. Generating a Merged .pmsf File from Multiple .pmsf Files                                 |      |

|       | 1.6.  | Generating Programming Files for Intel FPGA Devices with Hard Processor Systems                 |      |

|       |       | 1.6.1. Generating Programming Files for HPS Boot First Boot Flows                               |      |

|       |       | 1.6.2. Generating Programming Files for FPGA Configuration First Boot Flows                     |      |

|       | 1.7.  | Scripting Support                                                                               |      |

|       |       | 1.7.1. quartus_pfg Command Line Tool                                                            |      |

|       |       | 1.7.2. quartus_cpf Command Line Tool                                                            | 36   |

|       | 1.8.  | Generating Programming Files Revision History                                                   | . 37 |

| 2. Us | ing t | he Intel Quartus Prime Programmer                                                               | 39   |

|       |       | Intel Quartus Prime Programmer                                                                  |      |

|       |       | Programming and Configuration Modes                                                             |      |

|       |       | Basic Device Configuration Steps                                                                |      |

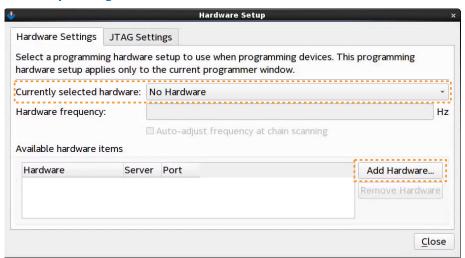

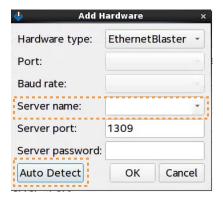

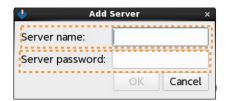

|       | 2.4.  | Specifying the Programming Hardware Setup                                                       | 42   |

|       |       | 2.4.1. JTAG Chain Debugger Tool                                                                 |      |

|       |       | 2.4.2. Editing the Details of an Unknown Device                                                 |      |

|       |       | 2.4.3. Running JTAG Daemon with Linux                                                           |      |

|       | 2.5.  | Programming with Flash Loaders                                                                  |      |

|       |       | 2.5.1. Specifying Flash Partitions                                                              |      |

|       |       | 2.5.2. Full Erase of Flash Memory Sectors                                                       |      |

|       | 2.6.  | Verifying the Programming File Source with Project Hash                                         |      |

|       | 2 7   | 2.6.1. Obtaining Project Hash for Intel Arria 10 Devices                                        |      |

|       |       | Using PR Bitstream Security Verification (Intel Stratix 10 Designs)                             |      |

|       | 2.8.  | Stand-Alone Programmer                                                                          |      |

|       | 2.0   |                                                                                                 |      |

|       | 2.9.  | Programmer Settings Reference                                                                   |      |

|       |       | 2.9.2. More Security Options Dialog Box                                                         |      |

|       |       | 2.9.3. Output Files Tab Settings (Programming File Generator)                                   |      |

|       |       | 2.9.4. Input Files Tab Settings (Programming File Generator)                                    |      |

|       |       | 2.9.5. Bitstream Co-Signing Security Settings (Programming File Generator)                      |      |

#### Contents

| 2.9.6. Configuration Device Tab Settings                                   | 59 |

|----------------------------------------------------------------------------|----|

| 2.9.7. Add Partition Dialog Box (Programming File Generator)               | 60 |

| 2.9.8. Convert Programming File Dialog Box                                 | 61 |

| 2.9.9. Compression and Encryption Settings (Convert Programming File)      | 61 |

| 2.9.10. SOF Data Properties Dialog Box (Convert Programming File)          | 62 |

| 2.9.11. Select Devices (Flash Loader) Dialog Box                           | 63 |

| 2.10. Scripting Support                                                    | 63 |

| 2.10.1. The jtagconfig Debugging Tool                                      | 64 |

| 2.11. Using the Intel Quartus Prime Programmer Revision History            | 64 |

| 3. Using the HPS Flash Programmer                                          | 67 |

| 3.1. HPS Flash Programmer Command-Line Utility                             | 68 |

| 3.2. How the HPS Flash Programmer Works                                    |    |

| 3.3. Using the Flash Programmer from the Command Line                      | 68 |

| 3.3.1. HPS Flash Programmer                                                | 68 |

| 3.3.2. HPS Flash Programmer Command Line Examples                          | 70 |

| 3.4. Supported Memory Devices                                              | 71 |

| 3.5. HPS Flash Programmer User Guide Revision History                      | 73 |

| A. Intel Quartus Prime Pro Edition User Guide: Programmer Document Archive | 74 |

| B. Intel Quartus Prime Pro Edition User Guides                             | 75 |

### 1. Intel® Quartus® Prime Programmer User Guide

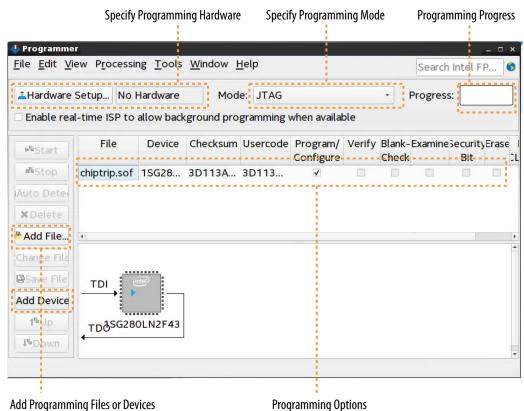

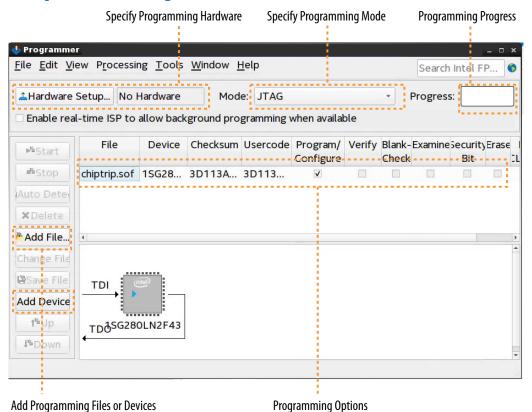

The Intel® Quartus® Prime Programmer allows you to program and configure Intel CPLD, FPGA, and configuration devices. Following full design compilation, you generate the primary device programming files in the Assembler, and then use the Programmer to load the programming file to a device. This user guide details Intel FPGA programming file generation and use of the Intel Quartus Prime Programmer.

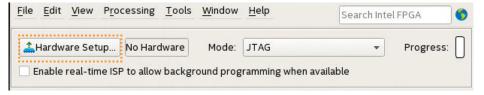

#### Figure 1. Intel Quartus Prime Programmer

#### **Related Information**

- Generating Primary Device Programming Files on page 5

- Generating Secondary Programming Files on page 6

- Enabling Bitstream Security for Intel Stratix 10 Devices on page 18

- Using the Intel Quartus Prime Programmer on page 39

- Programming with Flash Loaders on page 45

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

#### 1.1. Generating Primary Device Programming Files

By default, the Compiler's Assembler module generates the primary device programming files at the end of full compilation. Alternatively, you can start the Assembler independently any time after design place and route to generate primary device programming files, such as SRAM Object Files (.sof) for configuration of Intel FPGAs.

Follow these steps to generate primary device programming files:

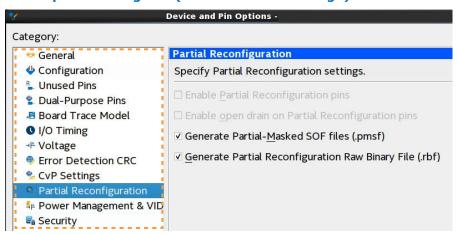

To specify programming options that enable features in the primary device programming file, such as Configuration, Error Detection CRC, and device Security options, click Assignments ➤ Device ➤ Device & Pin Options. Device & Pin Options Dialog Box on page 49 describes all options. (1)

Figure 2. Device & Pin Options Dialog Box (Intel Stratix® 10 Design)

- To generate primary device programming files, click Processing ➤ Start ➤ Start

Assembler, or double-click Assembler on the Compilation Dashboard. The

Assembler generates the programming files according to the options you specify.

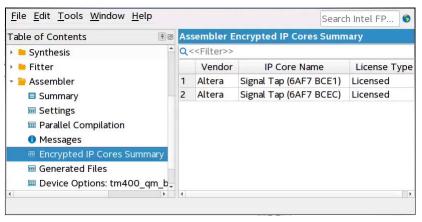

- 3. After running the Assembler, view detailed information about programming file generation, including the programming file Summary and Encrypted IP information in the Assembler report folder in the Compilation Report.

<sup>(1)</sup> Security options not yet available for Intel Agilex<sup>™</sup> devices.

Figure 3. Assembler Reports

Note: Each successive release of the Intel Quartus Prime software typically includes:

- Added support for new features in supported FPGA devices.

- Added support for new devices.

- Efficiency and performance improvements.

- Improvements to compilation time and resource use of the design software.

Due to these improvements, different versions of the Intel Quartus Prime Pro Edition, Intel Quartus Prime Standard Edition, and Intel Quartus Prime Lite Edition software can produce different programming files from release to release.

#### 1.2. Generating Secondary Programming Files

After generating primary device programming files, you can optionally generate one or more derivative programming files for alternative device configurations, such as flash programming, partial reconfiguration, remote system update, Configuration via Protocol (CvP), or hard processor system (HPS) core configuration.

You can use the **Programming File Generator** or **Convert Programming Files** dialog box to generate secondary programming files:

- The **Programming File Generator** supports advanced programming features and is optimized for Intel Agilex, Intel Stratix<sup>®</sup> 10, Intel MAX<sup>®</sup> 10, and Intel Cyclone<sup>®</sup> 10 LP devices.

- The **Convert Programming Files** dialog box supports all devices released prior to Intel Stratix 10 devices.

**Table 1.** Secondary Programming File Generators

|                | Programming File<br>Generator                                  | Convert Programming Files                                      |                                                                                                                      |  |  |

|----------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| Device Support | Intel Agilex Intel Stratix 10 Intel MAX 10 Intel Cyclone 10 LP | Intel Arria® 10     Intel Cyclone 10GX and LP     Intel MAX 10 | APEX20K, Arria II GX and GZ, Arria V,<br>Cyclone, Cyclone II, Cyclone III and LS,<br>Cyclone IV E and GX, Cyclone V, |  |  |

| Programming File<br>Generator | Convert Programming Files                                                                   |

|-------------------------------|---------------------------------------------------------------------------------------------|

|                               | HardCopy® III, HardCopy II, HardCopy IV, MAX V, Stratix, Stratix III, Stratix IV, Stratix V |

### **1.2.1.** Generating Secondary Programming Files (Programming File Generator)

Follow these steps to generate secondary programming files for alternative device programming methods with the **Programming File Generator**.

- 1. Generate the primary programming files for your design, as Generating Primary Device Programming Files on page 5 describes.

- 2. Click File ➤ Programming File Generator.

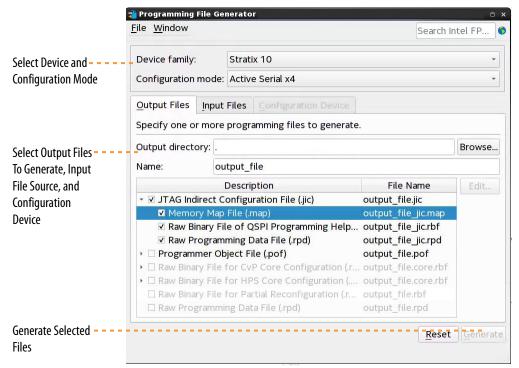

- 3. For **Device family**, select your target device. The options available in the **Programming File Generator** change dynamically, according to your device and configuration mode selection.

- For Configuration mode, select an Active Serial mode that your device supports. Configuration Modes (Programming File Generator) on page 10 describes all modes.

- 5. On the **Output Files** tab, enable the checkbox for generation of the file you want to generate. The **Input Files** tab is now available. Secondary Programming Files (Programming File Generator) on page 10 describes all output files.

- 6. Specify the **Output directory** and **Name** for the file you generate. Output Files Tab Settings (Programming File Generator) on page 58 describes all options.

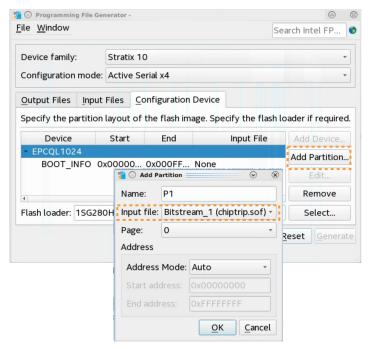

Figure 4. Programming File Generator

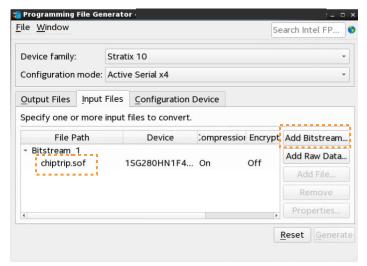

- 7. To specify a .sof file that contains the configuration bitstream data, on the **Input Files** tab, click **Add Bitstream**. To include raw data, click **Add Raw Data** and specify a Hexadecimal (Intel-Format) File (.hex) or Binary (.bin) file.

- 8. To specify bitstream authentication or encryption security settings for the file, select the .sof and click **Properties**, as Enabling Bitstream Authentication (Programming File Generator) on page 19 describes.<sup>(2)</sup>

<sup>(2)</sup> Security options not yet available for Intel Agilex devices.

#### Figure 5. Input Files Tab

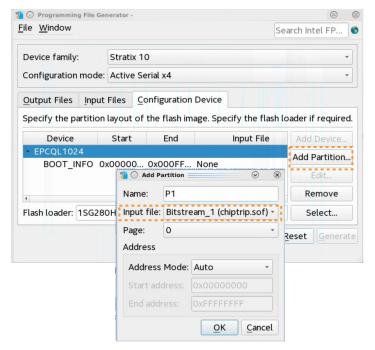

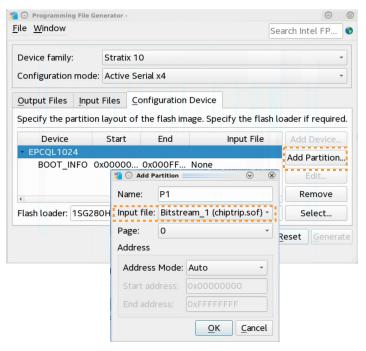

To specify the .sof file that occupies the flash memory partition, click Add Partition on the Configuration Device tab. Add Partition Dialog Box (Programming File Generator) on page 60 describes all options.

#### Figure 6. Add Flash Partition

- 10. To select a supported flash memory device and predefined programming flow, click Add Device on the Configuration Device tab. Alternatively, click << new device>> to define a new flash memory device and programming flow. Configuration Device Tab Settings on page 59 describes all settings.

- 11. Click the **Select** button for **Flash Loader** and select the device that controls loading of the flash memory device. Select Devices (Flash Loader) Dialog Box on page 63 describes all settings.

- 12. After you specify all options in **Programming File Generator**, the **Generate** button enables. Click **Generate** to create the files.

#### 1.2.1.1. Configuration Modes (Programming File Generator)

Select one of the following **Configuration modes** in **Programming File Generator** for generation of secondary programming files:

Table 2.

Programming File Generator Configuration Modes

| <b>Programming Mode</b>   | Description                                                                                                                                                                                                                                                                                                                                                                                           | <b>Supports Devices</b> |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| Active Serial x4          | For storing configuration data in a low-cost serial configuration device with non-volatile memory and four-pin interface. Serial configuration devices provide a serial interface to access the configuration data. During device configuration, Intel Stratix 10 devices read the configuration data through the serial interface, decompress the data if necessary, and configure their SRAM cells. | Intel Agilex            |  |

| AVST x8                   | The Avalon®-ST configuration mode uses an external host, such as a microprocessor or Intel MAX 10 device. The external host controls the                                                                                                                                                                                                                                                              | Intel Stratix 10        |  |

| AVST x16                  | transfer of configuration data from an external storage such as flash                                                                                                                                                                                                                                                                                                                                 |                         |  |

| AVST x32                  | memory to the FPGA. The design that controls the configuration process resides in the external host. You can use the PFL II IP core with an Intel MAX 10 device as the host to read configuration data from a flash memory device that configures an Intel Stratix 10 FPGA.                                                                                                                           |                         |  |

| 1-Bit Passive Serial      | An external controller passes configuration data to one or more FPGA devices via a serial data stream. The FPGA device is a slave device with a 5-wire interface to the external controller. The external controller can be an intelligent host such as a microcontroller or CPU.  Intel Cyclone 10                                                                                                   |                         |  |

| Active Serial             | Stores configuration data in a low-cost serial configuration device with non-volatile memory and four-pin interface.                                                                                                                                                                                                                                                                                  |                         |  |

| Internal<br>Configuration | Uses a .pof file for internal configuration of the Intel MAX 10 device's Configuration Flash Memory (CFM) and User Flash Memory (UFM) via a download cable Intel Quartus Prime Programmer.                                                                                                                                                                                                            | Intel MAX 10            |  |

#### 1.2.1.2. Secondary Programming Files (Programming File Generator)

After generating primary device programming files, you can generate the following secondary device programming files with the **Programming File Generator** for alternative device configuration modes:

**Table 3.** Programming File Generator Output File Types

| Programming File Type                              | Extension | Description                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hexadecimal (Intel-Format)<br>Output File for SRAM | .hexout   | An ASCII text file in Intel hexadecimal format that contains configuration data for programming a parallel data source, such as a configuration device or a mass storage device. The parallel data source in turn configures an SRAM-based Intel device.                                                                                                  |

| JTAG Indirect Configuration<br>File                | .jic      | Proprietary Intel FPGA file type that stores serial flash programming data for programming via Intel FPGA JTAG pins. This method only supports Active Serial configuration. Before programming the flash, the Programmer first configures the FPGA with the Serial Flash Helper Design.                                                                   |

| Map File                                           | .map      | A text file containing the byte addresses of pages and data stored in the memory of a configuration device for                                                                                                                                                                                                                                            |

| Programmer Object File                             | .pof      | A binary file used by the Programmer to program a flash memory device via active serial header, or to program a flash memory device via the Parallel Flash Loader Intel FPGA IP.                                                                                                                                                                          |

| Raw Binary File                                    | .rbf      | Configuration bitstream file for use with a third-party data source, partial reconfiguration, or HPS data source. Supports Passive Serial (PS) and Avalon-Streaming (AVST) modes.                                                                                                                                                                         |

| Raw Binary File for CvP Core<br>Configuration      | .rbf      | A binary file that containing logic that is programmed by configuration (CRAM) for CvP phase 2. The core bitstream is in .rbf format.                                                                                                                                                                                                                     |

| Raw Binary File for HPS Core<br>Configuration      |           | A binary file that containing logic that is programmed by configuration (CRAM) for HPS configuration phase 2. The core bitstream is in .rbf format.                                                                                                                                                                                                       |

| Raw Programming Data File                          | .rpd      | Stores data for configuration with third-party programming hardware. You generate Raw Programming Data Files from a .pof or .sof.  The .rpd file is a subset of a .pof or .jic that includes only device-specific binary programming data for Active Serial configuration scheme with EPCS or EPCQ serial configuration devices and remote system update. |

| Tabular Text File                                  | .ttf      | A TTF contains the decimal equivalent of a Raw Binary File (.rbf).                                                                                                                                                                                                                                                                                        |

# **1.2.2.** Generating Secondary Programming Files (Convert Programming File Dialog Box)

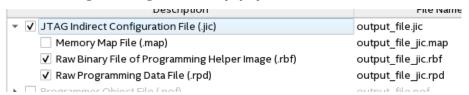

You can use the **Convert Programming File** dialog box to generate secondary programming files for alternative device programming methods. For example, generating the .jic file for flash programming, the .rbf file for partial reconfiguration, or the .rpd file for a third-party programmer configuration.

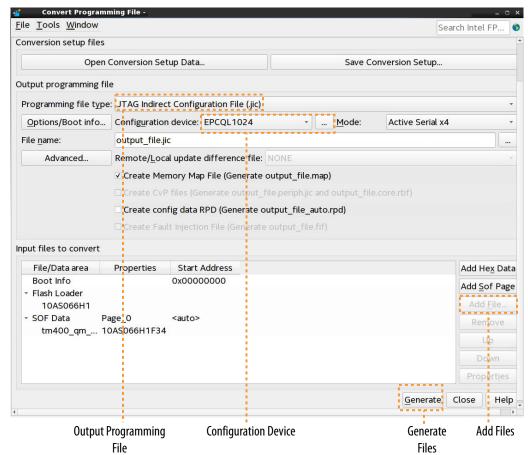

Figure 7. Convert Programming File Dialog Box

The options available in the **Convert Programming File** dialog box change dynamically, according to your device and configuration mode selection.

- 1. Generate the primary programming files for your design, as Generating Primary Device Programming Files on page 5 describes.

- 2. Click File ➤ Convert Programming Files.

- 3. Under **Output programming file**, select the **Programming file type** that you want to generate. Secondary Programming Files (Convert Programming Files) on page 14 describes all file options.

- 4. Specify the **File name** and output directory (...) for the file that you generate.

- For the configuration Mode, select Active Serial x4 or Active Serial. Configuration Modes (Convert Programming Files) on page 15 describes all modes.

Note: Intel Stratix 10 devices support only Active Serial x4.

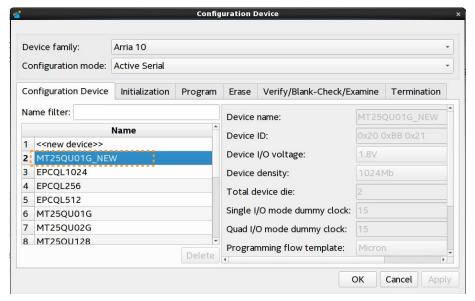

6. To specify the Configuration device, click the (...) button to select a supported flash memory device and predefined programming flow. When you select a predefined device, you cannot modify any setting. Alternatively, click <<new device>> to define a new flash memory device and programming flow. Configuration Device Tab Settings on page 59 describes all settings.

Figure 8. Configuration Device Dialog Box

- 7. Under **Input files to convert**, select the **SOF Data** item, and then click the **Add File** button. Specify the .sof file that contains the configuration bitstream data. To include raw data, click **Add Hex Data** and specify a .hex file.

- 8. To enable bitstream compression or encryption security settings, select the .sof file and click **Properties**, as Enabling Bitstream Encryption or Compression for Intel Arria 10 and Intel Cyclone 10 GX Devices on page 23 describes.

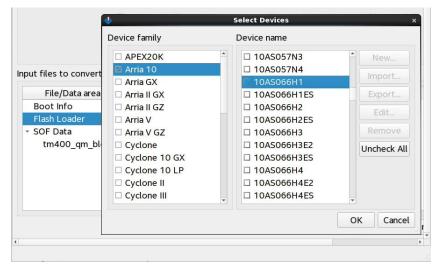

- 9. Select the **Flash Loader** text, and then click the **Add Device** button. Select the device that controls loading of the flash device.

Figure 9. Selecting the Flash Loader Device

10. After you specify all options in the **Convert Programming File** dialog box, click the **Generate** button to create the files.

#### 1.2.2.1. Secondary Programming Files (Convert Programming Files)

After generating primary device programming files, you can generate the following secondary device programming files with the **Convert Programming Files** dialog box for alternative device configuration modes:

**Table 4.** Output File Types

| Programming File Type                              | Extension | Description                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CvP Files                                          | .jic/.rbf | Files required for CvP configuration.                                                                                                                                                                                                                                                                                     |

| Hexadecimal (Intel-Format)<br>Output File for SRAM | .hexout   | An ASCII text file in Intel hexadecimal format that contains configuration data for programming a parallel data source, such as a configuration device or a mass storage device. The parallel data source in turn configures an SRAM-based Intel device.                                                                  |

| JTAG Indirect Configuration File                   | .jic      | Proprietary Intel FPGA file type that stores serial flash programming data for programming via Intel FPGA JTAG pins. This method only supports Active Serial configuration. Before programming the flash, the Programmer first configures the FPGA with the Serial Flash Helper Design.                                   |

| Memory Map File                                    | .map      | Contains the byte addresses of pages and HEX data stored in the memory of an EPC4, EPC8, or EPC16 configuration device. The MAP File stores the start and end addresses of the <b>Main Block Data</b> and <b>Bottom Boot Data</b> items, and the start and end addresses of pages within the <b>Main Block Data</b> item. |

| Partial-Masked SRAM Object Files                   | .pmsf     | Contains the partial-mask bits for configuration of a PR region. The .pmsf file contains all the information for creating PR bitstreams.                                                                                                                                                                                  |

| Merged Mask Setting File                           | .msf      | Contains the mask bits for the static region in a PR design.                                                                                                                                                                                                                                                              |

| Programmer Object File                             | .pof      | A binary file that contains the data for programming non-volatile Intel MAX 10, MAX V, MAX II, or flash memory devices that can configure Intel FPGA devices. A Programmer consists of a remote                                                                                                                           |

|                                                    |           | continued                                                                                                                                                                                                                                                                                                                 |

| Programming File Type     | Extension | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |           | update enabled .pof and additional remote update enabled .sof that you used to program configuration devices in remote update configuration mode.                                                                                                                                                                                                                                                                                      |

| Raw Binary File           | .rbf      | Configuration bitstream file for use with a third-party data source, partial reconfiguration, or HPS data source. Supports Passive Serial (PS) and Avalon-Streaming (AVST) modes.                                                                                                                                                                                                                                                      |

| Raw Programming Data File | .rpd      | Stores data for configuration with third-party programming hardware. You generate Raw Programming Data Files from a .pof or .sof. The .rpd file is a subset of a .pof or .sof that includes only device-specific binary programming data for Active Serial configuration scheme with EPCS or EPCQ serial configuration devices and remote system update. The .rpd file content has one bit swapped in comparison with the output file. |

| Tabular Text File         | .ttf      | A TTF contains the decimal equivalent of a Raw Binary File (.rbf).                                                                                                                                                                                                                                                                                                                                                                     |

#### 1.2.2.2. Configuration Modes (Convert Programming Files)

Select one of the following **Configuration modes** in **Convert Programming Files** for generation of secondary programming files:

Table 5.

Convert Programming Files Configuration Modes

| Programming Mode                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1-Bit/2-Bit/4-Bit/8-Bit Passive<br>Serial | An external controller passes configuration data to one or more FPGA devices via a serial data stream. The FPGA device is a slave device with a 5-wire interface to the external controller. The external controller can be an intelligent host such as a microcontroller or CPU, or the Intel Quartus Prime Programmer, or an EPC2 or EPC16 configuration device.                                                                                                       |  |  |

| Active Parallel                           | Supports configuration devices using commodity 16-bit parallel flash memories to control the configuration interface.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Active Serial                             | For storing configuration data in a low-cost serial configuration device with non-                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Active Serial x4                          | volatile memory. Serial configuration devices provide a serial interface to access the configuration data. During device configuration, the device reads the configuration data through the serial interface, decompresses the data if necessary, and configures their SRAM cells.                                                                                                                                                                                       |  |  |

| AVST x8/x16/x32                           | The Avalon-ST configuration mode uses an external host, such as a microprocessor or Intel MAX 10 device. The external host controls the transfer of configuration data from an external storage such as flash memory to the FPGA. The design that controls the configuration process resides in the external host. You can use the PFL II IP core with an Intel MAX 10 device as the host to read configuration data from a flash memory device that configures an FPGA. |  |  |

| Passive Parallel Synchronous              | An external controller, such as a CPU, loads the design data into a device via a common data bus. Data is latched by the device on the first rising edge of a CPU-driven clock signal. The next eight falling clock edges serialize this latched data within the device. The device latches the next 8-bit byte of data on every eighth rising edge of the clock signal until the device is completely configured.                                                       |  |  |

| Passive Parallel Asynchronous             | An external controller, such as a CPU, loads the design data into a device via a common data bus. The device accepts a parallel byte of input data. Intelligent communication between the external controller and the device allows the external controller to configure the device.                                                                                                                                                                                     |  |  |

| Internal Configuration                    | Uses a .pof file for internal configuration of the Intel MAX 10 device's Configuration Flash Memory (CFM) and User Flash Memory (UFM) via a download cable Intel Quartus Prime Programmer.                                                                                                                                                                                                                                                                               |  |  |

#### 1.2.2.3. Debugging the Configuration (Convert Programming Files)

Click the **Advanced** option in the **Convert Programming Files** dialog box to debug the file conversion configuration. Only choose advanced settings that apply to the design's target Intel FPGA device.

Changes in the **Advanced Options** dialog box affect .pof, .jic, .rpd, and .rbf file generation.

The following table describes the **Advanced Options** settings:

**Table 6. Advanced Options Settings**

| Option Setting                        | Description                                                                                                                                                                                                                                                                                                                                                                           | Values                                                                                           |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Disable EPCS/EPCQ ID check            | Directs the FPGA to skips the EPCS/EPCQ silicon ID verification.  Applies to single and multi device AS configuration modes on all devices.                                                                                                                                                                                                                                           | Default setting is ON (EPCS/EPCQ ID check is enabled).                                           |

| Disable AS mode CONF_DONE error check | Directs the FPGA to skip the CONF_DONE error check. Applies to single- and multi-device (AS) configuration modes on all devices.                                                                                                                                                                                                                                                      | Default setting is OFF (AS mode CONF_DONE error check is enabled).                               |

| Program Length Count adjustment       | Specifies the offset you can apply to the computed PLC of the entire bitstream.  Applies to single- and multi-device (AS) configuration modes on all FPGA devices.                                                                                                                                                                                                                    | Integer (Default = 0)                                                                            |

| Post-chain bitstream pad bytes        | Specifies the number of pad bytes appended to the end of an entire bitstream.                                                                                                                                                                                                                                                                                                         | If the bitstream of the last device is uncompressed, default value is 0. Otherwise, default is 2 |

| Post-device bitstream pad bytes       | Specifies the number of pad bytes appended to the end of the bitstream of a device.  Applies to all single-device configuration modes on all FPGA devices.                                                                                                                                                                                                                            | Zero or positive integer.<br>Default is 0                                                        |

| Bitslice Padding Value                | Specifies the padding value used to prepare bitslice configuration bitstreams, such that all bitslice configuration chains simultaneously receive their final configuration data bit.  Use only in 2, 4, and 8-bit PS configuration mode, when you use an EPC device with the decompression feature enabled. Applies to all FPGA devices that support enhanced configuration devices. | 0 or 1<br>Default value is 1                                                                     |

The following table lists possible symptoms of a failing configuration, and describes the advanced options necessary for configuration debugging.

#### UG-20134 | 2020.12.14

| Failure Symptoms                                                                                                                                                        | Disable EPCS/<br>EPCQ ID<br>Check | Disable AS<br>Mode<br>CONF_DONE<br>Error Check | PLC Settings       | Post-Chain<br>Bitstream Pad<br>Bytes | Post-Device<br>Bitstream Pad<br>Bytes | Bitslice<br>Padding Value |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------|--------------------|--------------------------------------|---------------------------------------|---------------------------|

| Configuration failure occurs after a configuration cycle.                                                                                                               | _                                 | Yes                                            | Yes                | Yes <sup>(3)</sup>                   | Yes <sup>(4)</sup>                    | _                         |

| Decompression feature is enabled.                                                                                                                                       | _                                 | Yes                                            | Yes                | Yes <sup>(3)</sup>                   | Yes <sup>(4)</sup>                    | _                         |

| Encryption feature is enabled.                                                                                                                                          | _                                 | Yes                                            | Yes                | Yes <sup>(3)</sup>                   | Yes <sup>(4)</sup>                    | _                         |

| CONF_DONE stays<br>low after a<br>configuration cycle.                                                                                                                  | _                                 | Yes                                            | Yes <sup>(5)</sup> | Yes <sup>(3)</sup>                   | Yes <sup>(4)</sup>                    | _                         |

| CONF_DONE goes high momentarily after a configuration cycle.                                                                                                            | _                                 | Yes                                            | Yes <sup>(6)</sup> | _                                    | _                                     | _                         |

| FPGA does not<br>enter user mode<br>even though<br>CONF_DONE goes<br>high.                                                                                              | _                                 | _                                              | _                  | Yes <sup>(3)</sup>                   | Yes <sup>(4)</sup>                    | _                         |

| Configuration failure occurs at the beginning of a configuration cycle.                                                                                                 | Yes                               | _                                              | _                  | _                                    | _                                     | _                         |

| EPCS128                                                                                                                                                                 | Yes                               | _                                              | _                  | _                                    | _                                     | _                         |

| Failure in .pof<br>generation for EPC<br>device using Intel<br>Quartus Prime<br>Convert<br>Programming File<br>Utility when the<br>decompression<br>feature is enabled. | _                                 | _                                              | _                  | _                                    | _                                     | Yes                       |

<sup>(6)</sup> Start with negative offset to the PLC settings

<sup>(3)</sup> Use only for multi-device chain

<sup>(4)</sup> Use only for single-device chain

<sup>(5)</sup> Start with positive offset to the PLC settings

#### 1.3. Enabling Bitstream Security for Intel Stratix 10 Devices

Intel Stratix 10 devices provide flexible and robust security features to protect sensitive data, intellectual property, and device hardware from physical and remote attacks. The Intel Stratix 10 device architecture supports bitstream authentication and encryption security features. The Assembler applies bitstream compression automatically to reduce file size whenever you use authentication or encryption.

- **Bitstream Authentication**—verifies that the configuration bitstream and firmware are from a trusted source. Enable additional co-signing device firmware authentication to ensure that only signed firmware runs on the HPS or FPGA, and to authorize HPS JTAG debugging. Enable authentication security by specifying a first level signature chain file (.qky) for the **Quartus Key File** option (**Device and Pin Options** dialog box), as Enabling Bitstream Authentication (Programming File Generator) on page 19 describes. (7)

- **Bitstream Encryption**—protects proprietary or sensitive data from view or extraction in the configuration bitstream using an Advanced Encryption Standard (AES) 256-bit or 384-bit security key. Encryption also provides side-channel protection from non-intrusive attack. You can store the owner AES key in eFuses or BBRAM. Enable encryption by turning on the **Enable programming bitstream encryption** option (**Device and Pin Options** dialog box), as Enabling Bitstream Encryption (Programming File Generator) on page 22 describes.

Table 7. Intel Stratix 10 Bitstream Authentication Files

| Term                                    | Description                                                                                                                                                                                                                                                             | Extension |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| First Level Signature Chain Key<br>File | File you generate that specifies the root key (.pem) and one or more design signing keys (.pem) required to sign the bitstream and allow access to the FPGA when using authentication or encryption.                                                                    | . qky     |

| Root Key File                           | File you generate that anchors the first level signature chain to a known root key. The FPGA calculates the hash of the root entry and checks if it matches the expected hash. The Assembler appends the root key to the programming file and stores the key in eFuses. | . qky     |

| Design Signing Key File                 | File you generate and append to the root key that authenticates the bitstream in the SDM to allow configuration of the device with the pending bitstream. Use separate design signing keys for the FPGA and HPS for highest security.                                   | .pem      |

| Firmware Co-signing Key File            | Files provided in <install>\common\devinfo\programmer \firmware that includes the owner signature and firmware file that you use to sign the firmware to run on the FPGA or HPS.</install>                                                                              | .zip      |

| Signed HPS Certificate File             | Specifies a secure HPS debug certificate that permits access to the JTAG interface for HPS debugging. A secure HPS debug certificate is valid until you power down or reconfigure the device.                                                                           | .cert     |

Note:

Intel Arria 10 and Intel Cyclone 10 GX devices do not support bitstream authentication.

#### **Related Information**

Intel Stratix 10 Device Security User Guide

For detailed device security configuration steps.

<sup>(7)</sup> Bitstream authentication is available only for Intel Stratix 10 devices that include the AS (Advanced Security) ordering code suffix and all Intel Stratix 10 DX devices.

#### 1.3.1. Enabling Bitstream Authentication (Programming File Generator)

Bitstream authentication requires that you generate a first level signature chain (.qky) that includes the root key and one or more design signing keys. The root key enables the base security features and authenticates the design signing key through the public signature chain. The root key stores the SHA-256 or SHA-384 hash of the key in eFuses. You can also optionally enable firmware co-signature capability to require signing the version of configuration firmware that runs on your device. The FPGA device then can only load authenticated firmware.

Note:

Refer to the *Intel Stratix 10 Device Security User Guide* for step-by-step first level signature chain key generation instructions.<sup>(8)</sup>

After you specify the .qky in Assembler settings, the Assembler appends the first level signature chain to the configuration .sof that you generate.

Use the **Programming File Generator** to generate the signed configuration bitstream for an .sof file. The JTAG Indirect Configuration File (.jic) and Raw Programming Data File (.rpd) formats are available for Active Serial (AS) configuration. The Programmer Object File (.pof) and Raw Binary File (.rbf) are available for Avalon Streaming configuration.

Follow these steps to enable bitstream authentication:

- Generate a first level signature chain (.qky) that includes the root key and one or more design signing keys, as *Intel Stratix 10 Device Security User Guide* describes.

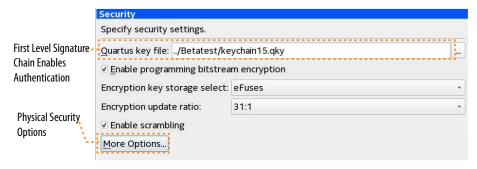

- 2. To add the first level signature chain to a configuration bitstream, click **Assignments ➤ Device ➤ Device and Pin Options ➤ Security**, and then specify the first level signature chain .qky for the **Quartus key file** option.

- To enable more physical device security options, click the More Options button on the Security page. More Security Options Dialog Box on page 57 describes all options.

Figure 10. Security Tab (Device and Pin Options)

<sup>(8)</sup> Security options not yet available for Intel Agilex devices.

- 4. Generate primary device programing files in the Assembler, as Generating Primary Device Programming Files on page 5 describes. The primary device programming file now contains data to enable first level authentication.

- 5. To optionally enable co-signing device firmware authentication, generate a .jic or .rbf secondary programming file with the following options, as Generating Secondary Programming Files (Programming File Generator) on page 7 describes:

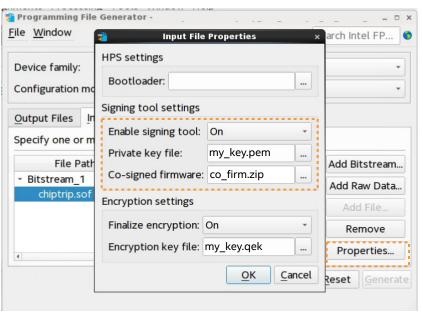

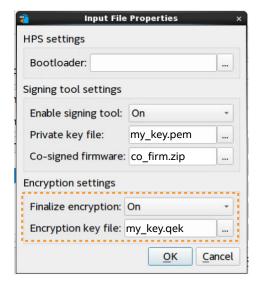

- a. In **Programming File Generator**, click the **Properties** button. The **Input File Properties** dialog box appears.

Figure 11. Enabling Co-Signing Device Firmware Authentication (Intel Stratix 10 Devices)

- b. Set Enable signing tool to On.

- c. For **Private key file**, specify a design signing key Privacy Enhanced Mail Certificates file (.pem) for firmware co-signing. This key can be separate from the FPGA design signing key.

- d. For **Co-signed firmware**, specify a Quartus Co-Signed Firmware file (.zip).

- e. Click **OK**.

- 6. Use the Programmer to configure the device with the .jic or .rbf.

#### **Related Information**

- Device & Pin Options Dialog Box on page 49

- Specifying Additional Physical Security Settings (Programming File Generator) on page 21

- Intel Stratix 10 Device Security User Guide

For detailed information on generating device security keys.

### **1.3.2. Specifying Additional Physical Security Settings (Programming File Generator)**

Intel Stratix 10 devices can store security and other configuration settings in eFuses. You can enable additional physical security settings in eFuses to extend the level of device security protection.

To specify additional physical device security settings, follow these steps:

- 1. Click Assignments ➤ Device ➤ Device and Pin Options ➤ Security.

- 2. On the **Security** tab, specify the First Level Signature Chain . qky file that contains the root key and one or more design signing keys for the **Quartus key file** setting.

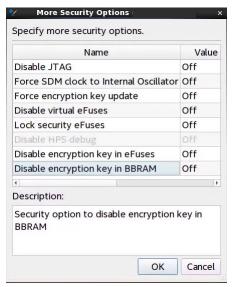

- 3. Click the **More Options** button and specify any of the following:

Figure 12. More Security Options Dialog Box

**Table 8.** More Security Options Dialog Box Settings

| Option                                 | Description                                                                                                                                                                                                      | Values                                                                                       |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Disable JTAG                           | Disables JTAG command and configuration of the device. Setting this eliminates JTAG as mode of attack, but also eliminates boundary scan functionality.                                                          | Off—inactive     On—active until wipe of containing                                          |  |  |

| Force SDM clock to internal oscillator | Disables an external clock source for the SDM. The SDM must use the internal oscillator. Using an internal oscillator is more secure than allowing an external clock source for configuration.                   | <ul> <li>design</li> <li>On sticky—active until next POR</li> <li>On check—checks</li> </ul> |  |  |

| Force encryption key update            | Specifies that the encryption key must update by the frequency that you specify for the <b>Encryption update ratio</b> option. The default ration value is 31:1. Encryption supports up to 20 intermediate keys. | for corresponding<br>blown fuse                                                              |  |  |

| Disable virtual eFuses                 | Disables the eFuse virtual programming capability.                                                                                                                                                               |                                                                                              |  |  |

| Lock security eFuses                   | Causes eFuse failure if the eFuse CRC does not match the calculated value.                                                                                                                                       |                                                                                              |  |  |

| continued                              |                                                                                                                                                                                                                  |                                                                                              |  |  |

| Option                           | Description                                                                                                                                                   | Values |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Disable HPS debug                | Disables debugging through the JTAG interface to access the HPS.                                                                                              |        |

| Disable encryption key in eFuses | Specifies that the device cannot use an AES key stored in eFuses. Rather, you can provides an extra level of security by storing the AES key in BBRAM.        |        |

| Disable encryption key in BBRAM  | Specifies that the device cannot use AES key stored in BBRAM.<br>Rather, you can provides an extra level of security when you store<br>the AES key in eFuses. |        |

#### 4. Click OK.

#### **Related Information**

Enabling Bitstream Authentication (Programming File Generator) on page 19

#### 1.3.3. Enabling Bitstream Encryption (Programming File Generator)

To enable bitstream encryption, you must first generate a first level signature chain (.qky) that enables encryption options in the GUI. Next, you generate the encrypted configuration bitstream in the Assembler. Finally, you generate a secondary programming file that specifies the AES **Encryption Key file** (.qek) for bitstream decryption.

Follow these steps to enable bitstream encryption:

- 1. Generate a First Level Signature Chain that includes the root key and one or more design signing keys, as *Intel Stratix 10 Device Security User Guide* describes.

- 2. Click Assignments ➤ Device ➤ Device and Pin Options ➤ Security.

- 3. For the **Quartus key file** setting, specify the first level signature chain .qky that contains the root key and one or more design signing keys.

- 4. Turn on **Enable programming bitstream encryption**, and specify one or more of the following:

**Table 9.** Assembler Encryption Security Settings

| Option                        | Description                                                                                                                                                                                                                                                                              |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Encryption key storage select | Specifies the location that stores the .qek key file. You can select either <b>Battery Backup RAM</b> or <b>eFuses</b> for storage.                                                                                                                                                      |  |

| Encryption update ratio       | Specifies the ratio of configuration bits compared to the number of key updates required for bitstream decryption. You can select either <b>31:1</b> (the key must change 1 time every 31 bits) or <b>Disabled</b> (no update required). Encryption supports up to 20 intermediate keys. |  |

| Enable scrambling             | Scrambles the configuration bitstream.                                                                                                                                                                                                                                                   |  |

| More Options                  | Opens the <b>More Security Options</b> dialog box for specifying additional physical security options.                                                                                                                                                                                   |  |

- 5. Generate primary device programing files in the Assembler, as Generating Primary Device Programming Files on page 5 describes.

- 6. Generate a .jic or .rbf secondary programming file, as Generating Secondary Programming Files (Programming File Generator) on page 7 describes:

- a. In the **Programming File Generator**, select the .sof file on the **Input Files** tab.

- b. Click the **Properties** button. The **Input File Properties** dialog box appears.

Figure 13. Input File Properties

- c. Set Finalize encryption to On.

- d. Specify the AES 256-bit or 384-bit **Encryption key file** (.qek) to decrypt the bitstream in the SDM prior to device configuration.

- 7. Click OK.

#### **Related Information**

Input Files Tab Settings (Programming File Generator) on page 58

## 1.4. Enabling Bitstream Encryption or Compression for Intel Arria 10 and Intel Cyclone 10 GX Devices

You can optionally enable bitstream file encryption that requires a user-defined 256-bit security key to access the configuration bitstream. Alternatively, you can enable bitstream compression to reduces the size of your programming file to minimize file transfer and storage requirements. The compression reduces configuration file size by 30% to 55% (depending on the design). File compression and encryption options are mutually exclusive for Intel Arria 10 and Intel Cyclone 10 GX devices.

Follow these steps to enable bitstream file compression or encryption for Intel Arria 10 and Intel Cyclone 10 GX devices:

- 1. Generate a . jic file for flash programming, as this document describes.

- 2. In the Convert Programming File dialog box, select the .sof file under Input files to convert.

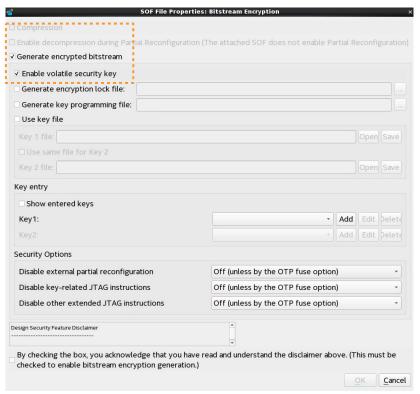

- 3. Click the **Properties** button. The **SOF File Properties: Bitstream Encryption** dialog box appears.

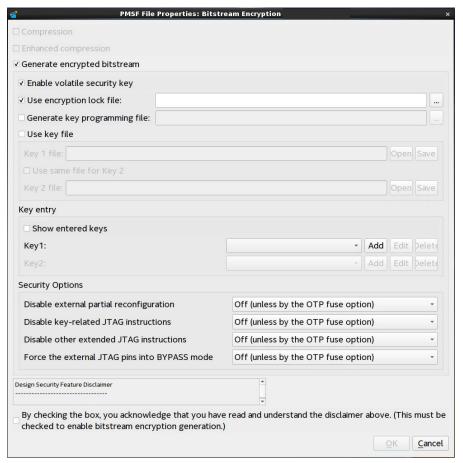

Figure 14. Enabling Bitstream Compression or Encryption (Intel Arria 10 and Intel Cyclone 10 GX Designs)

- 4. To enable compression, turn on the **Compression** option. All encryption options disable as these options are mutually exclusive.

- 5. To enable bitstream file encryption:

- a. Turn off the **Compression** option.

- b. Turn on the **Generate encrypted bitstream** option.

- Specify options for programming file key decryption, and Security Options, as Compression and Encryption Settings (Convert Programming File) on page 61 describes.

- 6. Click OK.

#### **Related Information**

- Intel Arria 10 Core Fabric and General Purpose I/Os Handbook For detailed device security configuration steps.

- Intel Cyclone 10 GX Core Fabric and General Purpose I/Os Handbook For detailed device security configuration steps.

#### 1.5. Generating Programming Files for Partial Reconfiguration

The following sections describe generation of bitstream and other files for partial reconfiguration.

#### 1.5.1. Generating PR Bitstream Files

For Intel Stratix 10 designs, the Assembler generates a configuration .rbf automatically at the end of compilation. For Intel Arria 10 and Intel Cyclone 10 GX designs, use any of the following methods to process the PR bitstreams and generate the Raw Binary File (.rbf) file for reconfiguration.

Note:

The Intel Quartus Prime Pro Edition software supports compilation of PR designs for Intel Agilex devices, but does not yet support Intel Agilex PR bitstream generation.

#### **Generating PR Bitstreams During Compilation**

Follow these steps to generate the .rbf file during compilation:

1. Add the following assignments to the revision .qsf to automatically generate the required PR bitstreams following compilation:

```

set_global_assignment -name GENERATE_PR_RBF_FILE ON set_global_assignment -name ON_CHIP_BITSTREAM_DECOMPRESSION OFF

```

To compile the revision and generate the .rbf, click Processing ➤ Start Compilation.

#### **Generating PR Bitstreams with Programming File Generator**

Follow these steps to generate the .rbf for PR programming with the **Programming File Generator**:

- Click File ➤ Programming File Generator. The Programming File Generator appears.

- 2. Specify the target **Device family** and the **Configuration mode** for partial reconfiguration.

- On the Output File tab, specify the Output directory, file name, and enable the Raw Binary File for Partial Reconfiguration (.rbf) file type.

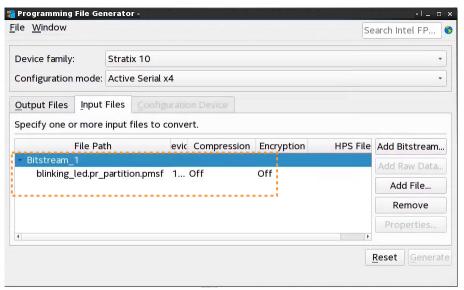

- 4. To add the input .pmsf file to convert, click the **Input Files** tab, click **Add Bitstream**, and specify the .pmsf that you generated in the Assembler.

Figure 15. Adding Bitstream File

- 5. On the **Input Files** tab, select the bitstream .pmsf file and click **Properties**. Specify any of the following options for the .rbf:

- Enable compression—generates compressed PR bitstream files to reduce file size.

- **Enable encryption**—generates encrypted independent bitstreams for base image and PR image. You can encrypt the PR image even if your base image has no encryption. The PR image can have a separate encryption key file (.ekp). You can also specify other **Security settings**.

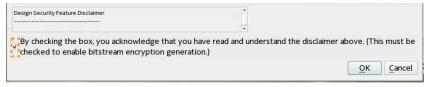

- If you turn on **Enable encryption**, you must also acknowledge the **Design Security Feature Disclaimer** by checking the box.

Figure 16. Design Security Feature Disclaimer

- 6. Click OK.

- 7. In **Programming File Generator**, click **Generate**. The PR bitstream files generate according to your specifications.

#### **Generating PR Bitstreams with Convert Programming Files Dialog Box**

Follow these steps to generate the .rbf with the **Convert Programming Files** dialog box:

- Click File > Convert Programming Files. The Convert Programming Files dialog box appears.

- 2. Specify the output file name and **Programming file type** as **Raw Binary File** for Partial Reconfiguration (.rbf).

- 3. To add the input .pmsf file to convert, click **Add File**.

- 4. Select the newly added .pmsf file, and click **Properties**.

- 5. Enable or disable any of the following options and click **OK**:

- Compression—enables compression on PR bitstream.

- **Enhanced compression**—enables enhanced compression on PR bitstream.

- **Generate encrypted bitstream**—generates encrypted independent bitstreams for base image and PR image. You can encrypt the PR image even if your base image has no encryption. The PR image can have a separate encryption key file (.ekp). If you enable **Generate encrypted bitstream**, enable or disable the **Enable volatile security key**, **Use encryption lock file**, and **Generate key programming file** options.

- 6. Click **Generate**. The PR bitstream files generate according to your specifications.

Figure 17. PMSF File Properties Bitstream Encryption

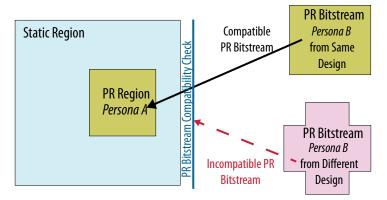

#### 1.5.2. Partial Reconfiguration Bitstream Compatibility Checking

Partial reconfiguration bitstream compatibility checking verifies the compatibility of the reconfiguration bitstream to prevent configuration with an incompatible PR bitstream. The following sections describe PR bitstream compatibility check support.

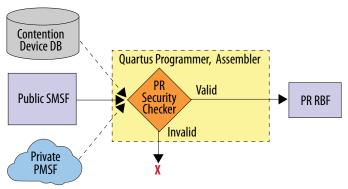

Figure 18. PR Bitstream Compatibility Checking

#### **Intel Stratix 10 and Intel Agilex PR Bitstream Compatibility Checking**

For Intel Stratix 10 and Intel Agilex designs, PR bitstream compatibility checking is automatically enabled in the Compiler and in the Secure Device Manager (SDM) firmware by default. The following limitations apply to PR designs *if PR bitstream compatibility checking is enabled*:

- The firmware allows up to a total of 32 PR regions, irrespective of the number of hierarchical partial reconfiguration layers.

- Your PR design can have up to six hierarchical partial reconfiguration layers.

- Your PR design, when there is no hierarchy, can have up to 32 regions.

- Your PR design can have up to 15 child PR regions of any parent PR region (if it is hierarchical). Child PR regions count towards the total limit of 32 PR regions.

The Compiler generates an error if your PR design exceeds these limits when PR bitstream compatibility checking is enabled.

If you require more PR regions than this limitation allows, or otherwise want to disable PR bitstream compatibility checking , you can add the following assignment to the .gsf file:

```

set_global_assignment -name ENABLE_PR_POF_ID OFF

```

When you set this assignment to off, the limit of 32 total regions does not apply in the Compiler.

Note:

If you require the PR bitstream authentication feature for your design, you must enable PR bitstream compatibility checking by setting the global assignment ENABLE PR POF ID to ON. The default setting is ON.

#### Intel Arria 10 and Intel Cyclone 10 GX PR Bitstream Compatibility Checking

For Intel Arria 10 and Intel Cyclone 10 GX designs, you enable or disable PR bitstream compatibility checking by turning on the **Enable bitstream compatibility check** option when instantiating the Partial Reconfiguration Controller Intel Arria 10/Cyclone 10 FPGA IP from the IP Catalog.

The PR IP verifies the partial reconfiguration PR Bitstream file (.rbf). When you enable the bitstream compatibility check, the PR .pof ID is encoded as the 71st word of the PR bitstream. If the PR IP detects an incompatible bitstream, then the PR IP stops the PR operation, and the status output reports an error.

When you turn on **Enable bitstream compatibility check**, the PR Controller IP core creates a **PR bitstream ID** and displays the bitstream ID in the configuration dialog box. For bitstream compatibility checking with hierarchical PR designs, refer to additional steps in AN 806: Hierarchical Partial Reconfiguration Tutorial for Intel Arria 10 GX FPGA Development Board.

#### **Related Information**

AN 806: Hierarchical Partial Reconfiguration Tutorial for Intel Arria 10 GX FPGA Development Board

### **1.5.3.** Raw Binary Programming File Byte Sequence Transmission Examples

The raw binary programming file (.rbf) file contains the device configuration data in little-endian raw binary format. The following example shows transmitting the .rbf byte sequence 02 1B EE 01 in x32 mode:

#### Table 10. Writing to the PR control block or SDM in x32 mode

In x32 mode, the first byte in the file is the least significant byte of the configuration double word, and the fourth byte is the most significant byte.

| Double Word = 01EE1B02 |            |            |                 |  |

|------------------------|------------|------------|-----------------|--|

| LSB: BYTE0 = 02        | BYTE1 = 1B | BYTE2 = EE | MSB: BYTE3 = 01 |  |

| D[70]                  | D[158]     | D[2316]    | D[3124]         |  |

| 0000 0010              | 0001 1011  | 1110 1110  | 0000 0001       |  |

#### 1.5.4. Generating a Merged .pmsf File from Multiple .pmsf Files

Use a single merged .rbf file to reconfigure two PR regions simultaneously. To merge two or more .pmsf files:

- 1. Open the Convert Programming Files dialog box.

- Specify the output file name and programming file type as Merged Partial-Mask SRAM Object File (.pmsf).

- 3. In the **Input files to convert** dialog box, select **PMSF Data**.

- 4. To add input files, click **Add File**. You must specify two or more files for merging.

- 5. To generate the merged file, click **Generate**.

Alternatively, to merge two or more .pmsf files from the Intel Quartus Prime shell, type the following command:

For example, to merge two .pmsf files, type the following command:

```

quartus_cpf --merge_pmsf=<2> <pmsf_input_file_1> <pmsf_input_file_2> \

<pmsf_output_file>

```

# **1.6.** Generating Programming Files for Intel FPGA Devices with Hard Processor Systems

When generating programming files for Intel FPGA devices with a Hard Processor System (HPS), you must first determine what boot flow you want to use for the device: HPS Boot First or FPGA Configuration First.

Depending on the boot flow that you want to use, follow the instructions in one of the following sections:

- Generating Programming Files for HPS Boot First Boot Flows on page 31

- Generating Programming Files for FPGA Configuration First Boot Flows on page 33

#### 1.6.1. Generating Programming Files for HPS Boot First Boot Flows

In HPS Boot First boot flows, the HPS I/O and EMIF are configured and the HPS is booted before configuring the FPGA I/O and core.

Configuring the HPS I/O for the first time and then loading the HPS FSBL is called "Phase 1 configuration". The subsequent configuration of FPGA I/O and core by HPS is called "Phase 2 configuration".

To generate programming files for HPS Boot First boot flows:

- 1. Generate the primary programming files for your design, as Generating Primary Device Programming Files on page 5 describes.

- 2. Click **File** ➤ **Programming File Generator**.

- 3. For **Device family**, select your target device. The options available in the **Programming File Generator** change dynamically, according to your device and configuration mode selection.

- For Configuration mode, select an Active Serial mode that your device supports. Configuration Modes (Programming File Generator) on page 10 describes all modes.

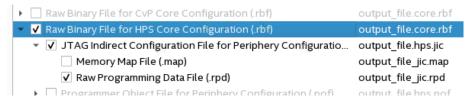

- 5. On the **Output Files** tab, select **Raw Binary File for HPS Core Configuration** (.rbf), then select the following files: