# CYBL10x7x, CY8C4128\_BL, CY8C4248\_BL (256K), CY8C4246\_L, CY8C4247\_L, CY8C4248\_L

# **Programming Specifications**

Document No. 001-96666 Rev. \*C

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2015-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW. CYPRESS MAKES NO WARRANTY OF ANY KIND. EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO. THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR-POSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities. including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1. Introduc         | tion                                        |    |

|---------------------|---------------------------------------------|----|

| 1.                  | 1 Programmer                                | 4  |

| 1.                  | 2 Introduction to CYBL10x7x                 |    |

| 2. Required         | l Data                                      | 6  |

| 2.                  | 1 Hex File Origin                           | 6  |

| 2.                  | •                                           |    |

| 2.                  | •                                           |    |

| 3. Commun           | nication Interface                          | 9  |

| 3.                  | 1 The Protocol Stack                        | 9  |

| 3.                  | 2 SWD Interface                             | 9  |

| 3.                  | 3 Hardware Access Commands                  | 10 |

| 3.                  | 4 Pseudocode                                | 11 |

| 3.                  | 5 Physical Layer                            | 12 |

| 4. Program          | ming Algorithm                              | 14 |

| 4.                  | 1 High-Level Programming Flow               | 14 |

| 4.                  |                                             |    |

| 4.                  | 3 Step 1 – Acquire Chip                     | 17 |

| 4.                  |                                             |    |

| 4.                  | 5 Step 3 – Erase All Flash                  | 21 |

| 4.                  | 6 Step 4 – Checksum Privileged              | 22 |

| 4.                  | 7 Step 5 – Program Flash                    | 23 |

| 4.                  | 8 Step 6 – Verify Flash                     | 25 |

| 4.                  | 9 Step 7 – Program Protection Settings      | 26 |

| 4.                  | 10 Step 8 – Verify Protection Settings      | 29 |

| 4.                  | 11 Step 9 – Verify Checksum                 | 31 |

| 4.                  | 12 Step 10 - Program User SFlash (optional) | 32 |

| Chip-Level P        | rotection                                   | 36 |

| Intel Hex File      | Format                                      | 38 |

|                     | ebug (SWD) Protocol                         |    |

| <b>Timing Speci</b> | fications of the SWD Interface              | 41 |

# 1. Introduction

This programming specifications document gives the information necessary to program the nonvolatile memory of the PSoC 4 BLE 256K and PSoC 4200-L devices. This specification describes the communication protocol required for access by an external programmer, explains the programming algorithm, and gives the electrical specifications of the physical connection. The programming algorithms described in the following sections are compatible for all devices mentioned in the title. The document will use "Target" as the generic reference to all families mentioned in the title.

#### 1.1 Programmer

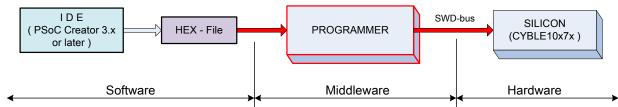

A programmer is a hardware-software system that stores a binary program (hex file) in the device's program (flash) memory. The programmer is an essential component of the engineer's prototyping environment or an integral element of the manufacturing environment (mass programming). Figure 1-1 illustrates a high-level view of the development environment.

Figure 1-1. Programmer in Development Environment

In the manufacturing environment, the integrated development environment (IDE) block is absent because its main purpose is to produce a hex file. As shown in Figure 1-1, the programmer performs three functions:

- Parses the hex file and extracts the necessary information

- Interfaces with the silicon as a serial wire debug (SWD) master

- Implements the programming algorithm by translating the hex data into SWD signals

The structure of the programmer depends on its exploiting requirements. It can be software- or firmware-centric.

In a software-centric structure, the programmer's hardware works as a bridge between the protocol (such as USB) and SWD. An external device (software) passes all SWD commands to the hardware through the protocol. The bridge is not involved in parsing the hex file and programming algorithm. This is the task of the upper layer (software). Examples of such programmers are the Cypress MiniProg3 and TrueTouchBridge.

A firmware-centric structure is an independent hardware design in which all the functions of the programmer are implemented in one device, including storage for the hex file. Its main purpose is to act as a mass programmer in manufacturing.

This document does not include the specific implementation of the programmer. It focuses on data flow, algorithms, and physical interfacing. Specifically, it covers the following topics, which correspond to the three functions of the programmer:

- Data to be programmed

- Interface with the chip

- Algorithm used to program the target device

### 1.2 Target Family Overview

The target family is based on the ARM Cortex-M0 processor core (48 MHz). This device family leverages the ARM debug interface for programming and debugging operations. It supports only SWD programming protocols; it does not support the JTAG interface.

The nonvolatile subsystem of the silicon consists of a flash memory system with a maximum of up to 256 KB. The flash memory system stores the user's program and silicon's protection information.

The part can be programmed after it is installed in the system by way of the SWD interface (in-system programming).

The programming frequency ranges from 1.5 MHz to 14.0 MHz.

This document focuses on the specific programming operations without referencing the silicon architecture. Many important topics are detailed in the appendices. Other device-specific information can be found in the PSoC4 BLE 256K datasheet (001-94624) and the PSoC 4200-L datasheet (001-91686).

This document includes four appendices:

- Appendix A: Chip-Level Protection

- Appendix B. Intel Hex File Format

- Appendix C: Serial Wire Debug Protocol

- Appendix D: Timing Specifications of the SWD Interface

### **Document Revision History**

**Document Title:** CYBL10x7x, CY8C4128\_BL, CY8C4248\_BL (256K), CY8C4246\_L, CY8C4247\_L, CY8C4248\_L Programming Specifications

**Document Number: 001-96666**

| Revision | Issue Date | Origin of<br>Change | Description of Change                                                             |

|----------|------------|---------------------|-----------------------------------------------------------------------------------|

| **       | 03/12/2015 | ANDI                | New specification                                                                 |

| *A       | 05/19/2015 | ANDI                | Added support for PSoC 4200-L family devices.                                     |

|          | 03/19/2013 | ANDI                | Added "Target" as a generic reference to all families mentioned in this document. |

| *B       | 08/30/2016 | STPP                | Removed "SROM_CMD_SET_IMO_48_MHz" from the Table 4.1.                             |

|          | 06/30/2010 | SIFF                | Removed IMO setting for 48 MHz from "Pseudocode - Step1. Acquire Chip".           |

| *C       | 05/03/2017 | AESATMP8            | Updated logo and Copyright.                                                       |

# 2. Required Data

This chapter describes the information that the programmer must extract from the hex file to program the Target silicon.

### 2.1 Hex File Origin

Customers will use PSoC Creator to develop their projects. After development is completed, the nonvolatile configuration of the silicon is saved in the file. Only three records in this file actually target the flash memory:

- User's program (code)

- Flash row-level protection

- Chip-level protection

Other records are auxiliary and are used to keep the integrity of the programming flow.

## 2.2 Nonvolatile Subsystem

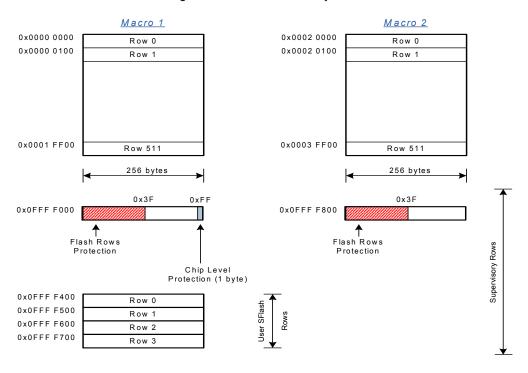

The flash memo is organized into two macros of 128 KB each. There are 512 rows in the macro, each consisting of 256 bytes. The programming granularity is one row at a time.

In addition to the users' rows, the flash macros contain supervisory rows, which store:

- Row-level protection bits

- Chip-level protection byte (only in macro 1)

- Application-specific Information (up to four rows and only in macro 1) User Supervisory Flash (SFlash)

Figure 2-1. Nonvolatile Subsystem

User SFlash rows can be used by the application to store arbitrary data. However, the primary intent is to store the Unique Bluetooth Address of the device. Since these rows are not part of the hex file, their programming is optional. During mass production, a vendor should define the process to guarantee for each device the uniqueness of the programmed Bluetooth address.

For the User Flash, the maximum number of rows is taken into account during programming and it depends only on the part's flash size. The formulae are as follows:

$$L=256$$

- row size in bytes

$$N=\frac{FlashSize}{L}$$

- total number of rows

$$K=\left\lfloor \frac{N}{512} \right\rfloor$$

- total number of macros

The flash memory is mapped directly to the CPU's address space starting from 0x00000000. Therefore, the firmware or external programmer can read its content directly from the given address.

The flash row-level protection is a feature to write-protect the user's flash with a granularity of one row. The flash rowlevel protection settings prevent rows from being written but do not prevent a row's data from being read.

Each user's row in the macro is associated with one protection bit. For this reason, the maximum number of protection

bits for each macro is 512. The corresponding number of bytes per macro is calculated as follows:

$$ProtectionSize = \frac{512}{8} = 64$$

- bytes per macro.

A bit value of 0 means that the row is unprotected and a value of 1 means the row is protected.

The last type of nonvolatile information in flash is chip-level protection. This consists of one byte that restricts access to the chip's resources (register, SRAM, and flash) by an external programmer or debugger. For example, in PROTECTED mode, the programmer cannot read or write either flash or SRAM; in KILL mode, the SWD interface is locked in silicon and the chip cannot be reprogrammed. The chip-level protection setting is programmed along with the flash row-level protection into the supervisory row of the "macro" (see Figure 2-1 on page 7). Its offset in the supervisory row is 0x7F. For more information about chip-level protection, see Appendix A: Chip-Level Protection on page 36.

# 2.3 Organization of the Hex File

The hexadecimal (hex) file is a medium to describe the non-volatile configuration of the project. It is the data source for the programmer.

The hex file for the Target family follows the Intel Hex File format. Intel's specification is very generic and defines only some types of records that can make up the hex file. The

specification allows customizing the format for any possible silicon architecture. The silicon vendor defines the functional meaning of the records, which typically varies for different chip families. See Appendix B: Intel Hex File Format on page 38 for details of the Intel Hex File format.

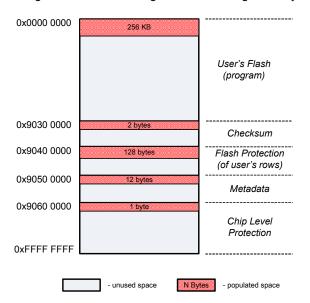

The Target family defines five types of data sections in the hex file: user flash, checksum, flash protection, metadata, and chip-level protection. See Figure 2-2 to determine the allocation of these sections in the address space of the Intel hex file.

The address space of the hex file does not map to the physical addresses of the CPU (other than the user's flash, which is an unintentional coincidence). The programmer uses hex addresses (see Figure 2-2) to read sections from the hex file into its local buffer. Later, this data is programmed (translated) into the corresponding addresses of the silicon.

Figure 2-2. Hex File Organization for Target Family

**0x0000 0000 – User's Flash** (256 KB): This is the user's program (code) that must be programmed. The size of this section matches the flash size of the target part. The programmer can either read all of this section at once or gradually by 256-byte blocks. The programming of the flash is carried out on the row on the basis of 128 bytes for each request.

**0x9030 0000 – Checksum** (2 bytes): This is the checksum of the entire user flash section—the arithmetical sum of every byte in the user's flash. Only two least significant bytes (LSB) of the result are saved in this section, in bigendian format (most significant byte (MSB) first). This must be used by the programmer to check the integrity of the hex file and to verify the quality of the programming. In this context, "integrity" means that the checksum and user's flash

sections must be correlated in this file. At the end of programming, the checksum of flash (two LSBs) is compared to the checksum from the hex file.

**0x9040 0000 – Flash Protection** (128 bytes): This data is programmed into supervisory rows of the flash macros (see Figure 2-1 on page 7). Every bit defines the write-protection setting for the corresponding user row. The number of bytes to be read from this section depends on the flash size.

Protection Size = Flash Size / Row Size / 8

Therefore, for a 256-KB part, flash protection consists of 128 bytes.

**0x9060 0000 – Chip-level Protection** (1 byte): This section represents chip-level protection of the programmed part (see Figure 2-1 on page 7). For more information, see Appendix A: Chip-Level Protection on page 36.

**0x9050 0000 – Metadata** (12 bytes): This section contains data that is not programmed into the target device. Instead, it is used to check data integrity of the hex file and the silicon ID of the target device. Table 2-1 lists the fields in this section.

Table 2-1. Meta Data in Hex File

| Offset | Data Type        | Length in Bytes |

|--------|------------------|-----------------|

| 0x00   | Hex file version | 2 (big-endian)  |

| 0x02   | Silicon ID       | 4 (big-endian)  |

| 0x06   | Reserved         | 1               |

| 0x07   | Reserved         | 1               |

| 0x08   | Internal use     | 4               |

- Hex file version: This 2-byte field in Cypress's hex file defines its version (or type). The version for the Target family is "2". The programmer should use this field to make sure this file corresponds to the Target device, or to select the appropriate parsing algorithm if the file supports several families.

- Silicon ID: This 4-byte field represents the ID of the target silicon. During programming, the ID of the acquired device is compared with the content of this field. To start programming, these fields must match. Cypress does not guarantee reliable programming (or data retention) if third-party programmers ignore this condition.

- Reserved: Not used by the Target family.

- Internal Use: This 4-byte field is used internally by the PSoC Programmer software. Because it is not related to actual programming, this field should be ignored by third-party vendors.

# 3. Communication Interface

This chapter explains the low-level details of the communication interface.

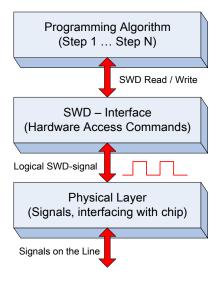

#### 3.1 The Protocol Stack

Figure 3-1 illustrates the stack of protocols involved in the programming process. The programmer must implement both hardware and software components.

Figure 3-1. Programmer's Protocol Stack

The Programming Algorithm protocol, the topmost protocol, implements the whole programming flow in terms of atomic SWD commands. It is the most solid and fundamental part of this specification. For more information on this algorithm, see Chapter 4: Programming Algorithm on page 14.

The SWD Interface and physical layer are the lower layer protocols. Note that the physical layer is the complete hardware specification of the signals and interfacing pins, and includes drive modes, voltage levels, resistance, and other components. Upper protocols are logical and algorithmic levels.

The purpose of the SWD interface layer is to act as a bridge between pure software and hardware implementations. The Programming Algorithm protocol is implemented completely in software; its smallest building block is the SWD command. The whole programming algorithm is the meaningful flow of these blocks. The SWD interface helps to isolate the programming algorithm from hardware specifics, which makes the algorithm reusable. The SWD interface must transform the software representation of these commands into line signals (digital form).

#### 3.2 SWD Interface

The SWD interface uses the SWD protocol developed by ARM. The Target silicon integrates the standard Cortex-M0 debug access port (DAP) block provided by ARM. Therefore, it complies with the ARM specification *ARM Debug Interface v5. Architecture Specification*. The CYBKE10x6x silicon does not support the JTAG interface.

Figure 3-2 on page 10 shows the top-level architecture of the silicon. It includes the debug interface, CPU subsystem, memory, and periphery. The standard ARM modules are outlined in red. The following acronyms are used in this figure:

- HSIOM High-speed I/O matrix

- DAP Debug access port

- AHB Advanced high-performance bus

- SPC System performance controller

SWDCK

SWDIO

ARM's subsystem

Cortex M0 DAP

SWD

Debug Port (DP)

AP Access

AHB

AHB

AHB

AHB

Peripheral Modules

Figure 3-2. Top-Level Silicon Architecture

The SWD interface (ARM) defines only two digital pins to communicate with an external programmer or a debugger. The SWDCK and SWDIO pins are sufficient for bidirectional, semi-duplex data exchange.

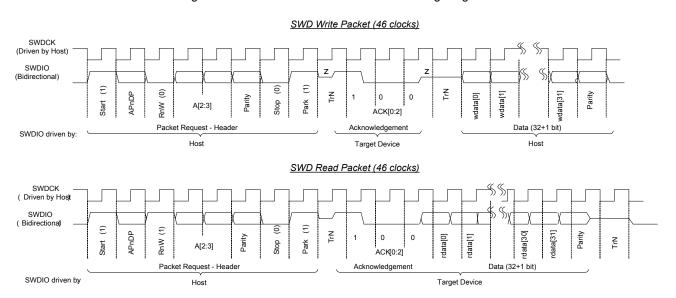

Only three types of SWD commands can appear on the bus: Read, Write, and Line Reset. The Line Reset command is used only once during programming to establish a connection with the device. The Read and Write commands compose the rest of the programming flow.

The programmer can access most resources of the silicon through the SWD interface. All programming algorithms are stored in SROM; the external programmer uses its system APIs to program the flash. During programming of the flash row, the system code is executed from the SROM. It communicates with the SPC module, which "knows" how to program flash. In contrast to a write operation, reading from flash is an immediate operation that is carried out directly from the necessary address (see Figure 2-1 on page 7 for address space). Reading works on a word basis (4-byte); writing works on a row basis (256-byte).

The typical operation of the programmer is to load all necessary parameters into the SRAM (I/O registers) and request a system call from the SROM. Only the SWD Read and Write commands perform this task.

# 3.3 Hardware Access Commands

The Cortex-M0 DAP module, shown in Figure 3-2, supports three types of transactions: Read, Write, and Line Reset. All are defined in the ARM specification. The APIs must be implemented by the SWD Interface layer shown in Figure 3-1 on page 9. In addition, the upper protocol, Programming Algorithm, requires two extra commands to manipulate the hardware: Power(state) and ToggleReset(). Table 3-1 lists the hardware access commands used by the software layer.

Table 3-1. Hardware Access Commands

| Command       | Parameters                                            | Description                                                                                                                                                                                                                                                                                                                                       |

|---------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWD_LineReset |                                                       | Standard ARM command to reset the debug port (DAP). It consists of at least 50 clock cycles with data = 1, that is, with the SWDIO asserted HIGH by the programmer. Transaction must be completed at least by 1 clock with SWDIO asserted LOW. This sequence synchronizes the programmer and chip; it is a first transaction in programming flow. |

| SWD_Write     | IN APnDP, IN addr, IN data32,<br>OUT ack              | Sends a 32-bit data to the specified register of the DAP. The register is defined by the "APnDP" (1 bit) and "addr" (2 bits) parameters. The DAP returns a 3-bit status in "ack".                                                                                                                                                                 |

| SWD_Read      | IN APnDP, IN addr,<br>OUT data32, OUT ack, OUT parity | Reads a 32-bit data from the specified register of the DAP. The register is defined by the "APnDP" (1 bit) and "addr" (2 bits) parameters. DAP returns a 32-bit data, status, and parity (control) bit of the read 32-bit word.                                                                                                                   |

| ToggleReset   |                                                       | Generates the reset signal for target device. The programmer must have a dedicated pin connected to the XRES pin of the target device.                                                                                                                                                                                                            |

| Power         | IN state                                              | If the programmer powers the target device, it must have this function to supply power to the device.                                                                                                                                                                                                                                             |

For information on the structure of the SWD read and write packets and their waveform on the bus, see Appendix C: Serial Wire Debug (SWD) Protocol on page 39.

The SWD\_Read and SWD\_Write commands allow accessing registers of the Cortex-M0 DAP module from Figure 3-2 on page 10. The DAP functionally is split into two control units:

- Debug Port (DP) Is responsible for the physical connection to the programmer or debugger.

- Access Port (AP) Provides the interface between the DAP module and one or more debug components (such as the Cortex-M0 CPU).

The external programmer can access the registers of these access ports using the following bits in the SWD packet:

- APnDP Select access port (0 DP, 1 AP).

- ADDR 2-bit field addressing a register in the selected access port

The SWD\_Read and SWD\_Write commands are used to access these registers. They are the smallest transactions that can appear on the SWD bus. Table 3-2 shows the DAP registers that are used during programming.

Table 3-2. DAP Registers (in ARM notation)

| Register  | APnDP (1 bit) | Address (2-bit) | Access (R/W) | Full Name                          |

|-----------|---------------|-----------------|--------------|------------------------------------|

| IDCODE    | 0             | 2'b00           | R            | Identification Code Register       |

| CTRL/STAT | 0             | 2'b01           | R/W          | Control/Status Register            |

| SELECT    | 0             | 2'b10           | w            | AP Select Register                 |

| CSW       | 1             | 2'b00           | R/W          | Control Status/Word Register (CSW) |

| TAR       | 1             | 2'b01           | R/W          | Transfer Address Register          |

| DRW       | 1             | 2'b11           | R/W          | Data Read/Write Register           |

For more information about these registers, see the ARM Debug Interface v5. Architecture Specification.

#### 3.4 Pseudocode

This document uses easy-to-read pseudocode to show the programming algorithm. The following two commands are used for the programming script:

```

Write_DAP ( Register, Data32)

Read DAP ( Register, OUT Data32)

```

Where the Register parameter is an AP/DP register defined by APnDP and address bits (see Table 3-2). The pseudocommands correspond to read or write SWD transactions. Following are some examples:

```

Write_DAP( TAR, 0x20000000)

Write_DAP( DRW, 0x12345678)

Read DAP ( IDCODE, OUT swd id)

```

The Register parameter technically can be represented as the structure in C:

```

struct DAP_Register

{

BYTE APnDP; // 1-bit field

BYTE Addr; // 2-bit field

};

```

#### Then, DAP registers will be defined as:

The defined Write and Read pseudocommands must be successful if both return the ACK status of the SWD transaction. For the Read transaction, the parity bit must be taken into account (corresponds to read data32 value). If the status of the trans-

action, the parity bit, or both is incorrect, the transaction must be considered to have failed. In this case, depending on the programming context, programming must terminate or the transaction must be tried again.

The implementation of Write and Read pseudocommands based on the hardware access commands SWD\_Read and SWD\_Write (Table 3-1 on page 10) is as follows.

```

SWD_Status Write_DAP ( Register, data32 ) {

SWD_Write ( Register.APnDP, Register.Addr, data32, OUT ack);

Return ack;

}

SWD_Status Read_DAP ( Register, OUT data32) {

SWD_Read ( Register.APnDP, Register.Addr, OUT data32, OUT ack, OUT parity);

If (ack == 3'b001) { //ACK, then check also the parity bit

Parity_data32 = 0x00;

For (i=0; i<32; i++) Parity_data32 ^= ((data32 >> i) & 0x01);

If (Parity_data32 != parity) ack = 3'b111; //NACK

}

Return ack;

}

```

The programming code in Chapter 4: Programming Algorithm on page 14 is based mostly on the Write and Read pseudo-commands and some commands in Table 3-1 on page 10.

### 3.5 Physical Layer

This section describes the hardware connections between the programmer and the target device for programming. It shows the connection schematic and gives information on electrical specifications. Check the device datasheet for the actual location of SWD/Power pins on the part's package.

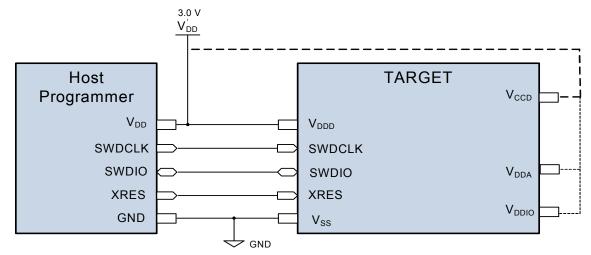

Check the device datasheet for the actual location of SWD/Power pins on the part's package. The generic connection between the target and programmer is shown in Figure 3-3.

Figure 3-3. Connection Schematic of Programmer

Only five pins are required to communicate with the chip. Note that the SWDCLK and SWDIO pins are only required by the SWD protocol. The silicon requires an additional XRES pin that is not related to the ARM standard. It is used to reset the part as a first step in a programming flow.

You can program a chip in either Reset or Power Cycle mode. The mode defines only the first step—how to reset the part—in the programming flow. The rest of the steps are identical (SWD traffic).

- Reset mode: To start programming, the host toggles the XRES line and then sends SWD commands (see Table 3-1 on page 10). The power on the target board can be supplied by the host or by an external power adapter (the V<sub>DD</sub> line can be optional).

- Power Cycle mode: To start programming, the host powers on the target and then starts sending the SWD commands. The XRES line is not used.

It is recommended that the programmer uses all five pins and supports at least Reset mode programming. The Power Cycle mode support is optional.

Table 3-3. Programming Mode

| Mode        | Necessary Pins                                   | Unused Pins                       | Use Cases                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset       | V <sub>DD</sub> (optional) GND XRES SWDCLK SWDIO | V <sub>DD</sub> (if self-powered) | The board can be self-powered ( $V_{DD}$ is not needed). The board consumes too much current, which the programmer cannot supply ( $V_{DD}$ is not needed). The 5-pin case: The host supplies power and toggles XRES (this is the most popular programming method).                                                                                                                               |

| Power Cycle | V <sub>DD</sub><br>GND<br>SWDCLK<br>SWDIO        | XRES                              | The only use case: The XRES pin is not available on the part's package, so Power Cycle mode is the only way to reset a part.  This is not applicable to the CYBL10x7x family, in which every package has an XRES pin. For this reason, Reset is the recommended mode.  Some third-party SWD masters can use this mode if they do not implement the XRES line but can supply power (power on/off). |

Table 3-4. Target Pin Names and Requirements

| Target Pin Name | Function                                        | External Programmer Drive Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| $V_{DDD}$       | Digital power supply<br>Input<br>(1.71 V–5.5 V) | Positive voltage – powered by external power supply or by programmer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V <sub>SS</sub> | Power supply return                             | Low resistance ground connection. Connect to circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| XRES            | External active low reset input.                | Output: Drive CMOS levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SWDCLK          | SWD clock input<br>(1.5 MHz–14 MHz)             | Output: Drive CMOS levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SWDIO           | SWD data line - bidirectional                   | Output: Drive CMOS levels Input: Read CMOS levels in HI-Z mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| $V_{DDA}$       | Analog power supply input (1.71 V–5.5 V)        | Depending on the board configuration, this power can be supplied from a $V_{DDD}$ source, which must be in the range 1.9 V–5.5 V. If it is lower, then a separate voltage source is required for analog circuits. Depending on the board's configuration, this power can be supplied from a $V_{DDD}$ source or own analog power supply. Check the silicon's datasheet for exact power pins configuration. For example, for the BLE family $V_{DDA}$ can be powered from $V_{DDD}$ if it is in range of 1.9 V–5.5 V (if $V_{DDD}$ is lower, then own $V_{DDA}$ source is required). |  |  |

| VDDIO           | I/O pins power supply                           | Available only for PSoC 4200-L series. Typically connected to V <sub>DDD</sub> (application-specific).                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

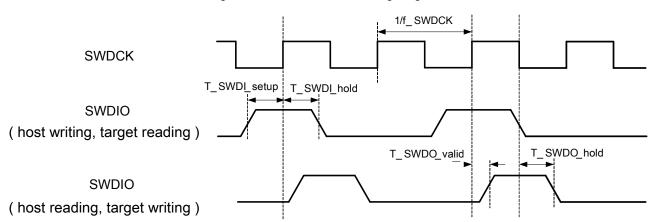

The SWD timing specifications are described in the datasheet (001-94624 or 001-91686).

.

# 4. Programming Algorithm

This chapter describes in detail the programming flow of the Target device. It starts with a high-level description of the algorithm and then describes every step using pseudocode. All code is based on upper-level subroutines composed of atomic SWD instructions (see "Pseudocode" on page 11). These subroutines are defined in "Subroutines Used in the Programming Flow" on page 15. The ToggleReset() and Power() commands are also used (see Table 3-1 on page 10).

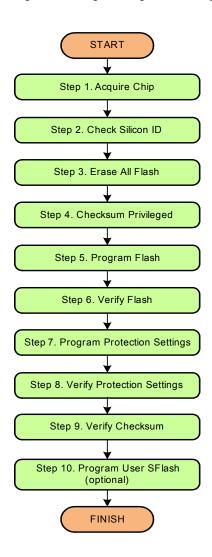

# 4.1 High-Level Programming Flow

Figure 4-1 shows the sequence of steps that must be executed to program the Target device. These steps are described in detail in the following sections. All the steps in this programming flow must be completed successfully for a successful programming operation. The programmer should stop the programming flow if any step fails. In addition, in pseudocode, it is assumed that the programmer checks the status of each SWD transaction (Write\_DAP, Read\_DAP, WriteIO, ReadIO). This extra code is not shown in the programming script. If any of these transactions fails, then programming must be aborted.

Flash programming in the Target family is implemented using the SROM APIs. The external programmer puts the parameters into the SRAM (or registers) and requests system calls, which in turn perform flash updates.

Figure 4-1. High-Level Programming Flow of Target Device

# 4.2 Subroutines Used in the Programming Flow

The programming flow includes some operations that are used in all steps. Eventually, the programming code will look compact and easy to read and understand. Besides that, most of the registers and frequently used constants are named and referred from the pseudocode.

Table 4-1. Constants Used in the Programming Script

| Constant Name             | Value      | Description                                                                                                                                    |

|---------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Space of CPU      |            |                                                                                                                                                |

| CPUSS_SYSREQ              | 0x40100004 | System request register used to make system requests to SROM code; system requests transition from User mode to Privileged mode                |

| CPUSS_SYSARG              | 0x40100008 | System request argument register used to make system requests to SROM code                                                                     |

| TEST_MODE                 | 0x40030014 | Test mode control register used to enter the chip into Programming mode (Test mode)                                                            |

| SRAM_PARAMS_BASE          | 0x20000100 | SRAM address where the parameters for SROM requests will be stored.                                                                            |

| SFLASH_MACRO_0            | 0x0FFFF000 | Location of the flash protection settings in the flash macro 0.                                                                                |

| SFLASH_MACRO_1            | 0x0FFFF800 | Location of the flash protection settings in the flash macro 1.                                                                                |

| SFLASH_CPUSS_PROTECTION   | 0x0FFFF0FC | Location of chip-level protection in the flash macro (actual byte located at 0x0FFFF0CF, but must read whole 32-bit word).                     |

| SROM Constants            |            |                                                                                                                                                |

| SROM_KEY1                 | 0xB6       | Parameter of SROM call                                                                                                                         |

| SROM_KEY2                 | 0xD3       | Parameter of SROM call                                                                                                                         |

| SROM_SYSREQ_BIT           | 0x80000000 | Mask of SYSREQ bit in CPUSS_SYSREQ register, which starts the execution of the SROM command                                                    |

| SROM_PRIVILEGED_BIT       | 0x10000000 | Mask of PRIVILEGED bit in CPUSS_SYSREQ register, which indicates whether the system is in Privileged mode (SROM command running) or User mode. |

| SROM_STATUS_SUCCEEDED     | 0xA0000000 | Successful status of the system request (SROM command).                                                                                        |

| SROM_STATUS_FAILED        | 0xF0000000 | Fail status of the system request (SROM command).                                                                                              |

| SROM Requests             |            |                                                                                                                                                |

| SROM_CMD_GET_SILICON_ID   | 0x00       | Reads the silicon ID of the target device.                                                                                                     |

| SROM_CMD_LOAD_LATCH       | 0x04       | Loads data into the volatile buffer (before writing into flash).                                                                               |

| SROM_CMD_PROGRAM_ROW      | 0x06       | Programs data into the flash row (from the volatile buffer).                                                                                   |

| SROM_CMD_ERASE_ALL        | 0x0A       | Erases all the user's flash and flash protection settings from the supervisory rows                                                            |

| SROM_CMD_CHECKSUM         | 0x0B       | Verifies the checksums of all flash contents (user and privileged rows)                                                                        |

| SROM_CMD_WRITE_PROTECTION | 0x0D       | Writes flash protection and chip-level protection                                                                                              |

| SROM_CMD_WRITE_SFLASH_ROW | 0x18       | Writes User SFlash Row. Valid row range is [03].                                                                                               |

| Chip -Level Protection    |            |                                                                                                                                                |

| CHIP_PROT_VIRGIN          | 0x00       | VIRGIN mode, used by Cypress only.                                                                                                             |

| CHIP_PROT_OPEN            | 0x01       | OPEN mode in which the chip is shipped to customers                                                                                            |

| CHIP_PROT_PROTECTED       | 0x02       | PROTECTED mode, which can be set by the customer                                                                                               |

| CHIP_PROT_KILL            | 0x04       | KILL mode, which can be set by the customer (irreversible)                                                                                     |

|                           |            |                                                                                                                                                |

Table 4-2. Subroutines Used in Programming Flow

| Subroutine                        | Description                                                                                                                                                                                                                                        |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| bool WritelO( addr32, data32 )    | Writes a 32-bit data into the specified address of the CPU address space.  Returns "true" if all SWD transactions succeeded (ACKed).                                                                                                               |  |  |

| bool ReadIO( addr32, OUT data 32) | Reads a 32-bit data from the specified address of the CPU address space. Note that the actual size of the read data (8, 16, 32 bits) depends on the setting in the CSW register of DAP (see Table 3-2). By default, all accesses are 32 bits long. |  |  |

|                                   | Returns "true" if all SWD transactions succeeded (ACKed).                                                                                                                                                                                          |  |  |

| bool PollSROMStatus()             | Waits until the SROM command is completed and then checks its status. Timeout is 1 second. Returns "true" (success) if the command is completed and its status is successful; otherwise, returns "false".                                          |  |  |

The implementation of these subroutines follows. It is based on the pseudocode and registers defined in "Hardware Access Commands" on page 10 and "Pseudocode" on page 11. It uses the constants defined in this chapter.

The pseudocode is similar to C-style notation.

```

// WriteIO Subroutine

bool "WriteIO" ( addr32, data32 )

ack1 = Write_DAP (TAR, addr32);

ack2 = Write_DAP (DRW, data32);

return (ack1 == 3'b001) && (ack2 == 3b'001);

// "ReadIO" Subroutine

bool ReadIO ( addr32, OUT data32 )

{

ack1 = Write DAP (TAR, addr32);

ack2 = Read DAP (DRW, OUT data32);

ack3 = Read DAP (DRW, OUT data32);

return (ack1 == 3'b001) && (ack2 == 3b'001) && (ack3 == 3b'001);

// "PollSROMStatus" Subroutine

bool PollSROMStatus()

{

do{

ReadIO (CPUSS SYSREQ, OUT status);

Status &= (SROM_SYSREQ_BIT | SROM_PRIVILEGED_BIT);

}while ((status != 0) && (time_elapsed < 1 sec));</pre>

if (time elapsed >= 1 sec ) return false; // timeout

ReadIO (CPUSS SYSARG, OUT statusCode);

if ((statusCode & 0xF0000000) != (SROM STATUS SUCCEEDED));

return false; // SROM command failed

else

return true; // SROM command succeeded

}

```

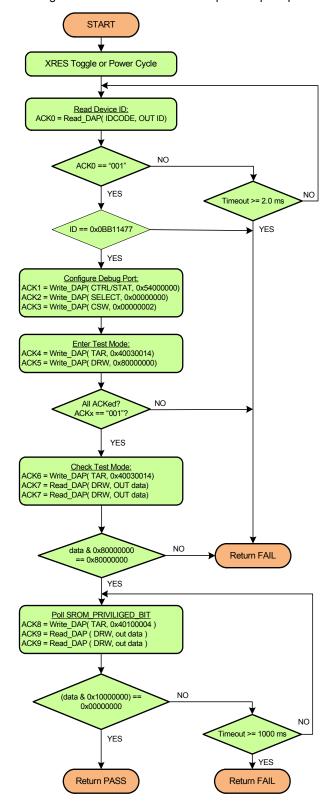

### 4.3 Step 1 – Acquire Chip

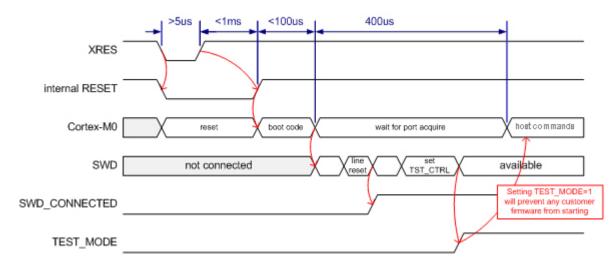

The first step in programming the Target device is to enter it into Test mode (or Programming mode). This is a special mode in which the CPU is controlled by the external programmer, which also can access other system resources such as SRAM and registers. This step has strict timing requirements that the host must meet to enter Test mode successfully. Figure 4-2 shows the timing diagram of entering Test mode.

Figure 4-2. Timing Diagram of Entering Test Mode

This diagram details the chip's internal signals while entering Test mode. Everything starts from toggling the XRES line (or applying power), so the chip enters Internal Reset mode. After that, the system boot code starts execution from the SROM. When completed, the CPU waits during a 400- $\mu$ s time frame for a special connection sequence on the SWD port. If, during this time, the host sends the correct sequence of SWD commands, the CPU enters Test mode. Otherwise, it starts the execution of the user's code.

The times of internal reset (<1 ms) and boot code (<100  $\mu$ s) are not specified exactly. Because they depend on the CPU clock and the size of the code, they can vary in different revisions of the chip.

In this case, the recommended way to enter Test mode is to start sending an acquire sequence right after XRES is toggled (or power is supplied in Power Cycle mode). This sequence is sent iteratively until it succeeds; that is, all SWD transactions are ACKed and all conditions are met. Figure 4-3 on page 18 shows the implementation of the Acquire Chip procedure. It is detailed in terms of the SWD transaction. Note that the recommended minimum frequency of the programmer is 1.5 MHz, which meets the timing requirement of this step (400 µs).

Figure 4-3. Flow Chart of the Acquire Chip Step

#### Pseudocode - Step 1. Acquire Chip

```

______

// Reset Target depending on acquire mode - Reset or Power Cycle

If (AcquireMode == "Reset") ToggleXRES(); // Toggle XRES pin, target must be powered.

Else If (AcquireMode == "Power Cycle") PowerOn();// Supply power to target.

//Execute ARM's connection sequence - acquire SWD-port.

Do

{

SWD LineReset();

ack = Read DAP ( IDCODE, out ID);

While ((ack != 3b'001) && time elapsed < 1.5 ms); //for PowerCycle timeout must be

//longer. For example ~30 ms.

If (time elapsed >= 1.5 ms) Return FAIL;

If (ID != 0x0BB11477) Return FAIL; //SWD ID of Cortex-M0 CPU.

//Initialize Debug Port

Write_DAP (CTRL/STAT, 0x54000000);

Write DAP (SELECT, 0x00000000);

Write DAP (CSW, 0x00000002);

//Enter CPU into Test Mode

WriteIO (TEST MODE, 0x80000000); //Set test mode bit in TEST MODE reg from CPU space

ReadIO (TEST MODE, out status);

if ((status & 0x80000000) != 0x80000000) Return FAIL;

//Poll SROM PRIVILEGED BIT in CPUSS SYSREQ register

{

ReadIO (CPUSS SYSREQ, out status);

status &= SROM PRIVILEGED BIT;

} While ((status != 0x00000000) && time_elapsed < 1000 ms)</pre>

If (time elapsed >= 1000 ms) Return FAIL;

Return PASS;

```

### 4.4 Step 2 - Check Silicon ID

This step is required to verify that the acquired device corresponds to the hex file. It reads the ID from the hex file and compares it with the ID obtained from the target.

#### Pseudocode – Step 2. Check Silicon ID

```

//-----

// Read "Silicon ID" from hex file, 4 bytes from address 0 \times 9050 0002 (big endian).

// HEX ReadSiliconID() must be implemented.

HexID = HEX ReadSiliconID();

// Read "Silicon ID" from the target using SROM request

Params = (SROM KEY1 << 0) +

//KEY1

((SROM_KEY2+SROM_CMD_GET_SILICON_ID) << 8); //KEY2

WriteIO (CPUSS SYSARG, Params); // Write parameters

WriteIO (CPUSS_SYSREQ, SROM_SYSREQ_BIT | SROM_CMD_GET_SILICON_ID); //Request SROM call

status = PollSromStatus();

If (!status) Return FAIL;

//Read 32-bit ID from the registers

ReadIO( CPUSS SYSARG, out part0);

ReadIO( CPUSS SYSREQ, out part1);

siliconID[0] = (part0 >> 8) & 0xFF;

siliconID[1] = (part0 >> 0) & 0xFF;

siliconID[2] = (part0 >> 16) & 0xFF;

siliconID[3] = (part1 >> 0) & 0xFF;

//Compare IDs from the hex and from the target

For (i = 0; i < 4; i++)

If ( i == 2 ) //Ignore Revision ID

Continue;

If ( siliconID[i] != hexID[i] ) Return FAIL;

Return PASS;

```

### 4.5 Step 3 - Erase All Flash

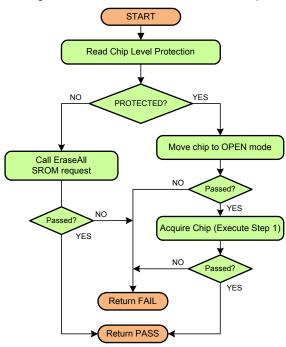

Before programming the flash, it must be erased. This step erases all user rows and the corresponding flash protection. It also moves chip-level protection to the OPEN state (if it was in PROTECTED mode, see Appendix A:Chip-Level Protection on page 36). Figure 4-4 shows the algorithm of the Erase All step.

Figure 4-4. Flow Chart of the Erase All Step

#### Pseudocode - Step 3. Erase All Flash

```

// Read Chip Level Protection using SROM call

Params = (SROM KEY1 << 0) + // KEY1

((SROM KEY2 + SROM CMD GET SILICON ID) << 8); // KEY2

WriteIO( CPUSS SYSARG, Params); //Write params in CPUSS SYSARG

WriteIO( CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD GET SILICON ID); //Request SROM call

Status = PollSromStatus();

If (!Status)) Return FAIL;

ReadIO( CPUSS SYSREQ, out data); // read result

chipProt = (byte) (data >> 12);

// Check current protection mode

If (chipProt == CHIP PROT PROTECTED) // PROTECTED

// Move chip to OPEN mode

Params = (SROM KEY1 << 0) +//KEY1

((SROM KEY2 + SROM CMD WRITE PROTECTION) << 8) +//KEY2

(0x01 << 16) + //OPEN mode

(0x00 << 24);//Flash Macro 0

WriteIO( CPUSS SYSARG, Params); //Write params in CPUSS SYSARG

WriteIO( CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD WRITE PROTECTION);

```

```

status = PollSromStatus();

if (!status) return FAIL;

// Re-acquire chip here to boot it in OPEN mode

// Execute Now: "Step 1 - Acquire Chip"

// Check result of re-acquire

If (!status) Return FAIL;

Else // OPEN (CHIP PROT OPEN)

Params = (SROM KEY1 << 0) +//KEY1

((SROM KEY2+SROM CMD ERASE ALL) << 8); //KEY2

WriteIO( SRAM PARAMS BASE + 0x00, Params); //Write params in SRAM

WriteIO( CPUSS SYSARG, SRAM PARAMS BASE); //Set location of parameters

WriteIO( CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD ERASE ALL); //Request SROM call

status = PollSromStatus();

If (!status) Return FAIL;

Return PASS;

//-----

```

### 4.6 Step 4 – Checksum Privileged

After the user's flash is erased, its checksum must be 0x00. However, the Checksum(All) API, which is used in "Step 9 – Verify Checksum" on page 31, also calculates the checksum of the privileged rows (not only the user rows). Therefore, it is necessary to find the checksum of the privileged rows when all the user rows are erased. The result of this operation is needed only to calculate the proper checksum of the user's flash in "Step 9 – Verify Checksum" on page 31. That checksum is calculated according to the following formula:

```

Checksum_User = Checksum_Step_9 - Checksum_Step_4

```

The result of this step must be used in "Step 9 – Verify Checksum" on page 31. A possible alternative solution to avoid this step is to calculate the checksum of each row individually and add them. However, this method takes much longer.

#### Pseudocode – Step 4. Checksum Privileged

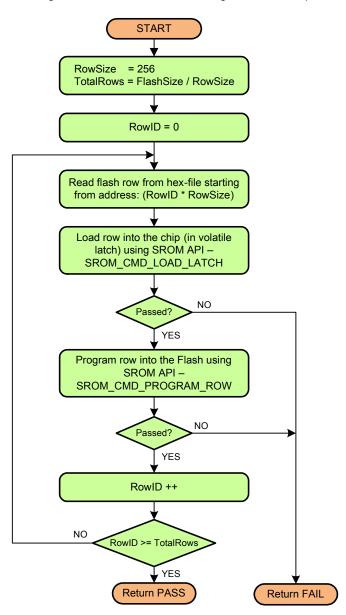

### 4.7 Step 5 – Program Flash

Flash memory is programmed in rows. Each row is 256 bytes long. The programmer must serially program each row individually. The source data is extracted from the hex file starting from address 0x00000000 (see Figure 2-2 on page 8). The flash size and the row size are input parameters of this step. Note that the flash size of the acquired silicon must be equal to the size of the user's code in the hex file, as verified in Step 2 by comparing the silicon IDs of the hex and the target. During programming, two SROM APIs are used:

- SROM CMD LOAD LATCH Loads the flash row into the silicon's volatile buffer.

- SROM\_CMD\_PROGRAM\_ROW Programs the row into flash (from the volatile buffer).

Figure 4-5 illustrates this programming algorithm.

Figure 4-5. Flow Chart of the "Program Flash" Step

#### Pseudocode – Step 5. Program Flash

```

//-----

// Flash Size must be provided.

RowSize = 256;

TotalRows = FlashSize / RowSize;

RowsPerMacro = 512;

//Program all flash rows

for (int RowID = 0; RowID < TotalRows; RowID++)</pre>

//1. Read Row data from hex

RowHexAddress = RowSize * RowID;

//Extract 256-byte row from the hex-file

//from address: "RowHexAddress" into buffer - "Data".

//HEX ReadData() must be implemented by Programmer.

Data = HEX ReadData( RowHexAddress, RowSize );

//2. Load Row to volatile buffer (latch)

MacroID = floor ( RowID / RowsPerMacro ); //Round to largest previous integer

Params1 = (SROM KEY1 << 0) +//KEY1

(SROM KEY2 + SROM CMD LOAD LATCH) << 8) + //KEY2

(0x00 << 16);//Byte number in latch from what to write

(MacroID << 24);

//Flash Macro ID (0 or 1)

Params2 = (RowSize - 1); //Number of Bytes to load minus 1

WriteIO(SRAM PARAMS BASE + 0x00, Params1); //Write params in SRAM

WriteIO(SRAM_PARAMS_BASE + 0x04, Params2); //Write params in SRAM

// Put row data into SRAM buffer

for (i = 0; i < RowSize; i += 4)

Params1 = (Data[i] << 0) + (Data[i + 1] << 8) +

Data[i + 2] << 16) + (Data[i + 3] << 24);

WriteIO(SRAM PARAMS BASE + 0x08 + i, Params1);//Write params is SRAM

}

// Call "Load Latch" SROM API

WriteIO(CPUSS SYSARG, SRAM PARAMS BASE); //Set location of parameters

WriteIO(CPUSS SYSREQ, SROM SYSREQ_BIT | SROM_CMD_LOAD_LATCH);//Request SROM operation

Status = PollSromStatus();

if (!Status) return FAIL;

//3. Program Row - call SROM API

Params = (SROM KEY1 << 0) + //KEY1

((SROM_KEY2+SROM_CMD_PROGRAM_ROW) << 8) + //KEY2

((RowID & 0x00FF) << 16) + //ROW_ID_LOW[7:0]

((RowID & 0xFF00) << 16); //ROW_ID_HIGH[9:8]

WriteIO(CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD PROGRAM ROW);//Request SROM operation

Status = PollSromStatus();

if (!Status) return FAIL;

return PASS;

```

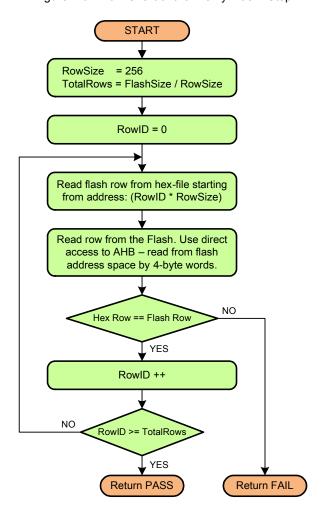

## 4.8 Step 6 - Verify Flash

Because the checksum is verified eventually, this step is optional. It is recommended that it be kept in the programming flow for higher reliability. The checksum cannot completely guarantee that the content is written without errors.

During verification, the programmer reads a row from flash and the corresponding data from the hex file and compares them. If any difference is found, the programmer must stop and return a failure. Each row must be considered.

Reading from the flash is achieved by direct access to the memory space of the CPU. No SROM API is required; simply read from the address range 0x00000000 – 0x0003FFFF.

Figure 4-6 illustrates the verification algorithm.

Figure 4-6. Flow Chart of the "Verify Flash" Step

#### Pseudocode – Step 6. Verify Flash.

```

//-----

// Flash Size must be provided.

RowSize = 256;

TotalRows = FlashSize / RowSize;

//Read and Verify Flash rows

for (int RowID = 0; RowID < TotalRows; RowID++)</pre>

//1. Read row from hex file

RowAddress = rowSize * rowID; //liner address of row in flash

//Extract 256-byte row from the hex file

//from address: "RowHexAddress" into buffer - "Data".

//HEX ReadData() must be implemented by Programmer.

hexData = HEX ReadData( RowAddress, RowSize );

//2. Read row from chip

for (i = 0; i < RowSize; i += 4)

//Read flash via AHB-interface

ReadIO( RowAddress + i, out data32);

chipData[i + 0] = (data32 >> 0) & 0xFF;

chipData[i + 1] = (data32 >> 8) \& 0xFF;

chipData[i + 2] = (data32 \gg 16) & 0xFF;

chipData[i + 3] = (data32 >> 24) \& 0xFF;

}

//3. Compare them

for (i = 0; i < RowSize; i++)</pre>

if (chipData[i] != hexData[i]) return FAIL;

return PASS;

```

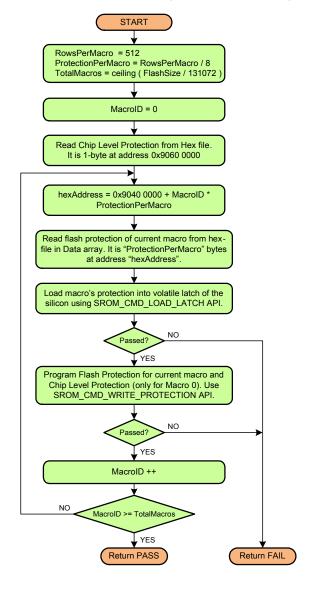

### 4.9 Step 7 - Program Protection Settings

At this point, the programmer writes into the supervisory flash all protection data: row-level protection and chip-level protection. For more information, see Figure 2-1 on page 7.

The Target device can have two flash macros, each with its own supervisory rows to store the protection settings of the user's rows. Each user row occupies one bit in the protection space: 0 means unprotected; 1 means protected. This provides write/ erase protection of the row. In the PROTECTED state, a row cannot be erased or written either by the firmware or by an external programmer. The protection setting can be reset only by the EraseAll() operation in Step 3, driven by the external programmer.

Chip-level protection is only 1 byte and is stored in the supervisory row of macro 0 where the flash protection data resides.

Figure 4-7 shows the algorithm of writing protection settings.

Figure 4-7. Flow Chart of the "Program Protection Settings" Step

#### Pseudocode – Step 7. Program Protection Settings

```

HexAddr = ProtectionPerMacro * MacroID;

Data = HEX ReadRowProtection(HexAddr, ProtectionPerMacro);

//3. Load protection setting of current macro into volatile latch.

//This is same implementation as for "Program Flash" step.

//So this code can be moved into a separate routine - "LoadLatch (MacroID, Data)".

Params1 = (SROM KEY1 << 0) +//KEY1

((SROM KEY2 + SROM CMD LOAD LATCH) << 8) +//KEY2

(0x00 << 16) + //Byte number in latch from what to write

(MacroID << 24);//Flash Macro ID (0 or 1)

Params2 = (ProtectionPerMacro - 1); //Number of Bytes to load minus 1

WriteIO(SRAM PARAMS BASE + 0x00, Params1); //Write params is SRAM

WriteIO(SRAM PARAMS BASE + 0x04, Params2); //Write params is SRAM

// Put row data into SRAM buffer

for (i = 0; i < ProtectionPerMacro; i += 4)</pre>

Params1 = (Data[i] << 0) + (Data[i + 1] << 8) +

(Data[i + 2] \ll 16) + (Data[i + 3] \ll 24);

WriteIO(SRAM PARAMS BASE + 0x08 + i, Params1); //Write params is SRAM

}

// Call "Load Latch" SROM API

WriteIO(CPUSS SYSARG, SRAM PARAMS BASE); //Set location of parameters

WriteIO(CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD LOAD LATCH);//Request SROM operation

Status = PollSromStatus();

if (!Status) return FAIL;

//4. Program protection setting of current macro into supervisory row.

Params = (SROM KEY1 << 0) +//KEY1

((SROM KEY2 + SROM CMD WRITE PROTECTION) << 8) +//KEY2

(ChipLevelProtection << 16)+ //Applicable only for Macro

(Macro0 << 24);//Flash Macro

WriteIO(CPUSS SYSARG, Params);

WriteIO(CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD WRITE PROTECTION);

//Read status of the operation

Status = PollSromStatus();

if (!Status)) return FAIL;

return PASS;

//-----

```

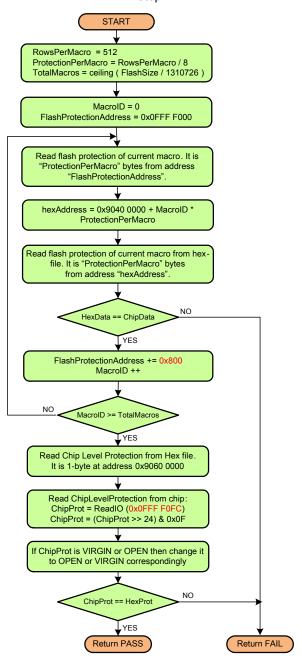

# 4.10 Step 8 – Verify Protection Settings

This step verifies the data that was written in Step 7. The point is to read back the details of flash protection and chiplevel protection from the silicon and compare this data with the corresponding data from the hex file. Although this step is optional, Cypress recommends that you implement it in the programmer.

Reading of the protection setting is carried out by direct access to the memory space of the CPU (via AHB). See Figure 2-1 on page 7 to find the address range of protection data. The programmer reads out the data in 4-byte words.

Note that when a chip-level protection byte is read from the silicon, it must be reviewed. This is because of the inverted values of OPEN and VIRGIN modes written in the supervisory rows (see Appendix A:Chip-Level Protection on page 36). If VIRGIN mode is read from flash, then it must be converted to OPEN mode; if OPEN mode is read from flash, it must be considered as VIRGIN mode. For KILL and PROTECTED modes, no translation is necessary.

Figure 4-8. Flow Chart of the "Verify Protection Settings"

Step

#### Pseudocode – Step 8. Verify Protection Settings

```

//-----

// Flash Size must be provided.

RowsPerMacro = 512;

ProtectionPerMacro = RowsPerMacro / 8;

TotalMacros = ceiling (FlashSize /131072); // round to smallest following integer65536

FlashProtectionAddress = SFLASH MACRO 0; //0x0FFF F000

for (MacroID = 0; MacroID < TotalMacros; MacroID++; FlashProtectionAddress += 0x800)

//1. Read Protection settings of current macro from hex-file.

//It is located at address 0x9040 0000.

//HEX ReadRowProtection() must be implemented.

HexAddr = ProtectionPerMacro * MacroID;

hexProt = HEX ReadRowProtection(HexAddr, ProtectionPerMacro);

//2. Read Protection of current macro from silicon

for (i = 0; i < ProtectionPerMacro; i += 4)</pre>

{

ReadIO(FlashProtectionAddress + i, out data32);

flashProt[i + 0] = (data32 \gg 0) & 0xFF;

flashProt[i + 1] = (data32 >> 8) & 0xFF;

flashProt[i + 2] = (data32 \gg 16) & 0xFF;

flashProt[i + 3] = (data32 >> 24) & 0xFF;

}

//3. Compare hex and silicon's data

for (i = 0; i < ProtectionPerMacro; i++ )</pre>

If (hexProt[i] != flashProt[i]) return FAIL;

//4. Read Chip Level Protection from hex-file. It is 1 byte at address 0x90600000.

//HEX ReadChipLevelProtection() must be implemented.

Hex ChipLevelProtection = HEX ReadChipLevelProtection();

//5. Read Chip Level Protection from the silicon

ReadIO(SFLASH CPUSS PROTECTION, out Chip ChipLevelProtection);

Chip ChipLevelProtection = (Chip ChipLevelProtection >> 24) & 0x0F;

if (Chip ChipLevelProtection == CHIP PROT VIRGIN) Chip ChipLevelProtection = CHIP PROT OPEN;

else

if (Chip_ChipLevelProtection == CHIP_PROT_OPEN) Chip_ChipLevelProtection = CHIP_PROT_VIRGIN;

//6. Compare hex's and silicon's data

if (Chip ChipLevelProtection != Hex ChipLevelProtection) return FAIL;

return PASS;

//-----

```

### 4.11 Step 9 - Verify Checksum

This step validates the result of the flash programming process. It calculates the checksum of the user rows written in Step 5 and compares this value with the 2-byte checksum from the hex file. The Checksum SROM API computes the checksum of the user and privileged rows. To find the checksum of only the user rows, it is necessary to subtract the checksum of the privileged rows found in Step 4. Figure 4-9 shows the final checksum algorithm. This is a mandatory step in the programming flow, although the checksum operation cannot completely guarantee that the data is written correctly. For this reason, the Verify Flash step is also recommended.

**START** Call SROM\_CMD\_CHECKSUM for all flash (user+privileged rows). Save result in variable "Step9\_Checksum". NO Passed? YES Find checksum of user rows: Chip\_Checksum = 0xFFFF & (Step9\_Checksum - Step4\_Checksum) Read 2-byte checksum from hex-file located at address 0x9030 0000. NO Chip\_Checksum = Hex\_Checksum YES Return PASS Return FAIL

Figure 4-9. Flow Chart of the "Verify Checksum" Step

#### Pseudocode - Step 9. Verify Checksum

```

//-----

// Checksum of Privileged rows must be taken from Step 4.

// SROM call here is identical to one Step 4, so it can be refactored into one subroutine.

// 1. SROM call - Checksum All

Params = (SROM KEY1 << 0) +//KEY1

((SROM KEY2+SROM CMD CHECKSUM) << 8)+//KEY2

((0x0000 \& 0x00FF) << 16) +//Row ID[7:0]

((0x8000 \& 0xFF00) << 16);/Row ID[15:8] - Checksum All(0x8000)

WriteIO( CPUSS SYSARG, Params); //Write params in CPUSS SYSARG

WriteIO( CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD CHECKSUM); //Request SROM call

status = PollSromStatus();

if (!status) return FAIL;

//Read Checksum from CPUSS SYSARG register

ReadIO(CPUSS SYSARG, out Checksum all);

Checksum All = (Checksum All & 0x0FFFFFFFF); //28-bit checksum

//2. Find 2-byte checksum of user rows, "Checksum Privileged" is calculated in Step 4.

Chip Checksum = (Checksum All - Checksum Privileged) & 0xFFFF;

//3. Read 2-byte checksum of user code from hex-file

// HEX ReadChecksum() must be implemented by Programmer.

Hex Checksum = HEX ReadChecksum();

//4. Compare silicon's vs hex's checksum

if (Chip Checksum != Hex Checksum) return FAIL;

return PASS;

```

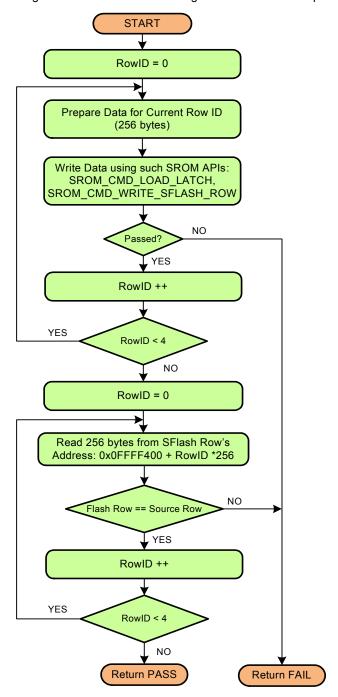

# 4.12 Step 10 - Program User SFlash (optional)

The Supervisory Flash of the Target device provides four rows in Macro 1 for application specific use. Every such row consists of 256 bytes - same as other flash rows. Application can store here any information, but typically it is the Unique Bluetooth Address of the device. Length and format of the address is also application specific. During mass production vendor should define the rule which quarantees that every programmed part is assigned with the unique address.

This step is considered as optional - every application should determine if it needs this flash region and for which purpose. Also, User SFlash rows are not stored in the hex file, since this information is unique for each part (for most of applications).

Programming of User SFlash via SWD port is only available in silicon's OPEN mode. So, we have to execute this step sometime after Erase All step, which guarantees that part is in OPEN mode. But, the recommendation is to execute it as the last step in the programming flow, since it's the non-hex flash region (optional). Alternatively, User Application can update this SFLash region whenever needed (CPU access via SROM APIs) - e.g. to store calibration data, non-volatile parameters, etc.

The User SFlash Rows are mapped onto CPUs address space in the range 0x0FFF F400 - 0x0FFF F7FF. So, user application can read these rows directly from these addresses.

Following SROM APIs are used in this step:

- SROM\_CMD\_LOAD\_LATCH Loads the flash row into the silicon's volatile buffer;

- SROM\_CMD\_WRITE\_SFLASH\_ROW Program rows from volatile latch into User's Flash.

Figure 4-10 illustrates User SFlash programming algorithm.

Figure 4-10. Flow Chart of "Program User SFlash" Step

#### Pseudocode. Step 10 - Program User SFlash

```

//-----

// Flash Row Size, Number of Rows and Data to Program must be provided.

RowSize = 256;

TotalRows = 4;

//Program all User SFlash rows

for (int RowID = 0; RowID < TotalRows; RowID++)</pre>

//1. Prepare data for current row (256-byte)

//Read it in the "Data" array .

//SFlash ReadSource() must return data for current SFlash row.

Data = SFlash ReadSource( RowID, RowSize );

//2. Load Row to volatile buffer (latch)

MacroID = 0x00; //User SFLash rows are located only in Macro 0

Params1 = (SROM KEY1 << 0) +//KEY1

((SROM KEY2 + SROM CMD LOAD LATCH) << 8) +//KEY2

(0x00 \ll 16) + //Byte number in latch from what to write

(MacroID << 24); //Flash Macro ID (0 or 1)

Params2 = (RowSize - 1); //Number of Bytes to load minus 1

WriteIO(SRAM PARAMS BASE + 0x00, Params1); //Write params in SRAM

WriteIO(SRAM PARAMS BASE + 0x04, Params2); //Write params in SRAM

// Put row data into SRAM buffer

for (i = 0; i < RowSize; i += 4)

Params1 = (Data[i] << 0) + (Data[i + 1] << 8) +

Data[i + 2] << 16) + (Data[i + 3] << 24);

WriteIO(SRAM PARAMS BASE + 0x08 + i, Params1);//Write params is SRAM

}

// Call "Load Latch" SROM API

WriteIO(CPUSS SYSARG, SRAM PARAMS BASE); //Set location of parameters

WriteIO(CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD LOAD LATCH);//Request SROM operation

Status = PollSromStatus();

if (!Status) return FAIL;

//3. Program User SFlash Row - call SROM API

Params1 = (SROM KEY1 << 0) + //KEY1

((SROM KEY2+SROM CMD WRITE SFLASH ROW) << 8)+ //KEY2

Params2 = RowID //Row ID of User SFlash

WriteIO(SRAM PARAMS BASE+0x00, Params1); //Write params is SRAM

WriteIO(SRAM PARAMS BASE+0x04, Params2); //Write params is SRAM

WriteIO(CPUSS SYSARG, SRAM PARAMS BASE); //Set location of parameters

WriteIO(CPUSS SYSREQ, SROM SYSREQ BIT | SROM CMD WRITE SFLASH ROW); //Request SROM oper-

ation

Status = PollSromStatus();

```

```

if (!Status) return FAIL;

//Verify all User SFlash rows

for (int RowID = 0; RowID < TotalRows; RowID++)</pre>

//1. Prepare Source data for current row (256-byte)

sourceData = SFlash ReadSource( RowID, RowSize );

//2. Read row from chip

RowAddress = 0x0FFFF200 + RowID * RowSize;

for (i = 0; i < RowSize; i += 4)

//Read flash via AHB-interface

ReadIO( RowAddress + i, out data32);

chipData[i + 0] = (data32 >> 0) & 0xFF;

chipData[i + 1] = (data32 >> 8) \& 0xFF;

chipData[i + 2] = (data32 \gg 16) & 0xFF;

chipData[i + 3] = (data32 >> 24) \& 0xFF;

//3. Compare them

for (i = 0; i < RowSize; i++)</pre>

if (chipData[i] != sourceData[i]) return FAIL;

}

return PASS;

```

# Appendix A. Chip-Level Protection

The difference between chip-level protection and row-level protection may not be obvious at first glance. Chip-level protection restricts access to the silicon's resources by way of the SWD bus by the external programmer. However, it does not restrict anything for the firmware. If any resource is not accessible, the SWD transaction is NACKed. Row-level protection restricts the firmware and the external programmer from writing to the protected flash rows.

There are four states of chip-level protection into which the silicon can be moved: VIRGIN, OPEN, PROTECTED, KILL.

Table A-1. States of Chip-Level Protection

| Protection State | Value in Hex and CPUSS_PROTECTION | Value in Written<br>Supervisory Row | Restrictions                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIRGIN           | 0x00                              | 0x01                                | In this mode, the silicon is in post-fab (untrimmed state). After trimming, the silicon is moved into OPEN mode for customer. This mode is not for custom use. Customers are not physically prohibited from bringing parts back to the VIRGIN state, but they will be left with parts missing critical trim, wounding, and other settings from Cypress. This essentially makes the part unusable for the customer. |