# **Aurora Reference Design**

**AN5864**

### Introduction (Ask a Question)

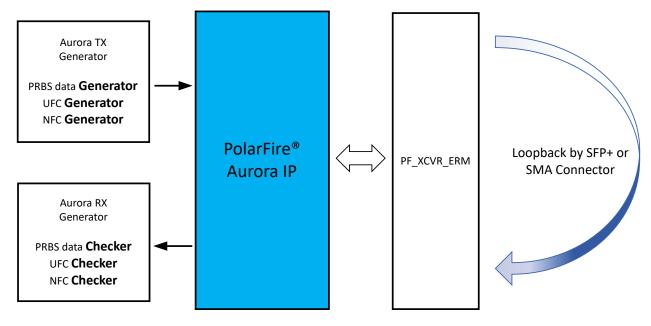

This document provides instructions for using the Aurora 8B/10B IP on the PolarFire Evaluation Board. The PolarFire high-speed transceiver (PF\_XCVR\_ERM) must be configured in PCS 8B10B mode along with the Aurora 8B/10B IP. The AURORA\_TX\_GENERATOR and AURORA\_RX\_CHECKER modules are used to generate and verify data through the AXI4-Stream interface.

The Evaluation Board has two interfaces: SFP+ and SMA. This reference design supports both configurations. The cable must be connected in loopback mode from TX to RX on the board.

# **Table of Contents**

| Intr | duction                                   | 1  |

|------|-------------------------------------------|----|

| 1.   | Overview                                  | 3  |

| 2.   | Reference Design Specifications           | 4  |

| 3.   | Design Information                        | 5  |

|      | 3.1. Aurora Tx Generator                  | 5  |

|      | 3.2. Aurora Rx Checker                    |    |

|      | 3.3. Transceiver Configuration            |    |

| 4.   | ibero Project                             | 8  |

|      | l.1. Timing Constraints                   | 8  |

|      | l.2. Interface Constraints                |    |

| 5.   | simulation                                | 10 |

| 6.   | Debug and Testing                         | 12 |

| 7.   | Revision History                          | 16 |

| Mic  | ochip FPGA Support                        | 17 |

| Mic  | ochip Information                         | 17 |

|      | rademarks                                 | 17 |

|      | egal Notice                               |    |

|      | Microchip Devices Code Protection Feature | 18 |

### 1. Overview (Ask a Question)

The Aurora 8B/10B IP uses AXI4-Stream as the user interface for communication. This reference design includes two modules, AURORA\_TX\_GENERATOR and AURORA\_RX\_CHECKER, for testing. The high-speed transceiver block supports data rates ranging from 250 Mbps to 12.7 Gbps. The transceiver (PF\_XCVR\_ERM) module integrates multiple functional blocks to enable high-speed serial data transfer within the FPGA. The transceiver used in the Aurora 8B/10B applications has a bandwidth limited to a line rate range of 0.5 Gb/s to 6.6 Gb/s.

The Aurora 8B/10B IP supports a 32-bit data width and single transceiver lanes. This reference design can be implemented on two Microchip PolarFire boards to enable full-duplex data transfer.

Figure 1-1. Aurora 8B/10B IP Reference Design Block Diagram

## 2. Reference Design Specifications (Ask a Question)

This section provides a list of reference design specifications.

- Full-duplex mode

- Single-lane channel

- Data rate: 3.125 Gbps

- Payload Data Unit (PDU): 32-bit data width

- Test User Flow Control (UFC) and Native Flow Control (NFC)

### 3. Design Information (Ask a Question)

This section provides an overview of the modules included in the design.

#### 3.1. Aurora Tx Generator (Ask a Question)

When the LANE and CHANNEL are successfully initialized, the AURORA\_TX\_GENERATOR.CHANNEL\_UP signal is asserted. The generator then starts producing test patterns and sends them to the Aurora 8B/10B IP through the AXI4-Stream interface.

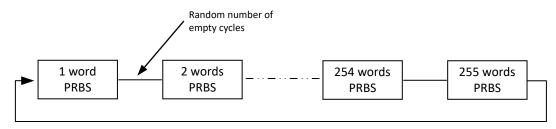

• **Data Transmission:** The PRBS data pattern is used to test the TX user interface. The data word size increases incrementally in each frame, ranging from 1 to 255 (1 word = 32 bits). A short random number of cycles is inserted between frames.

Figure 3-1. Data Test Sequence

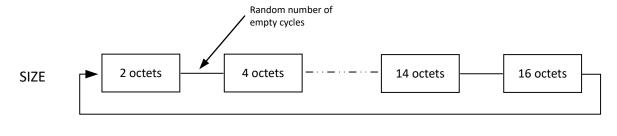

• **UFC Message Transmission:** Pre-set values are used to test the TX UFC user interface. According to the Aurora 8B/10B specification, the UFC size range is an even number of octets, between 2 and 16.

Figure 3-2. UFC Test Sequence

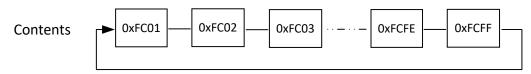

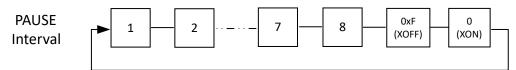

• **NFC Message Transmission:** The sequence of pause numbers follows the pattern 1 to 8, then 0xF and finally 0. According to the Aurora 8B/10B specification, the NFC data range is from 1 to 8. A value of 0xF instructs the channel partner to stop transmitting data, while a value of 0 instructs it to resume transmission.

Figure 3-3. NFC Test Sequence

#### 3.2. Aurora Rx Checker (Ask a Question)

After the LANE and CHANNEL are successfully initialized, the CHECKER module starts verifying the data received from the Aurora 8B/10B IP through the AXI4-Stream interface.

The following table provides port information. These ports indicate respective data mismatch errors.

Table 3-1. Aurora Rx Checker

| Signal Hierarchy          | Description                                       |

|---------------------------|---------------------------------------------------|

| AURORA_RX_CHECKER.ERR_PDU | Indicates a mismatch in the received PDU data.    |

| AURORA_RX_CHECKER.ERR_UFC | Indicates a mismatch in the received UFC message. |

| AURORA_RX_CHECKER.ERR_NFC | Indicates a mismatch in the received NFC message. |

### 3.3. Transceiver Configuration (Ask a Question)

PolarFire Aurora 8B/10B IP does not include transceiver PMA and PCS. The following figure shows the configuration of Transceiver IP in Libero $^{\text{®}}$  design.

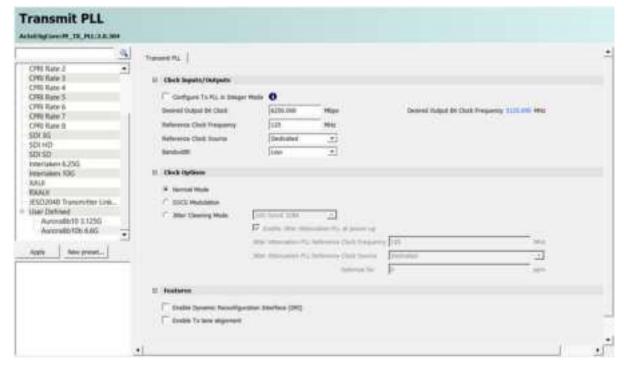

1. The PolarFire Evaluation Board provides a 125 MHz clock source. Configure the PF\_TX\_PLL IP to generate a 6250 Mbps bit clock for PF\_XCVR\_ERM.

Figure 3-4. Transmit PLL

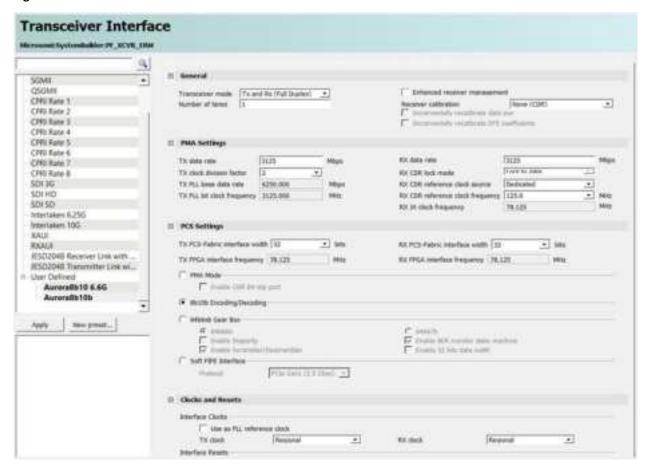

- 2. Configure PF\_XCVR\_ERM for full-duplex operation with a single lane and a data rate of 3.125 GHz.

- 3. Configure the PCS interface width to 32 bits with 8B/10B encoding and decoding.

Figure 3-5. Transceiver Interface

### 4. Libero Project (Ask a Question)

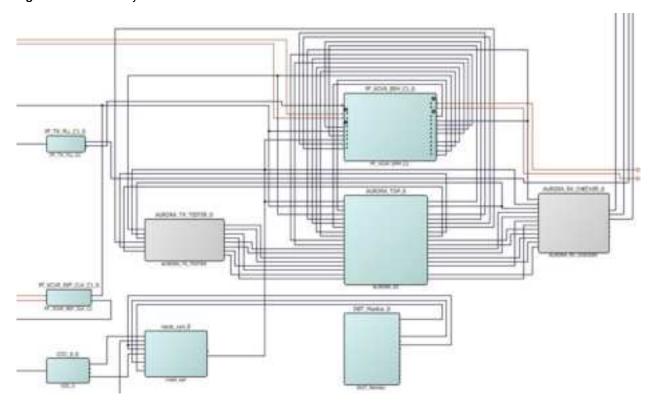

In addition to the main functional block, there are additional modules such as CCC, reset\_syn and INIT Monitor, which are responsible for generating the system clock and reset.

The following figure shows the top-level Libero design of the high-speed data transfer using Aurora 8B/10B IP.

Figure 4-1. Libero Project

### 4.1. Timing Constraints (Ask a Question)

The following constraint describes the frequency of SYS\_CLK is 125 MHz, TX\_CLK and RX\_CLK are 78.125 MHz.

The false path ARSTN is an asynchronous signal.

```

create_clock -name {REF_CLK_PAD_P} -period 8 -waveform {0 4 } [ get_ports { SYS_CLK } ]

create_clock -name {PF_XCVR_ERM_C1_0/I_XCVR/LANE0/TX_CLK_R} -period 12.8 [ get_ports

{ TX_CLK } ]

create_clock -name {PF_XCVR_ERM_C1_0/I_XCVR/LANE0/RX_CLK_R} -period 12.8 [ get_ports

{ RX_CLK } ]

set_false_path -from [ get_ports { ARSTN } ]

set_clock_groups -asynchronous -group [ get_clocks { PF_XCVR_ERM_C1_0/I_XCVR/LANE0/

TX_CLK_R } ]

set_clock_groups -asynchronous -group [ get_clocks { PF_XCVR_ERM_C1_0/I_XCVR/LANE0/RX_CLK_R }]

```

#### 4.2. Interface Constraints (Ask a Question)

This section describes interface constraints.

· Constraints for SFP+ connector

```

set_io -port_name LANEO_RXD_N -pin_name AD30 -DIRECTION_INPUT set_io -port_name LANEO_RXD_P -pin_name AD29 -DIRECTION_INPUT

```

```

set_io -port_name LANE0_TXD_N -pin_name AE32 -DIRECTION OUTPUT set_io -port_name LANE0_TXD_P -pin_name AE31 -DIRECTION OUTPUT

```

#### Constraints for SMA connector

```

set_io -port_name LANEO_RXD_N -pin_name AC32 -DIRECTION INPUT

set_io -port_name LANEO_RXD_P -pin_name AC31 -DIRECTION INPUT

set_io -port_name LANEO_TXD_N -pin_name AD34 -DIRECTION OUTPUT

set_io -port_name LANEO_TXD_P -pin_name AD33 -DIRECTION OUTPUT

```

### 5. Simulation (Ask a Question)

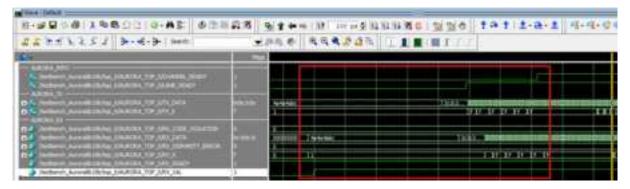

A loopback simulation testbench is provided. The following key observations can be made from the waveform:

• When both PF\_XCVR\_ERM.RX\_VAL and PF\_XCVR\_ERM.RX\_READY are asserted, it indicates that the receiver of PF\_XCVR\_ERM has completed initialization. The Aurora 8B/10B IP will start operating upon receiving these signals.

Figure 5-1. Simulation

• During the time interval from RX\_VAL to CHANNEL\_READY, the Aurora 8B/10B IP undergoes initialization and verification. The user application system must wait until CHANNEL\_READY is asserted before starting operation.

Figure 5-2. CHANNEL\_READY is Asserted before Starting Operation

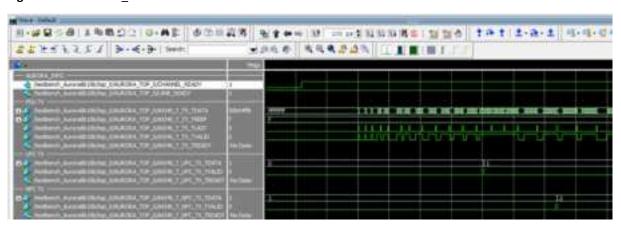

• The TX\_GENERATOR module starts transmitting test patterns to Aurora 8B/10B IP after CHANNEL READY is asserted.

Figure 5-3. CHANNEL\_READY is Asserted

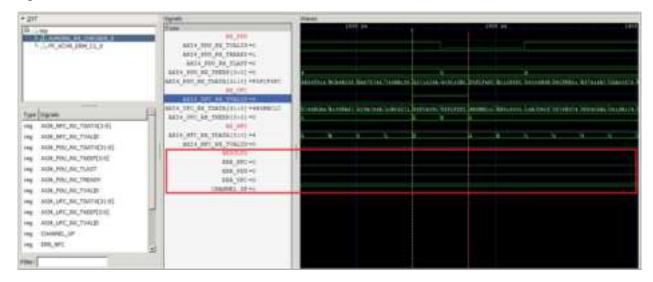

- The AURORA\_RX\_CHECKER module starts verifying the received data after CHANNEL\_UP is asserted.

- The PDU, UFC and NFC data are continuously checked. The ERR\_PDU, ERR\_UFC and ERR\_NFC signals must remain low; otherwise, a data mismatch is detected.

Figure 5-4. Data Mismatch Detected

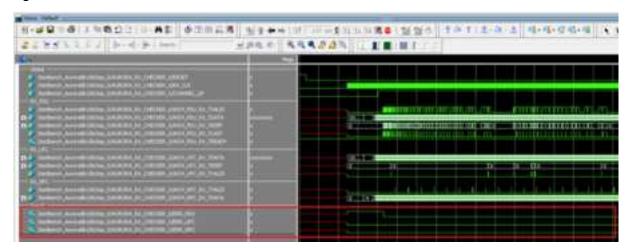

### 6. Debug and Testing (Ask a Question)

Use the Identify® Debug Design tool to monitor signals in the design.

- 1. CHANNEL UP

- This signal should be asserted after the cable is plugged in and the initialization process is complete.

- 2. ERR PDU/ERR UFC/ERR NFC

- These signals should always remain low.

- Set a trigger in tool to monitor for errors.

- 3. Status LEDs

- LED4: DATA error, LED illumination indicates an error for data.

- LED5: UFC error. LED illumination indicates an error for UFC.

- LED6: NFC error. LED illumination indicates an error for UFC.

- LED7: CHANNEL READY. LED illumination indicates successful initialization.

The following figure shows the Identify Debug Design Tool.

Figure 6-1. Debug and Testing

The following figure shows results in the waveform viewer.

Figure 6-2. Monitor Error

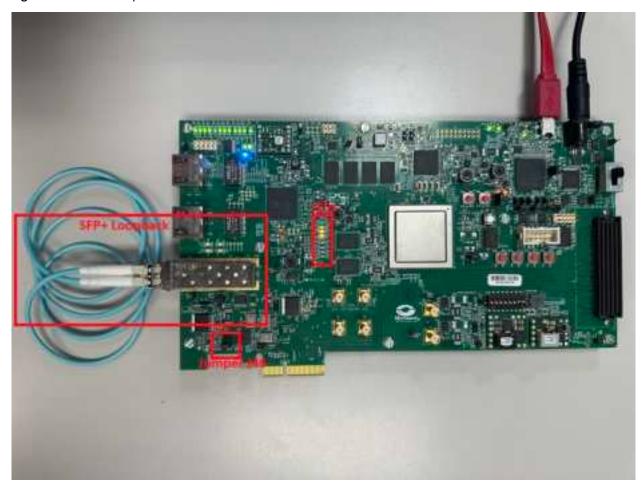

To test the hardware setup, follow the instructions below:

- 1. Close jumper J46.

- 2. Connect SPF+ and optical cable in loop-back mode.

- 3. Observe the status of LEDs.

The following figure shows the setup of a PolarFire development board.

Figure 6-3. Board Setup

Figure 6-4. Status of LEDs

# $\rightarrow$

#### Important:

- LED4: PDU error status, ON indicates, an error has detected.

- LED5: UFC error status, ON indicates, an error has detected.

- LED6: NFC error status, ON indicates, an error has detected.

- LED7: Channel ready status, ON indicates, the channel has initialized.

# 7. Revision History (Ask a Question)

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description       |

|----------|---------|-------------------|

| Α        | 05/2025 | Initial revision. |

### **Microchip FPGA Support**

Microchip FPGA products group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, and worldwide sales offices. Customers are suggested to visit Microchip online resources prior to contacting support as it is very likely that their queries have been already answered.

Contact Technical Support Center through the website at <a href="https://www.microchip.com/support">www.microchip.com/support</a>. Mention the FPGA Device Part number, select appropriate case category, and upload design files while creating a technical support case.

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

- From North America, call 800.262.1060

- From the rest of the world, call 650.318.4460

- Fax, from anywhere in the world, 650.318.8044

### **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at https://www.microchip.com/en-us/about/legal-information/microchip-trademarks.

ISBN: 979-8-3371-1155-1

### **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip products are strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable".

Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.