# **EVK-VERA-P174**

# Evaluation kit for VERA-P1 host-based V2X transceiver modules

User guide

## **Abstract**

This document describes how to set up the EVK-VERA-P174 evaluation kit to evaluate the VERA-P1 series host-based 802.11p V2X transceiver modules.

## **Document information**

| Title                  | EVK-VERA-P174                                                 |            |  |

|------------------------|---------------------------------------------------------------|------------|--|

| Subtitle               | Evaluation kit for VERA-P1 host-based V2X transceiver modules |            |  |

| Document type          | User guide                                                    |            |  |

| Document number        | UBX-17048707                                                  |            |  |

| Revision and date      | R08                                                           | 6-Nov-2020 |  |

| Disclosure Restriction | C1 Public                                                     |            |  |

This document applies to the following products:

| Product name  | Type number          | Firmware version | PCN reference |

|---------------|----------------------|------------------|---------------|

| EVK-VERA-P174 | EVK-VERA-P174-00A-00 |                  | N/A           |

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only permitted with the express written permission of u-blox.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com.

Copyright © u-blox AG.

# **Contents**

| Document information                                    | 2  |

|---------------------------------------------------------|----|

| Contents                                                | 3  |

| 1 Evaluation kit description                            | 5  |

| 1.1 Overview                                            | 5  |

| 1.2 Kit includes                                        | 6  |

| 1.3 Software and documentation                          | 6  |

| 1.4 System requirements                                 | 6  |

| 1.5 Specifications                                      |    |

| 2 Getting started                                       | 8  |

| 3 Board description                                     |    |

| 3.1 Block diagram                                       |    |

| 3.2 Overview                                            |    |

| 3.2.1 Main board                                        | 10 |

| 3.2.2 USB and power supply board                        | 11 |

| 3.3 Connectors                                          | 12 |

| 3.3.1 Power supply and configuration                    | 12 |

| 3.3.2 USB interface                                     | 12 |

| 3.3.3 Bootstrapping                                     |    |

| 3.3.4 SPI interface                                     |    |

| 3.3.5 SPI chip select                                   |    |

| 3.3.6 1PPS interface                                    |    |

| 3.3.7 GNSS interface                                    |    |

| 3.3.8 SMA connectors                                    |    |

| 3.3.9 Host interface connector                          |    |

| 3.4 LEDs                                                |    |

| 3.5 Buttons                                             |    |

| 3.6 Design files                                        |    |

| 4 Software                                              |    |

| 4.1 Quick start instructions                            |    |

| 4.2 Module calibration                                  |    |

| 4.3 Usage examples                                      |    |

| 4.3.1 Transmit and receive counters                     |    |

| 4.3.2 Channel configuration                             |    |

| 4.3.3 Transmitter test                                  |    |

| 4.3.4 Receiver test                                     |    |

| 4.3.5 LLC native IPv6 functionality                     |    |

| 4.4 Building the software for a different target platfo |    |

| Appendix                                                |    |

| A Glossary                                              |    |

| Related documents                                       | 29 |

| Revision history | 30 | ) |

|------------------|----|---|

| Contact          | 3: | 1 |

## 1 Evaluation kit description

## 1.1 Overview

VERA-P1 is a compact, embedded transceiver module that enables development of electronics for Vehicle-to-Everything (V2X) communication systems. The module includes an integrated MAC/LLC/Baseband processor and the required RF front-end components. It connects to a host processor through USB or SPI interface.

The EVK-VERA-P174 evaluation kit provides a simple way to evaluate the VERA-P1 series host-based V2X transceiver modules. The evaluation kit serves as an evaluation and development platform providing full access to the interfaces of the VERA-P1 radio module, and allows integration of the VERA-P1 module with an external PC or host processor development platform.

The main features of the EVK-VERA-P174 evaluation kit are:

- Enables host communication via Micro USB connector or SPI pin header

- Provides two SMA antenna connectors for the VERA-P1 module

- Has an integrated u-blox NEO-M8U GNSS module with SMA antenna connector

- Has an on-board SPI flash for evaluating different boot options

- Provides an integrated USB 2.0 hub to access VERA-P1, GNSS, and SPI flash via a single connector

- Has 9 28 V DC power supply input with the option to provide external supplies separately and measure current consumption

Table 1 lists the available versions of the evaluation kit:

| Evaluation kit | Description                           | Suitable for evaluation of                                                  |

|----------------|---------------------------------------|-----------------------------------------------------------------------------|

| EVK-VERA-P174  | Evaluation kit for the VERA-P1 module | VERA-P173 (with single radio firmware) VERA-P174 (with dual radio firmware) |

Table 1: EVK-VERA-P174 evaluation kit

For further information about the features supported by VERA-P1 series V2X modules, see the VERA-P1 series data sheet [1] and VERA-P1 series system integration manual [2].

The EVK-VERA-P174 consists of two boards, which are connected by a board-to-board connector. The upper main board contains the VERA-P174 and the NEO-M8U GNSS module. The USB interface and main power supply are included on the lower power supply board. The board-to-board connector allows the main board to be directly connected to a compatible host board.

Figure 1: EVK-VERA-P174 main board

## 1.2 Kit includes

The EVK-VERA-P174 evaluation kit includes the following:

- Evaluation board with the VERA-P174 module (main and power supply boards)

- Two 5.9 GHz DSRC antennas (Triton TD.10 5 dBi)

- Micro USB cable

- Quick Start card

## 1.3 Software and documentation

The Linux drivers, firmware, and basic evaluation tools for the VERA-P1 series modules are available via u-blox support. Distribution of the software requires signing of the u-blox Limited Use License Agreement (LULA-N).

Contact u-blox support for your area as listed in the Contact section to obtain the software package.

## 1.4 System requirements

- Host PC with a USB 2.0 interface

- Native Linux OS or virtual machine for building and running the software (for example, Ubuntu 18.04)

## 1.5 Specifications

Table 2 and Table 3 list the absolute maximum ratings and operating conditions for the EVK-VERA-P174:

| Symbol               | Description                    | Min. | Max. | Unit |  |

|----------------------|--------------------------------|------|------|------|--|

| V_Sys                | Main power supply 9 – 28 V     | -0.3 | 28.0 | V    |  |

| 5V0_A1,<br>5V0_A2    | Power supply voltage 5 V       | -0.3 | 6.0  | V    |  |

| 3V3                  | Power supply voltage 3.3 V     | -0.3 | 3.9  | V    |  |

| VIO                  | I/O supply voltage 1.8 V/3.3 V | -0.3 | 3.9  | V    |  |

| T <sub>STORAGE</sub> | Storage temperature            | -40  | +95  | °C   |  |

#### Table 2: Absolute maximum ratings

| Symbol            | Description                                      | Min. | Тур | Max. | Unit |

|-------------------|--------------------------------------------------|------|-----|------|------|

| V_Sys             | Main power supply voltage                        | 9    | 12  | 28   | V    |

| 5V0_A1,<br>5V0_A2 | Power supply voltage 5.0 V                       | 4.5  | 5.0 | 5.5  | V    |

| 3V3               | Power supply voltage 3.3 V                       | 3.0  | 3.3 | 3.6  | V    |

| VIO               | I/O supply voltage 1.8 V/3.3 V                   | 1.65 | 1.8 | 1.95 | V    |

|                   |                                                  | 3.0  | 3.3 | 3.6  | V    |

| T <sub>A</sub>    | Ambient operating temperature                    | - 40 | -   | + 95 | °C   |

| Ripple Noise      | Peak-to-peak voltage ripple on 3V3 supply lines  | -    | -   | 175  | mV   |

|                   | Peak-to-peak voltage ripple on 5V0 supply lines. |      |     | 125  | mV   |

|                   |                                                  |      |     |      |      |

## **Table 3: Operating conditions**

| Symbol           | Description         | Conditions                | Тур                  | Max.             | Unit |

|------------------|---------------------|---------------------------|----------------------|------------------|------|

| V <sub>IH</sub>  | Input high voltage  |                           | 0.7*VIO <sup>1</sup> | VIO <sup>1</sup> | V    |

| V <sub>IL</sub>  | Input low voltage   |                           | -0.3                 | 0.6²             | V    |

| V <sub>HYS</sub> | Input hysteresis    |                           | 0.18                 | -                | V    |

| V <sub>OH</sub>  | Output high voltage | I <sub>o</sub> max = 5 mA | VIO - 0.4            | -                | V    |

| V <sub>OL</sub>  | Output low voltage  | I₀max = -5 mA             | -                    | 0.4              | V    |

Table 4: Digital pad ratings

$<sup>^{\</sup>rm 1}$  1PPS pad always uses 1.8 V internally generated IO supply regardless of the VIO pad voltage.

$<sup>^{2}</sup>$  RSTn pad is internally pulled high to VIO voltage by 100k. During reset, it should be below 0.2 V.

## 2 Getting started

The basic steps to evaluate the VERA-P1 series modules using the EVK-VERA-P174 evaluation kit are provided below:

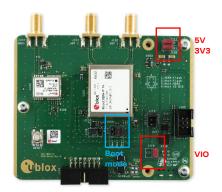

Make sure that jumpers are placed on the current measurement pin headers on the main board as shown in Figure 2. The jumpers for 5 V, 3.3 V, and 1.8 V supply must be placed on the power supply board to use the on-board voltage regulators. The jumper for VIO voltage selection on the power supply board is set to 3.3 V by default. See the description on the back of the board for the jumper locations.

Figure 2: Jumper locations on the main board

- 2. Place jumpers on Boot 0 and Boot 1 to select the USB DFU boot mode.

- 3. Connect two external 5.9 GHz antennas to the SMA antenna connectors of the VERA-P1 series module.

- Always make sure that the RF ports are properly terminated to a 50 Ω load such as an antenna, spectrum analyzer or 802.11p receiver. If you directly connect the RF ports of the two EVK-VERA-P174 evaluation kits, include a minimum attenuation of 50 dB, to avoid damage to the modules.

- 4. Connect a 9 28 V, 12 W power adapter to the  $2.5 \times 5.5 \text{ mm}$  barrel power connector ( $\bigcirc \bigcirc \bigcirc$ ) on the power supply board. The power and reset LEDs will be on.

- 5. Connect the micro USB connector on the power supply board to a host processor or a PC. The USB LED will be on.

- 6. Follow the quick start instructions in section 4.1 to build the Linux driver and applications for the VERA-P1 series modules and download the firmware to the VERA-P1 series module.

## 3 Board description

This section describes the EVK-VERA-P174 evaluation board, the available connectors, and configuration settings.

## 3.1 Block diagram

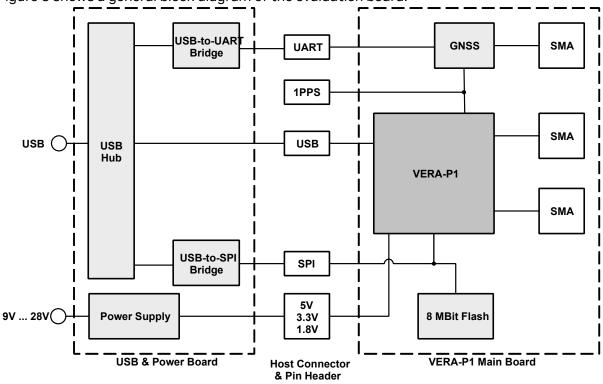

Figure 3 shows a general block diagram of the evaluation board.

Figure 3: Block diagram of the EVK-VERA-P174 evaluation board

## 3.2 Overview

Table 5 lists the available connectors on the upper main board of the EVK-VERA-P174 and their functions. Table 6 lists the available connectors on the lower power supply board of the EVK-VERA-P174 and their functions.

## 3.2.1 Main board

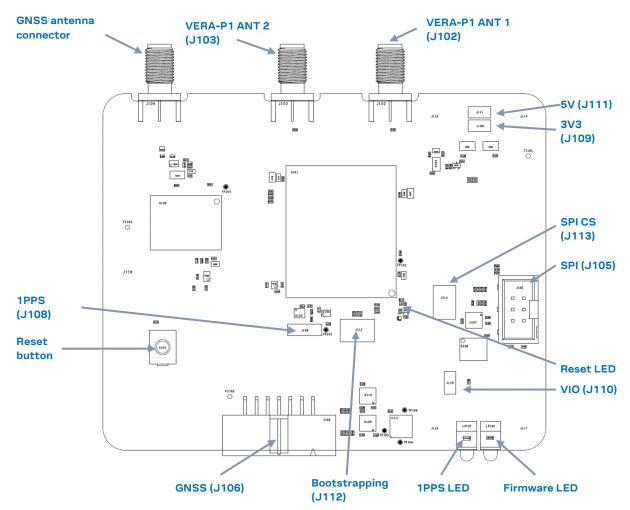

Figure 4: EVK-VERA-P1 Main board assembly overview

| Designator | Connector                | Description                                                                      |

|------------|--------------------------|----------------------------------------------------------------------------------|

| J112       | Bootstrapping            | Jumpers to select the VERA-P1 boot mode                                          |

| J105       | SPI                      | SPI interface connector                                                          |

| J108       | 1PPS                     | Jumper and connector for the internal or external 1PPS signal                    |

| J109       | 3V3 current measure      | Pin header to measure current on 3V3 rail                                        |

| J110       | VIO current measure      | Pin header to measure current on VIO rail                                        |

| J111       | 5V current measure       | Pin header to measure current on 5V rail                                         |

| J102       | ANT1                     | SMA connector for antenna 1 of VERA-P1                                           |

| J103       | ANT2                     | SMA connector for antenna 2 of VERA-P1                                           |

| J113       | SPICS                    | Jumper to configure SPI chip select routing between VERA-P1, SPI flash, and host |

| J104       | GNSS antenna             | SMA connector for the GNSS antenna                                               |

| J106       | GNSS connector           | Connector for GNSS UART/1PPS signals                                             |

| J101       | Host interface connector | Board-to-board connector to the power supply board                               |

Table 5: EVK-VERA-P174 Main board connector description

## 3.2.2 USB and power supply board

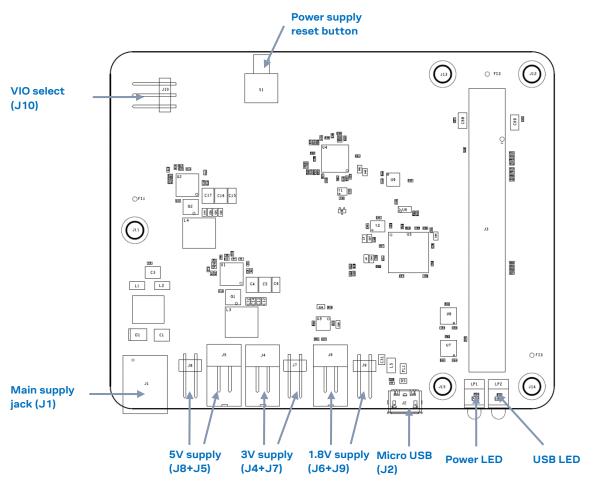

Figure 5: USB Power supply board assembly overview

| Designator | Connector                | Description                                                                                                |

|------------|--------------------------|------------------------------------------------------------------------------------------------------------|

| J1         | Main supply              | 2.5 x 5.5 mm barrel connector for 9 – 28 V power supply<br>Connect jumpers J7, J8, J9 and J10 before using |

| J8         | Jumper for 5 V supply    | Disconnect to use external 5 V supply on J5                                                                |

| J7         | Jumper for 3.3 V supply  | Disconnect to use external 3.3 V supply on J4                                                              |

| J5         | External 5 V supply      | Connector for external 5 V supply                                                                          |

| J4         | External 3.3 V supply    | Connector for external 3.3 V supply                                                                        |

| J10        | VIO select               | Jumper to select VIO voltage 1.8 V or 3.3 V                                                                |

| J9         | Jumper for 1.8 V supply  | Disconnect to use external 1.8 V supply on J6                                                              |

| J6         | External 1.8 V supply    | Connector for external 1.8 V supply                                                                        |

| J2         | Micro USB                | USB interface connector                                                                                    |

| J3         | Host interface connector | Board-to-board connector to the main board                                                                 |

Table 6: EVK-VERA-P174 Power supply board connector description

## 3.3 Connectors

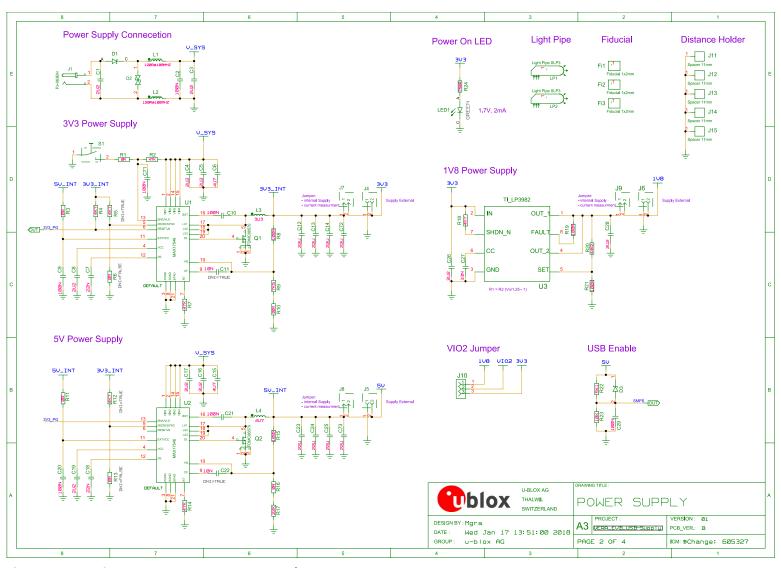

## 3.3.1 Power supply and configuration

The VERA-P1 module is supplied with  $3.3\,\mathrm{V}$ ,  $5\,\mathrm{V}$ , and a VIO that can be either  $3.3\,\mathrm{V}$  or  $1.8\,\mathrm{V}$ . Power supply for the evaluation board is provided through a DC power jack connector (J1) with an input voltage of  $9-28\,\mathrm{V}$ .

All supply voltages can be generated from the on-board DC-DC converters and LDO regulators or supplied externally via the connectors J5 (5 V), J4 (3.3 V) and J6 (1.8 V) of the power supply board. Disconnect the jumpers J8, J7 or J9 on the power supply board to use the external power supply connectors. The VIO voltage for the VERA-P1 module can be selected with jumper J10 on the power supply board between 1.8 V and 3.3 V.

Individual current consumption on the 3.3 V, 5 V, and VIO rails of the VERA-P1 module can be measured with the respective pin headers J109, J111, and J110 on the main board.

## 3.3.2 USB interface

The USB host communication for the VERA-P1 module is provided through the micro USB connector J2 on the power supply board. The connector J2 is connected to a USB 2.0 hub on the power supply board, which connects the USB port to the following downstream devices:

- The USB interface of the VERA-P1 module on the main board

- The u-blox NEO-M8U GNSS module on the main board via a USB-to-UART bridge (FT234XD-T)

- The SPI interface of the VERA-P1 module or on-board SPI flash on the main board via a USB-to-SPI bridge (FT2232H port A)

## 3.3.3 Bootstrapping

The bootstrapping jumper J112 on the main board is used to select the boot mode of the VERA-P1 module. The valid bootstrap options are listed in Table 7. To set a logic level 0, connect the boot pin with a jumper to GND. Leave the pin open for logic level 1.

| Boot mode  | Boot 2 | Boot 1 | Boot 0 | Description                                                                                                                                      |

|------------|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI master | 1      | 1      | 0      | VERA-P1 acts as an SPI master and automatically downloads a bootloader or firmware from an SPI flash.                                            |

| SPI slave  | 1      | 0      | 1      | Firmware download is under the control of an external SPI master.<br>VERA-P1 acts as SPI slave.                                                  |

| USB-DFU    | 1      | 0      | 0      | USB Device Firmware Upgrade (DFU) boot mode. The VERA-P1 module presents itself on the USB bus as a DFU device for downloading the SDR firmware. |

Table 7: Boot mode configuration

The EVK-VERA-P174 contains an on-board SPI flash to support the SPI master boot option. See section 3.3.5 for further configuration of the SPI chip select routing options.

## 3.3.4 SPI interface

The SPI interface connector J105 on the main board can be used to connect to the SPI interface of the VERA-P1 module or the on-board SPI flash. The SPI chip select jumpers are used to select either the VERA-P1 module or the SPI flash.

| Pin No. | Assignment      |

|---------|-----------------|

| 1       | SPI data MISO   |

| 2       | VIO             |

| 3       | SPI clock       |

| 4       | SPI data MOSI   |

| 5       | SPI chip select |

| 6       | GND             |

## 3.3.5 SPI chip select

The EVK-VERA-P174 contains an 8 Mbit SPI flash (SST25VF080B), which can be used to store the radio firmware or a different bootloader for the VERA-P1 module. The SPI chip select pin header (J113) on the main board is used to configure the routing of the SPI chip select signal between the VERA-P1, host, and SPI flash. Table 8 shows the possible configurations:

| SPI CS routing              | Jumper settings <sup>3</sup><br>(J113) | Description                                                                                                                                                                                                     |

|-----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host to flash via USB       | 2(1-3)                                 | Used to program the flash from the host over USB. The SPI flash is accessible via the USB interface on the power supply board. A USB-to-SPI bridge (FT2232H) connects the SPI flash to the USB.                 |

| Host to flash via J105      | 2(1-3), 4(5-6)                         | Used to program the flash from the host directly over SPI. The SPI flash is accessible via the SPI interface connector or the host interface connector. Jumper on 5-6 is used to disable the USB-to-SPI bridge. |

| VERA-P1 to flash            | 1 (1-2), 4 (5-6)                       | Used to connect VERA-P1 to the SPI flash for firmware or bootloader download, when boot mode "SPI master" is selected (see 3.3.3).                                                                              |

| Host to VERA-P1 via<br>J105 | 3(2-4), 4(5-6)                         | Used to connect VERA-P1 to the host over SPI, when boot mode "SPI slave" is selected (see 3.3.3). The VERA-P1 SPI interface is accessible via the SPI interface connector or the host interface connector.      |

Table 8: SPI Chip select configuration

#### 3.3.6 1PPS interface

A 1PPS UTC reference signal is required by the IEEE1609.4 MAC inside the module to align transmissions during channel switching and timekeeping. The 1PPS pin header J108 on the main board can be used to connect the 1PPS signal from the on-board NEO-M8U GNSS receiver to the 1PPS signal input of the VERA-P1 module.

Place a jumper on pins 1 and 2 of the 1PPS pin header to connect the 1PPS signal from the NEO-M8U GNSS module to the VERA-P1 module. The Pin 2 (VERA-P1 1PPS) and 3 (GND) can be used to connect a 1PPS signal from an external GNSS to the VERA-P1 module. The signal level for the external 1PPS can be in the range from 1.8-5 V and is converted to 1.8 V via a level shifter.

## 3.3.7 GNSS interface

The signals of the GNSS UART and 1PPS signal are available on the connector J106.

UBX-17048707 - R08 Board description Page 13 of 31 C1 Public

$<sup>^{\</sup>rm 3}$  Italic number is the designation as printed on the EVK

| Pin No. | Pin name    | Туре   | Level                      | Description                                                               |

|---------|-------------|--------|----------------------------|---------------------------------------------------------------------------|

| 5       | VIO2        | Power  | VIO                        | VIO voltage                                                               |

| 7       | GND         | Ground |                            |                                                                           |

| 10      | 1PPS        | I/O    | I: 1.8 - 5.5 V<br>O: 3.3 V | 1PPS signal output from GNSS (J108 1-2) or input to VERA-P1 (J108 2-3) $$ |

| 11      | NEO_UART_RX | ı      | 0 - 3.3 V                  | GNSS UART RX                                                              |

| 12      | NEO_UART_TX | 0      | 3.3 V                      | GNSS UART TX                                                              |

| 13      | GND         | Ground |                            |                                                                           |

## 3.3.8 SMA connectors

The EVK-VERA-P174 includes two SMA connectors, ANT1 (J102) and ANT2 (J103), which are used to connect external antennas or measurement instruments to the antenna pins of the VERA-P1 module.

A third SMA connector (J104) is included to connect an active antenna to the on-board NEO-M8U GNSS module.

The SMA connectors on the EVK are specified for RF signals up to 18 GHz.

Always ensure that the RF ports of the VERA-P1 module are properly terminated to a 50  $\Omega$  load such as an antenna, spectrum analyzer, or 802.11p receiver. If you directly connect the RF ports of two EVK-VERA-P174 evaluation kits, include a minimum attenuation of 50 dB, to avoid damage to the modules.

## 3.3.9 Host interface connector

The host interface connector is used in the EVK to connect the VERA-P1 main board to the power supply and USB interface board. Additionally, it can be used to connect the VERA-P1 main board directly to a compatible host board. The connector on the main board is a QMS-052-0675-L-D-PC4 and the counterpart on the power supply board is a QFS-052-0675-L-D-PC4.

## **3.4 LEDs**

Table 9 lists the available LEDs on the EVK-VERA-P174:

| Name     | Designator | Location                          | Function                                                       |

|----------|------------|-----------------------------------|----------------------------------------------------------------|

| Power    | LED1       | Power supply board                | Indicates 3.3 V supply (LED on)                                |

| USB      | LED2       | Power supply board                | Indicates USB connection to the host (LED on)                  |

| Reset    | LED103     | Main board, near pin 1 of VERA-P1 | Indicates VERA-P1 module in reset (LED off)                    |

| 1PPS     | LED102     | Main board                        | Indicates 1PPS signal (LED blinking)                           |

| Firmware | LED101     | Main board                        | Indicates firmware loaded (LED on) through current measurement |

**Table 9: LED Description**

## 3.5 Buttons

The reset button on the main board (S101) resets the VERA-P1 module. The button on the power supply board (S1) is used to reset the on-board power supply for the EVK.

## 3.6 Design files

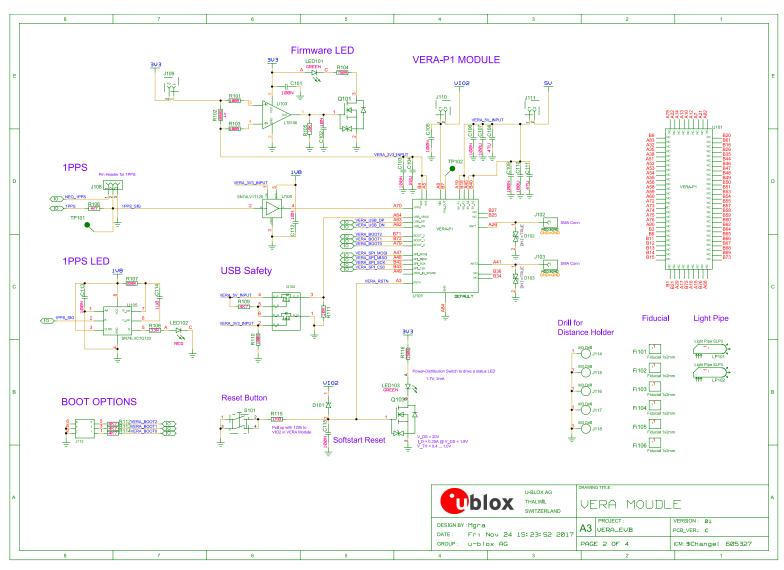

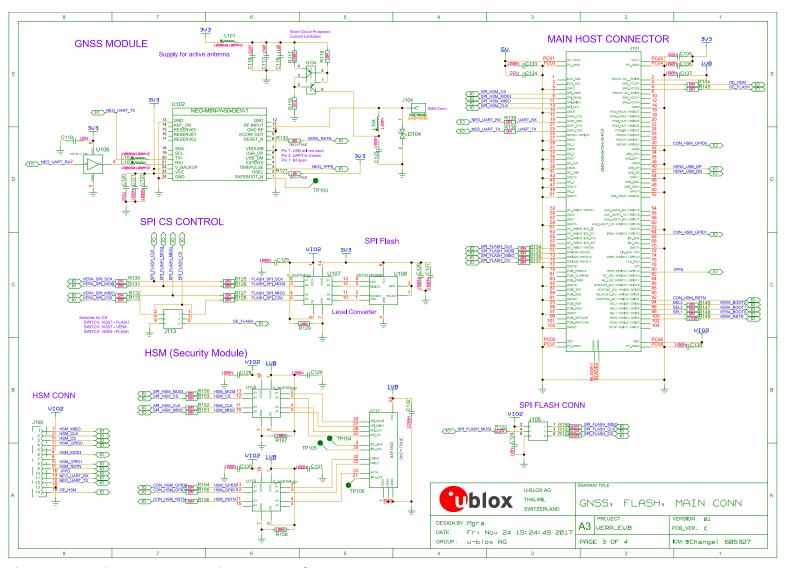

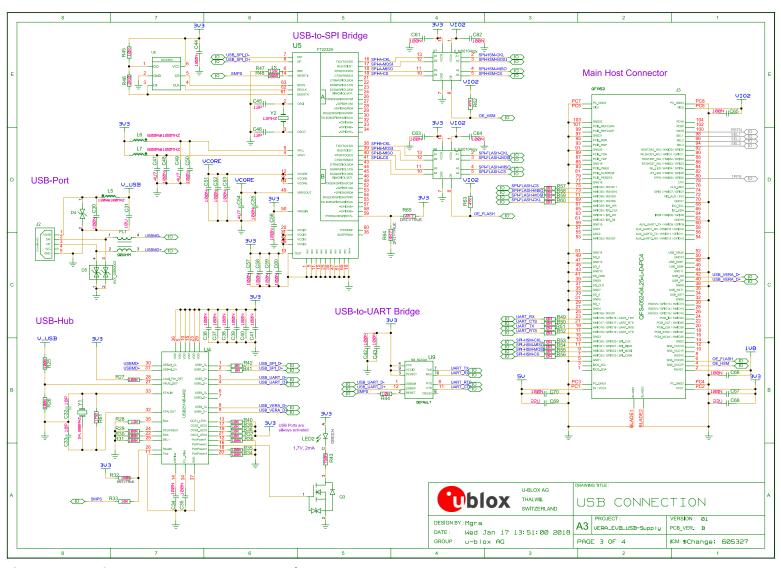

The schematics for the EVK-VERA-P174 are shown in Figure 6 and Figure 7. Full design files are also available via u-blox support. To obtain these documents, send an email to the support team email address for your area, as listed in the Contact section.

**Figure 6: Schematic of the VERA-P1 main board, page 1/2**UBX-17048707 - R08

Board description

C1 Public

Figure 7: Schematic of the VERA-P1 main board, page 2/2

Figure 8: Schematic of the power supply board, page 1/2

Figure 9: Schematic of the power supply board, page 2/2

## **Software**

A standalone software package for the VERA-P1 modules called "LLC Remote" is available through u-blox support. The "LLC Remote" software package contains the following:

- A firmware image that has to be downloaded to the module on system start

- A driver, which is placed between the bus driver and network layer of the V2X stack

- Various test tools and example applications

- Precompiled executables to run on a Linux x86 PC

The LLC driver and part of the tools are provided as source code. The SDR firmware and LLC driver is developed by Cohda Wireless Pty, as a subcontractor of NXP Semiconductors N.V. The release process of the firmware binary and the associated LLC Remote driver implementation is combined with the major release of the Cohda MKx Software Development Kit<sup>4</sup> and the version numbering of the LLC Remote package follows the numbering of the Cohda SDK.

A release notes document with quick start instructions for compiling the software is available with each software package. Recipes for integrating the software package into Yocto-based projects can be provided by u-blox on request.

To evaluate the VERA-P1 series module, the EVK-VERA-P174 can be connected via USB to a native Linux PC or a virtual machine running Linux. For this user guide, a virtual machine running Ubuntu 18.04 LTS with Linux kernel 4.15.0-23-generic (x86\_64) has been used.

## **Quick start instructions**

Copy the LLC Remote package archive into the target Linux development environment. Extract the package content and change to the extracted directory.

```

$ tar -xzf V2X_LLC_Remote_V15.0.0.tar.gz

$ cd llc-remote

```

Run the install.sh script once in a new development environment to automatically install the package dependencies. The script requires system privileges and an active Internet connection for downloading the packages. The main dependencies of the LLC Remote package are:

- dfu-util, for downloading the radio firmware to the module in USB DFU boot mode

- linux-headers, for building the LLC remote driver

- bison, flex, for building the included libpcap library used by the LLC user-space library

```

$ sudo ./install.sh

```

The next step is to run *make* to build the whole software package:

```

$ make

```

If the make process fails because of a missing pcap library, run the following command to create the missing symbolic link to the library and then run make again:

```

$ ln -sr bsp/app/libpcap/$(uname -m)/libpcap.a cohda/app/llc/lib/

```

This will compile and install the following parts:

- cw-llc driver for the active running Linux kernel

- LLC user-space library libLLC.so

Software Page 20 of 31

<sup>&</sup>lt;sup>4</sup> A full SDK supporting IEEE 1609 and ETSI ITS software stacks is available from Cohda Wireless.

LLC user-space tool and plugins<sup>5</sup>

The LLC user-space tool, plugins and library will be installed to the ./bin subdirectory and the cw-llc driver will be copied to the ./drivers/<kernel\_version> subdirectory.

Connect the EVK-VERA-P174 evaluation kit to the PC and connect the USB device to the virtual machine, if required. The VERA-P1 module enumerates itself on the USB as "NXP SAF510x DFU" device with the USB device ID 1fc9:0102, which can be checked using the *Isusb* command:

```

$ lsusb

Bus 001 Device 002: ID 1fc9:0102 NXP Semiconductors

```

Run the *load* script to detect the VERA-P1 module and download the radio firmware through USB via the Device Firmware Update (DFU) protocol, if required. If prompted for a firmware, select option 2 to download the SDRMK5Dual.bin for evaluation of VERA-P174 or option 4 to select SDRMK5Single.bin for evaluation of VERA-P173.

```

$ ./load

Load SAF5X00 firmware via DFU-util

** NOTE: dfu-util may fail under VMWare; you may need to unplug your board after

download and restart ./load **

1] DFUBootLoader.bin

21 SDRMK5Dual.bin

3] SDRMK5DualSPI.bin

4] SDRMK5Single.bin

Select file to download (1-4): 2

Using firmware file images/SDRMK5Dual.bin

[sudo] password for user:

dfu-util 0.9

Copyright 2005-2009 Weston Schmidt, Harald Welte and OpenMoko Inc.

Copyright 2010-2016 Tormod Volden and Stefan Schmidt

This program is Free Software and has ABSOLUTELY NO WARRANTY

Please report bugs to http://sourceforge.net/p/dfu-util/tickets/

dfu-util: Invalid DFU suffix signature

dfu-util: A valid DFU suffix will be required in a future dfu-util release!!!

Deducing device DFU version from functional descriptor length

Opening DFU capable USB device...

ID 1fc9:0102

Run-time device DFU version 0100

[...]

DFU mode device DFU version 0100

Device returned transfer size 4096

Copying data from PC to DFU device

Download [==========] 100% 436316 bytes

Download done.

state(8) = dfuMANIFEST-WAIT-RESET, status(0) = No error condition is present

dfu-util: can't detach

Resetting USB to switch back to runtime mode

```

In case of a virtual machine environment, repeat to run the *load* script until the cw-llc driver module is loaded. As the USB device changes roles after firmware download, ensure that the new 802.11p radio device with the USB device ID 1fc9:0103 is automatically connected to the virtual machine.

Once the device is properly detected, the *load* script will display an output as shown below:

```

$ ./load

0

```

<sup>&</sup>lt;sup>5</sup> LLC plugins for channel configuration, sending, and receiving packets are provided as source code. Other plugins are provided as binary only.

```

Echo loading cw-llc module for kernel 4.15.0-23-generic_x86_64

cw_llc 143360 0

1

LLC 4

```

Kernel crashes have been observed in some cases when loading the driver on systems where NetworkManager is running. In such a case, either stop the NetworkManager before loading the driver via

```

sudo systemctl stop NetworkManager.service

```

or configure it to ignore the LLC IPv6 interfaces by adding the following lines to /etc/NetworkManager/NetworkManager.conf:

```

[keyfile]

```

unmanaged-devices=interface-name:llc-\*

Then, restart the NetworkManager service via

sudo systemctl restart NetworkManager.service

Execute the "Ilc version" command to check the connection to the module and to verify the firmware version:

```

$ ./bin/llc version

WISPA Variant : TEF5200

: 0x0

WISPA Version

PCB Version

PCB Load

: 1

Boot Pins

: 0xc

SDR Firmware

: 69189

SDR Revision Date : 2018-01-22 12:14

SDR Build Date : 2018-01-22 12:15

Security Accel. : No

Antenna Mask

: 3

Radio B Present : 1

Last Reset Source: External (36, 1024)

Last Reset Source : External (53, 1024)

Last Reset Source : External (54, 1024)

```

The llc tool and plugins require the shared library - *libLLC* so that it can be located by the run-time linker. This is set up during the make process by calling *ldconfig* with the library path and could be overwritten during system startup. In this case, *ldconfig* must be called manually again:

```

$ sudo ldconfig $(realpath ./bin)

```

## 4.2 Module calibration

The EVK-VERA-P174 modules do not contain valid calibration settings. The calibration must be performed manually, by executing Ilc commands after each power cycle and loading of the firmware.

The instruction for loading the calibration parameters and calibration files for the EVK-VERA-P174 modules are provided in the VERA-P1 series system integration manual [2].

## 4.3 Usage examples

After loading the firmware and the LLC driver, basic tests can be performed using the LLC tool and the provided plugins. The LLC tool and plugins are installed in the ./bin subdirectory. A list of the available commands or plugins can be obtained by running the following command:

```

$ ./llc -c

```

Some basic plugins and their purpose are described in Table 10.

| Plugin    | Description                                                                                                                      |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| count     | Displays the transmit and receive counters for both radios                                                                       |  |  |  |

| config    | Displays the configuration (mode/antenna/freq) of both radios                                                                    |  |  |  |

| txqueue   | Displays the state of the Tx MAC, together with the counts of all of the queues                                                  |  |  |  |

| status    | Displays the instantaneous status of the radio, including the number of packets that are queued and also the state of the medium |  |  |  |

| cfg       | Command to read or write the current RadioConfig data, as stored in the baseband                                                 |  |  |  |

| version   | Reports the version details of the SDR firmware image                                                                            |  |  |  |

| dmesg     | Displays the debug print messages of the ARM/VDSP1/VDSP2 processor                                                               |  |  |  |

| rxphylast | Displays details of the last received frames by the PHY                                                                          |  |  |  |

| txphylast | Displays details of the last transmitted frames by the PHY                                                                       |  |  |  |

| chconfig  | Sets the channel configuration for both radios                                                                                   |  |  |  |

| test-tx   | Generates and transmits test packets                                                                                             |  |  |  |

| test-rx   | Receives test packets                                                                                                            |  |  |  |

|           |                                                                                                                                  |  |  |  |

Table 10: Description of LLC plugins

The source code for the chconfig, test-rx and test-tx plugins is provided in the cohda/app/llc/plugin/simtdapi subdirectory.

Instructions on how to use the individual commands are printed with the "--help" option.

```

$ ./llc <command-name> --help

```

## 4.3.1 Transmit and receive counters

Use the command "Ilc count" to print out transmit and receive counters for both the radios as shown below.

This command can be used to easily verify the access to the module.

| \$ ./llc count                   |          |          |          |          |

|----------------------------------|----------|----------|----------|----------|

|                                  | RadA Ch0 | RadA Ch1 | RadB Ch0 | RadB Ch1 |

| Tx MAC Unconfigured Frames       | 0        | 0        | 282      | 0        |

| Tx MAC Failed Enqueue            | 0        | 0        | 0        | 0        |

| Tx MAC Broadcast Enqueued Frames | 5331     | 0        | 3        | 0        |

| Tx MAC Broadcast Success Frames  | 5331     | 0        | 2        | 0        |

| Tx MAC Broadcast Failed TTL      | 0        | 0        | 0        | 0        |

| Tx MAC Broadcast Retired Frames  | 5331     | 0        | 2        | 0        |

| Tx MAC Unicast Enqueued Frames   | 0        | 0        | 0        | 0        |

| Tx MAC Unicast RTS/CTS Enq Frame | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Success Frames    | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Failed Retry      | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Failed TTL        | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Retired Frames    | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Retry Frames      | 0        | 0        | 0        | 0        |

| Tx MAC Unicast Ack Frames        | 0        | 0        | 0        | 0        |

| Tx MAC Unicast RTS Frames        | 0        | 0        | 0        | 0        |

| Tx MAC Unicast CTS Frames        | 0        | 0        | 0        | 0        |

| Tx PHY Frames                    | 5332     | 0        | 3        | 0        |

| Tx PHY Aborted Frames            | 2        | 0        | 0        | 0        |

| Tx PHY Aborted Resp (Ack/CTS/)   | 0        | 0        | 0        | 0        |

| Rx PHY AGC Firings               | 0        | 0        | 0        | 0        |

| Rx PHY Acquisitions              | 0        | 2765     | 0        | 0        |

| Rx PHY Failed SF                 | 0        | 2        | 0        | 0        |

| Rx PHY Valid SF Frames           | 0        | 2763     | 0        | 0        |

| Rx MAC Failed FCS                | 0        | 0        | 0        | 0        |

| Rx MAC Valid Matched RTS Frames  | 0        | 0        | 0        | 0        |

| Rx MAC Valid Unmatched RTS Frame | 0        | 0        | 0        | 0        |

| Rx MAC Valid Matched CTS Frames  | 0    | 0    | 0 | 0 |  |

|----------------------------------|------|------|---|---|--|

| Rx MAC Valid Unmatched CTS Frame | 0    | 0    | 0 | 0 |  |

| Rx MAC Valid Data Frames         | 0    | 2763 | 0 | 0 |  |

| Rx MAC Valid Matched Ack Frames  | 0    | 0    | 0 | 0 |  |

| Rx MAC Valid Unmatched Ack Frame | 0    | 0    | 0 | 0 |  |

| Rx MAC Valid Matched Late Ack Fr | 0    | 0    | 0 | 0 |  |

| Rx MAC Broadcast Frames          | 0    | 2763 | 0 | 0 |  |

| Rx MAC Address Matched Frames    | 0    | 0    | 0 | 0 |  |

| Rx MAC Address Dropped Frames    | 0    | 0    | 0 | 0 |  |

| Rx MAC Buffer Overflow Frames    | 0    | 0    | 0 | 0 |  |

| Rx MAC Duplicate Frames          | 0    | 0    | 0 | 0 |  |

| Rx MAC USB Transferred Frames    | 0    | 2763 | 0 | 0 |  |

| Rx MAC USB Callbacks             | 2763 | 0    | 0 | 0 |  |

| CS Active Firings                | 2    | 2751 | 0 | 0 |  |

| CS Idle Firings                  | 2    | 40   | 0 | 0 |  |

| CCA Active Firings               | 0    | 51   | 0 | 0 |  |

| CCA Idle Firings                 | 0    | 2765 | 0 | 0 |  |

| Rx Frame Firings                 | 0    | 2765 | 0 | 0 |  |

## 4.3.2 Channel configuration

Two different channel configurations are available per radio on the VERA-P1, which can be configured by using the *chconfig* LLC plugin via the Control Channel (CCH) or Service Channel (SCH). The plugin uses the LLC Remote API to set up, start, stop, or get the CCH/SCH configurations.

The following example configures and starts the control channel (radio channel configuration 0) on radio A, channel 184, using both the antennas:

## 4.3.3 Transmitter test

The *test-tx* LLC plugin is used to transmit a burst of packets. The CCH or SCH must be configured prior to transmitting a burst and their settings define the default configuration for the packets.

The following example transmits 100 test packets of 200 bytes length on channel 184 and both antennas, with the output power set to 40 and modulation set to ½ QPSK:

```

TxPwrCtrl: 0

TxPower: 40

TxAntenna[0]: 3

NTxAnt: 1

Expiry: 0

PayloadLength[0]: 200

Destination MAC Address: ff:ff:ff:ff:ff

EtherType: 0x88b5

ChannelNumber: 184

PayloadMode: increment

Source MAC Address: 04:e5:48:00:10:00

Packet Log File:

DumpPayload:

0

· 0

DumpToStdout:

DumpToStdout:

0

Interface:

wave-raw

Tx: Last SeqNum:

10 [/100]. Packet rate: Current

9.6, Target

10.0

Tx: Last SeqNum:

20 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

30 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

40 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

50 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

60 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

70 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

80 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

90 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

90 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

90 [/100]. Packet rate: Current

10.0, Target

10.0

Tx: Last SeqNum:

90 [/100]. Packet rate: Current

10.0, Target

10.0

```

## 4.3.4 Receiver test

The *test-rx* command is used to receive test packets sent by another module via the *test-tx* command. The receiving application periodically informs about the number of received packets, the calculated packet error rate and also dumps per packet and statistics logs. The receive test should be running before starting the transmission to receive all the packets.

The LLC driver supports only one VERA-P1 module connected to the host system. In order to test packet transmission with two modules, two host PCs or virtual machines must be used in parallel.

The following example sets the channel configuration and starts to receive and transmit test packets between two different VERA-P1 modules:

On the receiving side:

```

$ ./llc chconfig -s -w CCH -c 184

$ ./llc test-rx -c 184

```

On the transmitting side, sends 1000 packets at a rate of 100 packets per second:

```

$ ./llc chconfig -s -w CCH -c 184

$ ./llc test-tx -c 184 -a1 -p30 -n1000 -r100

```

The output on the receiver will look like the following:

```

Packet Log File:

Report File:

RxReport.txt

Ω

LogUnMatched:

0

DumpPayload:

DumpToStdout:

ReportPeriod: 100

Filter SA: None

Interface:

wave-raw

ChannelNumber:

184

Rx: Report [Last SeqNum: -1 (0xffffffff)]

Approx PER: -nan% [Missed: 0, Payload Error: 0 / Tx: 0] (264.6% [-67108864, -

1975612572 / -772014096)

Rx: Un/Matched Frames: 0/0

```

```

0

Rx: Report [Last SeqNum: 100 (0x00000064)]

Approx PER: 0.0% [Missed: 0, Payload Error: 0 / Tx: 101] (0.0% [0, 0 / 100)

Un/Matched Frames: 0/101

Channel 184: 00000101 Matched Packets.

# MCS Len Matched Payload Err

11 104

101

101

0

Total

[...]

Rx: Report [Last SeqNum: 999 (0x000003e7)]

Approx PER: 0.0% [Missed: 0, Payload Error: 0 / Tx: 1000] (0.0% [0, 0 / 99)

Un/Matched Frames: 0/1000

Rx:

Channel 184: 00001000 Matched Packets.

# MCS Len

Matched Payload Err

11 104

1000

Λ

1000

0

Total

```

## 4.3.5 LLC native IPv6 functionality

Native IPv6 functionality using the Linux IPv6 stack is supported in the LLC driver since release 15. The driver creates two network interfaces - Ilc-cch-ipv6 and Ilc-sch-ipv6, which can be used for IPv6 communication between two or more VERA-P1 modules. The network interfaces, Ilc-cch-ipv6 and Ilc-sch-ipv6 map to the channel configuration 0 of radio A and radio B respectively. All communicating VERA-P1 modules must be configured to use the same DSRC channel.

The module option IPv6Enabled=1 must be provided when the driver module is loaded to enable IPv6 support. The optional argument, IPv6MCS can be used to set the rate for transmitted IPv6 packets. The module options can be passed to the *load* script in the ./drivers subdirectory, after using the top level load script to download the radio firmware:

```

$ cd drivers; ./load IPv6Enabled=1; cd -

```

The Network Manager in the Linux host system should be deactivated, or the IPv6 configuration of the LLC IPv6 network interfaces should be set to Link-Local only and IPv4 should be disabled, in order to not interfere with the interface configuration.

The *chconfig* plugin is used to configure the DSRC channel on all VERA-P1 modules, for example to set the channel configuration 0 of radio A to channel 180 for communication using the *llc-cch-ipv6* network interface:

```

$ 11c chconfig -s -w CCH -r a -c 180

```

The following commands are used to enable the *llc-cch-ipv6* network interface and to get the automatically assigned link-local IPv6 address:

```

$ ip link set llc-cch-ipv6 up

$ ip addr show llc-cch-ipv6

39: llc-cch-ipv6: <BROADCAST,MULTICAST,UP,LOWER_UP> mtu 1500 qdisc noqueue state

UNKNOWN group default qlen 1000

link/ether fa:8b:7f:64:0e:eb brd ff:ff:ff:ff

inet6 fe80::8a8c:22ae:976d:cdde/64 scope link noprefixroute

valid_lft forever preferred_lft forever

```

The IPv6 address can then be used to send an IPv6 ping request from another VERA-P1 module over the *llc-cch-ipv6* interface:

```

$ ping6 -I llc-cch-ipv6 fe80::8a8c:22ae:976d:cdde

```

The throughput over IPv6 between two VERA-P1 modules can be tested using the iperf3 tool for example. To do this, start the iperf3 server on one side:

\$ iperf3 -s -D

Then start the throughput test on the client side and connect to the IPv6 address of the server:

```

$ iperf3 -6 -c fe80::8a8c:22ae:976d:cdde%llc-cch-ipv6

```

## 4.4 Building the software for a different target platform

Building the LLC Remote package for a different target system requires a toolchain and configured kernel sources for the target platform. The following example shows how to manually cross-compile the LLC driver and tools for an Arm® architecture using the gcc-arm-linux-gnueabi toolchain. The configured kernel sources should be available in the /home/duser/work/linux-3.10.107/directory.

Recipes for integrating the software package into Yocto-based projects can be provided by u-blox on request.

To cross-compile the LLC driver:

```

$ cd cohda/kernel/drivers/cohda/llc

$ make BOARD=mk5 ARCH=arm CROSS COMPILE=arm-linux-gnueabi-

KERNELDIR=/home/duser/work/linux-3.10.107/

```

To cross-compile the LLC tool, library, and plugins<sup>6</sup>:

```

$ cd cohda/app/llc

$ make BOARD=mk5 ARCH=arm CROSS COMPILE=arm-linux-gnueabi- CC=arm-linux-gnueabi-gcc

LD=arm-linux-gnueabi-ld

```

After successful compilation, the following files must be deployed on the target system:

- cohda/app/llc/llc LLC tool

- cohda/app/llc/lib/libLLC.so\* LLC library

- cohda/app/llc/plugin/\*.so LLC plugins (to plugin subdirectory)

- cohda/kernel/drivers/cohda/llc/cw-llc.ko LLC kernel module

- cohda/kernel/drivers/cohda/llc/SDRMK5\*.bin SDR firmware images

The dfu-util tool is required on the target system to download the SDR firmware to the VERA-P1 module.

Software Page 27 of 31

<sup>6</sup> Not all plugins are provided as source code. The Binary plugins are available only for i686, x86-64 and mk5 (Arm) architectures.

# A Glossary

| Abbreviation | Definition                                        |  |  |  |

|--------------|---------------------------------------------------|--|--|--|

| 1PPS         | 1 Pulse Per Second                                |  |  |  |

| API          | Application Programming Interface                 |  |  |  |

| CMOS         | Complementary Metal-Oxide-Semiconductor           |  |  |  |

| DFU          | Device Firmware Upgrade                           |  |  |  |

| DSRC         | Dedicated Short Range Communication               |  |  |  |

| ETSI         | European Telecommunications Standards Institute   |  |  |  |

| EVB          | Evaluation Board                                  |  |  |  |

| EVK          | Evaluation Kit                                    |  |  |  |

| IEEE         | Institute of Electrical and Electronics Engineers |  |  |  |

| ITS          | Intelligent Transport Systems                     |  |  |  |

| GNSS         | Global Navigation Satellite System                |  |  |  |

| GPS          | Global Positioning System                         |  |  |  |

| MAC          | Medium Access Control                             |  |  |  |

| LLC          | Logical Link Control                              |  |  |  |

| os           | Operating System                                  |  |  |  |

| PC           | Personal Computer                                 |  |  |  |

| PHY          | Physical Layer                                    |  |  |  |

| QPSK         | Quadrature Phase-Shift Keying                     |  |  |  |

| RF           | Radio Frequency                                   |  |  |  |

| SDK          | Software Development Kit                          |  |  |  |

| SDR          | Software Defined Radio                            |  |  |  |

| USB          | Universal Serial Bus                              |  |  |  |

| UTC          | Coordinated Universal Time                        |  |  |  |

| V2X          | Vehicle-to-Everything                             |  |  |  |

Table 11: Explanation of the abbreviations and terms used

## **Related documents**

- [1] VERA-P1 series data sheet, UBX-17004377

- [2] VERA-P1 series system integration manual, UBX-17006502

- [3] CohdaMobility MKx Radio LLCremote API Specification, CWD-MKx-0208

For regular updates to u-blox documentation and to receive product change notifications, register on our homepage (www.u-blox.com).

# **Revision history**

| Revision | Date        | Name             | Comments                                                                                                                                     |

|----------|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| R01      | 24-Aug-2017 | mzes, shoe, kgom | Initial release.                                                                                                                             |

| R02      | 20-Oct-2017 | mzes, kgom       | Removed references to VERA-P175.                                                                                                             |

| R03      | 25-Apr-2018 | shoe             | Fixed a typo in the calibration command in section 4.2.                                                                                      |

| R04      | 22-Jun-2018 | mzes, kgom       | Updated for Rev B of the evaluation board. Removed references to VERA-P171.                                                                  |

| R05      | 20-Jul-2018 | mzes             | Updated calibration sequence in section 4.2. Added iperf3 instructions in section 4.3.5.                                                     |

| R06      | 17-Apr-2019 | mzes             | Included a note with respect to Kernel crashes and workaround in section 4.1. Removed references to Hardware Security Module (HSM) from NXP. |

| R07      | 9-Jul-2019  | mzes             | Modified the size of the barrel connector in section 2 (step 4) and section 3.2.2 (first row in Table 6).                                    |

| R08      | 6-Nov-2020  | mzes             | Replaced calibration instructions in section 4.2 with a reference to the SIM.                                                                |

## Contact

For complete contact information, visit us at www.u-blox.com.

#### u-blox Offices

#### North, Central and South America

#### u-blox America, Inc.

Phone: +1 703 483 3180 E-mail: info\_us@u-blox.com

### **Regional Office West Coast:**

Phone: +1 408 573 3640 E-mail: info\_us@u-blox.com

#### **Technical Support:**

Phone: +1 703 483 3185 E-mail: support@u-blox.com

### Headquarters Europe, Middle East, Africa

#### u-blox AG

Phone: +41 44 722 74 44

E-mail: info@u-blox.com

Support: support@u-blox.com

#### Asia, Australia, Pacific

#### u-blox Singapore Pte. Ltd.

Phone: +65 6734 3811

E-mail: info\_ap@u-blox.com

Support: support\_ap@u-blox.com

#### Regional Office Australia:

Phone: +61 2 8448 2016

E-mail: info\_anz@u-blox.com

Support: support\_ap@u-blox.com

## Regional Office China (Beijing):

Phone: +86 10 68 133 545

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

## Regional Office China (Chongqing):

Phone: +86 23 6815 1588

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

#### Regional Office China (Shanghai):

Phone: +86 21 6090 4832 E-mail: info\_cn@u-blox.com Support: support\_cn@u-blox.com

#### Regional Office China (Shenzhen):

Phone: +86 755 8627 1083

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

## Regional Office India:

Phone: +91 80 405 092 00

E-mail: info\_in@u-blox.com

Support: support\_in@u-blox.com

## Regional Office Japan (Osaka):

Phone: +81 6 6941 3660

E-mail: info\_jp@u-blox.com

Support: support\_jp@u-blox.com

#### Regional Office Japan (Tokyo):

Phone: +81 3 5775 3850

E-mail: info\_jp@u-blox.com

Support: support\_jp@u-blox.com

## Regional Office Korea:

Phone: +82 2 542 0861

E-mail: info\_kr@u-blox.com

Support: support\_kr@u-blox.com

## Regional Office Taiwan:

Phone: +886 2 2657 1090

E-mail: info\_tw@u-blox.com

Support: support\_tw@u-blox.com