#### **About this document**

#### **Scope and purpose**

This application note describes how to set up a hardware environment for TRAVEO™ T2G MCU family.

#### Intended audience

This application note is intended for hardware designers.

#### **Associated part family**

TRAVEO™ T2G automotive microcontroller

#### Table of contents

### **Table of contents**

| Abou  | ıt this document                               | 1  |

|-------|------------------------------------------------|----|

| Table | e of contents                                  | 2  |

| 1     | Introduction                                   | 5  |

| 2     | Package selection                              | 6  |

| 2.1   | LQFP                                           |    |

| 2.2   | BGA and PBGA                                   |    |

| 3     | Power supply                                   | 7  |

| 3.1   | Power domains                                  | 7  |

| 3.2   | ADC supply pins                                | 7  |

| 3.3   | Power supply variants                          | 7  |

| 3.3.1 | ADC                                            | 7  |

| 3.3.2 |                                                |    |

| 3.4   | Power ON/OFF sequence of power supply domains  |    |

| 3.4.1 |                                                |    |

| 3.4.2 |                                                |    |

| 3.4.3 |                                                |    |

| 3.5   | Power supply circuit                           |    |

| 3.6   | External core supply control                   |    |

| 3.7   | Unused power domains                           |    |

| 4     | Clock system                                   | 11 |

| 4.1   | Clock sources                                  |    |

| 5     | PLL                                            | 12 |

| 5.1.1 |                                                |    |

| 6     | Reset circuit                                  | 13 |

| 6.1   | Reset pin (XRES)                               |    |

| 6.2   | Power supply monitoring                        |    |

| 6.2.1 | 11,                                            |    |

| 6.2.2 | ·                                              |    |

| 6.2.3 | ,                                              |    |

| 6.2.4 |                                                |    |

| 6.2.5 |                                                |    |

| 6.2.6 | ,                                              |    |

| 6.3   | Watchdog reset                                 |    |

| 7     | Ports and non-power pins                       |    |

| 7.1   | Port input/unused pins: General considerations |    |

| 7.1.1 | · · · · · · · · · · · · · · · · · · ·          |    |

| 7.1.2 |                                                |    |

| 7.1.3 | · · · · · · · · · · · · · · · · · · ·          |    |

| 7.1.4 | 1 1/                                           |    |

| 7.2   | Dedicated port pins                            |    |

| 7.3   | Port pin configuration in AUTOSAR MCAL         |    |

| 7.4   | Pins in low-power mode                         |    |

| 7.5   | Latch-up considerations (Switch)               |    |

| 7.5.1 | · · · · · · · · · · · · · · · · · · ·          |    |

| 7.5.2 |                                                |    |

| 7.6   | 5-V-tolerant input pins                        |    |

| 7.7   | Reset behavior of I/O port pins                |    |

| 7.8   | Glitch filtering                               |    |

|       | <u> </u>                                       |    |

### **Table of contents**

| 7.8.1  | Analog filter                                               |    |

|--------|-------------------------------------------------------------|----|

| 7.8.2  | Digital-based filter                                        | 22 |

| 7.9    | Mode pin                                                    | 23 |

| 7.10   | External interrupt input pins                               | 23 |

| 7.11   | Clamping structure of I/O pins with shared analog functions | 24 |

| 7.12   | External supply for the core voltage                        | 25 |

| 7.12.1 |                                                             |    |

| 7.12.2 | 2 Drive output current of "Enable" control pin              | 25 |

| 8      | Flash programming connection                                |    |

| 9      | Debug interface                                             |    |

| 9.1    | Legacy 20-pin IDC JTAG connector                            |    |

| 9.2    | 10-pin Cortex® debug connector                              |    |

| 9.3    | 20-pin Cortex® debug + ETM connector                        |    |

| 9.4    | Termination resistors                                       |    |

| 9.5    | Trace width                                                 | 30 |

| 10     | Clock output function                                       |    |

| 10.1   | Using the EXT_CLK port pin                                  |    |

| 10.2   | Using the alternate function pin                            | 31 |

| 11     | Layout and electromagnetic compatibility                    | 32 |

| 11.1   | General                                                     | 32 |

| 11.2   | Power supply pins                                           | 32 |

| 11.3   | Ground and power supply                                     | 32 |

| 11.4   | Power supply decoupling                                     | 33 |

| 11.4.1 | 1 Placement                                                 | 33 |

| 11.4.2 | 2 I/O domains                                               | 35 |

| 11.5   | Quartz crystal placement and signal routing                 |    |

| 11.5.1 |                                                             |    |

| 11.5.2 | 0                                                           |    |

| 11.5.3 | , 6                                                         |    |

| 11.6   | Component placement                                         |    |

| 11.7   | Signal routing                                              |    |

| 12     | Thermal considerations                                      |    |

| 13     | ADC                                                         |    |

| 13.1   | Filter design considerations for analog inputs              |    |

| 13.1.1 | '                                                           |    |

| 13.1.2 | , ,                                                         |    |

| 13.1.3 | 1 6 61                                                      |    |

| 13.1.4 | 2 - 8 EXI VIIV                                              |    |

| 13.1.5 |                                                             |    |

| 13.1.6 | - LAI - VIIV                                                |    |

| 13.1.7 |                                                             |    |

| 14     | Assembly and package-related PCB design                     |    |

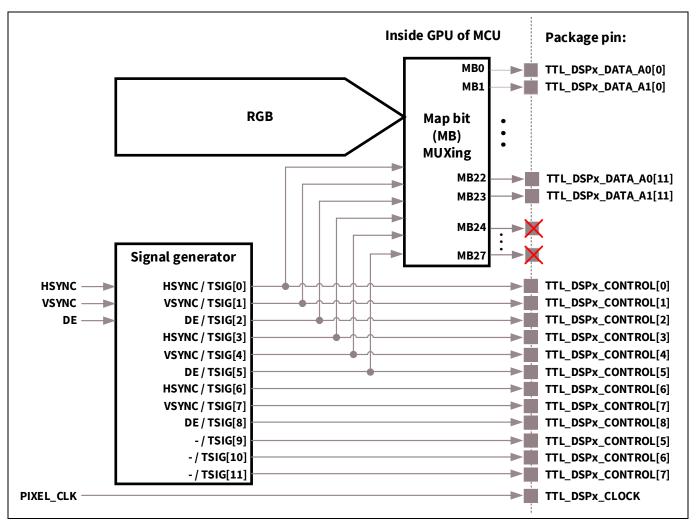

| 15     | Video interface                                             | 50 |

| 15.1   | FPD-link                                                    |    |

| 15.1.1 |                                                             |    |

| 15.1.2 | <del>-</del>                                                |    |

| 15.1.3 | ' '                                                         |    |

| 15.1.4 | ,                                                           |    |

| 15.2   | The PLL power RGB interface                                 |    |

| 15.2.1 | 1 Signal pin configuration                                  |    |

|        |                                                             |    |

#### Table of contents

| 15.3       | MIPI                                                                     | 51  |

|------------|--------------------------------------------------------------------------|-----|

| 15.3.1     |                                                                          |     |

| 15.3.2     |                                                                          |     |

| 15.3.3     | Unused power domain handling                                             | 51  |

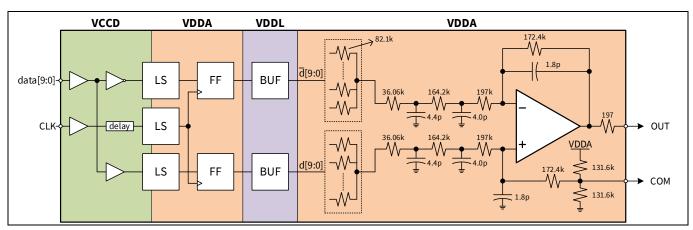

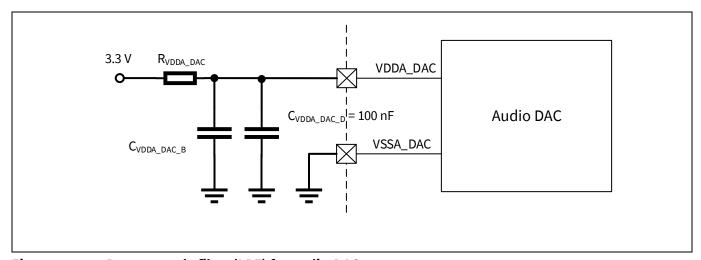

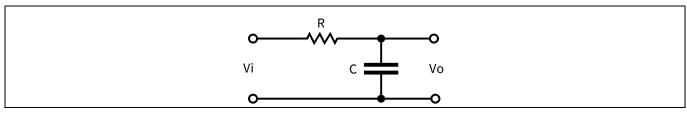

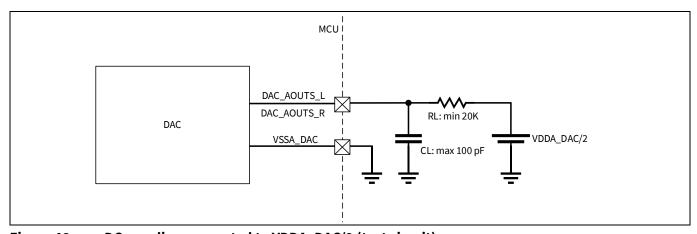

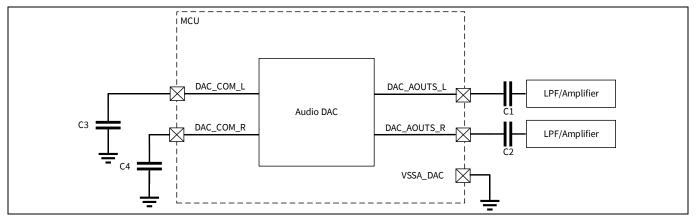

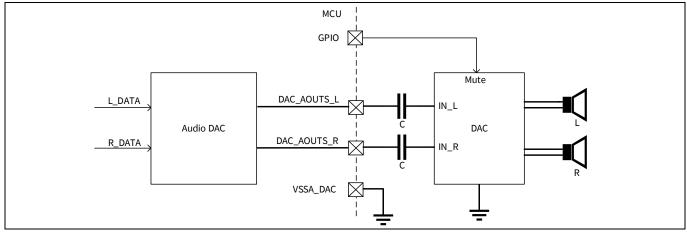

| 16         | Audio-DAC                                                                | 52  |

| <br>16.1.1 |                                                                          |     |

| 16.1.2     | ·                                                                        |     |

| 16.1.2     |                                                                          |     |

| 16.1.3     | •                                                                        |     |

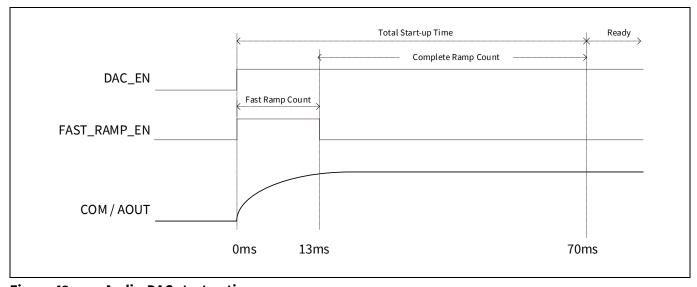

| 16.1.4     | 4 Avoiding the pop noise at the speaker output                           | 56  |

| 17         | Summary                                                                  | 58  |

| 18         | Abbreviations                                                            | 59  |

| 19         | Related documents                                                        | 61  |

| 20         | Appendix A – Power supply concept                                        | 63  |

| 20.1       | Introduction                                                             |     |

| 20.2       | Definitions                                                              | 63  |

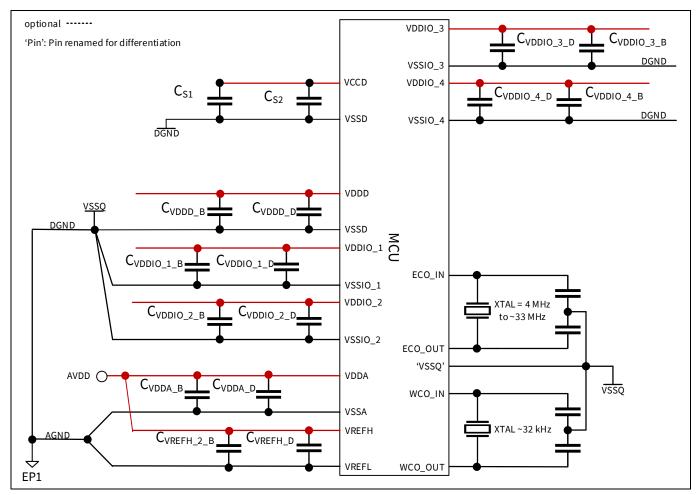

| 20.3       | CYT2B series                                                             | 64  |

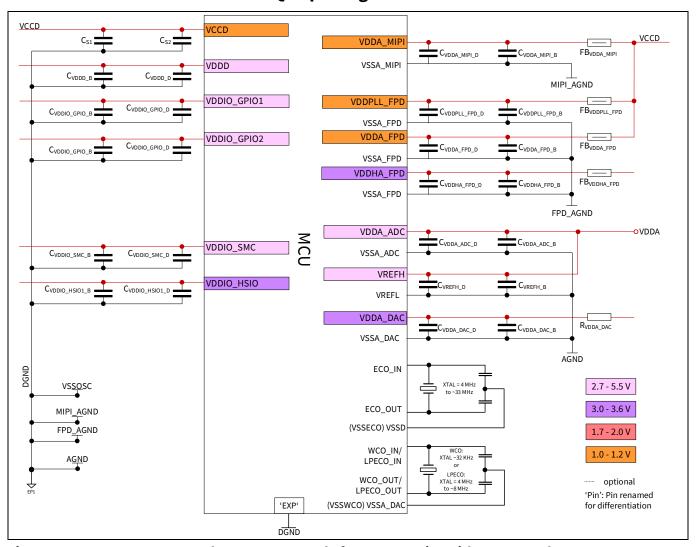

| 20.4       | CYT3B/4B series with TEQFP package                                       | 67  |

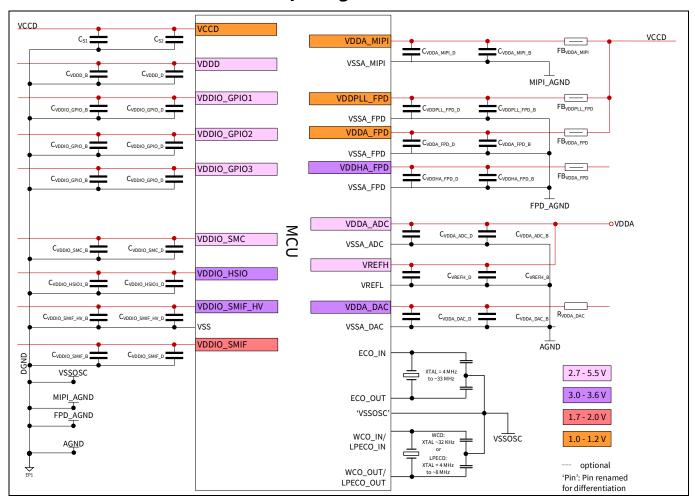

| 20.5       | CYT3B/4B series with BGA package                                         |     |

| 20.6       | CYT3D series with TEQFP package                                          |     |

| 20.7       | CYT4D series with BGA package                                            |     |

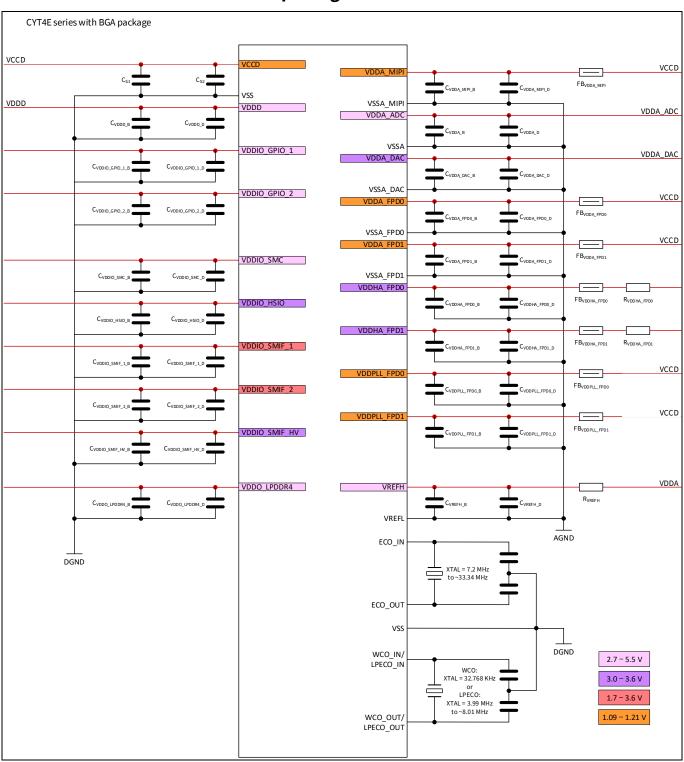

| 20.8       | CYT4E series with BGA package                                            |     |

| 21         | Appendix B – Analog supply                                               |     |

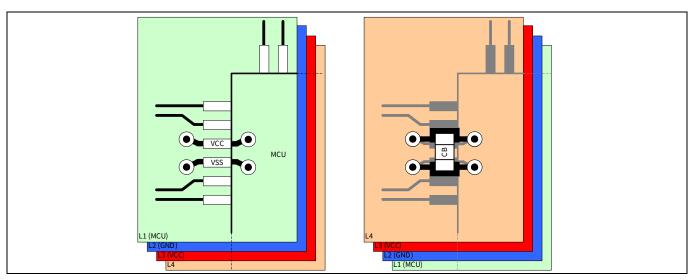

| 22         | Appendix C - Oscillator layout                                           |     |

| 22.1       | QFP packages                                                             |     |

| 22.2       | BGA packages                                                             |     |

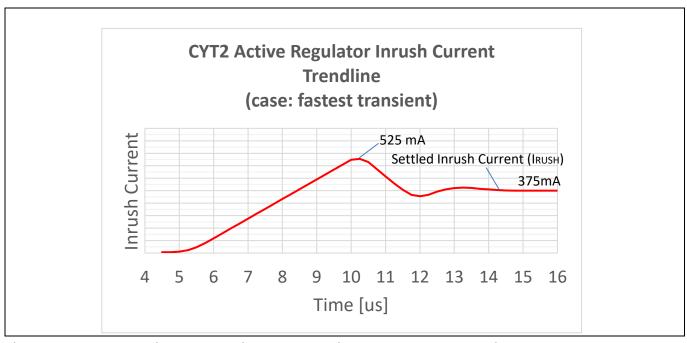

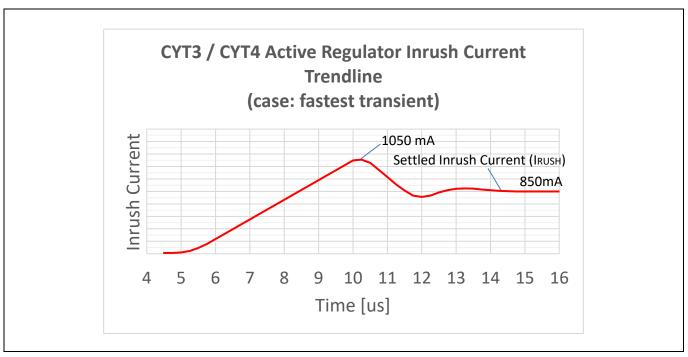

| 23         | Appendix D – Active regulator inrush current                             |     |

| 24         | Appendix E – Unused power domain handling                                |     |

| 24.1       | Introduction                                                             |     |

| 24.2       | CYT2B series                                                             | 91  |

| 24.3       | CYT3B/4B series                                                          | 92  |

| 24.4       | CYT3D Series                                                             | 93  |

| 24.5       | CYT4D Series                                                             |     |

| 24.6       | CYT4E Series                                                             |     |

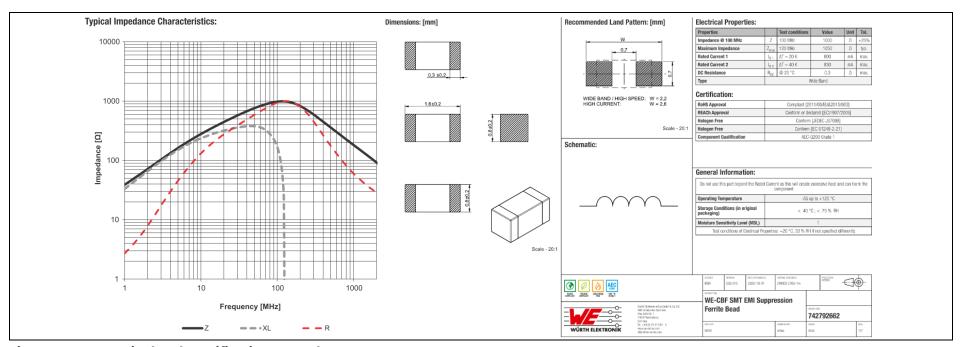

| 25         | Appendix F – Power supply filter characteristics                         | 99  |

| 26         | Appendix G - Clamping structure of I/O pins with shared analog functions |     |

| 26.1       | Introduction                                                             |     |

| 26.2       | CYT2B and CYT3B/4B series                                                | 100 |

| 26.3       | CYT3D series                                                             |     |

| 26.4       | CYT4D series                                                             |     |

| 26.5       | CYT4E series                                                             | 104 |

|            | rian history                                                             | 105 |

Introduction

#### Introduction 1

This document describes how to set up a hardware environment for the TRAVEO™ T2G MCU family.

Design restrictions and recommendations regarding signal wiring and the electrical power system of the MCU are considered. For details on device features and their relevant settings, see the TRAVEO™ T2G architecture technical reference manual (TRM) and the dedicated device datasheet.

This application note answers most of frequent questions. It is not intended to replace the designer's responsibility.

**Package selection**

#### **Package selection** 2

First, decide the package you want to use for your design. Several considerations drive this decision, including number of I/O pins required, PCB and product size, PCB design rules, and thermal and mechanical stresses.

The device families have a very large selection of devices to help match your exact needs in any situation with an efficient and cost-effective solution. Packaging solutions range from the ultra-small wafer scale packages to high-pin-count ball grid array (BGA) packages. Easier to layout on lower layer counts and lower cost PCBs are the leaded quad flat pack (LQFP). LQFP packaging options range from 48-pin devices to 176-pin devices for example.

Some of the package selection criteria are as follows:

#### 2.1 **LQFP**

- Easier to route signals due to large pitch and the open area below the part

- Less mechanical rigidity for more protection against vibration and mechanical stress

- Disadvantages include larger package size and lower thermal conduction ( $\theta_{JA}$ )

#### **BGA and PBGA** 2.2

- Small-scale packages offering high pin counts in larger lead pitches, which significantly reduce the manufacturing complexities for high I/O devices. BGA packages are used in applications requiring:

- Faster circuitry speed because the terminations are much shorter and therefore less inductive and resistive

- Better heat dissipation

- Conventional surface mount technology (SMT) production technologies such as stencil printing and component mounting can be used.

- Robust reflow processing, due to higher pitch (1.27 mm, 0.050", typical), better lead rigidity, and selfalignment characteristics. Self-alignment during reflow is beneficial and opens the process window considerably.

- Disadvantage: X-ray is needed for solder joint inspection.

**Power supply**

#### **Power supply** 3

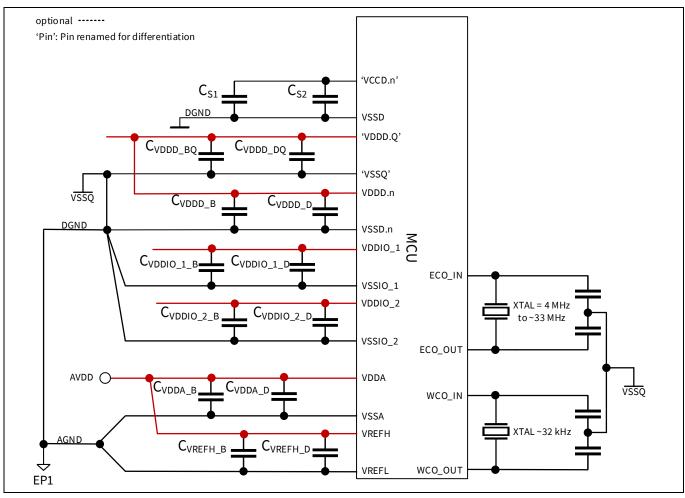

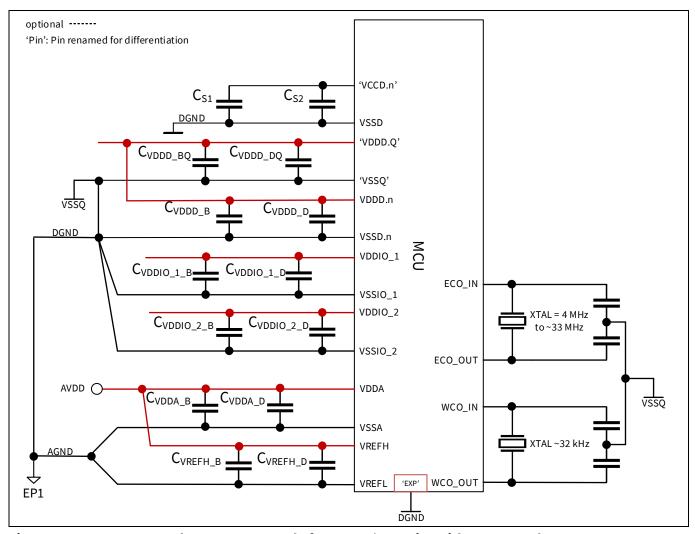

#### 3.1 **Power domains**

MCU power system is based on separate analog and digital supplies. To define a single supply rail, all power supplies should be connected to voltages between 3.3 V and 5.0 V. If you need to apply different power supply voltages, such as 5 V to the analog system (i.e., V<sub>DDA</sub> = V<sub>REFH</sub>) and 3.3 V to V<sub>DDIO</sub> of the MCU port pins, see the operating conditions in the datasheet of the dedicated device.

Devices designed for applications with higher power dissipation require an external core supply source, which is controlled by dedicated MCU pins. See also Appendix A – Power supply concept.

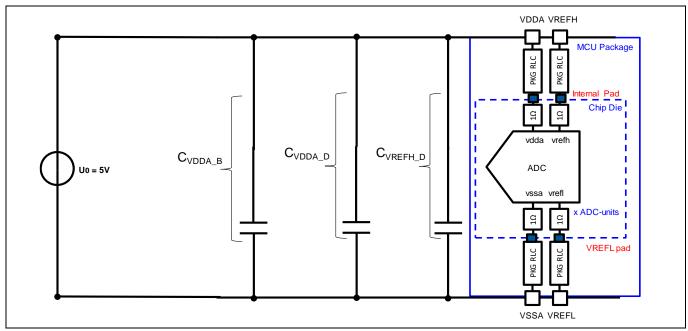

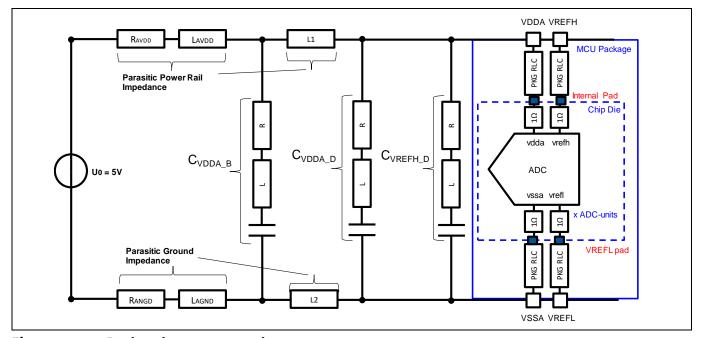

#### **ADC** supply pins 3.2

To avoid additional leakage current, connect the ADC supply pins (VDDA, VSSA, VREFH, and optionally VREFL), even if the ADC is not used.

#### 3.3 **Power supply variants**

Although separate power supplies are provided in the MCU, dependencies between each other must be considered. The power domains are independent of each other.

#### **ADC** 3.3.1

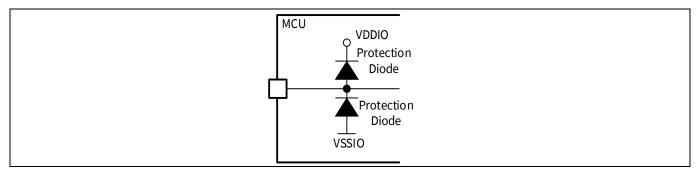

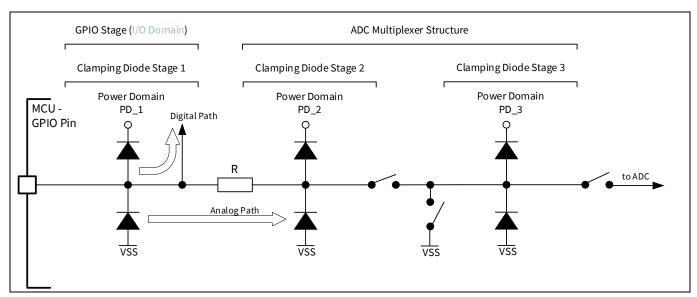

The enabled analog inputs belong to dedicated I/O domains, which means that the applied voltage level of an analog sensor is limited to the I/O domain supply level and the protection diode structure. That means, the analog supplies and the I/O domains of the selected analog inputs must have the same voltage supply level. See Clamping structure of I/O pins with shared analog functions.

#### **Debug connection** 3.3.2

You must select a power supply on which both the debug HW tool and the MCU can communicate with each other. For more information on the HW connection, see Debug interface.

Figure 1 Protection diode structure for all I/O pins

**Power supply**

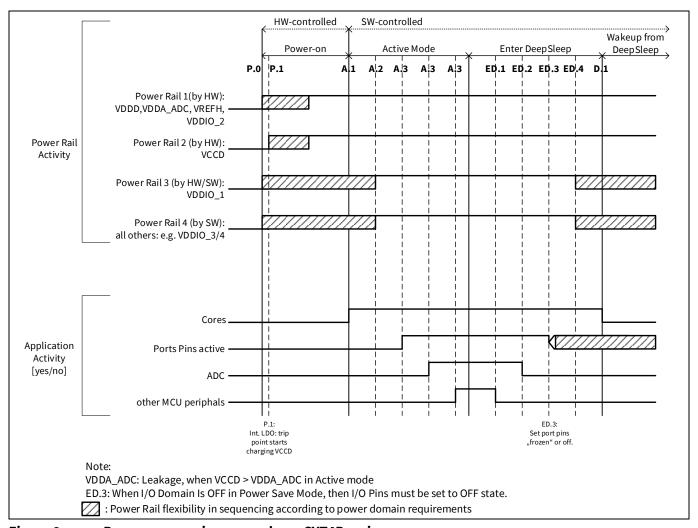

#### 3.4 Power ON/OFF sequence of power supply domains

Different voltage levels can be supplied to the power rails of the MCU. Therefore, power ON/OFF sequence is not required for power supplies of many devices. When there is no supply voltage at V<sub>DDD</sub>, but the analog supply V<sub>DDA</sub> is powered, a leakage current inside the MCU can occur. However, no port output will be driven. If a device needs a power sequence, see the device datasheet.

#### 3.4.1 General

- Disable monitoring features (for example, LVD, BOD, internal supply monitoring via ADC) before disabling related power domains. Otherwise, an unintended reset or fault might occur.

- Disable or tie to low-output pins before disabling the power domains.

- Disable input buffers before disabling the power domains.

- Power sequencing requirements and power domain dependencies can differ between power modes. So, when domains need to be switched OFF to reduce the leakage current in power save modes, carefully consider the transition phase for entering and leaving the modes.

- ECU peripherals must be in proper states during power mode transitions.

#### 3.4.2 **External core supply**

Devices running with external core supply have the same power ON/OFF sequence, because the MCU is starting in the internal supply mode and the external core supply must be enabled by the application. In power off transition, the external core supply is disabled by the MCU.

#### 3.4.3 **ADC**

- In Active mode, leakage current occurs only when  $V_{CCD} > V_{DDA ADC}$  in (LP) Active and Sleep power modes.

- Many I/O domains with shared analog/digital inputs can be ramped up after VDDA\_ADC, as long as the ADC does not start the sampling operation of these domains.

- When the I/O domain is deployed only for digital signaling, many I/O domains can also have voltage operation range different from that of the ADC. See Clamping structure of I/O pins with shared analog functions.

- Do not address analog multiplexing bus (AMUXBUS) to unpowered domains.

#### **Power supply**

Figure 2 Power sequencing example on CYT4B series

#### **Power supply circuit** 3.5

To meet the EMC requirements for the target board, a noise-efficient supply buffering concept is needed. Therefore, the supply should be filtered. To have a minimum noise on the analog supply, it is recommended to use separate analog and digital power supplies.

Power supply concept proposals for different devices are discussed in Appendix A – Power supply concept.

#### **External core supply control** 3.6

The power supply concept description is not part of this documentation. See the application note corresponding to your device in Related documents.

**Power supply**

#### 3.7 Unused power domains

An unused power domain is usually considered as a permanent OFF state related to the power domain in the full application lifecycle. However, a temporary state of an unused domain is also possible, when some not-always-on power domains stay on in power save modes. For details on how to handle the I/O port pins of dedicated domain, see Port input/unused pins.

In general, the following are the main classes of an unused domain:

- Permanent unused domain: Not required in application

- Temporary unused domain: Disabled in power save mode

For details on different devices, see Appendix E – Unused power domain handling.

Note:

In principle, you can remove the big bypass capacitors and keep only small decoupling caps (decaps) left on the unused power domains that cannot be grounded. However, you must check if bypass capacitors are also used for other shared power domains in power concept.

If you do not find information on unused power domains in the device datasheet, contact technical support.

**Clock system**

# 4 Clock system

The MCU provides several clock sources depending on the system requirements. Table 1 lists the available clock sources for the MCU system and shows how the clock sources are connected to the MCU internal clock system.

#### 4.1 Clock sources

Table 1 Clock sources

| Clock source                                                 | Oscillator | Int/<br>Ext | Port pin name<br>(ext. only) | Frequency              | Trimmable | Use case                 |

|--------------------------------------------------------------|------------|-------------|------------------------------|------------------------|-----------|--------------------------|

| Internal main oscillator (IMO)                               | Yes        | Int         | -                            | 8 MHz                  | Yes       | LIN                      |

| Internal low-speed oscillator (ILO)                          | Yes        | Int         | -                            | 32 kHz                 | Yes       | -                        |

| External crystal oscillator (ECO)                            | Yes        | Ext         | ECO_IN<br>ECO_OUT            | ~4 MHz to<br>33.33 MHz | Yes       | CAN communication        |

| Watch crystal oscillator (WCO)                               | Yes        | Ext         | WCO_IN<br>WCO_OUT            | 32.768<br>kHz          | No        | Watch                    |

| Low-power external crystal oscillator (LPECO) <sup>[1]</sup> | Yes        | Ext         | LPECO_IN<br>LPECO_OUT        | ~4 MHz to<br>8 MHz     | No        | Watch                    |

| EXT_CLK pin <sup>[2]</sup>                                   | No         | Ext         | Optional on several pins     | Note <sup>[3]</sup>    | _         | Test                     |

| Reference clock for                                          | Yes        | Ext         | ETHn_REF_CLK                 | 50 MHz                 | _         | Ethernet: RMII           |

| Ethernet PHY and MAC                                         |            |             |                              | 125 MHz                | _         | Ethernet: GMII,<br>RGMII |

<sup>&</sup>lt;sup>1</sup> LPECO is available only for CYT4D series.

<sup>&</sup>lt;sup>2</sup> This port pin is bidirectional and can be used as an external clock source for the device and as a clock observation mechanism for internal clock signals.

<sup>&</sup>lt;sup>3</sup> See the device datasheet for external clock input specifications.

PLL

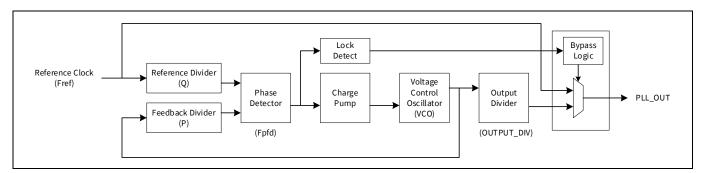

#### 5 PLL

With the help of the PLL, it is possible to generate higher output frequencies based on the input reference clock ( $F_{ref}$ ). The principal setup of a PLL is shown in Figure 3. According to application requirements for nominal target frequency and jitter, the PLLs can have different modi<sup>[4]</sup>:

- Integer

- Fractional

- Spread spectrum clock generation (SSCG)

Depending on the selected mode, the phase detector frequency  $(F_{pfd})$  has a permitted frequency range, which has also an impact to the nominal frequency selection of the external clock source (for example, crystal quartz).

### 5.1.1 Example

Several PLLs share an external crystal quartz as the common clock source and following modi are used:

PLL#A: Integer mode:  $F_{pfd} = 4-20 \text{ MHz}$ PLL#B: Fractional mode:  $F_{pfd} = 8-20 \text{ MHz}$

Result: The crystal quartz must be min. 8 MHz.

Figure 3 Principle block diagram of PLL

002-20270 Rev. \*H

<sup>&</sup>lt;sup>4</sup> See the corresponding architecture TRM for details about each configuration.

**Reset circuit**

#### **Reset circuit** 6

To make sure that an MCU operates within specifications, an external reset signal via the reset input pin (XRES pin) or an internal reset signal can be generated. The implementation of the internal reset circuits has several advantages over the hardware design:

- Reduced bill of material (BOM) cost as the external monitoring ICs are removed

- Detection of MCU internal out-of-range operations, which cannot be monitored externally (for example, MCU internal voltage drops)

Note that external monitoring or resetting ICs might still be needed based on the application requirements.

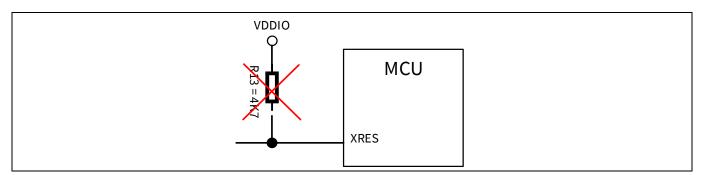

#### 6.1 Reset pin (XRES)

A switch connects the reset input pin to VSSIO (Ground). An internal pull-up resistor and an internal noise filter of minimum 100 ns are available to reduce the BOM cost. If an external capacitor is applied for additional filtering, make sure that the EMC requirements are fulfilled. Otherwise, the ESD test pulses might destroy the ESD protection structure inside the MCU.

For details on the reset pin, see the datasheet.

Figure 4 External reset input (XRES)

#### 6.2 Power supply monitoring

To make sure that the MCU is not running beyond operating conditions, a broad range of power monitor circuits is provided by the MCU. See the device architecture TRM and datasheet for details.

#### 6.2.1 Power-on reset (POR)

Power-on reset (POR) circuits provide a reset pulse during the initial power ramp. Here, only the V<sub>DDD</sub> power supply rail is observed.

#### **Brown-out detection (BOD)** 6.2.2

The brown-out detection (BOD) circuit protects the operating or retaining logic from possibly unsafe supply conditions by applying a reset to the device. BOD circuits for the VDDD, VDDA, and VCCD power supply rails are provided. A reset is generated when one of the monitored operating ranges is undercut. This circuit is required to detect a sneaking voltage drop of the battery power supply.

**Reset circuit**

### 6.2.3 Low-voltage detection (LVD) and high-voltage detection (HVD)

Before the BOD level threshold generates a reset, you might be warned by the configurable circuit for low-voltage detection (LVD) and high-voltage detection (HVD) use case. You can configure the trip point (detection level), which creates an interrupt for possible safety measures. This circuit can oversee faster transitions.

#### 6.2.4 Over-voltage detection (OVD)

Over-voltage detection (OVD) circuit applies a device reset when  $V_{CCD}$ ,  $V_{DDD}$ , or  $V_{DDA}$  supply goes above the maximum allowed voltage. This concept is a reverse of the BOD circuit.

### **6.2.5** Over-current detection (OCD)

The over-current detection circuit monitors the current of the  $V_{CCD}$  power supply rail and detects whether the load current of a regulator is higher than expected. If the current is over the regulator limit, the OCD circuit generates a reset to protect the device.

### 6.2.6 Power domain voltage monitoring by the ADC

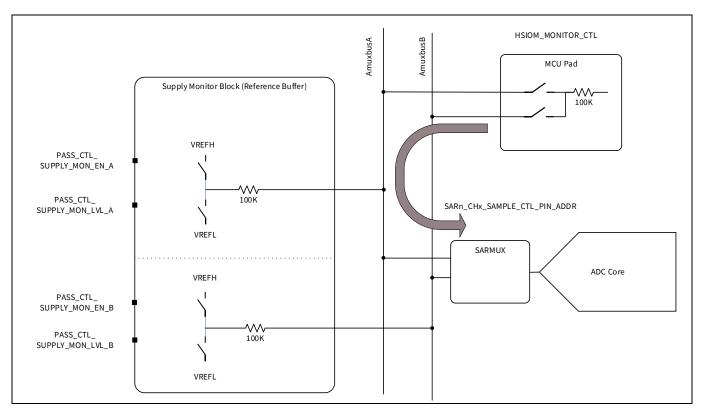

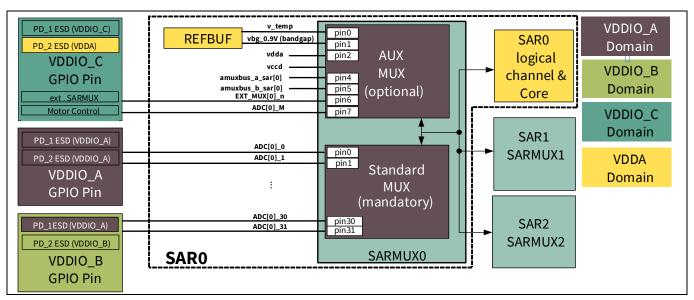

The ADC provides the opportunity to monitor several power supply and ground pads. Instead of a reset, only an interrupt is generated by the corresponding ADC unit. To keep the CPU load low, the range detection feature can be enabled to generate only an interrupt when a critical range is entered. The pads can be selected by a complex multiplexer structure as shown in Figure 5. For details on this feature, see the *Analog subsystem > SAR ADC > Reference buffer* and *Resources subsystem (SRSS) > Voltage monitoring > Voltage monitoring by ADC* chapters in the architecture TRM.

Figure 5 Block diagram of voltage monitoring by ADC

**Reset circuit**

#### **Watchdog reset** 6.3

An internal watchdog timer (WDT) within the MCU supports a wide range of capabilities. This WDT circuit can also run in the Hibernate power mode (see "Device power modes" in the architecture TRM).

Ports and non-power pins

#### Ports and non-power pins 7

#### 7.1 Port input/unused pins: General considerations

This section explains the different methods to handle unused pins and the advantages and disadvantages with respect to the MCU operation. In general, the risk of unused pins is floating inputs and a latch-up effect within the pin structure.

#### 7.1.1 Open pin connection

During and after POR, by default, the I/O pins are in a high-impedance (High-Z) analog state with disabled input buffers. The advantage of this method is that the current consumption of the MCU is lower when compared to the use of a terminal resistor, and the BOM cost is reduced. The disadvantage is that during an assembly option, a long signal trace is routed to the pin; the signal trace can take effect as an antenna and a captured noise can cause a latch-up at the pin.

#### 7.1.2 Direct connection to GND or power supply

The I/O pins should not be connected directly to GND or to power supply as the power supply traces can take effect as an antenna to the pin and the captured noise can cause a latch-up effect.

#### 7.1.3 Internal pull-up/down resistor as termination

When there is a risk of a latch-up effect at an unused pin due to the board design (long traces of optional features), terminate the input pin using internal pull-up or pull-down resistors.

The advantage is low current consumption and BOM cost reduction compared to using external termination resistors. Disadvantage is that you must configure the port pin state after a reset. Therefore, during a reset caused by any disturbance (supply, clock issues, and so on), the internal termination is not available anymore and the system is again vulnerable against a latch-up effect.

You can choose this method if there are unused pins without a long trace. In general, it must be considered that the pin state (enabled pull-up or pull-down resistor) must be unchanged when a low-power mode is entered. The reason is that for an external resistor, the internal termination must be available all the time.

#### 7.1.4 External pull-up/down resistor as termination

An external termination resistor can be placed next to the unused I/O pin instead of using the internal ones. In the case of an open signal line routed to the pin, any injected noise can be safely terminated even during a device reset. A resistor value between 2.2 k $\Omega$  and 10 k $\Omega$  can be used. However, you should not connect several unused pins to one common termination resistor because if unused I/O pins unintentionally drive different output levels against each other, the I/O pins might be permanently damaged.

Ports and non-power pins

### 7.2 Dedicated port pins

For dedicated MCU peripherals, the unused I/O handling is explicitly considered. In most of these cases, the entire MCU peripheral including the power domain pins must be considered to avoid the risk of latch-up (LU). For details on power domain pins, see Unused power domains.

Table 2 Handling of unused dedicated I/O pins

| MCU<br>peripheral | Power domain | I/O pin                | I/O function<br>[IN/OUT] | Pin I/O handling (Connect to)                             |

|-------------------|--------------|------------------------|--------------------------|-----------------------------------------------------------|

| MIPI              | VDDA_MIPI    | MIPI_DPx<br>x: 0/1/2/3 | IN                       | Open pin connection                                       |

|                   | VDDA_MIPI    | MIPI_DNx<br>x: 0/1/2/3 | IN                       | Open pin connection                                       |

|                   | VDDA_MIPI    | REXT                   | IN                       | Open pin connection (external 15 $k\Omega$ removed)       |

| FPD               | VDDA_FPD     | FPD_TxP<br>x: A/B/C/D  | OUT                      | Open pin connection                                       |

|                   | VDDA_FPD     | FPD_TxN<br>x: A/B/C/D  | OUT                      | Open pin connection                                       |

| Audio-DAC         | VDDA_DAC     | C_L, C_R               | IN                       | GND                                                       |

|                   |              | DAC_L, DAC_R           | OUT                      | (when Mono sound: Open pin connection of the unused part) |

| REGHC / PMIC      | VDDD         | DRV_OUT                | OUT                      | Open pin connection                                       |

| Controller        | (always-on)  |                        |                          |                                                           |

### 7.3 Port pin configuration in AUTOSAR MCAL

Microcontroller abstraction layer (MCAL) of AUTOSAR is a low-level driver for the microcontroller, which is used in the software developed for automotive applications. So, the port pin configuration with the PORT module is part of the MCAL.

The following are the possible risks if there is a wrong port pin setting to the MCU:

- I/O structure being destroyed

- Additional leakage current in power save modes

- Latch-up effect

Therefore, especially with regard to the latch-up risk, keep the SW port pin configuration always compliant with the HW concept for unused I/O pins (see Port input/unused pins) and unused I/O power domains (see Unused power domains). This is also relevant for the SW-controlled power sequencing procedure in which unpowered I/O domains must be considered as unused power domains.

In the MCAL PORT module, you can configure port pins depending on different use cases within the corresponding application cycles, each time in a PortContainer. All port pins which are not explicitly configured by the dedicated PortContainer will be implicitly configured according to the PortDefaultContainer. The Port\_Init() API sets all pins of the derivative device either according to the explicit configuration in PortContainer (if the pin was configured) or the implicit configuration in PortDefaultContainer (if the pin was not configured in PortContainer).

#### Ports and non-power pins

The PortPinDirection=PORT PIN IN setting sets the pin as an input and enables the input buffer. If a pin is not needed (that is, no output and no input required), the pin should be configured to PortPinDirection=PORT PIN OUT, PortPinOutputDrive=PORT PIN OUT MODE HIGHZ, and PortPinOutputInBufEnable=FALSE. This is the only recommended setting for PortDefaultContainer, but the key is to be compliant with the latch-up HW requirements to I/O pins.

#### 7.4 Pins in low-power mode

To achieve the lowest possible quiescent current in a low-power mode, the current consumption of I/O pins must be considered. Depending on the low-power mode, the configuration state and the last output state are frozen. In the case of input pins, it is forbidden to have floating input levels because the quiescent current of the MCU increases dramatically. When an input pin is used as a wake-up pin, do not change the configuration under the assumption that the pin has an internal or external pull-up or pull-down resistor for termination. When an input pin is not required in a low-power mode, it can be configured as High-Z input with disabled input buffer. For details on different low-power modes, see the architecture TRM and the corresponding application note listed in Related documents.

#### Latch-up considerations (Switch) 7.5

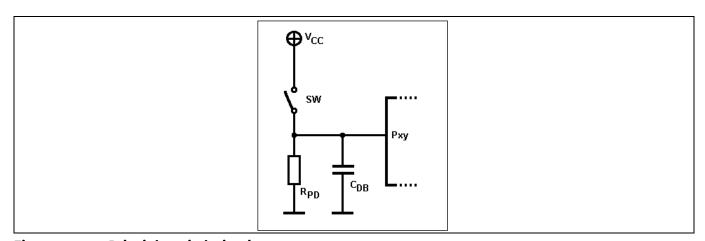

Pressed switches usually cause a bouncing signal, which can damage the MCU port pin. As a countermeasure, debounce capacitors are deployed. Exercise caution with external switches to V<sub>cc</sub> or ground together with debounce capacitors connected to port pins.

A usual configuration is shown in Figure 6.

Figure 6 Principle switch circuit

R<sub>PD</sub> is a pull-down resistor and C<sub>DB</sub> a debounce capacitor. If the switch SW is open, a "0" is read from the port pin Pxy. When the switch is closed, the input changes to "1".

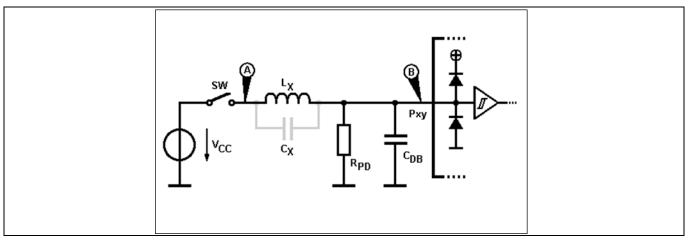

From the physical aspect, it needs to be considered that the switch is often placed at a distance from the MCU by cable, wire, or circuit path. The longer the circuit path is, the higher is its inductivity LX (and capacity CX).

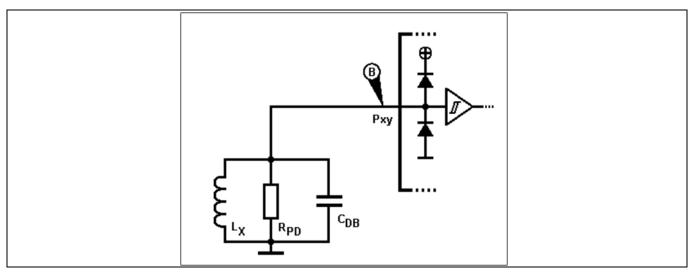

An equivalent circuit diagram is shown in Figure 7.

#### Ports and non-power pins

Figure 7 Equivalent circuit of the principle switch circuit

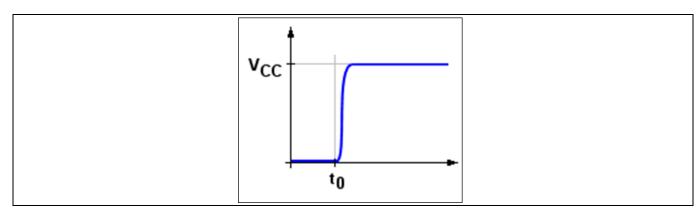

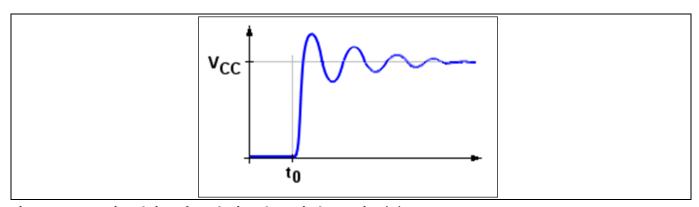

By closing the switch SW at time  $t_0$ , as shown in Figure 8, the voltage can be measured at point (A).

Figure 8 Signal rise after closing the switch at Point (A).

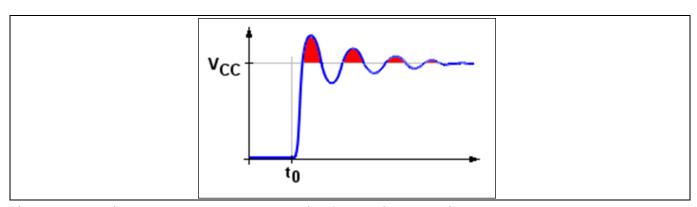

However, at the port pin Pxy on Point (B), as shown Figure 9, voltage can be measured.

Figure 9 Signal rise after closing the switch at Point (B)

By closing the switch SW, the circuit becomes a parallel oscillator with the wire inductivity  $L_x$ , the debounce capacitance  $C_{x_i}$  and the damping  $R_{PD}$  of the pull-down resistor (It is assumed that it is an ideal power supply, that is, it has no internal resistance).

#### Ports and non-power pins

Figure 10 **Equivalent circuit during closed switch**

$R_{PD}$  is often chosen high (> 50 k $\Omega$ ), and so its damping effect is weak.

This (weakly) attenuated oscillator causes voltage overshoots on the port pin (Point (B)), as shown in red in Figure 11.

Figure 11 Signal overshoots on the port pin after closing the switch

These overshoots may cause an internal latch-up on the port pin, as the internal clamping diode connected to internal power supply becomes conductive. Similar is the effect if the switch SW is opened. In this case, there are undershoots on the port pin.

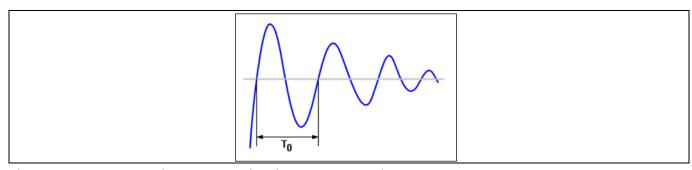

The frequency of the oscillation can be calculated by Equation 1.

$$f_{OSC} = \frac{1}{2\pi\sqrt{L_{X}C_{DB}}}$$

Equation 1

The inductivity (LX) is an unknown value and depends on the PCB, its routing, and the wire length.

There are two counter measures to prevent a latch-up.

Ports and non-power pins

#### 7.5.1 Solution A

Decrease the capacitance of the debounce capacitor. This increases the oscillation frequency, which causes the overall energy of the overshoots to be smaller.

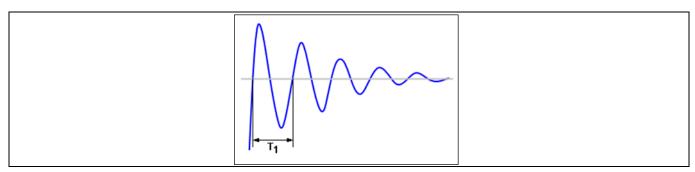

Figure 12 Bounce signal on the pin with a large capacitance

Figure 13 Bounce signal on the pin with a small capacitance

This solution has two disadvantages: the debounce effect decreases and there is no guarantee that the latch-up condition is eliminated.

### 7.5.2 Solution B (recommended)

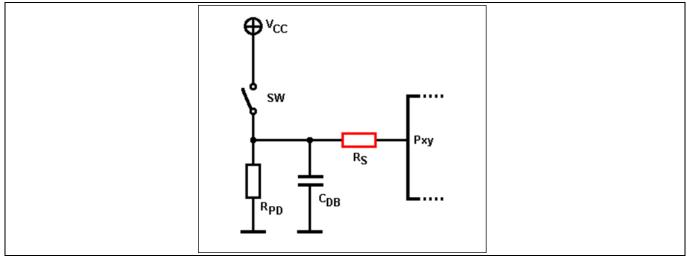

Use a series resistor (R<sub>s</sub>) at the port pin as shown Figure 14.

Figure 14 Recommended switch circuit with series resistor

#### Ports and non-power pins

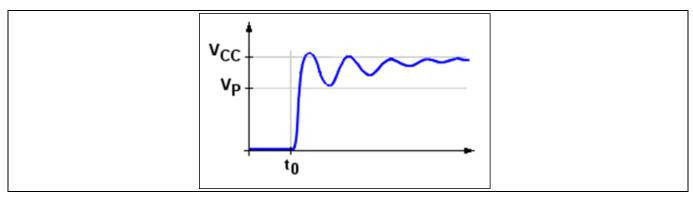

The series resistor  $R_S$  reduces the amplitude of the oscillation and decreases the voltage offset at first. Do not choose too high a resistor value. Otherwise, the port pin input voltage  $(V_P)$  will be below the high input level threshold of the dedicated port pin (for example, CMOS/TTL/Automotive level).

Figure 15 Reduction of the signal bouncing on the pin due to the series resistor

#### 7.6 5-V-tolerant input pins

The MCU does not have 5-V-tolerant input pins if the corresponding I/O domain has a smaller voltage supply (for example, 3.3 V). In the case of the deployment of an I<sup>2</sup>C bus system with 5 V, and if  $V_{DDIO}$  is supplied with 3.3 V, an external level shifter must be added to avoid the latch-up effect on the MCU pin.

#### 7.7 Reset behavior of I/O port pins

During and after the power-on reset (POR), all GPIOs are in high-impedance analog state and the input buffers are disabled. During runtime, GPIOs can be configured by writing to the associated registers. The Debug Access Port (DAP) connection can be disabled or reconfigured for general-purpose use only after the code execution starts.

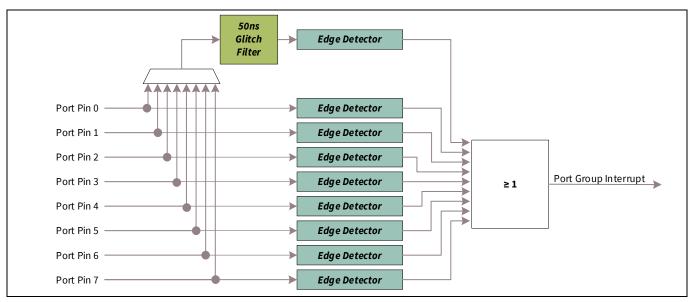

### 7.8 Glitch filtering

The MCU provides the option of internal glitch filtering. As the glitch filters are not available on every port pin, the assignment of wakeup pins must be done with caution. Before assigning wakeup pins, check the number of available glitch filters in the device datasheet.

### 7.8.1 Analog filter

Every port group has one analog filter, which also works in DeepSleep mode. For details on AC characteristics, see the device datasheet.

### 7.8.2 Digital-based filter

The smart I/O module in the I/O system can implement one digital-based filter in dedicated ports. In the DeepSleep mode, either the internal low-speed oscillator (ILO) or the external crystal oscillator (ECO) clock can be selected as the clock source (see Clock system). This means that the minimum filter period is ~30  $\mu$ s. Additionally, the current consumption increases because a clock is running. For more information, see smart I/O, I/O system in the architecture technical reference manual (TRM).

See Latch-up considerations (Switch) for the latch-up considerations regarding deployed external filters.

#### Ports and non-power pins

Figure 16 Port glitch filter and interrupt structure

### 7.9 Mode pin

A dedicated Mode pin is not required to enter the MCU into programming or normal run mode.

### 7.10 External interrupt input pins

In general, an external interrupt can be captured by edge detection on every general-purpose I/O (GPIO) port pin. See Glitch filtering to learn how to use glitch filtering.

Table 3 lists the wakeup sources in the different power modes. For more details on the power modes, see the "System resources subsystem (SRSS)" and "Device power modes" sections in the corresponding TRM.

Table 3 External interrupt/wakeup support in power modes

|                                      | External interrupt/wakeup in power mode |       |           |           |

|--------------------------------------|-----------------------------------------|-------|-----------|-----------|

| Port pin function                    | Active                                  | Sleep | DeepSleep | Hibernate |

| GPIO                                 | х                                       | Х     | х         | -         |

| Dedicated peripherals <sup>[5]</sup> | Х                                       | Х     | х         | х         |

| WAKEUP <sup>[6]</sup>                | -                                       | -     | -         | х         |

<sup>&</sup>lt;sup>5</sup> See the architecture TRM, device datasheet, or both.

<sup>&</sup>lt;sup>6</sup> The WAKEUP function is supported only on a few pins.

Ports and non-power pins

### 7.11 Clamping structure of I/O pins with shared analog functions

It is important to identify the power supply domains that must have a common supply level in each application. Figure 18 and Appendix G – Clamping structure of I/O pins with shared analog functions provide the overview of the clamping structure and the consequences when the analog input function is used on dedicated power domains. When any port pin of a dedicated power domain (PD) is applied as an analog input, the domain must have the same voltage level or lower than the analog supply (VDDA\_ADC). Appendix G – Clamping structure of I/O pins with shared analog functions lists the special use cases.

As soon as the ADC unit is in use, the deployed SARMUX also must be powered. For example, when an analog input AN[1]\_x of SARMUX[1] is used by the ADC[0] unit, the I/O power domain of SARMUX[0] is not relevant. Note that the SARMUX supplies the external (e.g., AN[x]) pins and internal analog sensing (e.g., VCCD) paths; as a result, the corresponding I/O power domain should have the same voltage level as VDDA\_ADC.

Figure 17 Power domains

#### General

- Usually the I/O domain, PD\_1, deployed is also the same as PD\_2, but in some cases there are exceptions for PD\_2.

- The power domain dependency PD\_1 ≤ PD\_2 is especially relevant when PD\_1 is a different power domain when compared to PD\_2.

- When VDDA\_ADC is only on PD\_3 and as long as the pin input has not started to operate as an analog input,

PD\_1 and PD\_2 can be greater than VDDA\_ADC. See also Power ON/OFF sequence of power supply domains.

Note:

The implementation of power rail voltage levels for the dedicated I/O domains and the ADC supply must be compliant with the other power sequencing requirements mentioned in the device datasheet.

Also for the I/O power domain of each SARMUX must be taken care, when analog function is used. Which power domain supplies which SARMUX, this is documented in the device DS either in chapter "Absolute Maxium Ratings", or "Device-level specifications, or "Analog peripherals" and is specified in following manner usually:

"VDDIO\_1 must be greater than 0.8 × VDDA when ADC[0] is enabled", i.e., VDDD is the SARMUX0 I/O power domain. "VDDIO\_GPIO >= 0.8 x VDDA when SARMUX0 enabled."

#### Ports and non-power pins

Clamping structure of I/O pins with shared analog functions Figure 18

See Appendix G – Clamping structure of I/O pins with shared analog functions for device-specific information.

#### 7.12 External supply for the core voltage

#### Requirements 7.12.1

- Applications with < 300 mA core current consumption can run with the MCU-internal LDO.

- Applications with > 300 mA core current consumption need an external supply for the core voltage.

For the technical requirements of the DC/DC converter and details on how to use it, see AN226698 listed in Related documents.

Note:

In AN226698, DC/DC converters are termed as PMIC, although only the core voltage regulation handling is considered.

#### Drive output current of "Enable" control pin 7.12.2

To control the Enable (EN) input pin of the external DC/DC converter, a dedicated output control pin on the MCU is available. Compared to a standard GPIO pin, the absolute maximum drive current is extremely limited. Therefore, for current limitation, a series resistor is necessary. Otherwise, this MCU control pin might be permanently damaged. For electrical specification, see the device datasheet.

Flash programming connection

#### Flash programming connection 8

Flash programming can be done with the JTAG/SWD connection. Due to this fact, no mode pins are available to switch the device into a programming mode after power-on reset. See Debug interface for information on the debug connections. There is also the option to use dedicated LIN and the CAN channels for mass production programming as integrated part of a Flash bootloader. For details, see AN227076 in Related documents.

**Debug interface**

#### **Debug interface** 9

There are several options to connect the debug system to the MCU depending on the debug requirements and the tool chain support. The following are the debug connectors:

- Legacy 20-pin IDC JTAG connector

- 10-pin Cortex® debug connector

- 20-pin Cortex® debug + ETM connector

In all these connectors, the JTAG and SWD signals are shared. The differences are indicated by marking the serial wire debug (SWD) protocol signals in blue. For more information on the interface signals, see Chapter 11 of the CoreSight components technical reference manual. A short overview is given in Table 4.

Table 4 Overview of SWD and JTAG interfaces

| Item            | JTAG          | SWD                  |  |

|-----------------|---------------|----------------------|--|

| Pin count       | 4             | 2                    |  |

| Functionalities | Programming   | Programming          |  |

|                 | Debugging     | Debugging            |  |

|                 | Boundary scan |                      |  |

| Topology        | Daisy-chained | Star                 |  |

| Extra features  | N/A           | Print out debug info |  |

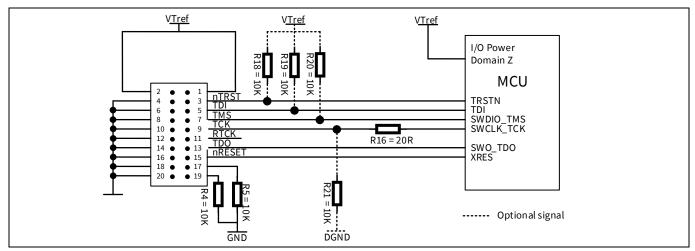

#### **Legacy 20-pin IDC JTAG connector** 9.1

The legacy JTAG interface is used for flash programming and debugging. The RTCK JTAG signal is not available on the MCU. Additionally, the SWD signals can be shared.

Note:

The JTAG interface terminates in a 20-way, 2.54-mm-pitch IDC connector (for example, Hirose HIF3FC-20PA-2.54DSA).

Figure 19 **Legacy 20-pin IDC JTAG connector**

**Debug interface**

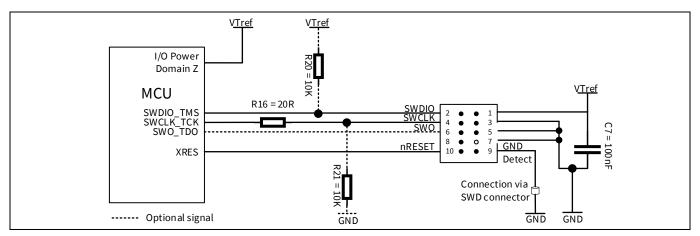

#### 9.3 10-pin Cortex® debug connector

To use the SWD debug interface, a 10-pin MIPI connector is defined with the minimum number of signals, which are required for debugging. The JTAG interface signals are replaced by the bidirectional data signal (SWDIO) and the clock signal (SWCLK). The freed-up TDO signal can be reused as a system trace data output serial wire output (SWO).

Note:

- 1. For the SWD debugging a 10-way connector with 1.27-mm pitch is applied (for example, Samtech FTSH-105-01-L-DV-K).

- 2. Position 7 (KEY) has no pin and serves only as a key to properly orient the connector.

```

SWDIO / TMS

VTref

1

/ TCK

3

GND

WCLK

6

5

(O) / TDO

GND

(KEY) GND

8

0

7

TDI

10

nRÉSET

9

(GNDDetect) GND

```

Figure 20 10-pin Cortex® debug connector

### 9.4 20-pin Cortex® debug + ETM connector

Beside JTAG debugging and SWD debugging, this connector is used to connect a signal trace probe for the embedded trace macrocell (ETM) instruction trace operations.

Note:

- 1. As a connector, a 20-way 1.27-mm-pitch IDC-connector is applied (for example, Samtech FTSH-110-01-L-DV-K).

- 2. Position 7 (KEY) has no pin and serves only as a key to properly orient the connector.

```

VTref

SWDIO / TMS

1

3

GND/

TCK

GND

TDO

(KEY) GND

7

8

10

9

(GNDDetect) GND

nTRST

TRACECLK

12

11

GND

14

13

GND

TRACEDATA[0]

TRACEDATA[1

16 •

15

GND

TRACEDATA 2

18 •

17

GND

20 •

GND

TRACEDATA[3]

```

Figure 21 20-pin Cortex® debug + ETM connector

#### 9.5 Termination resistors

In general, the debug connection needs termination resistors for a proper communication. External termination resistors should not be required for this MCU, because after POR, by default, the JTAG interface is enabled in the boot ROM. If externals are applied on the board, each external signal termination must in the same direction as it is done in the device implementation. Although the JTAG interface is enabled by after reset, the SWD mode can be enabled afterward by establishing the SWD connection.

#### **Debug interface**

Table 5 **Termination resistor for debug interface**

| JTAG<br>mode | SWD mode          | Signal                                                | Required termination resistor (if N/A in the MCU)         | MCU implementation                                     |

|--------------|-------------------|-------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------|

| TCK          | SWCLK             | Clock into debug core                                 | 10 k–100 kΩ pull-down<br>resistor to GND                  | Pull-down resistor                                     |

| TDI          | -                 | JTAG test data input                                  | 10 k–100 k $\Omega$ pull-up resistor to $V_{DDIO}$        | Pull-up resistor                                       |

| TDO          | SWO<br>(optional) | JTAG test data<br>output,<br>SWV trace data<br>output | 10 k–100 k $\Omega$ pull-up resistor to $V_{\text{DDIO}}$ | None. Termination,<br>push-pull driver<br>implemented. |

| TMS          | SWDIO             | JTAG test mode<br>select,<br>SWD data in/out          | 10 k–100 k $\Omega$ pull-up resistor to $V_{\text{DDIO}}$ | Pull-up resistor                                       |

| nTRST        | -                 | JTAG TAP reset<br>(active LOW)                        | 10 k–100 k $\Omega$ pull-up resistor to $V_{\text{DDIO}}$ | Pull-up resistor                                       |

| GND          | GND               | Connection to the system ground                       | -                                                         | -                                                      |

Figure 22 and Figure 23 show how to connect the debug connector to the MCU. In general, it is recommended to place a series resistor (R16) closer to the connector to avoid reflections and ringing of the debug clock signal. Otherwise, with strong oscillations during level settlement, the debug interface can interpret the wrong data. It must be considered that due to the internal termination resistor, a possible voltage divider in the debug clock signal might be created.

Figure 22 JTAG debug connection to the MCU with 20-pin IDC connector

#### **Debug interface**

SWD debug connection to the MCU with 10-pin MIPI SWD debug connector Figure 23

#### Note:

- 1. When SWD is used as the debug interface instead of JTAG, there is a time slot after reset and in between boot ROM and user pin configuration in which unused JTAG pins are configured according to JTAG communication. When these unused JTAG pins are used in an application, make sure that the peripherals on the ECU are not negatively affected.

- 2. It is recommended to check the debug connection that is supported by the vendors for flash programming and debugging. Also, check for the target board supply and the supported power supply level of the vendor's hardware. In the case of a power supply mismatch, an adapter is required.

- 3. Boundary-scan is supported only on JTAG interface, not on SWD.

#### Trace width 9.6

The trace signals are identified by the function names TRACE\_DATA\_x(0) and TRACE\_DATA\_x (1). The number in parentheses denotes the relocation set. Other than that, they are functionally identical. Nevertheless, you should only use the signals from the same relocation set; i.e., only (0) signals or only (1) signals.

If all trace signals are not used, the ones with the higher numbers can be omitted. Your debugger tool should allow you to select the actual trace port width.

#### Possible trace width combinations

| Trace signal | 8-bit width        | 4-bit width        | 2-bit width        |

|--------------|--------------------|--------------------|--------------------|

| Variant A    | TRACE_CLOCK (0)    | TRACE_CLOCK (0)    | TRACE_CLOCK (0)    |

|              | TRACE_DATA_0-7 (0) | TRACE_DATA_0-3 (0) | TRACE_DATA_0-1 (0) |

| Variant B    | TRACE_CLOCK (1)    | TRACE_CLOCK (1)    | TRACE_CLOCK (1)    |

|              | TRACE_DATA_0-7 (1) | TRACE_DATA_0-3 (1) | TRACE_DATA_0-1 (1) |

**Clock output function**

#### **Clock output function** 10

You might need to cross-check the MCU internal clock signals for evaluation purposes. You can cross-check with the following options:

- EXT\_CLK port pin

- Alternate output function pin

#### 10.1 Using the EXT\_CLK port pin

Internal clocks can be routed through a divider to the alternate function port pin EXT\_CLK as the clock output function. It must be taken into consideration that the event generator macro (EVTGEN) and EXT\_CLK are driven by the same internal clock signal (CLK\_HF1). Therefore, when the divided ECO signal should be observed at the EXT\_CLK pin, the EVTGEN macro is also driven with the ECO clock accordingly. This may have an impact on the application. The EXT\_CLK pin is a bidirectional pin and can be also used as an external clock source. See Clock system for more information about this pin.

As the MCU clock output functionality drives the fast digital signal, this signal must be routed far away from the analog input and the analog voltage reference signals.

#### 10.2 Using the alternate function pin

The system clocks can be implicitly observed by using a PWM signal coming from a TCPWM output channel for instance. It must be taken into consideration that each TCPWM channel input clock is derived by a dedicated clock divider of the peripheral clock. See the "Clocking system" chapter in the TRM for details on the clock tree.

Layout and electromagnetic compatibility

### 11 Layout and electromagnetic compatibility

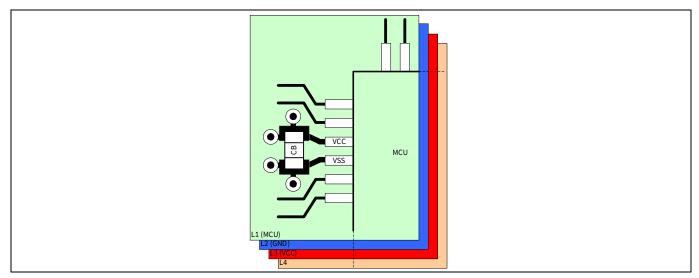

#### 11.1 General

To avoid ESD problems and noise emission of the system, consider some rules for the layout design.

The most critical point is the VCCD pin, as this is the connection to the internal supply for the MCU core. The required decoupling capacitors (decaps) must be placed as close as possible to this pin. Usually a bigger buffer or bypass capacitor of  $\mu F$  range is added to the dedicated power domain to bypass the period of time until the capacitors are recharged again. Otherwise, decaps and finally the system fall below the power supply operating range.

As the MCU has different digital supply rails, routing of power supply traces must be done carefully. Supply traces should be routed in a star shape or as digital plane in the middle layer. A digital ground plane in the middle layer or on the mounting side just under the MCU is recommended. Decoupling capacitors should be assembled as near as possible to the related pins. If these capacitors are placed too far away, their functionality is diminished.

If possible, all decoupling capacitors should be placed on the same mounting side as the MCU. Alternatively, the decaps could be placed on the bottom layer below the paired power supply pins (for example, VDD/VSS pair).

The analog supply should be decoupled from the digital supply and a common-ground star point should be placed as far as possible from the MCU. In the hardware design, make sure that no latch-up effect between the digital and analog supply or between analog and digital ground can occur. Therefore, the impedance between the different VSS pins and between analog ground and analog reference input must be as low as possible.

#### 11.2 Power supply pins

For proper operation of the MCU decaps and bypass capacitors are needed for the power supply pins. See General regarding recommendations about the placement of the decaps.

#### 11.3 Ground and power supply

For a multi-layer PCB, the power supply rails and ground should be routed as a plane in the inner layers of the PCB. Considering a layer stack with several power supply planes, these planes should not overlap to avoid noise coupling.

Here are some recommendations for good EMC behavior:

- Use a multi-layer PCB.

- Use power supply planes (ground and power) in the inner-layer of the PCB layer stack.

- Place one or two decoupling capacitors close to each corresponding supply pin pair to reduce possible radiation.

- Use capacitor groups to match the frequency behavior of power supply decoupling. The decoupling capacitors can have values between 1 nF and 10  $\mu$ F.

- Make sure that only one common star point connects analog and digital ground planes to each other. To

have less noise on the analog part, the star point should be placed as far as possible from the MCU and as

close as possible to the voltage regulator capacitor with respect to the electronic control unit (ECU)

connector.

#### Layout and electromagnetic compatibility

- Make sure that the digital and analog planes do not overlap and interfere. Furthermore, there should be no signal plane between these planes.

- Shield the analog input signals by the analog ground as much as possible.

- Avoid ground loops.

- Make sure that the supply traces with a layer changeover have at least two vias.

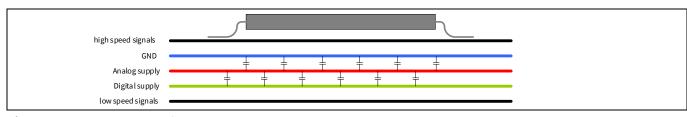

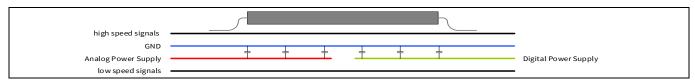

Figure 24 shows an example of a bad PCB layer stack, as there might be crosstalk between different power supply planes. However, Figure 25 is an example of a well-designed PCB layer stack in which the analog and digital supply planes are separated in the common layer. Thus, the EMC behavior of the board is already improved.

Figure 24 Example of a bad PCB layer stack

Figure 25 Example of a good PCB layer stack

### 11.4 Power supply decoupling

#### 11.4.1 Placement

In general, the decaps should be placed as close as possible to the MCU. When a small ceramic capacitor is used together with a large electrolytic capacitor for decoupling, place the ceramic capacitor closer to the MCU power supply rail than the electrolytic capacitor.

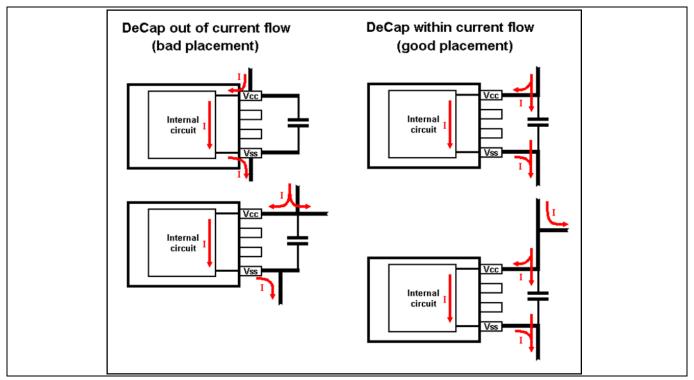

Decaps for power supply must be placed within the current flow. If not, they provide no benefit as their function becomes less efficient as shown in Figure 26. As the description is valid for generic use, as shown in Figure 26 to Figure 28, the generic naming convention for power supply pins is VCC; for ground pins, it is VSS.

#### Layout and electromagnetic compatibility

Figure 26 Power supply decoupling capacitor placement

Usually the noise current should flow through the soldering pad of decoupling capacitor CB. Figure 27 shows the recommended routing and placement on the boards.

Figure 27 Recommended power supply decoupling on boards

Figure 28 shows an alternate, but not recommended routing and placement. Note that the capacitor is placed on the opposite PCB side like the MCU. This solution works best for high-density board assembly.

#### Layout and electromagnetic compatibility

Figure 28 Alternate power supply decoupling on boards

### **11.4.2** I/O domains

The dimensioning of the decaps and bypass capacitors for the I/O domain is application-specific. The following are some points to be considered while dimensioning:

- How is the switching behavior (periodic or random) of the output stages and what is the transition requirement?

- How many outputs have the same transition at the same time during the running operation or after any wakeup or reset?

- How big is the capacitive load at one output pin?

- Which driver strength configuration is selected?

- Is there any DC current caused by resistors which might be also buffered by a big bypass capacitor?

It is strongly recommended to make either a power distribution network (PDN) analysis with an according model (IBIS or lumped model) or test on the PCB. A simplified consideration about the decoupling is provided in the SRAM board design guidelines.

### 11.5 Quartz crystal placement and signal routing

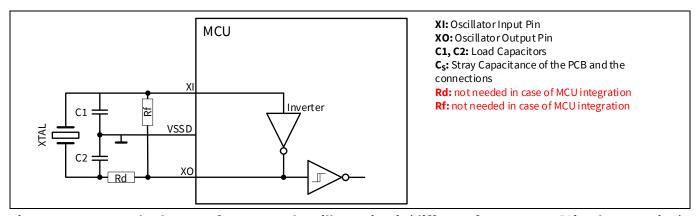

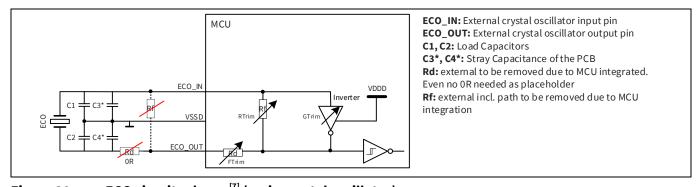

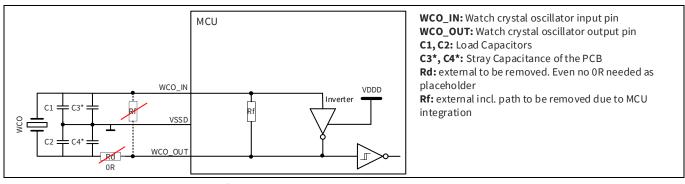

The MCU provides two Pierce oscillators implementations with an embedded feedback resistor (Rf) for the ECO and external watch oscillator (WCO). You can enable both oscillators by software. It means that the MCU starts the boot process from an internal clock source.

Note:

Figure 30 to Figure 32 showing the implementation of oscillators in the MCU family and the trimming features discussed in this application note might differ from the dedicated device architecture TRM. Due to different trimming features, the external BOM cost can be reduced in the ECU design.

#### 11.5.1 Setup

Figure 29 shows the principle of an external oscillator circuit. The feedback resistor (Rf) is required to act is necessary for the inverter to act as an amplifier. Optionally, a damping resistor (Rd) is required for drive-level

#### Layout and electromagnetic compatibility

(DL) reduction. If the DL is too strong, the crystal can be damaged over the life time. The load capacitance  $C_L$  is the terminal capacitance and is connected to the crystal. Thus,  $C_L$  includes the external capacitors C1 and C2 and the stray capacitance  $C_S$ .  $C_S$  comes from the PCB layout, manufacturing tolerances, and the oscillator MCU pins. As the stray capacitance is usually ~4 pF for each signal line, the value of both load capacitors (C1 and C2) should be determined with a crystal matching test. This test must always be done by the crystal manufacturer when there is any change on the target board affecting the oscillator circuit.

#### Load capacitance (C<sub>L</sub>)

$$C_{\rm L} = \frac{C1 \times C2}{C1 + C2} + C_{\rm S}$$

Equation 2

Note:

- 1. The oscillator pins are shared with standard GPIO pins, which automatically leads to additional load capacitance in the oscillator circuit. This must be considered with regards to external load capacitors.

- 2. For details on crystal trimming, see AN230194.

Figure 29 Standard setup of an external oscillator circuit (different from TRAVEO™ implementation)

The ECO design is optimized for BOM cost reduction (see Figure 30). This is realized by a scalable DL and an embedded Rf implementation. By trimming features, a broad crystal frequency range can be supported. For details, see the "Clock sources" section in the architecture TRM.

Figure 30 ECO circuit scheme<sup>[7]</sup> (main crystal oscillator)

Application note 36 002-20270 Rev. \*H

$<sup>^{\</sup>scriptscriptstyle 7}$  Figure might differ from dedicated architecture TRM. Trimming features are not covered 100%.

### Layout and electromagnetic compatibility

The WCO implementation scheme is shown in Figure 31. Like in the ECO, Rf is embedded to reduce the external BOM cost. An external Rd might be required to avoid damage of the external watch crystal.

Figure 31 WCO circuit scheme<sup>7</sup> (watch crystal oscillator)

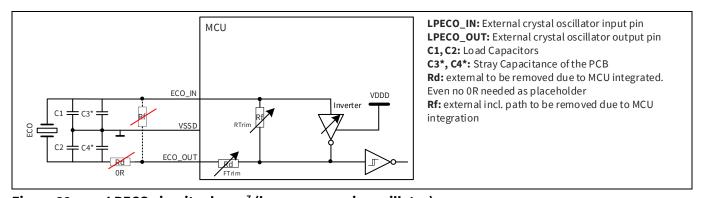

The LPECO design is optimized for BOM cost reduction (see Figure 32). This is realized by a scalable DL and an embedded Rf implementation.

Figure 32 LPECO circuit scheme<sup>7</sup> (low-power main oscillator)

Table 6 shows the resulting external BOM based on the feature set in each oscillator implementation.

Table 6 BOM overview of crystal oscillator implementations

| Ext. component    | ECO               | LPECO <sup>[8]</sup>        | WCO                        |  |

|-------------------|-------------------|-----------------------------|----------------------------|--|

|                   | (main oscillator) | (low-power main oscillator) | (watch crystal oscillator) |  |

| XTAL              | Mandatory         | Mandatory                   | Mandatory                  |  |

| C1, C2            | Mandatory         | Mandatory                   | Mandatory                  |  |

| Rd <sup>[9]</sup> | Remove            | Remove                      | Remove                     |  |

| Rf                | Remove            | Remove                      | Remove                     |  |

<sup>&</sup>lt;sup>8</sup> Not available on each device. When available, then same pins might be shared with WCO.

<sup>&</sup>lt;sup>9</sup> Rd not needed due to low power oscillator implementation

Layout and electromagnetic compatibility

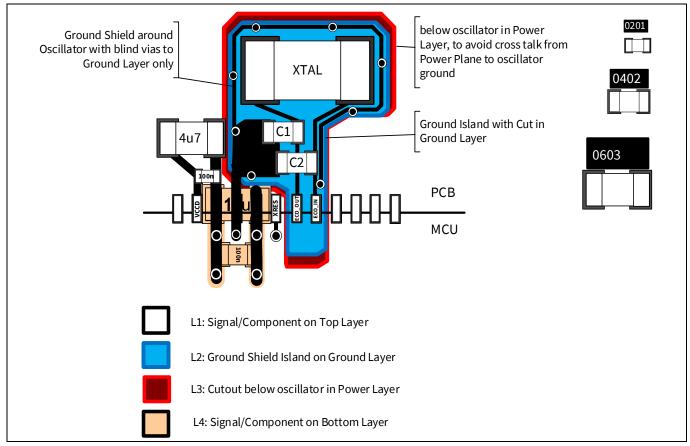

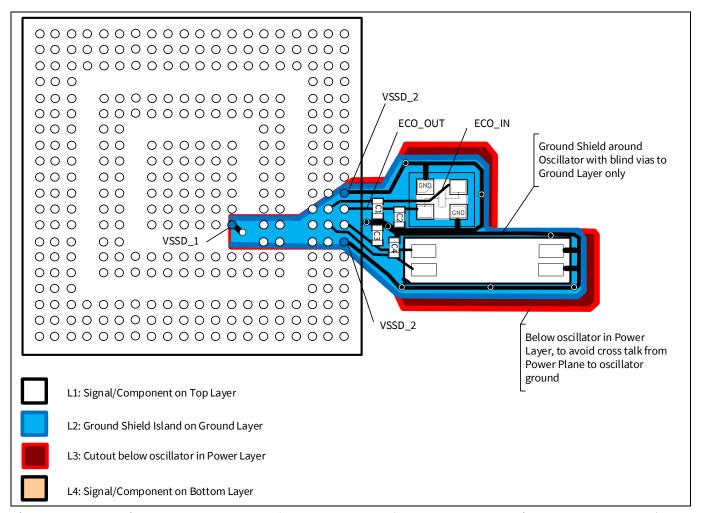

# 11.5.2 PCB design

To reduce the impact of EMI, the placement of the external oscillator components and the signal routing must be done carefully. The following should be considered during PCB layouts. Due to design constraints, it might be required to make a tradeoff between the items.

- Stable frequency

- Place the external oscillator components on the MCU layer.

- Place the external oscillator components as close as possible to the MCU.

- Make sure that the connection of load capacitors C1 and C2 to the oscillator ground is in a common star point.

- Make sure that there is no signal line between both capacitor ground connections.

- Do not use vias for ground signal routing.

- Noise injection

- Use a ground layer directly below the MCU.

- Use a ground shield in the MCU layer and use the neighbor layer as the ground layer.

- Shield the area of oscillator bonding wires.

- Do not use the ground shield as the oscillator ground signal.

- Avoid ground loops. The oscillator ground signal must be connected at first to VSSD before connecting to the system ground.

- Make sure that the routing of the oscillator ground to VSSD is as short as possible.

- Do not route signals with strong pulses close to the oscillator. This is also valid for the neighbor layer.

Connect the silent ground of the oscillator to the system ground after passing the silent VSSD MCU pin to ensure a stable current return path. So, the via to the system ground will be usually below the MCU package and not between the oscillator and the silent MCU VSSD pin. See Figure 59 as an example.

- Noise emission

- Do not route sensitive signals close to the oscillator signals (example: analog sensor signals).

# 11.5.3 Crystal matching test

For each device package and ECU variant, a crystal matching test must be done by the crystal vendor. The oscillator MCU module must be configured according to the oscillator circuit. See AN230194 to learn how to configure the ECO module.

To reduce the iterations of matching activities between the customer and crystal vendor, a crystal matching test software is provided on demand. It can be directly used by the vendor to modify the preconfigured crystal setting from the customer for optimization. By default, a UART interface with a PC terminal is used. Due to the availability of the source code, another UART channel or even interface can be used.

# 11.6 Component placement

- The placement of analog components should be done in a way that the ground connection is on a common partition area. The same should be also done for digital components. The analog voltage reference regulator should be placed over the analog plane and the digital voltage regulator accordingly over the digital plane.

- Components with a common power supply should be located as centrally as possible to each other.

### Layout and electromagnetic compatibility

• The MCU and other mixed signal components should accordingly be placed on the PCB as a bridge between the analog and digital partitions.

# 11.7 Signal routing

- Digital power and signal traces should be routed over the digital ground planes and analog power and signal traces should be routed over the analog ground plane.

- To isolate analog signals traces, areas around the traces should be filled with copper, which are connected to analog ground plane. Accordingly, the same recommendation is also valid for areas with digital signal traces.

- Do not route traces near to or parallel to other noisy and sensitive traces.

- Keep the trace lengths as short as possible.

Furthermore, when designing an application, the following areas should be closely studied to improve the EMC performance:

- Noisy signals, for example, signals with fast edge times

- Sensitive and high-impedance signals

- Signals that capture events, such as interrupts and strobe signals

### Thermal considerations

# 12 Thermal considerations

Once an indication of the MCU total power requirement is known, it is very important to understand, whether the system design can properly dissipate this power into the ambient air efficiently enough. This determines whether further action or significant heat sinking and PCB design choices is required.

The MCUs cover a wide range of products from devices capable of very low power to MCUs with very fast complex logic requiring higher power needs. Under certain conditions, MCUs may dissipate more than 1 watt of power including the core, peripheral, and I/O currents. With a lot of power in a device, necessary steps must be considered to avoid it from overheating.

Before a design is finalized, a complete thermal review should be done. Items such as the amount of airflow through the system, nearby heat sources, and PCB construction should be reviewed. The examples given below are first steps to determine whether the preliminary design objectives can be met by taking the equation.

### **Calculation of junction temperature**

$$T_{\rm I} = T_{\rm A} + \Theta_{\rm IA} \times P_{\rm D}$$

Equation 3

T<sub>1</sub>: Junction temperature

T<sub>A</sub>: Ambient temperature

$\Theta_{JA}$ : Thermal resistance from junction to ambient

P<sub>D</sub>: Power dissipation

For a first-order approximation, first check the datasheet for the thermal resistance from junction to ambient  $(\theta_{JA})$  for the target device package.  $\theta_{JA}$  is expressed in units of °C/watt. These values are estimated with a 2s2p PCB per JESD51-9.

For example, the  $\theta_{JA}$  for an LQFP 120-pin is 38 °C/watt. For the same device in an LQFP 120-pin package with an exposed pad on the bottom side correctly mounted, the  $\theta_{JA}$  is reduced to 18 °C/watt, allowing a much higher total device power usage or a higher ambient operating temperature.

The maximum temperature difference between the device junction and the ambient air surrounding the device is  $\theta_{JA}$  times the maximum power, or as in the first case above, 38°C/watt x 1.0 watt = 38°C. Because the specified maximum operating junction temperature of the device is 125°C, the maximum allowable ambient air temperature is 125 – 38 = 87°C. If you use the exposed pad version of package, which has a lower thermal resistance  $\theta_{JA}$  of 18°C/watt if implemented with proper PCB to pad design, the maximum allowable ambient air temperature is 125°C – 18°C = 107°C. This allows a 20°C increase in ambient operating temperature or the possibility to drive more power from the device I/O or core.

Each datasheet for a device series contains a table showing package thermal resistance and maximum permissible power. This allows you to quickly see the amount of power that can practically be consumed by a device in a given package. In the DS, a recommended minimal PCB construction might be given. So, for example, a four-layer PCB has a better power dissipation characteristic than a two-layer PCB, because inner plane layers help to dissipate heat. Ensuring good contact between package exposed pad and leads with copper pads on the PCB would improve the heat dissipation from the package to the PCB and improve the junction temperature.

The need to use airflow and other cooling solutions must be determined on each case with the customer's own simulations.

### **Thermal considerations**

Note: The datasheet specifications for  $\square_{JA}$  are typical. The ambient air temperature should be much less

than the allowable maximum for the product design.

Note: With the above calculation, if the  $\square_{\mathsf{JA}}$  or the power dissipated is high, the maximum allowable

ambient air temperature could theoretically approach the 125°C junction temperature limit. However, the product's commercial-range ambient air temperature limit of 85°C or the industrial-range ambient air temperature limit of 105°C still applies. In the example above, the first example would be unacceptable for operating a consumer grade (85°C) device. In the second example, a consumer grade or industrial grade device would be well suited depending on the choice of

operating conditions of the final product.

MCUs offered in BGA or QFN packages have a reduced available surface area for thermal conduction due to the small package size; these packages must be thoroughly reviewed for power applications.

Detailed information is provided in the application notes AN72845, AN202751, and AN79938 listed in Related documents.

**ADC**

### 13 ADC

This section considers ADC and its analog input (AN) circuit for highly accurate sampling of the analog sensor level and potential other issues.

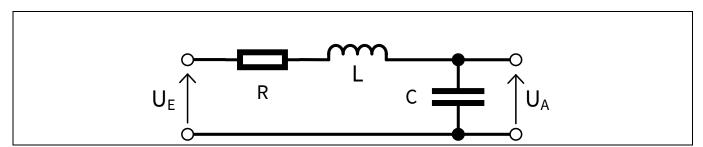

# 13.1 Filter design considerations for analog inputs

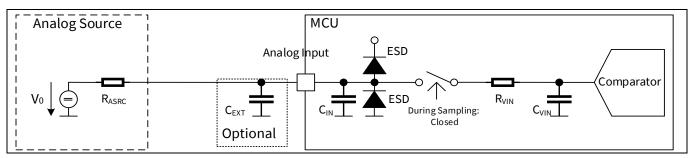

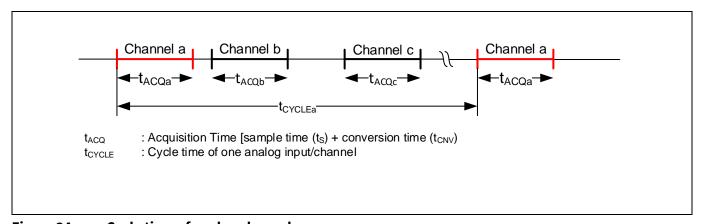

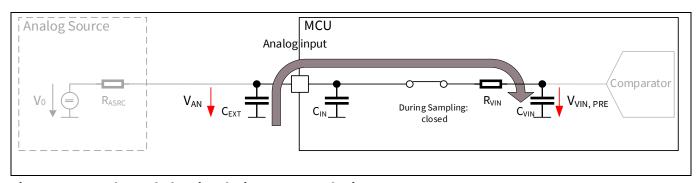

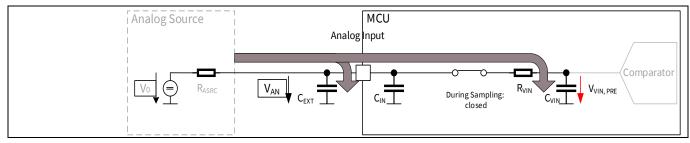

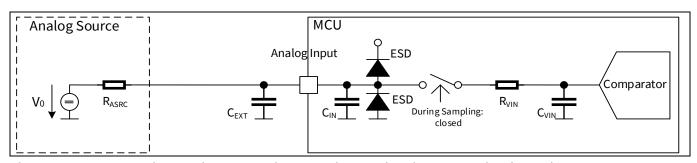

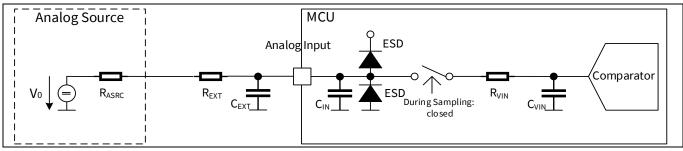

## 13.1.1 Principle of acquisition

The full period of sampling the analog value and then the conversion into a digital value is called acquisition time ( $t_{ACQ}$ ). The voltage level of the analog input is sampled by an internal sample capacitor ( $C_{VIN}$ ) within a configurable sample time ( $t_{c}$ ); the conversion time ( $t_{CNV}$ ) is implicitly configurable by the ADC clock input.

Figure 33 shows a principle circuit between the sensor, the analog source V<sub>0</sub>, and the analog input.

$t_{ACQ} = t_S + t_{CNV}$  Equation 4

Figure 33 Analog input with optional external buffer capacitor

Figure 34 Cycle time of analog channels

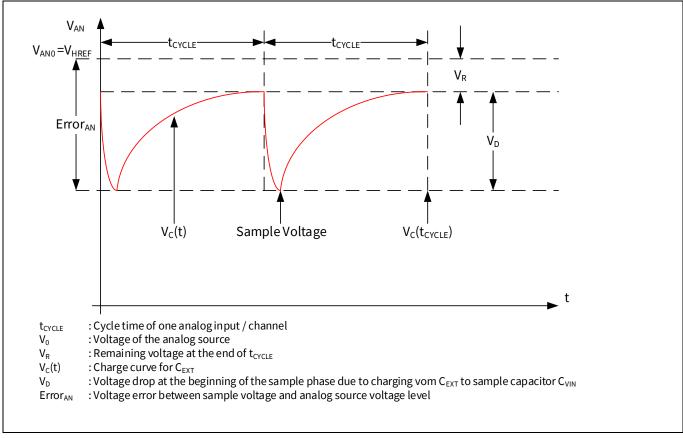

## 13.1.2 Accuracy at sample time

The sample time  $(t_s)$  must be long enough for charging  $C_{VIN}$  at the same level as the analog source, which means that that the internal resistance of the analog source  $(R_{ASRC})$  should be usually small enough. When  $R_{ASRC}$  is too high, either the sample time must be longer which has an impact on the total sample rate of all channels or the cycle time  $(t_{CYCLE})$ , the period between two acquisitions of a channel, must be longer accordingly (see Figure 33). After the cycle time, there should be either no or a neglectable voltage difference between the

**ADC**

analog source V<sub>0</sub> and the analog input (AN) before the next acquisition. When a channel is sampled twice or more directly one after the other, the following equation must be fulfilled:  $t_{CYCLE} \le t_{ACO}$ .

The following are the assumptions to be considered while calculating the cycle time  $t_{\text{CYCLE}}$ :

- The analog input must be reloaded to a new source level V<sub>0</sub> with a remaining voltage difference V<sub>R</sub> depending on the required resolution 2<sup>r</sup>. V<sub>R</sub> should be smaller than the sampled error.

- The reloading from the external capacitor C<sub>EXT</sub> to internal sample capacitor C<sub>VIN</sub> during the sample time extends the cycle time.

$$t_{CYCLE} = t_S + k \times \tau = t_S + \ln\left(\frac{2^r}{V_{R,LSB}}\right) \times \left(R_{ASRC} \times (C_{EXT} + C_{IN})\right)$$

Equation 5

Example:

Resolution: 12-bit

$V_{R,LSB}$ : 0.25 LSB = 0.25 x (1/2<sup>12</sup>)

$$t_{CYCLE} = t_S + k \times \tau = t_S + \ln\left(\frac{2^{12}}{0.25}\right) \times \left(R_{ASRC} \times (C_{EXT} + C_{IN})\right) = t_S + 9.7 \times \tau$$

Equation 6

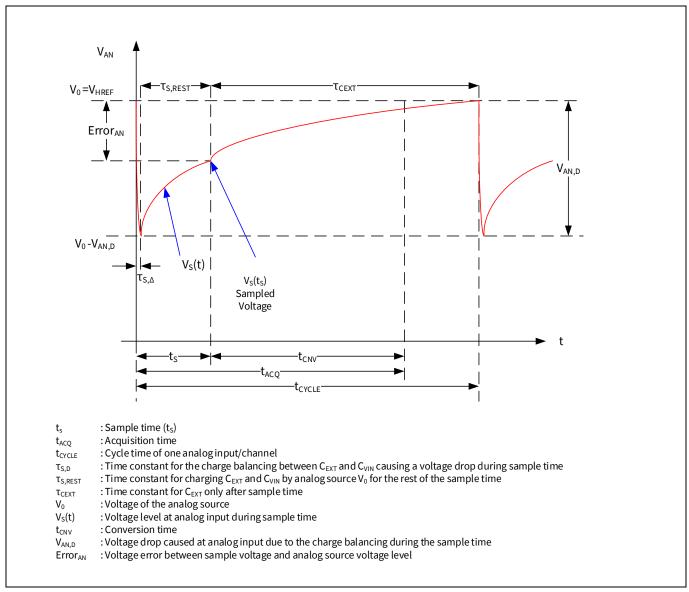

#### 13.1.3 Sample time charging process

During the sample phase, the sample capacitor CVIN is charged by the external capacitor CEXT until both reach a common voltage (charge balancing). After that, both capacitors are charged to the analog source level V<sub>0</sub> via the source resistance.

So, different time constants must be considered: