# NTAG I<sup>2</sup>C Technical Product Presentation

July 2014 Michael Salfer CAS

#### **Agenda**

#### General

- NFC Forum tag NDEF

- Product Portfolio Differences

#### NTAG I<sup>2</sup>C

- Overview

- Delivery Types

- Memory Structure

- RF Interface

- I<sup>2</sup>C Interface

- Features:

- Field Detection

- SRAM / SRAM Mirror

- Passthrough Mode

- Energy Harvesting

- Memory Arbitration

- Product Support Package

- Known Software Issues

### What is a NFC Tag?

- A NFC tag is a contactless tag capable of storing NDEF formatted data, which interoperates with ISO14443 infrastructure and NFC devices as defined by the NFC Forum

- A NFC Forum tag is compatible to one of four NFC Forum Tag platforms capable of storing NDEF formatted data

- ▶ ICODE, MIFARE Classic can be NFC tags, but <u>NOT</u> NFC Forum tags (ICODE is becoming a NFC Forum tag)

- UL, ULC, DESFire and SmartMX can be NFC Forum tags

- NTAGs are NFC Forum tags (already formatted)

# NFC Forum Type Tag Platform – Product Overview

| <b>,</b> T | he NFC Forum has standa<br>NFC Forum Platform | rdized 4 Type Tags Platform. Compatible Products |

|------------|-----------------------------------------------|--------------------------------------------------|

| 1          | NFC Forum Type 1 Tag                          | Innovision Topaz                                 |

|            |                                               |                                                  |

| 3          | NFC Forum Type 3 Tag                          | Sony Felica                                      |

|            |                                               |                                                  |

#### Similarly NXP has also specified

| NXP Specific Platform          | Compatible Products                                      |

|--------------------------------|----------------------------------------------------------|

| NFC Type MIFARE Classic<br>Tag | MIFARE Classic 1k / MIFARE Classic 4k / MIFARE Plus X/S  |

| NFC Type ICODE tag             | ICODE SLI/SLIX / ICODE SLI-S/SLIX-S / ICODE SLI-L/SLIX-L |

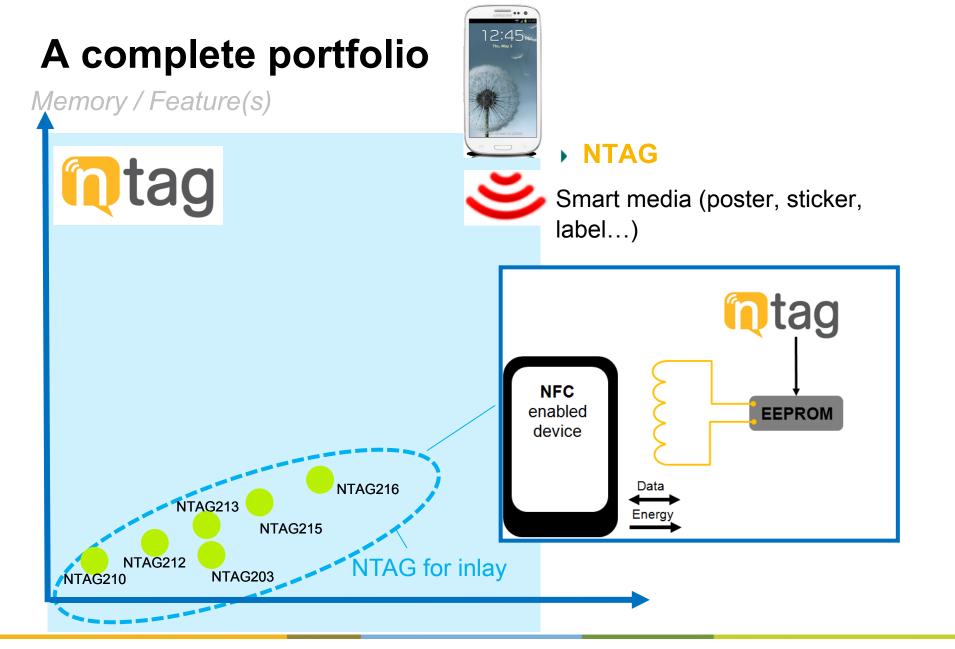

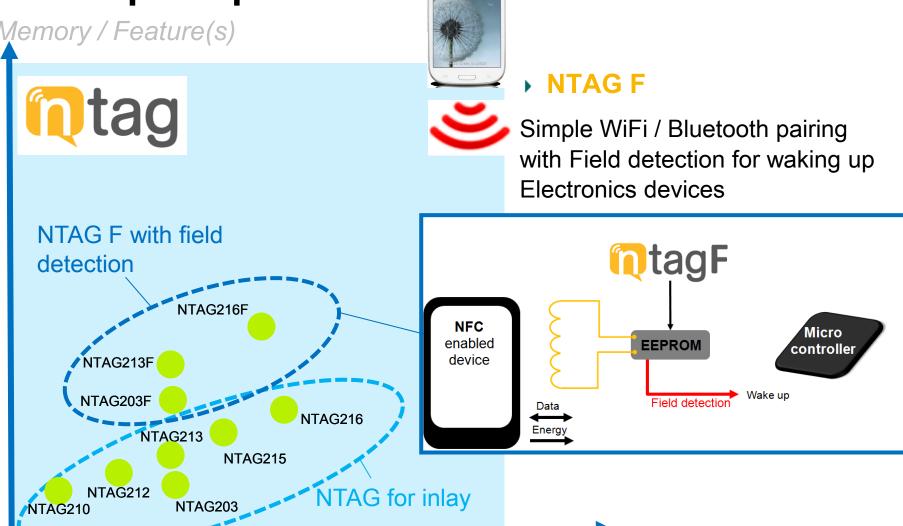

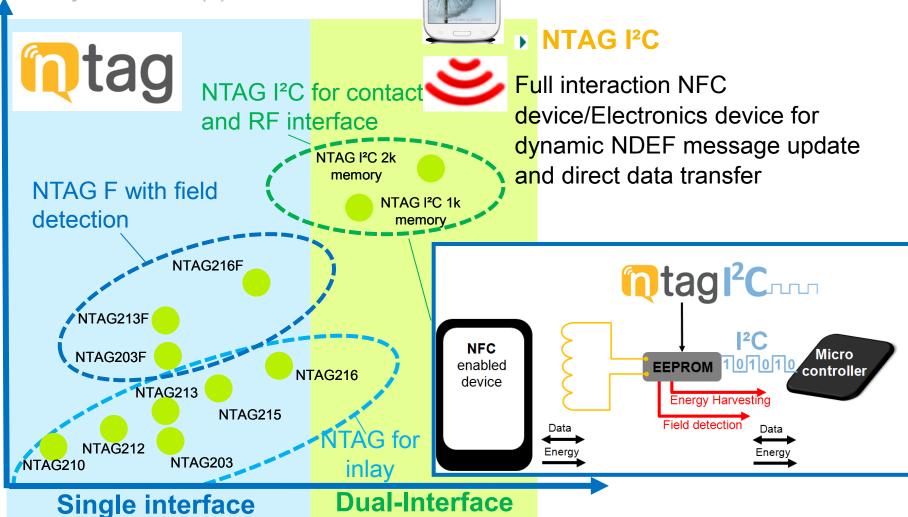

# Product portfolio

### A complete portfolio

Memory / Feature(s)

## A complete portfolio

Memory / Feature(s)

## Product differences

#### **NTAG Product Overview**

|                     | NTAG<br>203 | NTAG<br>203F | NTAG<br>210 / 212 | NTAG<br>213 / 215 / 216 | NTAG<br>213F / 216F | NTAG I2C<br>1k / 2k |

|---------------------|-------------|--------------|-------------------|-------------------------|---------------------|---------------------|

| User memory in byte | 144         | 144          | 48 / 128          | 144 / 504 / 888         | 144 / 888           | 888 / 1904          |

| Pwd auth            | -           | -            | r/w               | r/w                     | r/w                 | -                   |

| Capacitance         | 50 pF       | 50 pF        | 17 pF             | 50 pF                   | 50 pF               | 50 pF               |

| UID mirror          | -           | -            | •                 | •                       | •                   | -                   |

| NFC counter         | -           | -            | -                 | •                       | •                   | -                   |

| One way counter     | •           | •            | -                 | -                       | -                   | -                   |

| FD pin              | -           | •            | -                 | -                       | •                   | •                   |

| I2C                 | -           | -            | -                 | -                       | -                   | •                   |

| READ0 to ACTIVE     | •           | •            | •                 | •                       | •                   | -                   |

• = yes / supported

#### **RF Command Code Overview**

| Command                          | ISO/IEC 14443     | NFC Forum     | Code        | 203(F) | 210/<br>212 | 213(F)/<br>215/<br>216(F) | I2C<br>1k / 2k |

|----------------------------------|-------------------|---------------|-------------|--------|-------------|---------------------------|----------------|

| Request                          | REQA              | SENS_REQ      | 26h (7 bit) | •      | •           | •                         | •              |

| Wake-Up                          | WUPA              | ALL_REQ       | 52h (7bit)  | •      | •           | •                         | •              |

| Anticollision CL1                | Anticollision CL1 | SDD_REQ CL1   | 93h 20h     | •      | •           | •                         | •              |

| Select CL1                       | Select CL1        | SEL_REQ CL1   | 93h 70h     | •      | •           | •                         | •              |

| Anticollision CL2                | Anticollision CL2 | SDD_REQ CL2   | 95h 20h     | •      | •           | •                         | •              |

| Select CL2                       | Select CL2        | SEL_REQ CL2   | 95h 70h     | •      | •           | •                         | •              |

| Halt                             | HLTA              | SLP_REQ       | 50h 00h     | •      | •           | •                         | •              |

| Get_Version                      |                   |               | 60h         | -      | •           | •                         | •              |

| Read                             |                   | READ          | 30h         | •      | •           | •                         | •              |

| Fast_Read                        |                   |               | 3Ah         | -      | •           | •                         | •              |

| Write                            |                   | WRITE         | A2h         | •      | •           | •                         | •              |

| Comp_Write                       |                   |               | A0h         | •      | •           | •                         | -              |

| Read_Cnt                         |                   |               | 39h         | -      | -           | •                         | -              |

| Pwd_Auth                         |                   |               | 1Bh         | -      | •           | •                         | -              |

| Read_Sig                         |                   |               | 3Ch         | -      | •           | •                         | -              |

| Sector_Select (two part command) |                   | SECTOR_SELECT | C2h         | -      | -           | -                         | •              |

## NTAG I<sup>2</sup>C

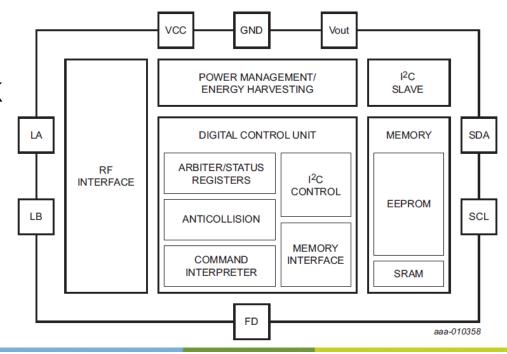

#### NTAG I<sup>2</sup>C Features

- NFC Forum Type 2 Tag compliant

- Dual interface

- NFC & I<sup>2</sup>C interface

- 50 pF input capacitance

- Either 888 or 1904 Byte of Non-Volatile User Memory

- PASS THROUGH mode for fast data transfer

- 64 bytes SRAM Buffer for RF→I<sup>2</sup>C and I<sup>2</sup>C→RF data transfer

- Mapped at the end of the memory sector

- Field detection feature

- Open drain implementation

- Configurable reaction on

- RF field presence

- · First valid command (State of Frame) / NDEF message read

- Device selection / Deselection

- Data read/written in the SRAM buffer

- Clear arbitration / customized access between the 2 interfaces

- Memory locked to one interface upon the other interface accessing the memory

- Status flag to check access status

- Flexible WRITE Access settings

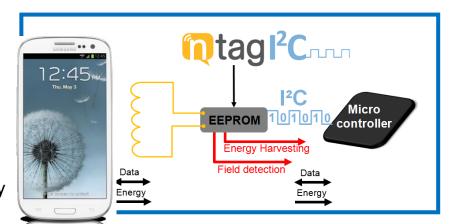

- Energy harvesting functionality to power external devices (e.g. μC)

- XQFN8 package (1,6\*1,6\*0,5mm)

#### NTAG I<sup>2</sup>C for a complete NFC Eco System

#### Home automation

Tap your phone to adjust settings or for commissioning Video (Youtube)

#### **Smart Meters**

Tap your phone to read out consumption data

#### NFC accessories

Tap your phone to configure or retrieve personal data

#### **Consumer Electronics**

Tap your phone to stream media or set the programming

#### **Appliances**

Tap your phone for service diagnostics or settings

Video (Youtube)

#### Healthcare

Tap your phone to read and upload vital measurements

# Some features in more detail on the following slides

- Passive Tag

- NTAG I<sup>2</sup>C can execute all RF operations in passive tag mode (powered by RF field)

- I<sup>2</sup>C Interface

- Easy I<sup>2</sup>C commands for EEPROM and SRAM access

- Field detection

- NTAG I<sup>2</sup>C can drive the open drain FD signal in passive tag mode

- Embedded SRAM

- can be used to transfer data (pass-through-mode) or be mirrored on the EEPROM

- Energy Harvesting

- can supply the I<sup>2</sup>C-part, the SRAM and external circuitry

## **Delivery types**

#### NTAG I<sup>2</sup>C

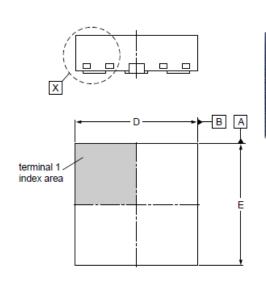

#### **Delivery Types Package and Pinning**

| Model                       | Package | Package<br>Version | Marking   | Сар   | Туре          | User<br>Memory |

|-----------------------------|---------|--------------------|-----------|-------|---------------|----------------|

| NTAG<br>I <sup>2</sup> C 1k | XQFN8   | SOT902-3           | N11 / yww | 50 pF | NT3H1101W0FHK | 888 bytes      |

| NTAG<br>I <sup>2</sup> C 2k | XQFN8   | SOT902-3           | N12 / yww | 50 pF | NT3H1201W0FHK | 1904 bytes     |

V0F V0B-V0E Marking of Engineering Sample

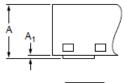

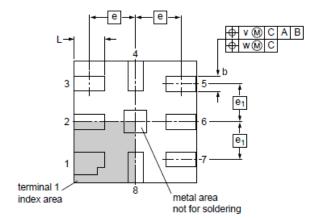

## Package SOT902-3 (XQFN8)

#### Marking of Engineering Sample

| Dimer | scale             | )   |                |   |      |      |     |                |                      |     |      |      |      |

|-------|-------------------|-----|----------------|---|------|------|-----|----------------|----------------------|-----|------|------|------|

| U     | nit               | Α   | A <sub>1</sub> | b | D    | Ε    | е   | e <sub>1</sub> | L                    | v   | w    | у    | У1   |

| mm    | max<br>nom<br>min | 0.5 | 0.05           |   | 1.60 | 1.60 | 0.6 | 0.5            | 0.45<br>0.40<br>0.35 | 0.1 | 0.05 | 0.05 | 0.05 |

#### Note

1. Plastic or metal protrusions of 0.075 mm maximum per side are not included.

| Pin | Symbol | Description                              |

|-----|--------|------------------------------------------|

| 1   | LA     | Antenna coil connection LA               |

| 2   | VSS    | GND connection                           |

| 3   | SCL    | Serial Clock I <sup>2</sup> C connection |

| 4   | FD     | RF field detection connection            |

| 5   | SDA    | Serial Data I <sup>2</sup> C connection  |

| 6   | VCC    | VCC in connection                        |

| 7   | Vout   | Voltage out (energy harvesting)          |

| 8   | LB     | Antenna coil connection LB               |

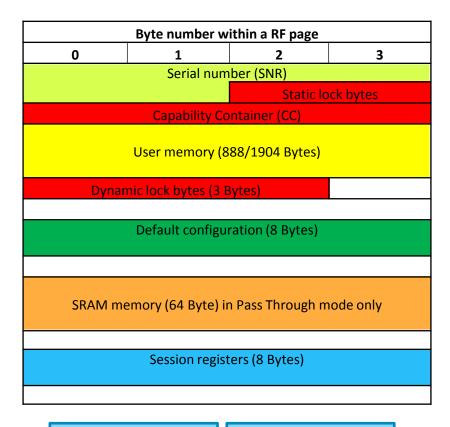

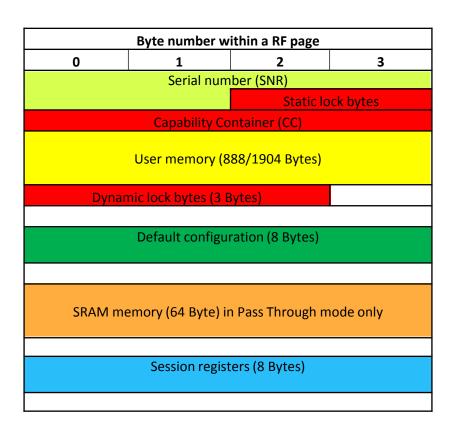

# Memory structure

### NTAG I<sup>2</sup>C Memory Structure

- 888/1904 Byte User Memory

- Organization RF:

- 4 byte per page

- 256 pages per sector

- NTAG I<sup>2</sup>C 1k: 1 sector data

- NTAG I<sup>2</sup>C 2k: 2 sectors of data

- Organization I<sup>2</sup>C:

- 16 byte per block

- No sectors

Detail 1k RF Detail 1k I<sup>2</sup>C

Detail 2k RF Detail 2k I<sup>2</sup>C

### NTAG I<sup>2</sup>C Memory Access Rights

#### ▶ 888/1904 Byte User Memory

| Momony           | Re | ad               | Write            |                  |  |  |  |  |

|------------------|----|------------------|------------------|------------------|--|--|--|--|

| Memory           | RF | I <sup>2</sup> C | RF               | I <sup>2</sup> C |  |  |  |  |

| Serial Number    | ok | ok               | -                | I2C<br>Address * |  |  |  |  |

| Lock Bytes / CC  | ok | ok               | OTP,<br>lockable | ok               |  |  |  |  |

| User Memory      | ok | ok               | Ok,<br>lockable  | ok               |  |  |  |  |

| Configuration    | ok | ok               | ok,<br>lockable  | ok,<br>lockable  |  |  |  |  |

| SRAM             | ok | ok               | ok               | ok               |  |  |  |  |

| Session Register | ok | ok               | -                | ok               |  |  |  |  |

\*: I<sup>2</sup>C Address only writeable, but not readable

### **Special memory Block: Lock bits**

Static Lock Bits (static position)

| Static L | ock Bit | S   | Address Byte / Bit |   |   |   |    |       |     |    |    |    |    |    |    |    |   |   |  |

|----------|---------|-----|--------------------|---|---|---|----|-------|-----|----|----|----|----|----|----|----|---|---|--|

|          | Page 2  |     |                    |   |   |   |    |       |     |    | 3  |    |    |    |    |    |   |   |  |

| Model    | Dec     | hex | 7                  | 6 | 5 | 4 | 3  | 2     | 1   | 0  | 7  | 6  | 5  | 4  | 3  | 2  | 1 | 0 |  |

| NTAG I2C | 2       | 02h | 7                  | 6 | 5 | 4 | CC | 10-15 | 4-9 | CC | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |  |

Dynamic Lock Bits (position depends on memory size)

| Dyna                     | Dynamic Lock Bits |        |     |      |      |      |      |      |     |     |     |      |      | Add  | lress | Byte | / Bit |      |      |      |      |      |      |      |      |     |     |

|--------------------------|-------------------|--------|-----|------|------|------|------|------|-----|-----|-----|------|------|------|-------|------|-------|------|------|------|------|------|------|------|------|-----|-----|

|                          | Pag               | e Addı | ess |      |      |      | (    | )    | 1 2 |     |     |      |      |      |       |      |       |      |      |      |      |      |      |      |      |     |     |

| Model                    | Sector            | Dec    | Hex | 7    | 6    | 5    | 4    | 3    | 2   | 1   | 0   | 7    | 6    | 5    | 4     | 3    | 2     | 1    | 0    | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|                          |                   |        |     | 128- | 112- | 96-  | 80-  | 64-  | 48- | 32- | 16- |      |      | 224- | 208-  | 192- | 176-  | 160- | 144- | RFUI | 208- | 176- | 144- | 112- | 80-  | 48- | 16- |

| NTAG I <sup>2</sup> C 1k | 0                 | 226    | E2h | 143  | 127  | 111  | 95   | 79   | 63  | 47  | 31  | RF   | UI   | 225  | 223   | 207  | 191   | 175  | 159  |      | 225  | 207  | 175  | 143  | 111  | 79  | 47  |

|                          |                   |        |     | 240- | 208- | 176- | 144- | 112- | 80- | 48- | 16- |      | 464- | 432- | 400-  | 368- | 336-  | 304- | 272- | 464- | 400- | 336- | 272- | 208- | 144- | 80- | 16- |

| NTAG I <sup>2</sup> C 2k | 1                 | 224    | E0h | 271  | 239  | 207  | 175  | 143  | 111 | 79  | 47  | RFUI | 479  | 463  | 431   | 399  | 367   | 335  | 303  | 479  | 463  | 399  | 335  | 271  | 207  | 143 | 79  |

Lock bit: to lock corresponding page(s) to read only

Block lock bit: to lock corresponding lock bits (disable changing of lock bits)

Note: after writing to lock area the changes are immediately active

Note: Access from RF = OTP, Access from I2C = read/write

Note: for setting the lockbits according to NFC Forum rules, look at AN11456

"NTAG215\_216(F)\_I2C Using the dynamic lock bits to lock the tag\_2769xx"

AN In publish process

#### NTAG I<sup>2</sup>C

## **Memory Initialization - NDEF**

- Memory is already initialized with CC and TLVs to be used for NDEFstorage

- TLV = Type, Length, Value (generic container for data)

| Memory I                 | Initialization | Page / Byte    |         |             |                  |    |     |                                                                |    |    |         |                      |    |  |  |

|--------------------------|----------------|----------------|---------|-------------|------------------|----|-----|----------------------------------------------------------------|----|----|---------|----------------------|----|--|--|

|                          |                |                | Pag     | e 03        |                  |    | Pag | e 04                                                           |    |    | Page 05 |                      |    |  |  |

| Model                    | Mem Bytes      | 0              | 1       | 2           | 3                | 0  | 1   | 2                                                              | 3  | 0  | 1       | 2                    | 3  |  |  |

| NTAG I <sup>2</sup> C 1k | 888            | E1             | 10      | 6D          | 00               | 03 | 00  | FE                                                             | 00 | 00 | 00      | 00                   | 00 |  |  |

| NTAG I <sup>2</sup> C 2k | E1             | 10             | EA      | 00          | 03               | 00 | FE  | 00                                                             | 00 | 00 | 00      | 00                   |    |  |  |

| Desc                     | cription       | NDEF-Indicator | Version | Memory Size | Access Indicator |    |     | Lock Control TLV<br>(Specify Position of<br>Dynamic Lock Bits) |    |    |         | Zero Length NDEF TLV |    |  |  |

Note: for setting the lockbits according to NFC Forum rules, look at AN11456 "NTAG215 216(F) I2C Using the dynamic lock bits to lock the tag 2769xx"

AN In publish process

## Special Memory Block: Configuration and **Session Registers**

- Configuration bytes are stored in EEPROM and are loaded in the session registers of NTAG I<sup>2</sup>C on power up

- Define power-up behavior

- Changes of the configuration bytes are only affective after Power on reset

- Configuration is readable and writable from both interfaces

- Write protection possible (REG\_LOCK)

- Session registers contain current configuration and status of the tag

- Used for runtime configuration and data transfer synchronization (Passthrough mode)

- readonly via RF (prevent unwanted configuration from RF)

- writeable for I<sup>2</sup>C (the I<sup>2</sup>C host has always full control over the tag)

July 14

## RF interface

### NTAG Read (30h)

- READ command needs page address as parameter

Tag returns 16 bytes (4 pages), starting from provided page address

- Note Ultralight: Reading over the end of the tag memory wraps over to the first page Note NTAG I<sup>2</sup>C: Reading over the end of the memory returns zero filled bytes

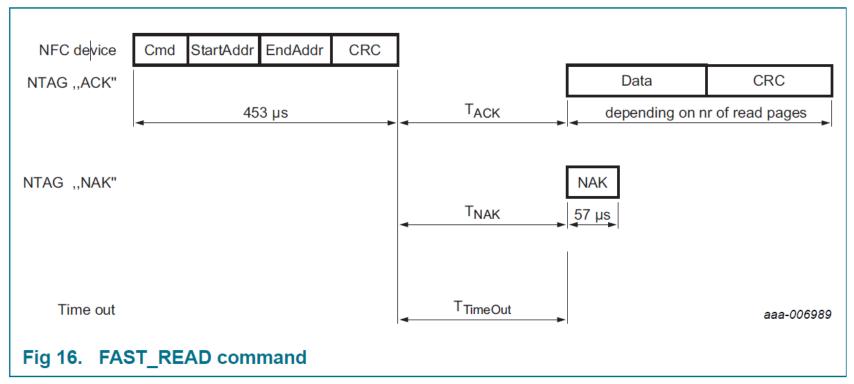

### NTAG Fast\_Read (3Ah)

With FAST\_READ one entire memory sector can be read with one command

Note Ultralight: Reading over the end of the tag memory wraps over to the first page Note NTAG I<sup>2</sup>C: Reading over the end of the memory returns zero filled bytes

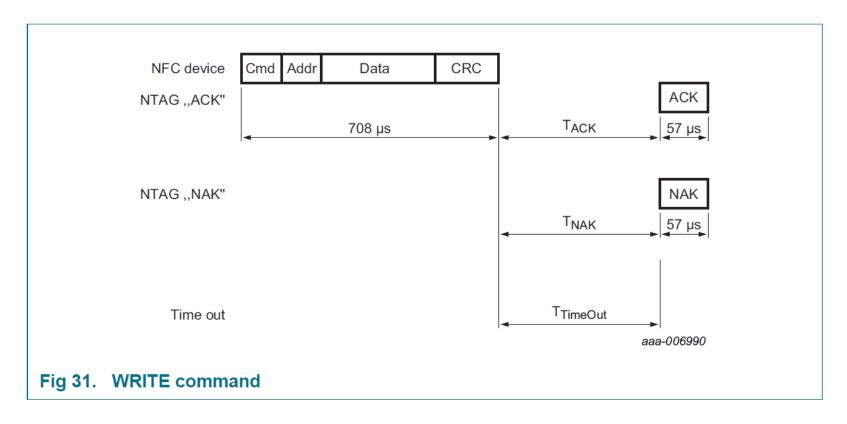

### **NTAG Write (A2h)**

WRITE command needs page address and 4 bytes of data as parameters

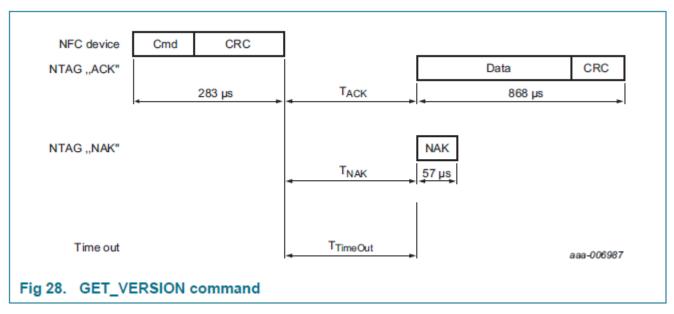

## NTAG Get\_Version (60h)

Provides 8 byte of identification data to exactly identify which NXP-IC it is

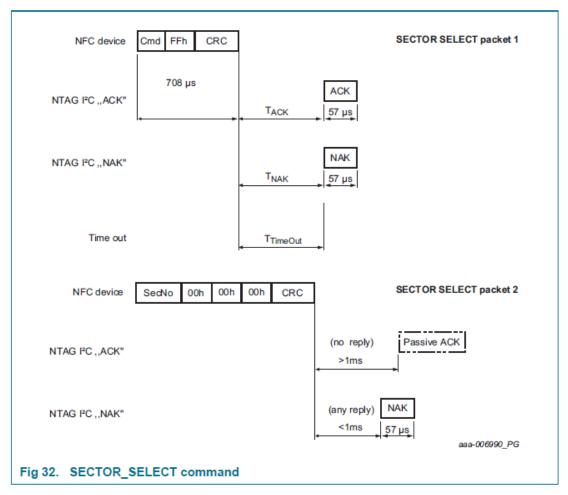

## NTAG Sector\_Select (C2h)

Changes active memory sector which is accessed by read/write Note: second part of command has a passive ACK – no response is ACK!

July 14

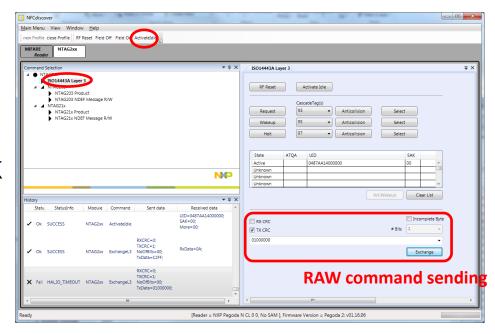

### NFC Discover: sending the sector\_select

- Press Activate Idle if not done yet

- In 14443A-Layer 3 Window:

- Deselect RX-CRC

- Enter C2FF in command field

- Click Exchange tag sends ACK

- Enter sector number + 3x "00",e.g. 01000000 for sector 1

- Click Exchange tag sends nothing! Ignore error in NFC Discover

You can now read/write in sector 1 until the next tag activation

## l<sup>2</sup>C interface

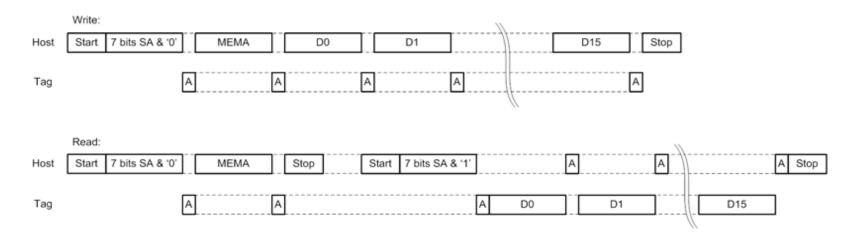

# I<sup>2</sup>C Communication on NTAG I<sup>2</sup>C Memory Access

- For accessing memory and registers there are two different commands

- I<sup>2</sup>C Memory Access

- access the EEPROM and SRAM

- read/write always 16 byte

Note: If I2C\_RESET\_ON\_REPEATED\_START is set, don't forget the STOP after the first part of the read command (I<sup>2</sup>C Bird does not send STOP with GUI)

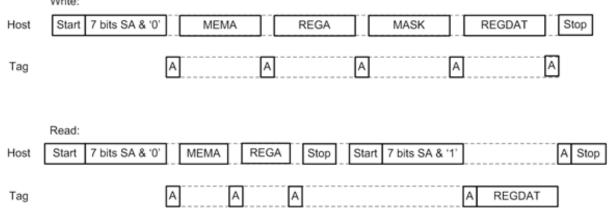

# I<sup>2</sup>C Communication on NTAG I<sup>2</sup>C Register Access

- I²C Register Access:

- access the Session registers located in 0xFE (I<sup>2</sup>C block address) read/write always only one byte

- MEMA = 0xFE

- REGA = 0 6

Note: If I2C\_RESET\_ON\_REPEATED\_START is set, don't forget the STOP after the first part of the read command (I<sup>2</sup>C Bird does not send STOP with GUI)

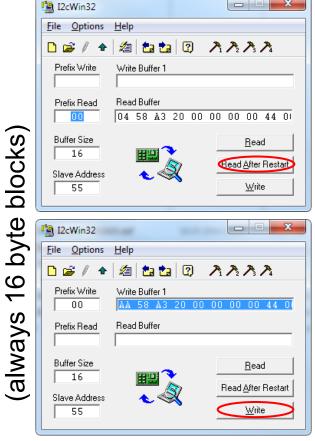

#### NTAG I<sup>2</sup>C Communication with I<sup>2</sup>C Bird

Connect the Bird with 3V levelshifter to the tag (e.g. from UCODE I<sup>2</sup>C)

Read/Write Register (always one byte)

I2cWin32 File Options Help  $\lambda \lambda \lambda \lambda$ Prefix Write Write Buffer 1 Read Buffer Prefix Read 01 Buffer Size Read Read After Restart Slave Address <u>W</u>rite 55 - - X I2cWin32 File Options Help AAAA Prefix Write Write Buffer 1 FE 00 Prefix Read Read Buffer Buffer Size Read Read After Restart Slave Address 55 Write

Note: If I2C\_RESET\_ON\_REPEATED\_START is set, don't forget the STOP after the first part of the read command (I<sup>2</sup>C Bird does not send STOP with GUI)

Read/Write Memory

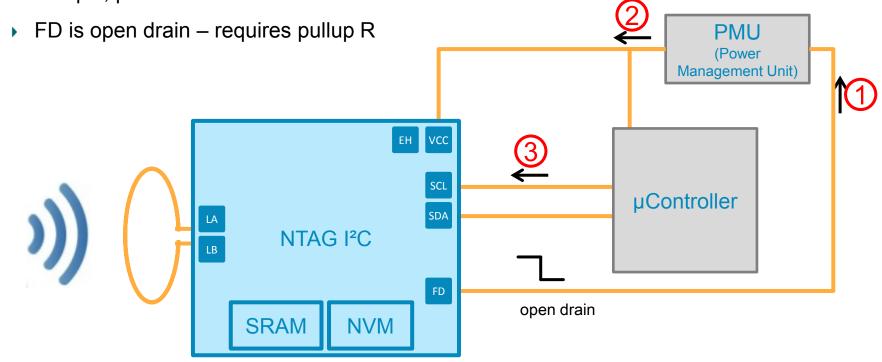

## **Special feature (1): Field Detection**

# Wake up on field detect - Passive tag mode

For battery saving, the whole system can be powered up upon Field Detection

FD goes low when field is detected; PMU receives interrupt, switches on VCC on NTAG and μC; μC activates I<sup>2</sup>C

# Field Detection Pin Configuration

- The ON and OFF-conditions for the FD pin can be configured:

- FD\_ON (FD goes low):

- field is switched on

- first valid SOF (retrigger only possible after RF-reset)

- tag reaches state "ACTIVE" (anti-collision done, retriggerable without RF-reset)

- In pass-through-mode:

- RF→I2C: data is ready for I2C to be read

- I2C→RF: data is ready for RF to be read

- FD\_OFF (FD goes high):

- field is switched off

- field off or tag in HALT state

- field switched off or NDEF message got read based on register LAST\_NDEF\_BLOCK

- pass-through-mode:

- If FD\_ON=0x3:

- RF→I2C: last data read by I2C

- I2C→RF: last data written by I2C

- If FD OFF!=0x3:

- If the field is switched OFF

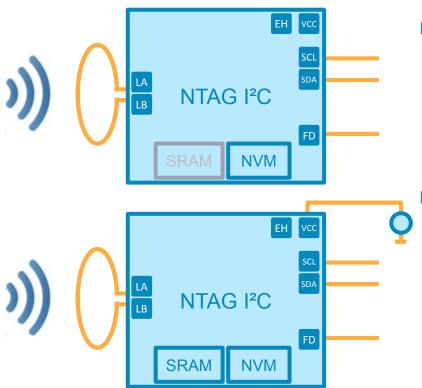

# Special feature (2): SRAM

# **Embedded 64-byte SRAM**

- Passive tag mode

- Tag works like a normal Type 2 tag with EEPROM

- SRAM not useable without supply on VCC

- VCC powered

- SRAM accessible from I<sup>2</sup>C, from RF when enabled (SRAM Mirror or Pass-through)

- SRAM available for

- Fast data transfer

- Unlimited endurance

# Special feature (3): SRAM Mirror

# **SRAM Mirroring**

- The SRAM can be mirrored into the user memory

- Behaves like a overlay each read and write from RF to that addresses is not executed on the underlying EEPROM, but on the SRAM

- EEPROM content is not influenced

- Use-Case:

- Dynamic Update of e.g. pairing information (write every some seconds a new key)

- Address is given by register SRAM\_MIRROR\_BLOCK

- Use the address like seen from I<sup>2</sup>C

- Only addresses with valid user memory are usable

- Hints:

- Not combinable with pass-through-mode

- The mirroring is only effective for the RF side, I<sup>2</sup>C has to use the fixed SRAM address

# **SRAM Mirroring – memory map illustration**

- Example:

- NTAG I<sup>2</sup>C 1k

- SRAM\_MIRROR enabled

- SRAM\_MIRROR\_BLOCK= 0x01

- ➤SRAM Mirror starts on RF page 0x04 (Block address multiplied by 4)

| Sector adr | Page address |            | Byte number within a page                                                                   |                |                   |                   | Access     |

|------------|--------------|------------|---------------------------------------------------------------------------------------------|----------------|-------------------|-------------------|------------|

| Hex        | Dec.         | Hex.       | 0                                                                                           | 1              | 2                 | 3                 | conditions |

| 0h         | 0            | 0h         | Serial number                                                                               |                |                   | READ              |            |

|            | 1            | 1h         | Serial number                                                                               |                | Internal data     | READ              |            |

|            | 2            | 2h         | Internal data                                                                               |                | lock bytes        |                   | READ/R&W   |

|            | 3            | 3h         | Capability Container (CC)                                                                   |                |                   | READ              |            |

|            | 4            | 4h         | SRAM memory (16 pages) with memory mirror mode enabled only with SRAM_MIRROR_ADDR set to 1h |                |                   | READ & WRITE      |            |

|            |              |            |                                                                                             |                |                   |                   |            |

|            | 19           | 13h        |                                                                                             |                |                   |                   |            |

|            |              |            | User memory                                                                                 |                |                   |                   |            |

|            | 225          | E1h        |                                                                                             |                |                   |                   |            |

|            | 226          | E2h        | Dynamic lock bytes 00h                                                                      |                | 00h               | R&W/R             |            |

|            | 227          | E3h        | •                                                                                           |                |                   |                   | n.a.       |

|            | 228          | E4h        | Invalid access - returns NAK                                                                |                |                   |                   |            |

|            | 229          | E5h        |                                                                                             |                |                   |                   |            |

|            | 230          | E6h        |                                                                                             |                |                   |                   |            |

|            | 231          | E7h        |                                                                                             |                |                   |                   |            |

|            | 232          | E8h        | Configuration                                                                               |                |                   | See section 8.5.9 |            |

|            | 233          | E9h        |                                                                                             |                |                   |                   |            |

|            | 234          | EAh        | Invalid access - returns NAK                                                                |                |                   | n.a.              |            |

|            |              |            |                                                                                             |                |                   |                   |            |

|            | 240          | F0h        |                                                                                             |                |                   | READ & WRITE      |            |

|            |              |            | SRAM memory (16 pages)                                                                      |                |                   |                   |            |

|            | 255          | FFh        |                                                                                             |                |                   |                   |            |

| 1h         |              |            | Invalid access - returns NAK                                                                |                |                   | n.a.              |            |

| 2h         |              |            |                                                                                             | Invalid access | - returns NAK     |                   | n.a.       |

| 3h         | 0            | <b>0</b> h | Invalid access - returns NAK                                                                |                | Г                 |                   |            |

|            |              |            |                                                                                             |                | n.a.              |                   |            |

|            | 248          | F8h        | Session registers                                                                           |                | See section 8.5.9 |                   |            |

|            | 249          | F9h        |                                                                                             |                |                   |                   |            |

|            |              |            | Invalid access - returns NAK                                                                |                |                   |                   |            |

|            | 255          | FFh        |                                                                                             |                |                   | n.a.              |            |

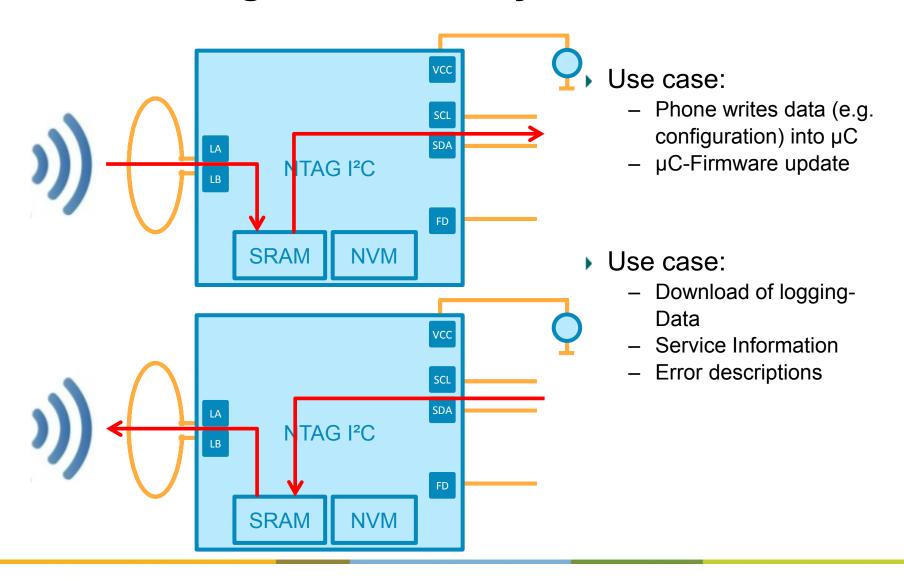

# Special feature (4): Pass Through

# **Pass-through functionality**

# Pass-Trough mode features

- Passthrough automates signalling for the arbitration of RF and I2C side. It provides help to speed up the communication.

- A read/write of the last SRAM page/block triggers the side switch

- Synchronization signalling on I<sup>2</sup>C-side can be done either by:

- Field detect pin

- Polling on register NS\_REG (bit SRAM\_I2C\_READY and SRAM\_RF\_READY)

- Synchronization signalling on RF side can be done by

- Polling on register NS\_REG (bit SRAM\_I2C\_READY and SRAM\_RF\_READY)

- Timing, when μC-timing is reproducible

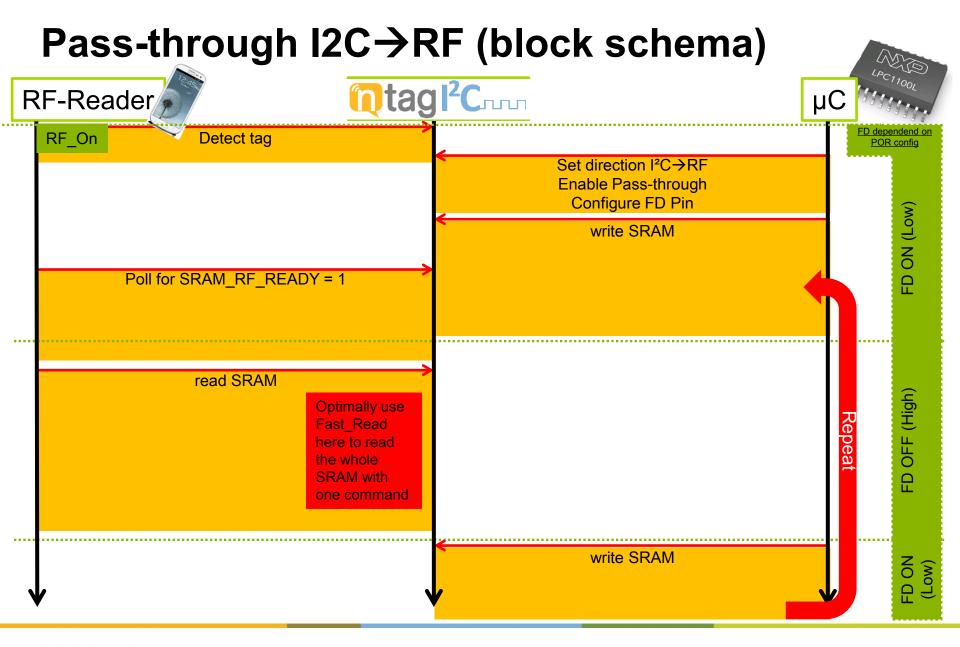

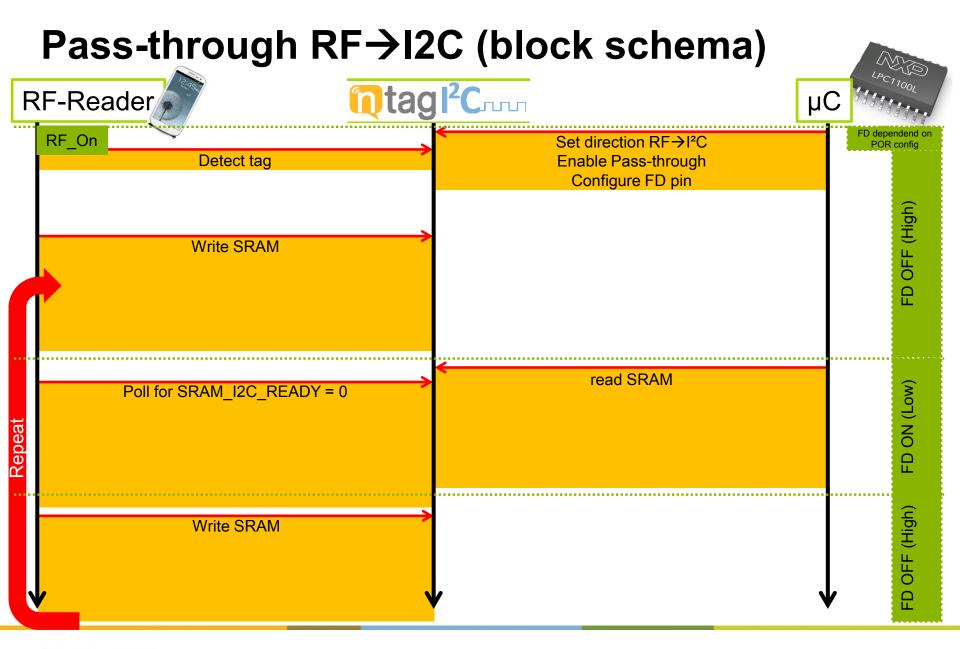

# Pass Through Mode Command flow

- The following slides illustrate the communication in pass trough mode

- shown is the mode with:

- synchronization RF-side: polling

- Wait for SRAM\_RF\_READY = 1 → Data ready in SRAM for RF to be fetched

- Wait for SRAM\_I2C\_READY = 0 → Data was fetched from SRAM by I<sup>2</sup>C

- synchronization I<sup>2</sup>C-side: Field detect pin

- Slides with title "block schema" shows the basic communication blocks

- Slides with title "details" shows commands in more depth, but not all

### Pass through implementation hints

- Pass through and SRAM Mirror activation It needs to be (re-)enabled in the session register after every power down of RF or I2C, it cannot effectively enabled in the configuration to be on automatically on every power up

- Memory locked to one side in pass through When the pass-through mode is enabled, the arbiter locks the memory access either to RF or I2C – the other side can the access the memory only, when the active side was changed by the arbiter (due to a read/write to the terminator page in SRAM)

- In case of communication with mobile phones the time where I2C accesses the memory has to be kept as short as possible, because some phones need regular memory access to keep RF active – if the memory access fails, RF is switched off and pass-through is automatically disabled

- Use FAST\_READ: Readout from SRAM with RF can be speed up by using FAST\_READ to read the whole SRAM with one command. FAST\_READ can not be used to read the registers.

### Pass through implementation hints

- ▶ **Bit PTHRU\_DIR in NC\_REG:** Double function, is also write enable in non-passthroughmode. If set to 0, memory is readonly from RF

- Bidirectional communication: before changing the passthrough direction with PTHRU\_DIR, always disable PTHRU\_ON\_OFF first

- Fastest combination:

- Use the FD pin on the I<sup>2</sup>C side

- On RF use polling only to detect the start of the transfer and do the following transfers based on timing

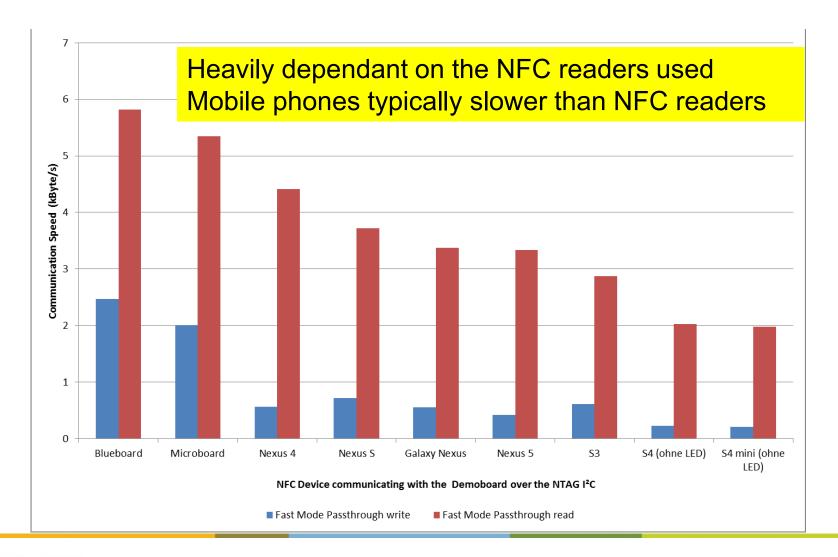

# Pass-through – Speed Test

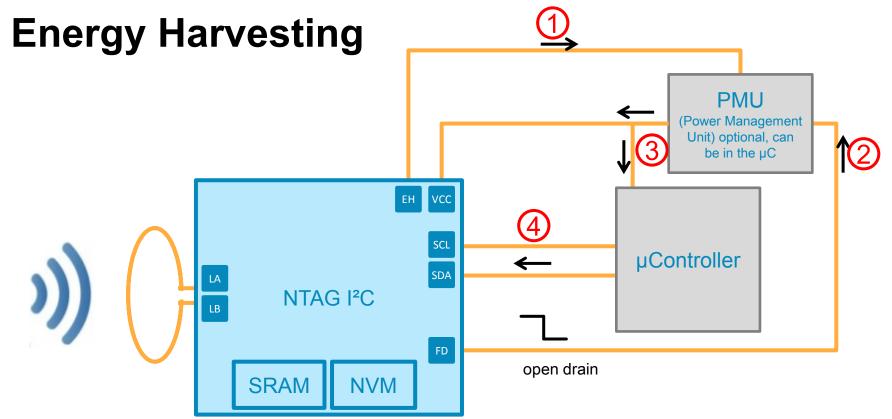

# Special feature (5): Energy harvesting

- With energy harvesting a microcontroller can be supplied with power

- Typically >5mA @2V

- Up to 13mA in case of strong NFC readers (not NFC phones)

- Power up can be controlled by Field Detection for further power management optimization

- FD goes low when field is detected; PMU receives interrupt, switches on VCC on NTAG and  $\mu$ C;  $\mu$ C starts communication on I<sup>2</sup>C

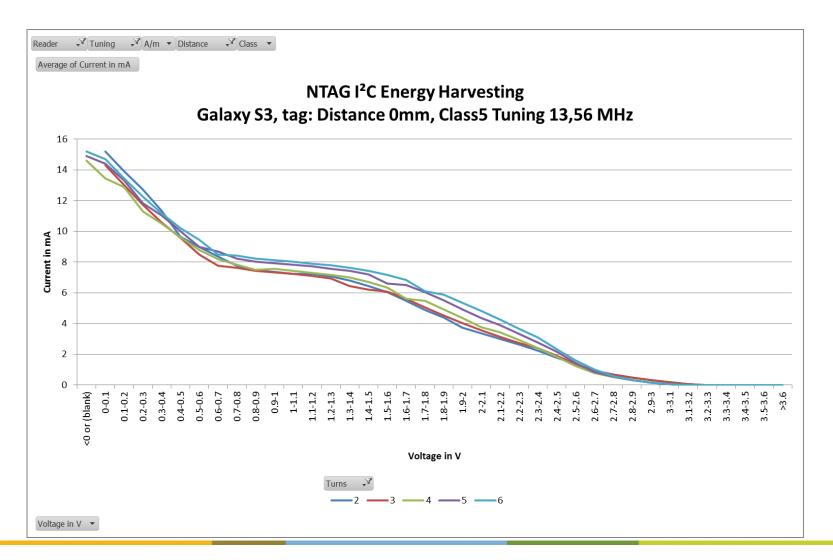

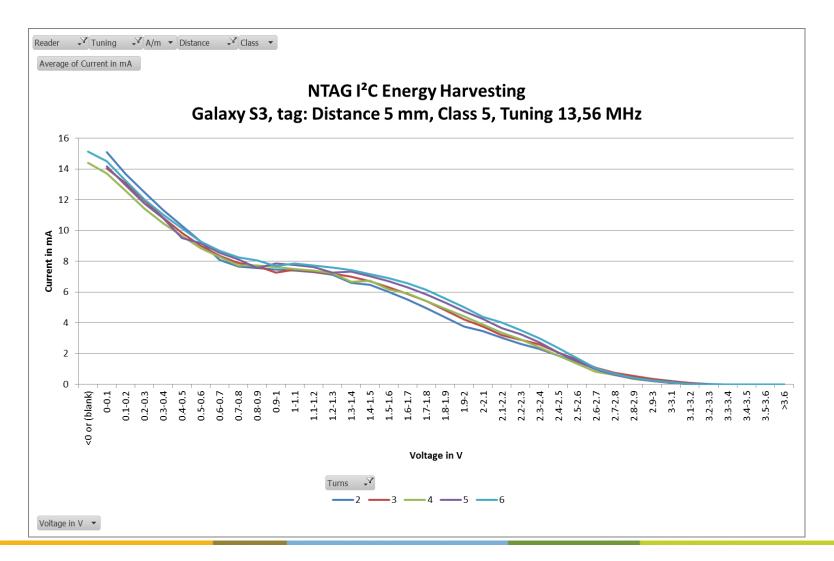

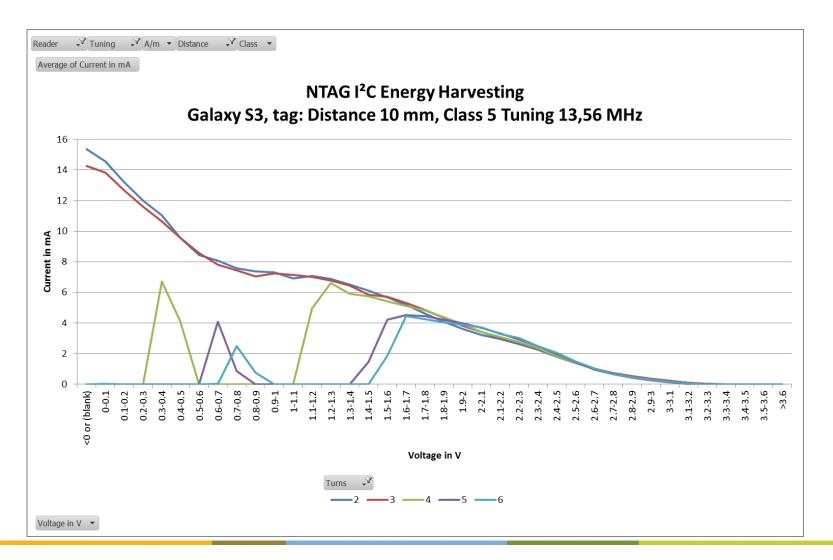

# Influence factors on Energy Harvesting

- Reader:

- Field strength

- "Stiffness" of the reader

- Antenna Geometry

- Size

- Antenna Turn Count

- Tuning (low influence)

- A higher turncount improves Energy Harvesting output power on mobile phones in close coupling

- Reducing the turncount improves the stability of energy harvesting in the distance

- Application Note in preparation, ready: R-Gate, CW1431

# **Energy Harvesting – Achievable Power**

# **Energy Harvesting – Achievable Power**

# **Energy Harvesting – Achievable Power**

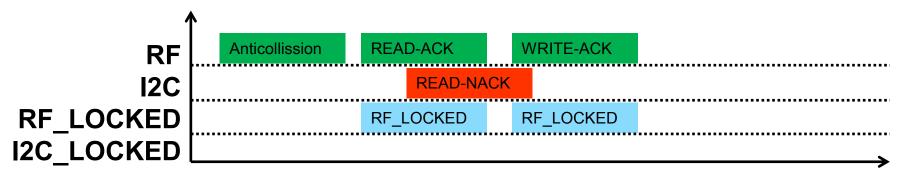

# **Memory Arbitration**

# NTAG I<sup>2</sup>C Memory Arbitration

- Registers can always be read/written

- RF and I<sup>2</sup>C cannot access the EEPROM / SRAM at the same time

- → Arbiter controls access to the memory

Arbiter status in NS\_REG:

- ▶ RF\_LOCKED

→RF Access to Memory OK

→I2C has no access

- I2C\_LOCKED for I2C

→I<sup>2</sup>C access to memory OK

→RF has no access

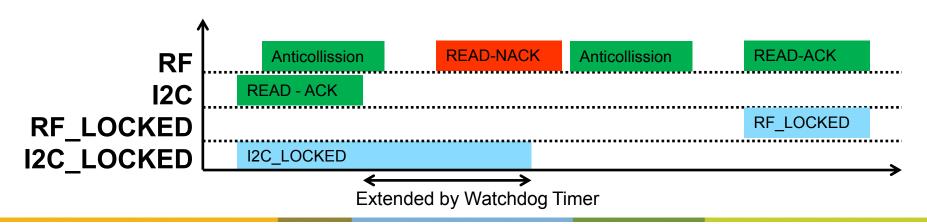

# NTAG I<sup>2</sup>C Memory Arbitration Normal mode (non-passthrough)

- Each RF read/write on memory sets RF\_LOCKED during the handling of the RF command. It clears directly afterwards.

- Each I<sup>2</sup>C read/write on memory sets I2C\_LOCKED. To prevent intermittent RF accesses it stays locked after the command. It either needs to be cleared manually by

- Sending a different slave-address on I<sup>2</sup>C as the NTAG I<sup>2</sup>C has

- Writing 0 to I2C\_LOCKED over I<sup>2</sup>C

- Or it gets automatically unset by the Watchdog timer

- Default timeout: 20 ms

**Reason:** the delayed clearing of I2C\_LOCKED is to prevent RF accesses on partially updated memory

# NTAG I<sup>2</sup>C Memory Arbitration Normal mode (non-passthrough)

RF-Access:

I2C-Access:

# NTAG I<sup>2</sup>C Memory Arbitration Pass Through Mode

- Access to EEPROM and SRAM has the same locking bit when the SRAM is accessed by one interface, also the EEPROM is not accessible by the other interface

- the arbiter locks the memory access exclusively to the current active side.

- The other side can meanwhile only access the registers

- Two additional bits signal the availability of new data in the SRAM:

- SRAM\_I2C\_READY: Data is ready in SRAM to be fetched by I2C

- SRAM\_RF\_READY: Data is reay in SRAM to be fetched by RF

- The arbiter switches automatically the active side and sets/clears the SRAM\_xx\_READY flags, when the last page/block of the SRAM was read/written

# Product support package

# NTAG I<sup>2</sup>C General Support Tools

- PC-Software

- NFC Discover (usable with Pegoda)

- http://www.nxp.com/documents/software/SW275410.zip

- Android general

- NFC TagInfo by NXP (in Google PlayStore)

- Identify tag and read memory

- NXP TagWriter by NXP (in Google PlayStore)

- Store NDEF messages

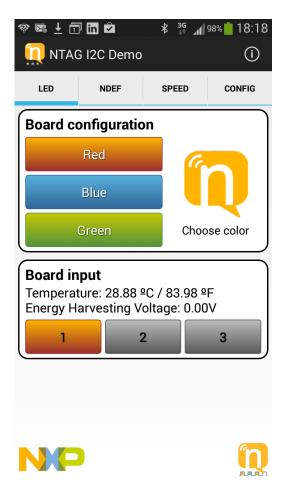

- Android: "NTAG I2C Demoboard"

- Controlling LEDs and showing communication speed available on Google Play store "NTAG I2C Demoboard"

# NTAG I<sup>2</sup>C Hardware

- Antenna board (also called Evalboard)

- Only NTAG I<sup>2</sup>C connected to Antenna (Class 5)

- Can be connected to demo board or any I<sup>2</sup>C interface (e.g. I2C Bird)

- Demoboards:

- LPC812 Demoboard

- NTAG I<sup>2</sup>C Explorer Kit Rev 1 and 2

- Development board:

- Both demoboards have programming connectors

- Source code of demos available

- For μC

- For Android

# NTAG I<sup>2</sup>C Chip and Eval Board Generations

- V0B / Wave#1

- UID "04 xx yy 13 00 00 00"

- V0C / Wave#2

- UID "04 xx yy 14 00 00 00"

- V0D / Wave#3

- UID "04 xx yy 08 00 00 00"

- UID "04 xx yy 10 00 00 00"

- UID "04 xx yy 30 00 00 00"

- V0E / Wave#4

- UID "04 xx yy 18 00 00 00"

- UID "04 xx yy 20 00 00 00"

- UID "04 xx yy 28 00 00 00"

- V0F / Wave#5

- UID "04 xx yy 3A 7C 3B 80"

# NTAG I<sup>2</sup>C Android Demo Application

- Available in Google Playstore

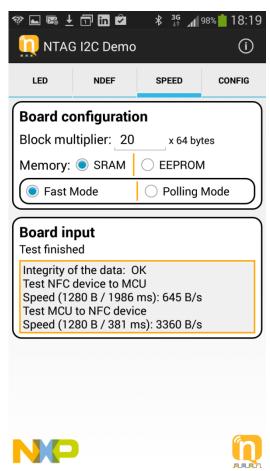

- Shows:

- Passhtrough Communication in both directions:

- Set LED colour (interactive)

- Read Buttons pressed and demoboard temperature

- NDEF read/write

- Depends on demoboard: show message content on LCD

- Communication speed

- Passthrough and EEPROM

- NTAG I<sup>2</sup>C Configuration:

- Memory Readout

- Configuration Read/Write

- Register Read

- Old version on Playstore to be replaced ~ next week

- Source Code: <a href="https://nxp.box.com/NTAGI2CDemoboardLPC812">https://nxp.box.com/NTAGI2CDemoboardLPC812</a>

Google play

NTAG I2C Demoboard

# NTAG I<sup>2</sup>C Android Demo Application Screen: LEDDemo

- Select a LED colour which should light up on demoboard

- Reads back (if on demoboard):

- Temperature

- Energy Harvesting Voltage

- Communication is done in Passthrough Mode

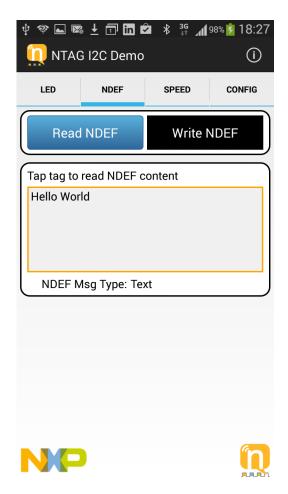

# NTAG I<sup>2</sup>C Android Demo Application Screen: NDEF

- Allows to read NDEF-Messages from type text

- Write NDEF messages from type:

- Text

- URI

- Bluetooth Pairing Information

- In case the demoboard has a display:

- The LCD displays the written text

# NTAG I<sup>2</sup>C Android Demo Application Screen: Speed

- Measures data troughput in the following modes:

- SRAM fast: Data transfer Phone<->MCU without register polling (MCU timing needs to be known)

- SRAM polling: Data transfer Phone<->MCU with register polling. Slower, but works independent of MCU timing

- EEPROM: Read/Write to NTAG I<sup>2</sup>C EEPROM, MCU not involved (demo case: zero power configuration)

# NTAG I<sup>2</sup>C Android Demo Application Screen: Config

- Allows to:

- Dump Memory Content

- Reset complete tag memory (if not locked)

- Read Session Registers

- Read/Write Configuration

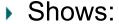

#### NTAG I<sup>2</sup>C LPC812 Demoboar

To be connected to a NTAG I<sup>2</sup>C Antennaboa

Programming Microcontroller Connector to e.g. LPC812 LPCXpresso board Connector to e.g. LPC812 (optional)

**LEDs**

**Temperature**

**Push buttons**

- Shows:

- Energy Harvesting

- LED Demo with interactive LED control and Button + Temp feedback

- Zero-Power Configuration (switch LED on depending on NDEF)

- SRAM and EEPROM speed measurement

- Code for LPC and Android downloadable: <a href="https://nxp.box.com/NTAGI2CDemoboardLPC812">https://nxp.box.com/NTAGI2CDemoboardLPC812</a>

- Will be put on public Internet at release

- Availability: on eDemoboard ~CW36

# NTAG I<sup>2</sup>C Explorer Board

#### Components:

- LPC11U24

- RGB-LED

- Buttons

- Temp-Sensor

- LCD

- micro-USB

- Energy Harvesting

- LED Demo with interactive LED control and Button + Temp feedback

- Zero-Power Configuration (switch LED on depending on NDEF)

- SRAM and EEPROM speed measurement

- NDEF message read write with NDEF content display on LCD

- I<sup>2</sup>C memory read/write with a windows GUI (I<sup>2</sup>C-USB-Bridge)

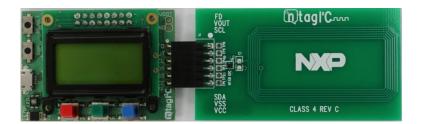

# NTAG I<sup>2</sup>C Communciation with NTAG I<sup>2</sup>C Explorer PC GUI

- LPC μC used as bridge USB<->I<sup>2</sup>C

- Needed

Firmware

integrated in

NTAG I<sup>2</sup>C

Explorer Kit

# NTAG I<sup>2</sup>C Application Notes

- How to lock the tag to readonly

- How to optimize Energy Harvesting

- How to use the Passthrough Mode

- Manual for the Android Demo Application

- Porting guide for general NTAG\_UCODE-API

# Software Issues

#### **Known Software Issues with NFC Devices**

#### Memory Initialization:

To improve NFC Device compatibility the Memory is initialized without Lock Control TLV. Effect: Locking a tag with automatic lock functions defined by NFC Forum only locks a part of the tag.

Details: AN11456: Using the dynamic lock bits to lock the tag

#### Sector Select:

Automatic read of NDEF messages which are larger as ~1 kByte does not work on all NFC devices in the market. It is recommended to use the corresponding NDEF message read functions in the MIFARE SDK

#### Sector Select Timeout:

When sending the sector select command with NFC devices it is necessary to reduce the timeout as the second part of the command has no answer. Otherwise the command execution gets very slow. On some NFC devices this timeout cannot be changed and a sector select can take up to 5 seconds time

# Thank you!