# Intel<sup>®</sup> Quartus<sup>®</sup> Prime Pro Edition User Guide

# **Power Analysis and Optimization**

Updated for Intel® Quartus® Prime Design Suite: 21.4

Version: 2022.06.22

ID: 683174

# **Contents**

| 1. P | ower Analysis                                               | 4  |

|------|-------------------------------------------------------------|----|

|      | 1.1. Power Analysis Tools                                   | 5  |

|      | 1.2. Running the Power Analyzer                             |    |

|      | 1.3. Specifying Power Analyzer Input                        | 8  |

|      | 1.3.1. Settings for Power Analysis                          | 8  |

|      | 1.3.2. Specifying Signal Activity Data                      | 10 |

|      | 1.3.3. Specifying the Default Toggle Rate                   | 17 |

|      | 1.3.4. Specifying Toggle Rates for Specific Nodes           | 17 |

|      | 1.3.5. Avoiding Simulation Node Name Match                  | 18 |

|      | 1.4. Viewing Power Analysis Reports                         |    |

|      | 1.5. Power Analysis in Modular Design Flows                 |    |

|      | 1.5.1. Complete Design Simulation Power Analysis Flow       | 24 |

|      | 1.5.2. Modular Design Simulation Power Analysis Flow        |    |

|      | 1.5.3. Multiple Simulation Power Analysis Flow              |    |

|      | 1.5.4. Overlapping Simulation Power Analysis Flow           |    |

|      | 1.5.5. Partial Design Simulation Power Analysis Flow        |    |

|      | 1.5.6. Vectorless Estimation Power Analysis Flow            |    |

|      | 1.6. Scripting Support                                      |    |

|      | 1.6.1. Running the Power Analyzer from the Command-Line     |    |

|      | 1.7. Power Analysis Revision History                        | 28 |

| 2. P | ower Optimization                                           | 32 |

|      | 2.1. Factors Affecting Power Consumption                    |    |

|      | 2.1.1. Design Activity and Power Analysis                   |    |

|      | 2.1.2. Device Selection                                     |    |

|      | 2.1.3. Environmental Conditions                             |    |

|      | 2.1.4. Device Resource Usage                                |    |

|      | 2.1.5. Signal Activity                                      |    |

|      | 2.2. Design Space Explorer II for Power-Driven Optimization | 35 |

|      | 2.3. Power-Driven Compilation                               | 35 |

|      | 2.3.1. Power-Driven Synthesis                               | 35 |

|      | 2.3.2. Power-Driven Fitter                                  | 38 |

|      | 2.3.3. Area-Driven Synthesis                                | 38 |

|      | 2.3.4. Gate-Level Register Retiming                         | 39 |

|      | 2.3.5. Intel Quartus Prime Compiler Settings                | 39 |

|      | 2.3.6. Assignment Editor Options                            |    |

|      | 2.4. Design Guidelines                                      | 41 |

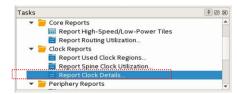

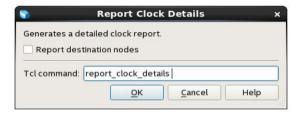

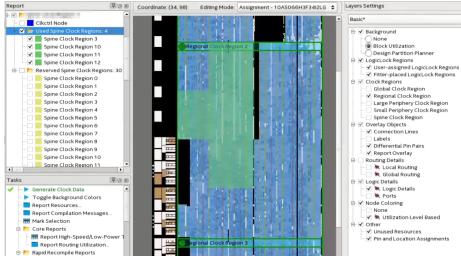

|      | 2.4.1. Clock Power Management                               | 41 |

|      | 2.4.2. Pipelining and Retiming                              | 46 |

|      | 2.4.3. Architectural Optimization                           |    |

|      | 2.4.4. I/O Power Guidelines                                 |    |

|      | 2.4.5. Dynamically Controlled On-Chip Terminations (OCT)    |    |

|      | 2.4.6. Memory Optimization (M20K/MLAB)                      |    |

|      | 2.4.7. DDR Memory Controller Settings                       |    |

|      | 2.4.8. DSP Implementation                                   |    |

|      | 2.4.9. Reducing High-Speed Tile (HST) Usage                 |    |

|      | 2.4.10. Unused Transceiver Channels                         | 53 |

#### Contents

| 3. Power Analysis and Optimization Document Archive | 60 |

|-----------------------------------------------------|----|

| 2.6. Power Optimization Revision History            | 58 |

| 2.5.9. Pipeline Logic to Reduce Glitching           | 57 |

| 2.5.8. Clock Enables on Logic                       |    |

| 2.5.7. Shut Down RAM Blocks                         |    |

| 2.5.6. Use RAM Blocks                               |    |

| 2.5.5. Appropriate I/O Standards                    |    |

| 2.5.4. Static Power                                 | 56 |

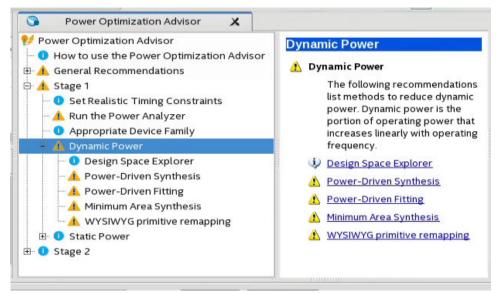

| 2.5.3. Dynamic Power                                | 55 |

| 2.5.2. Appropriate Device Family                    |    |

| 2.5.1. Set Realistic Timing Constraints             | 54 |

| 2.5. Power Optimization Advisor                     |    |

| 2.4.11. Periphery Power reduction XCVR Settings     | 53 |

# 1. Power Analysis

Power consumption is a critical design consideration. When designing a PCB, you must determine the power consumption of the FPGA device to develop an accurate power budget, and to design the power supplies, voltage regulators, heat sink, and cooling system.

The Intel® Quartus® Prime Design Suite provides the Early Power Estimator (EPE) spreadsheet for Intel Arria® 10 devices, and the Intel FPGA Power and Thermal Calculator for Intel Stratix® 10 and Intel Agilex $^{\text{\tiny M}}$  devices.

The Power Analyzer helps you to estimate the power consumption of your compiled design, for these three device families.

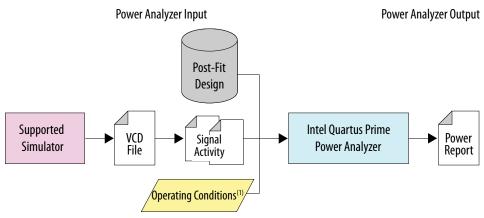

Figure 1. Power Analyzer Tool

Power estimation and analysis allows you to confirm that your design does not exceed thermal or power supply requirements throughout the design process:

- **Thermal**—Thermal power is the power that dissipates as heat from the FPGA. Devices use a heatsink or fan to act as a cooling solution. This cooling solution must be sufficient to dissipate the heat that the device generates. Additionally, the computed junction temperature must fall within normal device specifications.

- **Power supply**—Power supply is the power that the device needs to operate. Power supplies must provide adequate current to support device operation.

Note:

Do not use the results of the Power Analyzer as design specifications. You must also verify the actual power during device operation to account for actual environmental operating conditions.

#### **Related Information**

- Intel FPGA Power and Thermal Calculator (PTC) User Guide

- Power Analyzer Support Resources

# 1.1. Power Analysis Tools

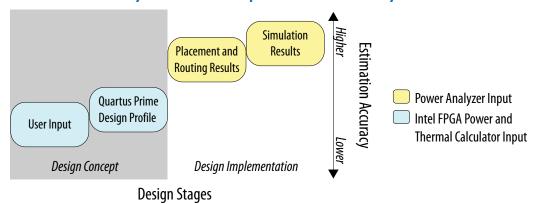

The Intel Quartus Prime Design Suite provides tools to analyze the power consumption of your FPGA design at different stages of the design process.

- Intel FPGA Power and Thermal Calculator (PTC)—estimates power supply and system thermal requirements before compiling the design, or anytime during the design phase. Supports Intel Stratix 10 and Intel Agilex devices.

- Intel Quartus Prime Power Analyzer (QPA)—estimates power consumption for a post-fit design, allowing you establish guidelines for the power budget.

- Early Power Estimator (EPE) spreadsheet—estimates power consumption for power supply planning before compiling the design. Supports Intel Arria 10 and Intel Stratix 10 devices. (For versions of the Intel Quartus Prime software later than version 19.4, Intel Stratix 10 devices are supported in the Intel FPGA Power and Thermal Calculator.)

Figure 2. Estimation Accuracy for Different Inputs and Power Analysis Tools

The accuracy of the power model is determined on a per-power-rail basis for the Intel Quartus Prime Power Analyzer.

- For most Intel Stratix 10 designs, the Intel Quartus Prime Power Analyzer has the following accuracy, assuming final power models: Within 10% of silicon for the majority of power rails with higher power, assuming accurate inputs and toggle rates.

- For most Intel Agilex designs, the Intel Quartus Prime Power Analyzer has the following accuracy, assuming final power models: Within 10% of silicon for all power rails, assuming accurate inputs and toggle rates.

Table 1. Comparison of EPE/Intel FPGA PTC and Intel Quartus Prime Power Analyzer Capabilities

| Characteristic                                                                | EPE / PTC                                                                                                                                                                                         | Intel Quartus Prime Power Analyzer                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When to use                                                                   | Any time  Note: For post-fit power analysis, you get better results with the Intel Quartus Prime Power Analyzer.                                                                                  | Post-fit                                                                                                                                                                                                                                                        |

| Software requirements                                                         | EPE: Spreadsheet program.  Intel FPGA PTC: Integrated into the Intel Quartus Prime software, and is also available as a standalone tool.                                                          | The Intel Quartus Prime software                                                                                                                                                                                                                                |

| Accuracy                                                                      | Medium                                                                                                                                                                                            | Medium to very high                                                                                                                                                                                                                                             |

| Data inputs                                                                   | <ul> <li>Resource usage estimates</li> <li>Clock requirements</li> <li>Environmental conditions</li> <li>Toggle rate</li> </ul>                                                                   | Post-fit design     Clock requirements     Signal activity defaults     Environmental conditions     Register transfer level (RTL) simulation results (optional)     Post-fit simulation results (optional)     Signal activities per node or entity (optional) |

| Data outputs  Note: The EPE and Power Analyzer outputs vary by device family. | <ul> <li>Total thermal power dissipation</li> <li>Thermal static power</li> <li>Thermal dynamic power</li> <li>Off-chip power dissipation</li> <li>Current drawn from voltage supplies</li> </ul> | Total thermal power Thermal static power Thermal dynamic power Thermal I/O power Thermal power by design hierarchy Thermal power by block type Thermal power dissipation by clock domain Device supply currents                                                 |

| Estimation of transceiver power for dynamic reconfiguration features          | Includes an estimation of the incremental power consumption by these features.                                                                                                                    | Not included                                                                                                                                                                                                                                                    |

683174 | 2022.06.22

Note:

The Intel Quartus Prime Power Analyzer does not support power analysis of the following Intel FPGA IP:

- Intel Stratix 10 HBM2 IP

- Intel Stratix 10 HPS IP

- Intel Arria 10 HPS IP

In versions of the Intel Quartus Prime software later than 19.4, you can obtain power estimations for the Intel Stratix 10 HBM2 IP and Intel Stratix 10 HPS IP using the Intel FPGA Power and Thermal Calculator (PTC).

For power estimation of Intel Arria 10 HPS IP, and for power estimation in the Intel Quartus Prime software version 19.4 or earlier, you can can obtain power estimations using the Early Power Estimator spreadsheet (EPE).

# 1.2. Running the Power Analyzer

Before running the Power Analyzer you must run full compilation of your design to generate the post-fit netlist. In addition, you must either provide timing assignments for all clocks in the design, or specify signal activity data for power analysis. You must specify the I/O standard on each device input and output, and the board trace model on each output in the design.

To run the Power Analyzer:

- To specify device power characteristics, operating voltage, and temperature conditions for power analysis, click Assignments ➤ Settings ➤ Operating Settings and Conditions, as Settings for Power Analysis on page 8 describes.

- 2. To run full compilation of your design, click **Processing** ➤ **Start Compilation**.

- 3. Click Assignments ➤ Settings ➤ Power Analyzer.

- 4. Specify the source of signal activity data, as Generating Signal Activity Data for Power Analysis on page 12 describes.

- 5. To generate a Signal Activity (.saf) file during analysis, turn on **Write out signal** activities used during power analysis, and specify the file name.

- To direct the Power Analyzer to generate an Early Power Estimation file, turn on

Write out Early Power Estimation file, and specify the file name. The Early

Power Estimation file summarizes the resource utilization and allows you to

perform what-if analyses in EPE.

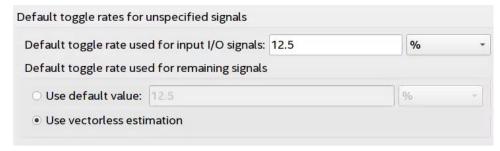

- 7. Specify the **Default toggle rates for unspecified signals**, as Specifying the Default Toggle Rate on page 17 describes.

- 8. To specify temperature range and cooling options, click **Cooling Solution and Temperature**.

- To run full compilation of your design, click Processing ➤ Start ➤ Start Power Analyzer.

- 10. When power analysis is complete, click **Report** to open the Power Analyzer reports that Viewing Power Analysis Reports on page 18 describes.

#### **Related Information**

Specifying Power Analyzer Input on page 8

# 1.3. Specifying Power Analyzer Input

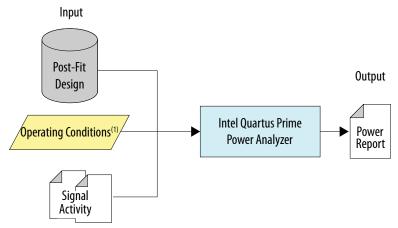

The Power Analyzer accuracy is driven by design factors, operating conditions, and signal activity data that affect power consumption. The following figure shows how the Power Analyzer interprets these inputs and generates results in the Power Analysis report:

Figure 3. Power Analyzer High-Level Flow

(1)Operating condition specifications are available for only some device families

To obtain accurate I/O power estimates, the Power Analyzer requires full compilation of your design, in addition to specifying the following settings:

- The electrical standard on each I/O cell.

- The board trace model on each I/O standard in the design.

- Timing assignments for all the clocks in your design, or use a simulation-based flow to generate activity data.

Note:

For accurate results, ensure that any  $\mbox{.}\mbox{VCD}$  file used with the Power Analyzer is the result of gate-level simulation.

#### 1.3.1. Settings for Power Analysis

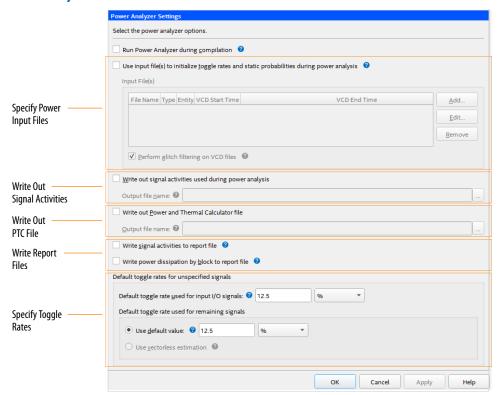

You can specify device power characteristics, operating voltage conditions, operating temperature conditions, Power Analyzer settings and thermal settings, in the **Operating Settings and Conditions**, **Power Analyzer Settings**, and **Thermal** pages of the **Settings** dialog box.

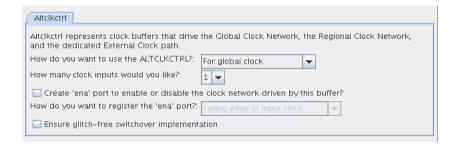

#### Figure 4. Operating Settings and Conditions

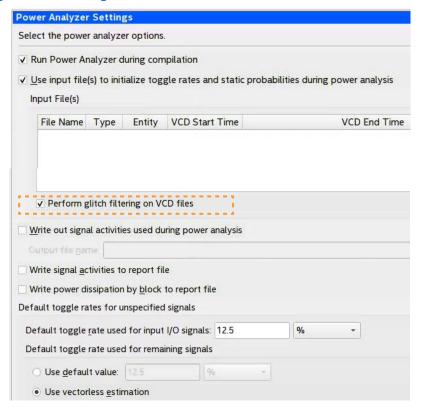

#### Figure 5. Power Analyzer and Thermal Settings

The Power Analyzer reads the following settings to determine the operating conditions for power analysis:

#### **Table 2.** Device Operating Condition Settings

| Option                       | Settings                                                                                                                                                                                 |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device power characteristics | <ul> <li>Typical—specifies average power consumed by typical silicon at nominal operating conditions.</li> <li>Maximum—specifies maximum power consumed by worst-case device.</li> </ul> |  |

| Voltage tab                  | Specifies the operating voltage conditions for each power rail in the device, and the supply voltages for power rails with selectable supply voltages.                                   |  |

| Temperature tab              | Specifies the minimum and maximum junction temperature range.                                                                                                                            |  |

#### **Table 3. Power Analyzer and Thermal Settings**

| Option                                                                                                                                           | Settings                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Analyzer Settings  Specifies the Power Analyzer options, including:  Run Power Analyzer during compilation—Check this box to turn on power |                                                                                                                                                                                                                                |

|                                                                                                                                                  | during compilation.                                                                                                                                                                                                            |

|                                                                                                                                                  | Use input file(s) to initialize toggle rates and static probabilities during power analysis—Check this box to use Signal Activity Files or VCD files to initialize toggle rates and static probabilities for power estimation. |

|                                                                                                                                                  | Write out signal activities used during power analysis—Check this box to write<br>the toggle rates and static probabilities used during power estimation to a file.                                                            |

|                                                                                                                                                  | continued                                                                                                                                                                                                                      |

| Option           | Settings                                                                                                                                                                                                                                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Write out Power and Thermal Calculator file—Check this box to have the Power<br>Analyzer export a design summary that you can import into the Intel FPGA Power and<br>Thermal Calculator.                                                                                                                         |

|                  | Write signal activities to report file—Check this box to have the Power Analyzer write a report file containing the signal activities used during power analysis.                                                                                                                                                 |

|                  | <ul> <li>Write power dissipation by block to report file—Check this box to have the Power<br/>Analyzer report the thermal power dissipation calculated during power analysis, in the<br/>Thermal Power Dissipation by Block report panel.</li> </ul>                                                              |

|                  | Default toggle rate used for input I/O signals—Specify a default toggle rate for use on input I/O pins during power estimation. Can be expressed as a percentage or in transitions/second.                                                                                                                        |

|                  | Default toggle rate used for remaining signals                                                                                                                                                                                                                                                                    |

|                  | <ul> <li>Use default value—Specify a default toggle rate for use during power estimation on all nodes except I/O pins. This value is used only if no toggle rate is specified through a Signal Activity File, VCD file, or user assignment. Can be expressed as a percentage or in transitions/second.</li> </ul> |

|                  | <ul> <li>Use vectorless estimation—Turn on this control to use vectorless estimation to fill in undefined toggle rates and static probabilities. If this option is not available, the device family does not support vectorless estimation.</li> </ul>                                                            |

| Thermal Settings | Specifies the thermal power analysis temperature conditions, including:                                                                                                                                                                                                                                           |

| _                | Thermal Solver Mode—Select the thermal solver mode to use during power estimation.                                                                                                                                                                                                                                |

|                  | Junction temperature—Specifies the junction temperature, in °C, used during power estimation.                                                                                                                                                                                                                     |

|                  | Ambient temperature—Specifies the ambient temperature, in °C, used during power estimation.                                                                                                                                                                                                                       |

|                  | • Cooling solution—Specifies the cooling solution case-to-ambient thermal resistance, in °C per watt.                                                                                                                                                                                                             |

|                  | Maximum junction temperature limit—Specifies the maximum junction temperature limit that no part of any die in the package should exceed.                                                                                                                                                                         |

|                  | • <b>Apply additional margin</b> —Specifies, as a percentage, the amount of additional margin to apply to detailed thermal analysis results. Valid values are 0–25%. The default value is 0%. The recommended margin for Intel Agilex devices is 10%, and for Intel Stratix 10 devices, 25%.                      |

|                  | Note: For a design compiled in an earlier version of the Intel Quartus Prime software with the <b>Apply Recommended Margin</b> parameter set to Yes, the current version of Power Analyzer interprets this as an <b>Apply Additional Margin</b> setting of 25%.                                                   |

|                  | • <b>Temperature measurement method</b> —Select the method to use for reporting temperature sensors for thermal analysis.                                                                                                                                                                                         |

# 1.3.2. Specifying Signal Activity Data

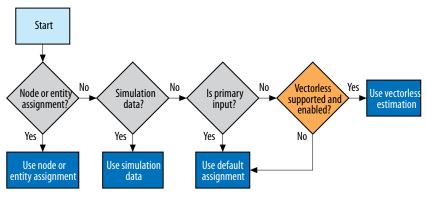

The accuracy of the power estimation depends on how representative signal activity data is during power analysis. The Power Analyzer allows you to specify signal activity data from the following sources:

- .vcd files generated by simulation of the gate-level design netlist, by supported third-party simulators

- User-entered node, entity, and clock assignments

- User-entered default toggle rate assignment

- Vectorless estimation (selected devices)

You can mix and match the signal activity data sources on a signal-by-signal basis. The following figure shows the priority scheme applied to each signal.

Figure 6. Signal Activity Data Source Priority Scheme

#### 1.3.2.1. Using Simulation Signal Activity Data in Power Analysis

You can specify a Verilog Value Change Dump File (.vcd) generated by simulating a placed and routed gate-level netlist in a supported $^{(1)}$  simulator as the source of signal activity data for power analysis.

Third-party simulators can output a .vcd that contains signal activity and static probability information that inform the power analysis. The generated .vcd includes all of the routing resources and the exact logic array resource usage.

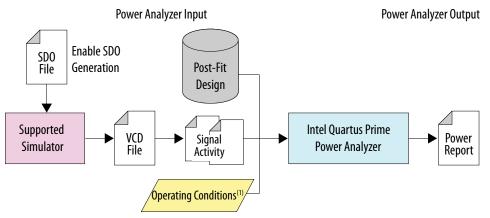

Figure 7. Using Simulation Signal Activity Data in Power Analysis

To improve accuracy of power analysis, you can generate a Standard Delay Output (.sdo) file that includes back-annotated delay estimates of the instances of core atoms for ModelSim simulation. ModelSim simulation can then output a more accurate .vcd for use as power analysis input. You must run the **Fitter (Finalize)** command before generating the .sdo. **Note:** To improve accuracy of power analysis, the Intel Quartus Prime EDA Netlist writer can generate a Standard Delay Output (.sdo) file that includes back-annotation of delays for a design's netlist for use during

<sup>(1)</sup> ModelSim\*, ModelSim - Intel FPGA Edition, QuestaSim, Active-HDL, NCSim, VCS\*, VCS MX, Riviera-PRO\*

simulation in ModelSim. Although the .sdo only contains delay estimates and imprecise timing information, including the .sdo in simulation results in a more accurate output .vcd for power analysis.

Note:

The EDA Netlist Writer currently supports .sdo file generation only for Verilog .vo simulation in the ModelSim simulator (not ModelSim - Intel FPGA Edition) for Intel Stratix 10 designs. The EDA Netlist Writer does not currently support .sdo file generation for any other simulator or device family.

#### 1.3.2.1.1. Generating Signal Activity Data for Power Analysis

Follow these steps to generate and use simulation signal activity data for power analysis:

- 1. To run full compilation on your design, click **Processing ➤ Start Compilation**.

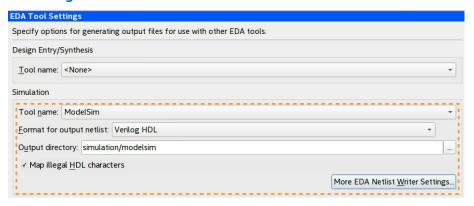

- To specify settings for output of simulation files, click Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulation. Select your simulator in Tool name and the Format for output netlist and Output directory.

- 3. Turn on **Map illegal HDL characters**. This setting directs the EDA Netlist Writer to map illegal characters for VHDL or Verilog HDL, and results in more accurate data for power analysis.

#### Figure 8. EDA Tool Settings for Simulation

- 4. For Intel Stratix 10 designs, to generate a Standard Delay Output (.sdo) file that includes back-annotation of delays for power analysis, refer to Generating Standard Delay Output for Power Analysis on page 13.

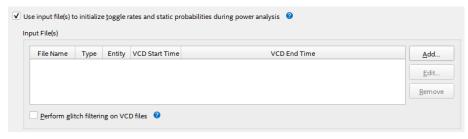

- In the Intel Quartus Prime software, click Assignments ➤ Settings ➤ Power Analyzer Settings.

- 6. Under Input file, turn on Use input files to initialize toggle rates and static probabilities during power analysis.

Figure 9. Specifying Power Analysis Input Files

- 7. To specify a .vcd for power analysis, click **Add** and specify the **File name**, **Entity**, and **Simulation period** for the .vcd, and click **OK**.

- 8. To enable glitch filtering during power analysis with the .vcd you generate, turn on **Perform glitch filtering on VCD files**.

- 9. To run the power analysis, click **Start** on the **Power Analysis** step in the Compilation Dashboard. View the toggle rates in the power analysis results.

#### 1.3.2.1.2. Generating Standard Delay Output for Power Analysis

To improve accuracy of power analysis, you can generate a Standard Delay Output (.sdo) file that includes back-annotated delay estimates for ModelSim simulation.

ModelSim simulation can then output a more accurate .vcd for use as power analysis input. You must run **Fitter (Finalize)** before generating the .sdo.

Figure 10. Using an SDO in Power Analysis

- 1. Click Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulation. In Tool name select ModelSim and Verilog for Format for output netlist.

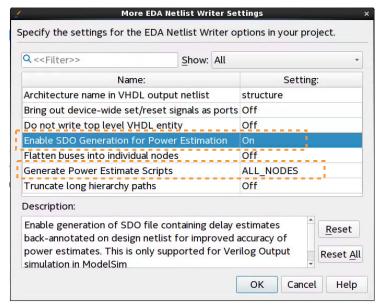

- 2. Click More EDA Netlist Writer Settings. Set Enable SDO Generation for Power Estimation to On. Set Generate Power Estimate Scripts to ALL\_NODES.

Figure 11. More EDA Netlist Writer Settings

- 3. To run the Fitter, click **Processing** ➤ **Start** ➤ **Start Fitter (Finalize)**.

- 4. Create a representative testbench (.vt) that exercises the design functions appropriately.

- 5. To specify the appropriate hierarchy level for signals in the output .vcd, add the following line to the project .qsf file:

- 6. After Fitter processing is complete, click Processing ➤ Start ➤ Start EDA Netlist Writer. EDA Netlist Writer generates the following files in /

/

simulation/modelsim/power/:

- project>.vo (contains a reference to the .sdo file by default)

- <project>\_dump\_all\_vcd\_nodes.tcl—specifies nodes to save in .vcd

- project>\_v.sdo—back-annotated delay estimates

- 7. Create a ModelSim script (.do) to load the design and testbench, start ModelSim, and then source the .do script.

- 8. To specify the signals ModelSim includes in the .vcd file, source \*\_dump\_all\_vcd\_nodes.tcl in ModelSim.

- 9. To generate the .vcd file, simulate the test bench and netlist in ModelSim. The .vcd file generates according to your specifications.

- 10. Specify the .vcd as an input to power analysis, as Generating Signal Activity Data for Power Analysis on page 12 describes.

<sup>(2)</sup> Specify the full hierarchical path in the testbench, not just the instance name. For example, specify a|b|c, not just c.

Note: The EDA Netlist Writer currently supports .sdo file generation only for Verilog .vo simulation in the ModelSim simulator (not ModelSim - Intel FPGA Edition) for Intel Stratix 10 designs. The EDA Netlist Writer does not currently support .sdo file generation for any other simulator or device family.

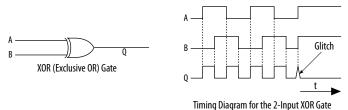

#### 1.3.2.1.3. Simulation Glitch Filtering

You can enable glitch filtering in the .vcd that you generate in a third-party simulator for use in power analysis by turning on the **Perform glitch filtering on VCD files** option.

Figure 12. Enabling Glitch Filtering for VCD

The Power Analyzer defines a glitch as two signal transitions so closely spaced in time that the pulse, or glitch, occurs faster than the logic and routing circuitry can respond. The output of a transport delay model simulator contains glitches for some signals. The logic and routing structures of the device form a low-pass filter that filters out glitches that are tens to hundreds of picoseconds long, depending on the device family.

Some third-party simulators use different models than the transport delay model as the default model. Different models cause differences in signal activity and power estimation. The inertial delay model, which is the ModelSim default model, filters out more glitches than the transport delay model and usually yields a lower power estimate.

Note:

Intel FPGA recommends that you use the transport simulation model when using the Intel Quartus Prime software glitch filtering support with third-party simulators. Simulation glitch filtering has little effect if you use the inertial simulation model.

Glitch filtering in a simulator can also filter a glitch on one logic element (LE) (or other circuit element) output from propagating to downstream circuit elements to ensure that the glitch does not affect simulated results. Glitch filtering prevents a glitch on one signal from producing non-physical glitches on all downstream logic, which can result in a signal toggle rate and a power estimate that are too high. Circuit elements in which every input transition produces an output transition, including multipliers and logic cells configured to implement XOR functions, are especially prone to glitches. Therefore, circuits with such functions can have power estimates that are too high when glitch filtering is not used.

Note:

Intel FPGA recommends that you use the glitch filtering feature to obtain the most accurate power estimates. For .vcd files, the Power Analyzer flows support two levels of glitch filtering.

The .vcd file reader performs glitch filtering that is complementary to simulation glitch filtering, but is often less precise. While the .vcd file reader has the ability to remove glitches on logic blocks, the file reader cannot determine how a given glitch potentially affects downstream logic and routing. Filtering the glitches during simulation avoids switching downstream routing and logic automatically.

Note:

When running simulation for design verification (rather than to produce input to the Power Analyzer), Intel recommends that you turn off the glitch filtering option to produce the most rigorous and conservative simulation from a functionality viewpoint. When performing simulation to produce input for the Power Analyzer, Intel FPGA recommends that you turn on the glitch filtering to produce the most accurate power estimates.

# 1.3.2.2. Signal Activities from RTL (Functional) Simulation, Supplemented by Vectorless Estimation

In the functional simulation flow, simulation provides toggle rates and static probabilities for all pins and registers in your design. Vectorless estimation fills in the values for all the combinational nodes between pins and registers, giving good results. This flow usually provides a compilation time benefit when you use the third-party RTL simulator.

#### 1.3.2.2.1. RTL Simulation Limitation

RTL simulation may not provide signal activities for all registers in the post-fitting netlist because synthesis loses some register names. For example, synthesis might automatically transform state machines and counters, thus changing the names of registers in those structures. As a result, a large number of nodes in the .vcd file may not match the nodes in your design netlist, which can result in the power analysis results being less accurate or of lower confidence.

# 1.3.2.3. Signal Activities from Vectorless Estimation and User-Supplied Input Pin Activities

The vectorless estimation flow provides a low level of accuracy, because vectorless estimation for registers is not entirely accurate.

#### 1.3.2.4. Signal Activities from User Defaults Only

The user defaults only flow provides the lowest degree of accuracy.

# 1.3.3. Specifying the Default Toggle Rate

You can specify the **Default toggle rates for unspecified signals** in your design for power analysis. The Power Analyzer uses the default toggle rate when no other method specifies the signal activity data.

#### Figure 13. Specifying the Default Toggle Rate

You specify the toggle rate in absolute terms (transitions per second), or as a fraction of the clock rate in effect for each node. The toggle rate for a clock derives from the timing settings for the clock. For example, if the Power Analyzer specifies a clock with an  $f_{MAX}$  constraint of 100 MHz and a default relative toggle rate of 20%, nodes in this clock domain transition in 20% of the clock periods, or 20 million transitions occur per second.

In some cases, the Power Analyzer cannot determine the clock domain for a node because the clock domain is ambiguous. For example, the Power Analyzer cannot determine a clock domain for a node unless you specify sufficient timing constraints for the clock domains. If the Power Analyzer cannot determine the clock domain for a node, the Power Analyzer substitutes and reports a toggle rate of zero.

Note:

The transceiver I/O toggle rate is determined by the XCVR data rate value specified in your IP catalog settings. Do not include transceiver I/O toggle rate in the default toggle rates that you specify in the Power Analyzer.

#### **Related Information**

Toggle Rate on page 34

## 1.3.4. Specifying Toggle Rates for Specific Nodes

You can assign toggle rates and static probabilities to individual nodes in the design. These assignments have the highest priority, overriding data from all other signal activity sources.

You must use the Assignment Editor or Tcl commands to create the **Power Toggle Rate** and **Power Static Probability** assignments. You can specify the power toggle rate as an absolute toggle rate in transitions per second using the **Power Toggle Rate** assignment, or you can use the **Power Toggle Rate Percentage** assignment to specify a toggle rate relative to the clock domain of the assigned node for a more specific assignment made in terms of hierarchy level.

Note:

If you use the **Power Toggle Rate Percentage** assignment, and the node does not have a clock domain, the Intel Quartus Prime software issues a warning and ignores the assignment.

Assigning toggle rates and static probabilities to individual nodes is appropriate for signals in which you have knowledge of the signal being analyzed. For example, if you know that a 100 MHz data bus or memory output produces data that is essentially random (uncorrelated in time), you can directly enter a 0.5 static probability and a toggle rate of 50 million transitions per second.

The Power Analyzer treats bidirectional I/O pins differently. The combinational input port and the output pad for a pin share the same name. However, those ports might not share the same signal activities. For reading signal activity assignments, the Power Analyzer creates a distinct name <node\_name~output> when configuring the bidirectional signal as an output and <node\_name~result> when configuring the signal as an input. For example, if a design has a bidirectional pin named MYPIN, assignments for the combinational input use the name MYPIN~result, and the assignments for the output pad use the name MYPIN~output.

Note:

When you create the logic assignment in the Assignment Editor, you cannot find the MYPIN~result and MYPIN~output node names in the Node Finder. Therefore, to create the logic assignment, you must manually enter the two differentiating node names to create the assignment for the input and output port of the bidirectional pin.

#### 1.3.4.1. Clock Node Toggle Rates

For clock nodes, the Power Analyzer uses timing requirements to derive the toggle rate when neither simulation data nor user-entered signal activity data is available.  $f_{MAX}$  requirements specify full cycles per second, but each cycle represents a rising transition and a falling transition. For example, a clock  $f_{MAX}$  requirement of 100 MHz corresponds to 200 million transitions per second for the clock node.

#### 1.3.5. Avoiding Simulation Node Name Match

Node name mismatches happen when you have .vcd applied to entities other than the top-level entity. In a modular design flow, the gate-level simulation files created in different Intel Quartus Prime projects might not match their node names with the current Intel Quartus Prime project.

For example, you may have a file named  $8b10b\_enc.vcd$ , which the Intel Quartus Prime software generates in a separate project called  $8b10b\_enc$  while simulating the 8b10b encoder. If you import the .vcd into another project called Top, you might encounter name mismatches when applying the .vcd to the  $8b10b\_enc$  module in the Top project. This mismatch happens because the Intel Quartus Prime software might name all the combinational nodes in the  $8b10b\_enc.vcd$  differently than in the Top project. To avoid such mismatches, Intel recommends using .vcd files generated from simulation of your top level project.

# 1.4. Viewing Power Analysis Reports

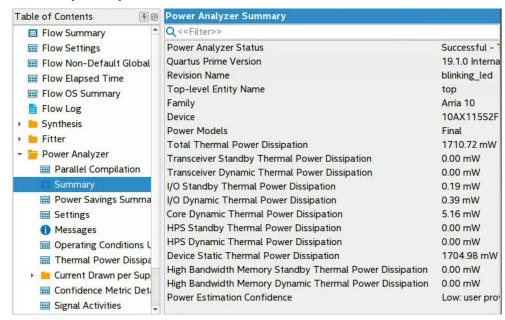

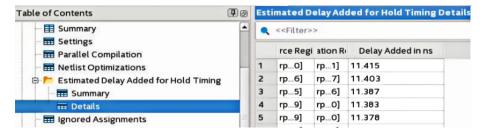

Following successful power analysis, click the **Power Analyzer** pulldown in the **Table of Contents** of the Compilation Report, to view the Power Analysis section of the report.

Figure 14. Power Analysis Reports

The Power Analysis reports contains the following sections:

#### **Summary**

The Summary section of the report shows the estimated total thermal power consumption of your design. This includes dynamic, static, and I/O thermal power consumption. The I/O thermal power includes the total I/O power drawn from the  $V_{CCIO}$  and  $V_{CCPD}$  power supplies and the power drawn from  $V_{CCINT}$  in the I/O subsystem including I/O buffers and I/O registers. The report also includes a confidence metric that reflects the overall quality of the data sources for the signal activities. For example, a Low power estimation confidence value reflects that you have provided insufficient toggle rate data, or most of the signal activity information used for power estimation is from default or vectorless estimation settings. For more information about the input data, refer to the Power Analyzer Confidence Metric report.

#### **Power Savings Summary**

Lists any savings (in mW) and the type of savings method, such as SmartVID Power Savings.

#### **Parallel Compilation**

When you enable parallel compilation, the Parallel Compilation report list the number of processors you use during Power Analysis

#### **Settings**

The Settings section of the report shows the Power Analyzer settings information of your design, including the default input toggle rates, operating conditions, and other relevant setting information.

#### **Simulation Files Read**

The Simulation Files Read section of the report lists the simulation output file that the .vcd used for power estimation. This section also includes the file ID, file type, entity, VCD start time, VCD end time, the unknown percentage, and the toggle percentage. The unknown percentage indicates the portion of the design module unused by the simulation vectors.

#### **Operating Conditions Used**

The Operating Conditions Used section of the report shows device characteristics, voltages, temperature, and cooling solution, if any, during the power estimation. This section also shows the entered junction temperature or auto-computed junction temperature during the power analysis.

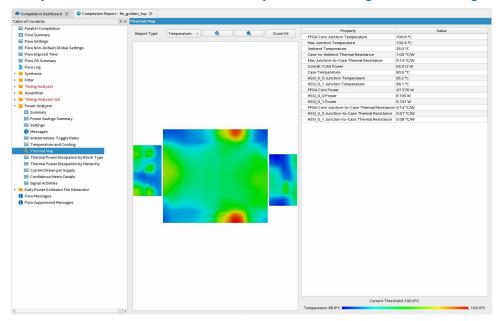

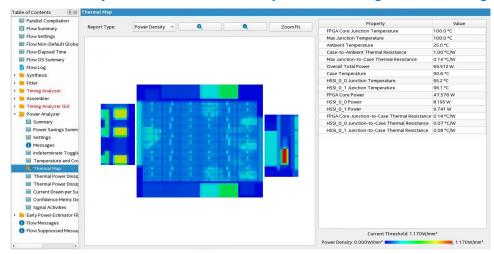

#### **Thermal Map Visualization**

For Intel Agilex FPGA designs, the Power Analyzer provides a visualization of the expected thermal distribution on the core die and the transceiver dies. This data is available when you run the Power Analyzer on your compiled Intel Agilex FPGA design. After you run the Power Analyzer, select the **Thermal Map** section in the Power Analyzer report. You can set the threshold temperature you want to use, which is useful if you are making any what-if analyses based on your thermal design. You can adjust the threshold temperature in increments of 5°C, between the ambient temperature (or 50°C, whichever is lower), and an upper limit of 100°C.

Figure 15. Temperature View of the Thermal Map for an Intel Agilex FPGA Design

Knowing the locations of hot spots in your design can help you make modifications as necessary for proper operation of the system.

The thermal map report can show two different views—a temperature view and a power density view. You can choose the view from a pulldown selection in the GUI, when you open the thermal map in the Power Analyzer.

Figure 16. Power Density View of the Thermal Map for an Intel Agilex FPGA Design

#### **Thermal Power Dissipated by Block**

The Thermal Power Dissipated by Block section of the report shows estimated thermal dynamic power and thermal static power consumption categorized by atoms. This information provides you with estimated power consumption for each atom in your design.

By default, this section does not contain any data, but you can turn on the report with the **Write power dissipation by block to report file** option on the **Power Analyzer Settings** page.

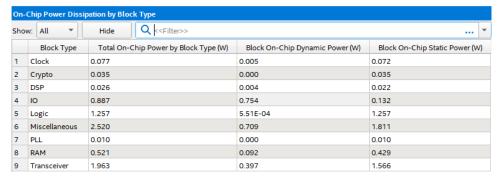

#### **On-Chip Power Dissipation by Block Type**

The On-Chip Power Dissipation by Block Type section of the report shows the estimated total on-chip power consumption by block type, and estimated on-chip dynamic power and estimated on-chip static power, by block type.

Figure 17. On-Chip Power Dissipation by Block Type

#### **On-Chip Power Dissipation by Hierarchy**

This On-Chip Power Dissipation by Hierarchy section of the report shows estimated total on-chip power consumption by hierarchy node, and both the cumulative and current-hierarchy-level dynamic, static, and routing power consumptions. This information is useful when locating modules with high power consumption in your design. (Available for Intel Agilex devices.)

#### **Core Dynamic Thermal Power Dissipation by Clock Domain**

The Core Dynamic Thermal Power Dissipation by Clock Domain section of the report shows the estimated total core dynamic power dissipation by each clock domain, which provides designs with estimated power consumption for each clock domain in the design. If the clock frequency for a domain is unspecified by a constraint, the clock frequency is listed as "unspecified." For all the combinational logic, the clock domain is listed as no clock with zero MHz.

#### **Current Drawn per Supply**

The Current Drawn per Supply section of the report lists the current drawn from each voltage supply. The  $V_{\text{CCIO}}$  and  $V_{\text{CCPD}}$  voltage supplies are further categorized by I/O bank and by voltage. This section also lists the minimum safe power supply size (current supply ability) for each supply voltage. Minimum current requirement can be higher than user mode current requirement in cases in which the supply has a specific power up current requirement that goes beyond user mode requirement.

The I/O thermal power dissipation on the summary page does not correlate directly to the power drawn from the  $V_{CCIO}$  and  $V_{CCPD}$  voltage supplies listed in this report. This is because the I/O thermal power dissipation value also includes portions of the  $V_{CCINT}$  power, such as the I/O element (IOE) registers, which are modeled as I/O power, but do not draw from the  $V_{CCIO}$  and  $V_{CCPD}$  supplies.

The reported current drawn from the I/O Voltage Supplies (ICCIO and ICCPD) as reported in the Power Analyzer report includes any current drawn through the I/O into off-chip termination resistors. This can result in ICCIO and ICCPD values that are higher than the reported I/O thermal power, because this off-chip current dissipates as heat elsewhere and does not factor in the calculation of device temperature. Therefore, total I/O thermal power does not equal the sum of current drawn from each  $V_{\rm CCIO}$  and  $V_{\rm CCPD}$  supply multiplied by  $V_{\rm CCIO}$  and  $V_{\rm CCPD}$  voltage.

For SoC devices, there is no standalone ICC\_AUX\_SHARED current drawn information. The ICC\_AUX\_SHARED is reported together with ICC\_AUX.

#### **Confidence Metric Details**

The Confidence Metric is defined in terms of the total weight of signal activity data sources for both combinational and registered signals. Each signal has two data sources allocated to it; a toggle rate source and a static probability source.

The Confidence Metric Details section also indicates the quality of the signal toggle rate data to compute a power estimate. The confidence metric is low if the signal toggle rate data comes from poor predictors of real signal toggle rates in the device during an operation. Toggle rate data that comes from simulation, user-entered assignments on specific signals or entities are reliable. Toggle rate data from default toggle rates (for example, 12.5% of the clock period) or vectorless estimation are relatively inaccurate. This section gives an overall confidence rating in the toggle rate data, from low to high. This section also summarizes how many pins, registers, and

combinational nodes obtained their toggle rates from each of simulation, user entry, vectorless estimation, or default toggle rate estimations. This detailed information helps you understand how to increase the confidence metric, letting you determine your own confidence in the toggle rate data.

#### **Signal Activities**

The Signal Activities section lists toggle rates and static probabilities assumed by power analysis for all signals with fan-out and pins. This section also lists the signal type (pin, registered, or combinational) and the data source for the toggle rate and static probability. By default, this section does not contain any data, but you can turn on the report with the **Write signal activities to report file** option on the **Power Analyzer Settings** page.

Intel recommends that you keep the **Write signal activities to report file** option turned off for a large design because of the large number of signals present. You can use the Assignment Editor to specify that activities for individual nodes or entities are reported by assigning an on value to those nodes for the **Power Report Signal Activities** assignment.

#### Messages

The Messages section lists the messages that the Intel Quartus Prime software generates during the analysis.

# 1.5. Power Analysis in Modular Design Flows

In modular or hierarchical design flows you develop each design block separately, and then instantiate these blocks into a higher-level design to form a complete design. The Intel Quartus Prime software supports simulation and power analysis of the top-level design or individual blocks with the design.

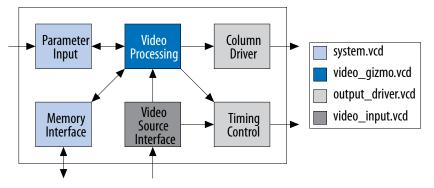

Figure 18. Modular Simulation Flow

You can associate multiple .vcd simulation output files with specific node names, enabling the integration of partial design simulations into a complete design power analysis. When specifying multiple .vcd files for a node, more than one simulation file can contain signal activity information for the same signal. In those cases, the Power Analyzer follows these rules:

- When you apply multiple .vcd files to the same design node, the Power Analyzer calculates the signal activity as the equal-weight arithmetic average of each .vcd.

- When you apply multiple simulation files to design nodes at different levels in the design hierarchy, the signal activity in the power analysis derives from the simulation file that applies to the most specific design node.

The following figure shows an example of a hierarchical design:

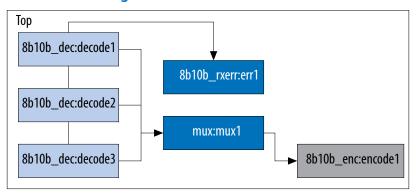

Figure 19. Example Hierarchical Design

The top-level module of the design, called  $\mathtt{Top}$ , consists of three 8b/10b decoders, followed by a  $\mathtt{mux}$ . The software encodes the output of the  $\mathtt{mux}$  to produce the final output of the top-level module. An error-handling module handles any 8b/10b decoding errors. The Top module contains the top-level entity of the design and any logic not defined as part of another module. The design file for the top-level module can be a wrapper for the hierarchical entities or can contain its own logic.

The following usage scenarios show common ways that you can simulate the design and import the .vcd into the Power Analyzer:

#### 1.5.1. Complete Design Simulation Power Analysis Flow

You can simulate the entire gate-level design and generate a .vcd from a third-party simulator. The Power Analyzer can then import the .vcd (specifying the top-level design). The resulting power analysis uses the signal activities information from the generated .vcd, including those that apply to submodules, such as decode [1-3], err1, mux1, and encode1.

#### 1.5.2. Modular Design Simulation Power Analysis Flow

You can independently simulate the top-level design, and then import all the resulting .vcd files into the Power Analyzer. For example, you can simulate the  $8b10b\_dec$  independent of the entire design and mux,  $8b10b\_rxerr$ , and  $8b10b\_enc$ . You can then import the .vcd files generated from each simulation by

specifying the appropriate instance name. For example, if the files produced by the simulations are 8b10b\_dec.vcd, 8b10b\_enc.vcd, 8b10b\_rxerr.vcd, and mux.vcd, you can use the import specifications in the following table:

**Table 4. Import Specifications**

| File Name       | Entity                |

|-----------------|-----------------------|

| 8b10b_dec.vcd   | Top 8b10b_dec:decode1 |

| 8b10b_dec.vcd   | Top 8b10b_dec:decode2 |

| 8b10b_dec.vcd   | Top 8b10b_dec:decode3 |

| 8b10b_rxerr.vcd | Top 8b10b_rxerr:err1  |

| 8b10b_enc.vcd   | Top 8b10b_enc:encode1 |

| mux.vcd         | Top mux:mux1          |

The resulting power analysis applies the simulation vectors in each file to the assigned instance. Simulation provides signal activities for the pins and for the outputs of functional blocks. If the inputs to an instance are input pins for the entire design, the simulation file associated with that instance does not provide signal activities for the inputs of that instance. For example, an input to an instance such as  $\max$ 1 has its signal activity specified at the output of one of the decode instances.

# 1.5.3. Multiple Simulation Power Analysis Flow

You can perform multiple simulations of an entire design or specific modules of a design. For example, in the process of verifying the top-level design, you can have three different simulation testbenches: one for normal operation, and two for corner cases. Each of these simulations produces a separate .vcd. In this case, apply the different .vcd file names to the same top-level entity, as shown in the following table.

**Table 5.** Multiple Simulation File Names and Entities

| File Name   | Entity |

|-------------|--------|

| normal.vcd  | Тор    |

| corner1.vcd | Тор    |

| corner2.vcd | Тор    |

The resulting power analysis uses an arithmetic average of the signal activities calculated from each simulation file to obtain the final signal activities used. If a signal err\_out has a toggle rate of zero transition per second in normal.vcd, 50 transitions per second in cornerl.vcd, and 70 transitions per second in cornerl.vcd, the final toggle rate in the power analysis is 40 transitions per second.

If you do not want the Power Analyzer to read information from multiple instances and take an arithmetic average of the signal activities, use a .vcd that includes only signals from the instance that you care about.

### 1.5.4. Overlapping Simulation Power Analysis Flow

You can perform a simulation on the entire design, and more exhaustive simulations on a submodule, such as 8b10b\_rxerr. The following table lists the import specification for overlapping simulations:

#### **Table 6.** Overlapping Simulation Import Specifications

| File Name       | Entity               |

|-----------------|----------------------|

| full_design.vcd | Тор                  |

| error_cases.vcd | Top 8b10b_rxerr:err1 |

In this case, the software uses signal activities from error\_cases.vcd for all the nodes in the generated .vcd and uses signal activities from full\_design.vcd for only those nodes that do not overlap with nodes in error\_cases.vcd. In general, the more specific hierarchy (the most bottom-level module) derives signal activities for overlapping nodes.

# 1.5.5. Partial Design Simulation Power Analysis Flow

You can perform a simulation in which the entire simulation time is not applicable to signal activity calculation. For example, if you run a simulation for 10,000 clock cycles and reset the chip for the first 2,000 clock cycles. If the Power Analyzer performs the signal activity calculation over all 10,000 cycles, the toggle rates are only 80% of their steady state value (because the chip is in reset for the first 20% of the simulation). In this case, you must specify the useful parts of the .vcd for power analysis. The **Limit VCD Period** option enables you to specify a start and end time when performing signal activity calculations.

#### 1.5.5.1. Specifying Start and End Time for Signal Activity Calculations

To specify a start and end time for signal activity calculations using the **Limit VCD period** option, follow these steps:

- 1. In the Intel Quartus Prime software, click **Assignments** ➤ **Settings**.

- 2. Under the Category list, click Power Analyzer Settings.

- 3. Turn on the Use input file(s) to initialize toggle rates and static probabilities during power analysis option.

- 4. Click Add.

- 5. In the **File name** and **Entity** fields, browse to the necessary files.

- 6. Under Simulation period, turn on VCD file and Limit VCD period options.

- 7. In the **Start time** and **End time** fields, specify the desired start and end time.

- 8. Click OK.

You can also use the following Tcl or .qsf assignment to specify .vcd files:

```

set_global_assignment -name POWER_INPUT_FILE_NAME "test.vcd" -section_id test.vcd set_global_assignment -name POWER_VCD_FILE_START_TIME "10 ns" -section_id test.vcd set_global_assignment -name POWER_VCD_FILE_END_TIME "1000 ns" -section_id test.vcd set_instance_assignment -name POWER_READ_INPUT_FILE test.vcd -to test_design

```

# 1.5.6. Vectorless Estimation Power Analysis Flow

For some device families, the Power Analyzer automatically derives estimates for signal activity on nodes with no simulation or user-entered signal activity data.

Vectorless estimation statistically estimates the signal activity of a node based on the signal activities of nodes feeding that node, and on the actual logic function that the node implements. Vectorless estimation cannot derive signal activities for primary inputs. Vectorless estimation is accurate for combinational nodes, but not for registered nodes. Therefore, the Power Analyzer requires simulation data for at least the registered nodes and I/O nodes for accuracy.

# 1.6. Scripting Support

You can run procedures and create settings described in this chapter in a Tcl script. Alternatively, you can run procedures at a command prompt. For more information about scripting command options, refer to the Intel Quartus Prime Command-Line and Tcl API Help browser. To run the Help browser, type the following command at the command prompt:

```

quartus_sh --qhelp

```

#### **Related Information**

Intel Ouartus Prime Pro Edition Settings File Reference Manual

# 1.6.1. Running the Power Analyzer from the Command-Line

The executable to run the Power Analyzer is quartus\_pow. For a complete listing of all command-line options supported by quartus\_pow, type the following command at a system command prompt:

```

quartus_pow --help

Or

quartus_sh --qhelp

```

The following lists the examples of using the quartus\_pow executable. Type the command listed in the following section at a system command prompt:

Note:

These examples assume that operations are performed on Intel Quartus Prime project called *sample*.

• To instruct the Power Analyzer to generate a EPE File:

```

quartus_pow sample --output_epe=sample.csv ←

```

• To instruct the Power Analyzer to generate a EPE File without performing the power estimate:

```

quartus_pow sample --output_epe=sample.csv --estimate_power=off

```

• To instruct the Power Analyzer to generate an export file for the Power and Thermal Calculator:

```

quartus_pow sample --output_ptc=sample.qptc ←

```

• To instruct the Power Analyzer to generate an export file for the Power and Thermal Calculator without performing the power estimate:

```

quartus_pow sample --output_ptc=sample.qptc --estimate_power=off

```

To instruct the Power Analyzer to use a .vcd as input (sample.vcd):

```

quartus_pow sample --input_vcd=sample.vcd

```

• To instruct the Power Analyzer to use two .vcd files as input files (sample1.vcd and sample2.vcd), perform glitch filtering on the .vcd and use a default input I/O toggle rate of 10,000 transitions per second:

```

quartus_pow sample --input_vcd=sample1.vcd --input_vcd=sample2.vcd \

--vcd_filter_glitches=on --\

default_input_io_toggle_rate=10000transitions/s

```

To instruct the Power Analyzer not to use an input file, specify a default input I/O toggle rate of 60%, with vectorless estimation off, and a default toggle rate of 20% on all remaining signals:

```

quartus_pow sample --no_input_file --default_input_io_toggle_rate=60% \

--use_vectorless_estimation=off --default_toggle_rate=20%

```

Note:

No command–line options are available to specify the information found on the **Operating Settings and Conditions** and **Power Analyzer Settings** ➤ **Thermal** pages. Use the Intel Quartus Prime GUI to specify these options.

The quartus\_pow executable creates a report file, <revision name>.pow.rpt. You can locate the report file in the main project directory. The report file contains the same information that the Power Analyzer Compilation Report.

#### **Related Information**

Viewing Power Analysis Reports on page 18

# 1.7. Power Analysis Revision History

The following revision history applies to this chapter:

| Document Version | Intel Quartus<br>Prime Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2022.06.22       | 21.4                           | In the <i>Power Analysis Tools</i> topic, added statements about Intel Quartus Prime Power Analyzer accuracy for Intel Stratix 10 and Intel Agilex designs.                                                                                                                                                                                                                                                      |

| 2021.12.13       | 21.4                           | <ul> <li>In the Settings for Power Analysis topic, modified a Thermal Settings entry in the Power Analyzer and Thermal Settings table. Specifically, changed Apply Recommended Margin to Apply Additional Margin, and modified the description accordingly.</li> <li>In the Viewing Power Analysis Reports topic, added the Crypto block type to the On-Chip Power Dissipation by Block Type section.</li> </ul> |

| 2021.10.04       | 21.3                           | Recast the note in the <i>Power Analysis Tools</i> topic for greater clarity.                                                                                                                                                                                                                                                                                                                                    |

|                  | •                              | continued                                                                                                                                                                                                                                                                                                                                                                                                        |

#### 683174 | 2022.06.22

| <b>Document Version</b> | Intel Quartus Prime Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2021.03.29              | 21.1                        | <ul> <li>In the Power Analysis topic, updated the figure.</li> <li>In the Running the Power Analyzer topic, modified step 3 and removed the figure following step 9.</li> <li>Changed the title of the Device Operating Condition Settings for Power Analysis topic to Settings for Power Analysis, updated the existing figure and added an additional figure, recast the existing table and added an additional table.</li> <li>In the Generating Signal Activity Data for Power Analysis topic, modified step 5 and the figure within step 6.</li> <li>In the Viewing Power Analysis Reports topic, made minor changes to the first paragraph of the Thermal Map Visualization section.</li> <li>In the Running the Power Analyzer from the Command-Line topic, modified the note at the bottom of the topic.</li> </ul> |

| 2020.12.07              | 20.3.0                      | Added note to the Specifying the Default Toggle Rate topic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2020.10.05              | 20.3.0                      | <ul> <li>Added mention of gate-level simulation to the Specifying Power Analyzer Input, Specifying Signal Activity Data, Using Simulation Signal Activity Data in Power Analysis, and Complete Design Simulation Power Analysis Flow topics,</li> <li>Added a sentence to the RTL Simulation Limitation and Avoiding Simulation Node Name Match topics.</li> <li>Added a Thermal Map Visualization section to the Viewing Power Analysis Reports topic.</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |

| 2020.04.13              | 20.1.0                      | Added information about the Intel FPGA Power and Thermal Calculator to the following topics:  • Power Analysis  • Power Analysis Tools  • Running the Power Analyzer from the Command-Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2019.12.04              | 19.1.0                      | Removed references to entity-specific toggle rates in "Specifying Toggle Rates for Specific Nodes." Toggle rates must be either global or node specific.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2019.08.02              | 19.1.0                      | <ul> <li>Clarified wording of statements about .vcd files in "Simulation Glitch Filtering" topic.</li> <li>Corrected typo in "Specifying the Default Toggle Rate" topic.</li> <li>Corrected typo in "Running the Power Analyzer from the Command Line" topic.</li> <li>Improved explanation in "Generating Standard Delay Output for Power Analysis" topic.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2019.07.03              | 19.1.0                      | Corrected broken links to Help.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2019.04.01              | 19.1.0                      | <ul> <li>Described new support for generation of SDO for use in power analysis.</li> <li>Retitled some topic headings for greater clarity.</li> <li>Changed the order of some topics for improved flow of information.</li> <li>Added descriptions of Power Savings Summary and Parallel Compilation power analysis reports.</li> <li>Added new Power Analysis flow diagrams.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2018.09.24              | 18.1.0                      | General chapter reorganization.     Moved Factors Affecting Power Consumption to chapter: Power Optimization.     Updated figure: Power Analyzer High-level Flow.  continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>Document Version</b> | Intel Quartus Prime Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                             | Divided topic: Types of Power Analysis into two topics: Power Estimations and Design Requirements and Design Activity and Power Analysis.  Updated figure: Power Analysis Tools from Design Concept through Design Implementation and renamed to: Estimation Accuracy for Different Inputs and Power Analysis Tools  Removed content referring to device families not supported in Intel Quartus Prime Pro Edition.        |

| 2018.06.11              | 18.0.0                      | <ul> <li>In Comparison of the EPE and the Intel Quartus Prime Power Analyzer, updated the data output types that the Power Analyzer supports.</li> <li>In Comparison of the EPE and the Intel Quartus Prime Power Analyzer, added row about estimation of transceiver power for features that you enable only through dynamic reconfiguration.</li> <li>Specified features not supported by the Power Analyzer.</li> </ul> |

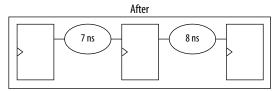

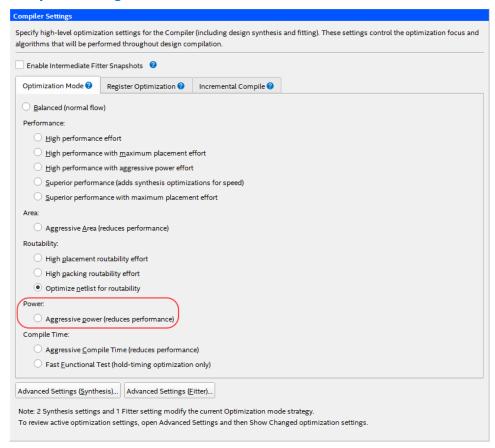

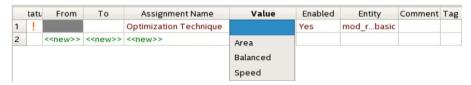

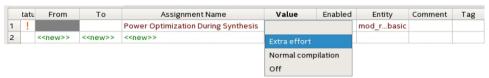

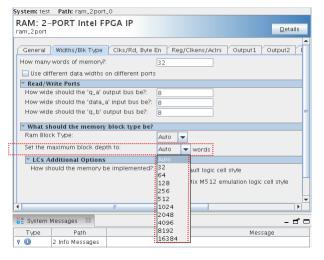

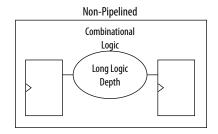

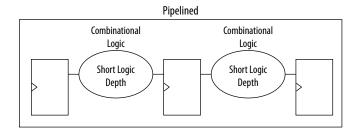

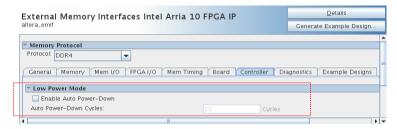

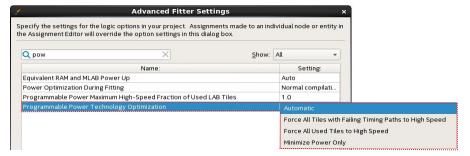

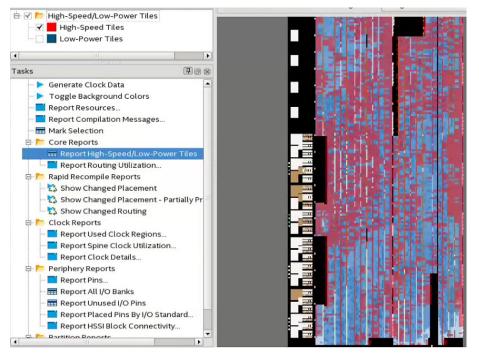

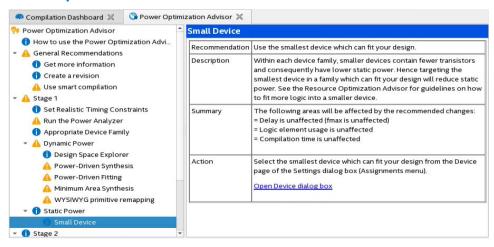

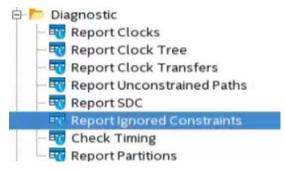

| 2017.05.08              | 17.0.0                      | Removed references to PowerPlay name. Power analysis occurs in the Inte Quartus Prime Power Analyzer.                                                                                                                                                                                                                                                                                                                      |