# JY-5710 Series Family of Analog Output Function Modules User Manual

User Manual Version: v1.0.8

Revision Date: October 8, 2024

# **Table of Contents**

| 1.Introduction                                              | 1  |

|-------------------------------------------------------------|----|

| 1.1 Overview                                                | 1  |

| 1.2 Main Features                                           | 1  |

| 1. Abbreviations                                            | 1  |

| 1.4 Learn by Example                                        | 2  |

| 2. Hardware Specifications                                  | 3  |

| 2.1 Analog Output Specifications                            | 3  |

| 2.2 AO Accuracy                                             | 4  |

| 7.3 Digital IO / PFI Specifications                         | 4  |

| 7.4 Bus and Power Specification                             | 5  |

| 7.5 Physical and Environment                                | 5  |

| 2.E Front Panel and Pin Definition                          | 6  |

| 3.Performance and Tests                                     | 8  |

| 3.1 AO Accuracy                                             | 8  |

| 3.2 Temperature Drift                                       | 9  |

| 3.3 Crosstalk                                               | 9  |

| 4.Software                                                  | 10 |

| 4.1 System Requirements                                     | 10 |

| 4.7 System Software                                         |    |

| 4_3 C# Programming Language                                 |    |

| 4.4 PCIe/PXIe-5710 Series Hardware Driver                   |    |

| 4_5 Install the SeeSharpTools from JYTEK                    |    |

| 4.E Running C# Programs in Linux                            |    |

| 5.Operating PCle/PXle-5710                                  | 13 |

| 5.1 Quick Start                                             |    |

| 5.2 AO Operations                                           | 13 |

| 5.2.1 Finite Output                                         |    |

| 5.2.2 Continuous NoWrappping Output                         | 15 |

| 5.2.3 Continuous Wrapping Output                            |    |

| 5.3 Trigger Source                                          |    |

| 5.3.1 Immediate trigger                                     |    |

| 5.3.2 Software Trigger                                      |    |

| 5.3.3 External Digital Trigger                              |    |

| 5.4 Digital I/O Operations                                  |    |

| 5.4.1 Static DI/DO                                          |    |

| 5.5 System Synchronization Interface (SSI) for PCIe Modules |    |

| 5.E DIP Switch in PCIe-5710                                 |    |

| 6.Calibration                                               |    |

| 7.Using PCle/PXle-5710 in Other Software                    |    |

| 7.1 Python                                                  | 31 |

|     | 7.2 C++                                                                      | 31    |

|-----|------------------------------------------------------------------------------|-------|

|     | 7.3 LabVIEW                                                                  | 31    |

| 8.A | About JYTEK                                                                  | 32    |

|     | 8.1 JYTEK China                                                              | 32    |

|     | 8.2 JYTEK Hardware Products                                                  | 32    |

|     | 8.3 JYTEK Software Platform                                                  | 32    |

|     | E.4 JYTEK Warranty and Support Services                                      | 33    |

| 9.S | tatement                                                                     | 34    |

|     |                                                                              |       |

|     | Figure 1 JYPEDIA Information                                                 | 2     |

|     | Figure 2 PCle/PXle-5710 experiment                                           | 2     |

|     | Figure 3 PXIe/PCIe 5710 Front Panel                                          | 6     |

|     | Figure 4 Temperature Drift                                                   | 9     |

|     | Figure 5 Finite Output for Single Channel Setting                            |       |

|     | Figure 6 Finite Output for Single Channel                                    | 14    |

|     | Figure 7 Finite Output Signal Image on the Oscilloscope                      | 15    |

|     | Figure 8 Continuous NoWrapping Output for Single Channel Setting             | 16    |

|     | Figure 9 Continuous NoWrapping Output for Single Channel                     | 16    |

|     | Figure 10 Continuous NoWrapping Signal Image on the Oscilloscope             | 17    |

|     | Figure 11 Continuous NoWrapping Output for Single Channel Squarewave Set     | tting |

|     |                                                                              | 17    |

|     | Figure 12 Continuous NoWrapping Signal Image on the Oscilloscope             | 18    |

|     | Figure 13 Continuous Wrapping Output for Single Channel Setting              | 19    |

|     | Figure 14 Continuous Wrapping Output for Single Channel                      | 19    |

|     | Figure 15 Continuous Wrapping Signal Image on the Oscilloscope               | 20    |

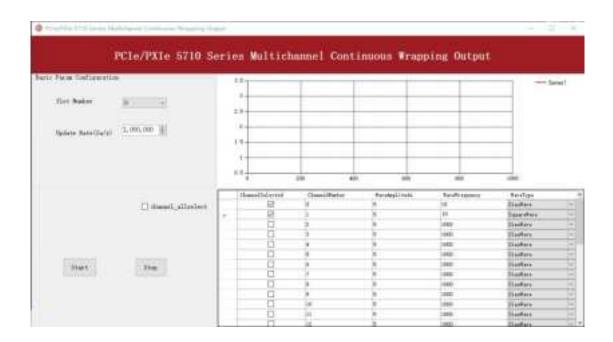

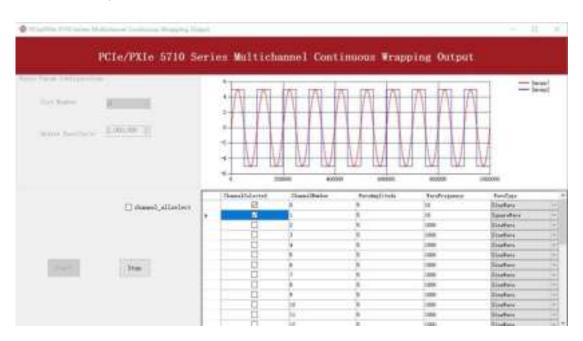

|     | Figure 16 Continuous Wrapping Output for Multichannel Setting                | 21    |

|     | Figure 17 Continuous Wrapping Output for Multichannel                        | 21    |

|     | Figure 18 Continuous Wrapping Multichannel Signal Image on the Oscilloso     | ope   |

|     |                                                                              | 22    |

|     | Figure 19 Continuous Wrapping Output Soft Trigger for Single Channel Setting | 1g23  |

|     | Figure 20 Continuous Wrapping Output Soft Trigger for Single Channel         |       |

|     | Figure 21 Continuous Wrapping Output Soft Trigger Signal Image on            | the   |

|     | Oscilloscope                                                                 | 24    |

|     | Figure 22 External Digital Trigger                                           | 24    |

|     | Figure 23 Continuous Wrapping Output Digital Trigger for Single Channel Set  | tting |

|     |                                                                              | 25    |

|     | Figure 24 Continuous Wrapping Output Digital Trigger for Single Channel      | 25    |

|     | Figure 25 Continuous Wrapping Output Digital Trigger Signal Image on         |       |

|     | Oscilloscope                                                                 |       |

|     | Figure 26 Digital Output SinglePoint Setting                                 |       |

|     | Figure 27 Digital Output SinglePoint                                         | 27    |

| Figure 28 SSI Connector in PCIe-5710                          | 28 |

|---------------------------------------------------------------|----|

| Figure 29 DIP Switch in PCIe-5710                             | 29 |

|                                                               |    |

| T. I. 4.A. I. O. I. C. I. I.                                  | 2  |

| Table 1 Analog Output Specifications                          |    |

| Table 2 Analog Output Basic Accuracy                          | 4  |

| Table 3 Analog Output Additional Accuracy                     | 4  |

| Table 4 Digital IO / PFI Specifications                       | 5  |

| Table 5 Bus and Power Specification                           | 5  |

| Table 6 Physical and Environment                              | 5  |

| Table 7 5710 Pin Definition                                   | 7  |

| Table 8 Notes to Legend                                       | 7  |

| Table 9 Typical AO Accuracy                                   | 8  |

| Table 10 Temperature Drift                                    | 9  |

| Table 11 Crosstalk                                            | 9  |

| Table 12 Supported Linux Versions                             | 10 |

| Table 13 SSI Connector Pin Assignment for PCIe-5710           | 28 |

| Table 14 Relationship between switch position and slot number | 29 |

## 1. Introduction

This chapter presents the information how to use this manual and how to quick start if you are already familiar with Microsoft Visual Studio and C# programming language.

#### 1.1 Overview

The JY5710 Series is a family of Analog Output function modules, which can run on PCIe, PXIe, TXI (Thunderbolt) and USB buses. Depending on the model number, a 5710 series provide different AO channels, sampling rate.

JY5711 features up to 32 channels analog output module with 16 bits resolution and maximum update rate to 2MS/s, 3 lines of digital input/output.

Please check with JYTEK for the latest JY5710 series offering.

# 1.2 Main Features

- High accuracy: 0.02%

- 32 channels of voltage output

- 16 bits DAC

- Output range: ±10 V

- Maximum update rate

- > 8 channels (2 MS/s/ch per bank)

- > 32 channels: 1 MS/s

- Output current drive: ±10 mA

- Overdrive current: 15 mA

- 8M samples FIFO buffer size per channel

- DMA for data transfers

## **1.3** Abbreviations

AO: Analog Output DI: Digital Input DO: Digital Output

DAC: Digital-to-Analog Conversion PFI: Programmable Function Interface

SE: Single-Ended

PPM: Parts Per Million

## 1.4 Learn by Example

JYTEK has added Learn by Example in this manual. We provide many sample programs for this device. Please download the sample programs for this device. You can download a JYPEDIA excel file from our web www.jytek.com. Open JYPEDIA and search for JY5710 in the driver sheet, select JY5710 Examples.zip. In addition to the download information, JYPEDIA also has a lot of other valuable information, JYTEK highly recommend you use this file to obtain information from JYTEK.

| 简仪科技<br>JYTEK              | Drivers are often updated, please register and | Drivers are often updated, please register and receive the update information. |  |  |

|----------------------------|------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| Drivers                    |                                                |                                                                                |  |  |

| JY5710 V1.0.0 Win.zip      | 2021/5/8                                       |                                                                                |  |  |

| JY5710 V1.0.0 Examples.zip | 2021/5/8                                       |                                                                                |  |  |

|                            |                                                |                                                                                |  |  |

|                            |                                                |                                                                                |  |  |

|                            |                                                |                                                                                |  |  |

|                            |                                                |                                                                                |  |  |

Figure 1 JYPEDIA Information

In a Learn by Example section, the sample program is in bold style such as Analog Output-->Winform AO Continuous Wrapping Soft Trigger; the property name in the sample program is also in bold style such as SamplesToUpdate the technical names used in the manual is in italic style such as UpdateRate. You can easily relate the property names in the example program with the manual documentation.

In an Learn by Example section, the experiment is set up as follow. A PCIe/PXIe-5710 card is plugged in a PXI Chassis. The PCIe/PXIe-5710 is connected to a TB-68 terminal block. A Oscilloscope is also connected to the same terminal block as shown Figure 2.

Figure 2 PCIe/PXIe-5710 experiment

# 2. Hardware Specifications

# 2.1 Analog Output Specifications

| Number of channels                                                                | 32 ch                                       |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Resolution                                                                        | 16 bits                                     |  |  |

| DNL                                                                               | ±1 LSB                                      |  |  |

| Unscaled data format                                                              | Signed integer (-32768 to 32767)            |  |  |

| Monotonicity                                                                      | 16 bits                                     |  |  |

| Clock                                                                             | 200 MHz                                     |  |  |

| Maximum update rate                                                               |                                             |  |  |

| 1 channel                                                                         | 2 MS/s                                      |  |  |

| 8 channels (1 channel per bank)*                                                  | 2 MS/s                                      |  |  |

| 32 channels                                                                       | 1 MS/s                                      |  |  |

| Output range                                                                      | ±10 V                                       |  |  |

| Output coupling                                                                   | DC                                          |  |  |

| Output impedance                                                                  | 0.2 Ω                                       |  |  |

| Output current drive                                                              | ±10 mA                                      |  |  |

| Overdrive protection                                                              | ±15 V                                       |  |  |

| Overdrive current                                                                 | 15 mA                                       |  |  |

| Power-on state                                                                    | ±200 mV                                     |  |  |

| FIFO buffer size                                                                  | 8M Samples per channel                      |  |  |

| Data transfers                                                                    | DMA                                         |  |  |

|                                                                                   | Nonperiodic waveform,                       |  |  |

|                                                                                   | Periodic waveform regeneration mode from    |  |  |

| AO waveform modes                                                                 | onboard FIFO,                               |  |  |

|                                                                                   | Periodic waveform regeneration from host    |  |  |

|                                                                                   | buffer including dynamic update             |  |  |

| Slew rate                                                                         | 20 V/μs                                     |  |  |

| Noise                                                                             | 400 μVrms, DC to 1 MHz                      |  |  |

| AO update glitch Glitch energy                                                    | 5 nVs                                       |  |  |

| Channel crosstalk                                                                 | -65 dB                                      |  |  |

| Reference clock                                                                   | PXIe_DSTARA, PXIe_DSTARB, PXIe_CLK100       |  |  |

| External sample clock                                                             | PFI, PXI_TRIG                               |  |  |

| Trigger source                                                                    | Digital, Software                           |  |  |

| Trigger type                                                                      | Start Trigger                               |  |  |

| Digital trigger source                                                            | PFI, PXI_TRIG                               |  |  |

| * Each bank consists of four AO channe<br>within a single bank will update simult | els using two DACs. Any channels being used |  |  |

within a single bank will update simultaneously.

Table 1 Analog Output Specifications

# 2.2 AO Accuracy

| JY5711 AO Basic Accuracy = ±(% of Output+% of Range) |       |                   |       |       |           |       |        |                                   |

|------------------------------------------------------|-------|-------------------|-------|-------|-----------|-------|--------|-----------------------------------|

| Nominal<br>Range (V)                                 |       | 24 Hour Tcal ±1C° |       | 90 [  | Days Tcal |       |        | 90 Days<br>Full-Scale<br>Accuracy |

| 10                                                   | 0.003 | +                 | 0.005 | 0.012 | +         | 0.008 | 790 uV | 2000 uV                           |

Table 2 Analog Output Basic Accuracy

| JY5711 AO Additional Accuracy Adjustment |                                 |      |        |            |

|------------------------------------------|---------------------------------|------|--------|------------|

|                                          |                                 |      |        | Full-Scale |

| Nominal                                  | Tomporatu                       | Temp |        |            |

| Range (V)                                | Temperature Coefficients (/ °C) |      |        | Adjustment |

|                                          |                                 |      |        | (uV/ °C)   |

| 10                                       | 0.0007                          | +    | 0.0002 | 90 uV      |

Table 3 Analog Output Additional Accuracy

# 2.3 Digital IO / PFI Specifications

## **Static Characteristics**

| Number of channels       | 3 DIO                           |

|--------------------------|---------------------------------|

| Ground reference         | DGND                            |

| Direction control        | Each terminal individually      |

| Direction control        | programmable as input or output |

| Pull-down resistor       | 50 kΩ typical                   |

| Input voltage protection | ±15 V                           |

### PFI Functionality

| Number of channels                  | 3                            |  |

|-------------------------------------|------------------------------|--|

| lexternal digital trigger intertace | Trigger voltage 3.3 V TTL;   |  |

|                                     | Trigger edge: Rising/Falling |  |

| Initial state                       | Input                        |  |

## **Recommended Operating Conditions**

| Minimum Input high voltage (V <sub>IH</sub> )  | 2.2 V  |

|------------------------------------------------|--------|

| Maximum Input high voltage (V <sub>IH</sub> )  | 5.25 V |

| Minimum Input Iow voltage (V <sub>IL</sub> )   | 0 V    |

| Maximum Input Iow voltage (V <sub>IL</sub> )   | 0.8 V  |

| Maximum Output high current (I <sub>OH</sub> ) | -16 mA |

| Maximum Output low current (I <sub>OL</sub> )  | 16 mA  |

# 2.4 Bus and Power Specification

#### Bus Interface

| Form factor        | x4 PXI Express peripheral module                  |

|--------------------|---------------------------------------------------|

| Slot compatibility | x1 and x4 PXI Express or PXI Express hybird slots |

#### **Power Requirements**

| 3.3 V: | 3.0 W  |

|--------|--------|

| +12 V: | 14.0 W |

Table 5 Bus and Power Specification

# 2.5 Physical and Environment

**Operating Environment**

| Ambient temperature range | 0 °C to 50 °C             |

|---------------------------|---------------------------|

| Relative humidity range   | 20% to 80%, noncondensing |

#### **Storage Environment**

| 000.080 =                 |                           |  |  |  |

|---------------------------|---------------------------|--|--|--|

| Ambient temperature range | -20 °C to 80 °C           |  |  |  |

| Relative humidity range   | 10% to 90%, noncondensing |  |  |  |

Table 6 Physical and Environment

# 2.6 Front Panel and Pin Definition

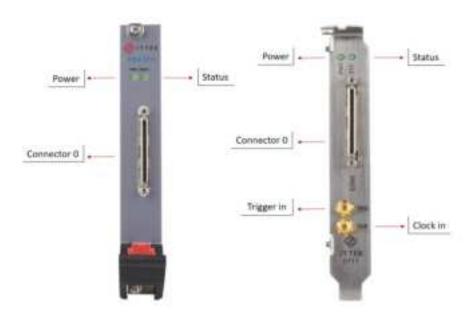

Figure 3 PXIe/PCIe 5710 Front Panel

PCIe/PXIe-5710 series boards are connected to outside signals by one 68-pin cable for the 32 channel configurations, Table 7 shows the pin definitions of PCIe/PXIe-5711 .

| Pin Signal Name Pin Sig                 | nal Name     |

|-----------------------------------------|--------------|

| , , , , , , , , , , , , , , , , , , , , | ilai ivallic |

| 1 PFI0/DIO_0 35                         | DGND         |

| 2 PFI1/DIO_1 36 PF                      | 12/DIO_2     |

| 3 AO_0 37                               | AO_GND       |

| 4 AO_1 38                               | AO_GND       |

| 5 AO_2 39 A                             | AO_GND       |

| 6 AO_3 40                               | AO_GND       |

| 7 AO_4 41 A                             | AO_GND       |

| 8 AO_5 42 A                             | AO_GND       |

| 9 AO_6 43 A                             | AO_GND       |

| 10 AO_7 44 A                            | AO_GND       |

| 11 AO_8 45                              | AO_GND       |

| 12 AO_9 46 A                            | AO_GND       |

| 13 AO_10 47                             | AO_GND       |

| 14 AO_11 48 A                           | AO_GND       |

| 15 AO_12 49 A                           | AO_GND       |

| 16 AO_13 50 A                           | AO_GND       |

| 17 AO_14 51 A                           | AO_GND       |

| 18 AO_15 52 A                           | AO_GND       |

| 19 AO_16 53 A                           | AO_GND       |

| 20 AO_17 54 A                           | AO_GND       |

| 21 AO_18 55 A                           | AO_GND       |

| 22 AO_19 56 A                           | AO_GND       |

| 23 AO_20 57                             | AO_GND       |

| 24 AO_21 58 A                           | AO_GND       |

| 25 AO_22 59 A                           | AO_GND       |

| 26 AO_23 60 A                           | AO_GND       |

| 27 AO_24 61 A                           | AO_GND       |

| 28 AO_25 62 A                           | AO_GND       |

| 29 AO_26 63 A                           | AO_GND       |

| 30 AO_27 64 A                           | AO_GND       |

| 31 AO_28 65 A                           | AO_GND       |

| 32 AO_29 66 A                           | AO_GND       |

| 33 AO_30 67 A                           | AO_GND       |

| 34 AO_31 68                             | AO_GND       |

Table 7 5710 Pin Definition

# Notes to Legend in the Pin Definitions

| AO_GND  | Analog Output Reference Ground  |  |  |

|---------|---------------------------------|--|--|

| AO<031> | Analog Output channel           |  |  |

| D_GND   | Digital Signal Reference Ground |  |  |

| PFI<02> | Programmable Function Interface |  |  |

Table 8 Notes to Legend

# 3. Performance and Tests

# 3.1 AO Accuracy

The best AO accuracy is limited by two factors: Total Gain Error and Total Offset Error as shown in the following table. The PCIe/PXIe-5710 device is first calibrated.

| JY5711 AO Basic Accuracy = ±(% of Output+% of Range) |                   |                   |        |                                   |

|------------------------------------------------------|-------------------|-------------------|--------|-----------------------------------|

| Nominal<br>Range (V)                                 | 24 Hour Tcal ±1C° | 90 Days Tcal ± 5° |        | 90 Days<br>Full-Scale<br>Accuracy |

| 10                                                   | 0.003 + 0.005     | 0.007 + 0.011     | 790 uV | 1800 uV                           |

Table 9 Typical AO Accuracy

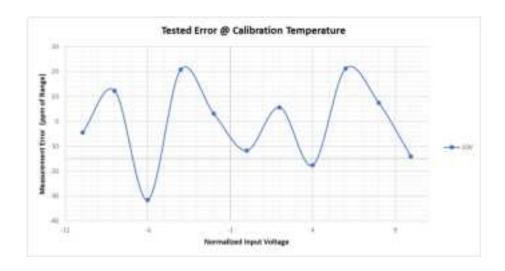

# 3.2 Temperature Drift

The temperature change will affect the AO accuracy by the gain error and offset error. The typical gain error and offset error of PCIe/PXIe-5710 are show below.

| JY5711 AO Additional Accuracy Adjustment |                                         |            |  |

|------------------------------------------|-----------------------------------------|------------|--|

|                                          |                                         | Full-Scale |  |

| Nominal                                  | Nominal Temperature Coefficients (/ %C) |            |  |

| Range (V)                                | Temperature Coefficients (/ °C)         | Adjustment |  |

| . ,                                      |                                         | (uV/ °C)   |  |

| 10                                       | 0.0007 + 0.0002                         | 90 uV      |  |

Table 10 Temperature Drift

Figure 4 Temperature Drift

# 3.3 Crosstalk

| Reference Channel | Tested Channel | Crosstalk (dB at 100 KHz) |

|-------------------|----------------|---------------------------|

| 0                 | 1              | -71.8                     |

| 0                 | 15             | -71.4                     |

| 0                 | 16             | -70.4                     |

| 1                 | 2              | -71.8                     |

| 6                 | 7              | -71.4                     |

| 6                 | 22             | -70.9                     |

| 10                | 11             | -72.1                     |

| 16                | 17             | -67.2                     |

| 31                | 30             | -71.6                     |

Table 11 Crosstalk

### 4. Software

# **4.1 System Requirements**

PCIe/PXIe-5710 boards can be used in a Windows or a Linux operating system.

Microsoft Windows: Windows 7 32/64 bit, Windows 10 32/64 bit.

Linux Kernel Versions: There are many Linux versions. It is not possible JYTEK can support and test our devices under all different Linux versions. JYTEK will at the best support the following Linux versions.

|                           | Linux Version                                               |  |  |

|---------------------------|-------------------------------------------------------------|--|--|

|                           | Ubuntu LTS                                                  |  |  |

| 16.04: 4                  | .4.0-21-generic(desktop/server)                             |  |  |

| 16.04.6: 4                | 4.15.0-45-generic(desktop) 4.4.0-142-generic(server)        |  |  |

| 18.04: 4                  | .15.0-20-generic(desktop) 4.15.0-91-generic(server)         |  |  |

| 18.04.4: 5                | 5.3.0-28-generic (desktop) 4.15.0-91-generic(server)        |  |  |

| Localized Chinese Version |                                                             |  |  |

| 中标麒麟县                     | 桌面操作系统软件(兆芯版)V7.0(Build61): 3.10.0-862.9.1.nd7.zx.18.x86_64 |  |  |

| 中标麒麟哥                     | 高级服务器操作系统软件V7.0U6: 3.10.0-957.el7.x86_64                    |  |  |

**Table 12 Supported Linux Versions**

# 4.2 System Software

When using the PCIe/PXIe-5710 in the Window environment, you need to install the following software from Microsoft website:

Microsoft Visual Studio Version 2015 or above,

.NET Framework version is 4.0 or above.

.NET Framework is coming with Windows 10. For Windows 7, please check .NET Framework version and upgrade to 4.0 or later version.

Given the resources limitation, JYTEK only tested PCIe/PXIe-5710 be with .NET Framework 4.0 with Microsoft Visual Studio 2015. JYTEK relies on Microsoft to maintain the compatibility for the newer versions.

# **4.3** C# Programming Language

All JYTEK default programming language is Microsoft C#. This is Microsoft recommended programming language in Microsoft Visual Studio and is particularly suitable for the test and measurement applications. C# is also a cross platform programming language.

# 4\_4 PCIe/PXIe-5710 Series Hardware Driver

After installing the required application development environment as described above, you need to install the PCIe/PXIe-5710 hardware driver.

JYTEK hardware driver has two parts: the shared common driver kernel software (FirmDrive) and the specific hardware driver.

Common Driver Kernel Software (FirmDrive): FirmDrive is the JYTEK's kernel software for all hardware products of JYTEK instruments. You need to install the FirmDrive software before using any other JYTEK hardware products. FirmDrive only needs to be installed once. After that, you can install the specific hardware driver.

Specific Hardware Driver: Each JYTEK hardware has a C# specific hardware driver. This driver provides rich and easy-to-use C# interfaces for users to operate various PCIe/PXIe-5710 function. JYTEK has standardized the ways which JYTEK and other vendor's DAQ boards are used by providing a consistent user interface, using the methods, properties and enumerations in the object-oriented programming environment. Once you get yourself familiar with how one JYTEK DAQ card works, you should be able to know how to use all other DAQ hardware by using the same methods.

Note that this driver does not support cross-process, and if you are using more than one function, it is best to operate in one process.

# 4.5 Install the SeeSharpTools from JYTEK

To efficiently and effectively use PCIe/PXIe-5710 boards, you need to install a set of free C# utilities, SeeSharpTools from JYTEK. The SeeSharpTools offers rich user interface functions you will find convenient in developing your applications. They are also needed to run the examples come with PCIe/PXIe-5710 hardware. Please register and download the latest SeeSharpTools from our website, www.jytek.com.

# 4.6 Running C# Programs in Linux

Most C# written programs in Windows can be run by MonoDevelop development system in a Linux environment. You would develop your C# applications in Windows using Microsoft Visual Studio. Once it is done, run this application in the MonoDevelop environment. This is JYTEK recommended way to run your C# programs in a Linux environment.

If you want to use your own Linux development system other than MonoDevelop, you can do it by using our Linux driver. However, JYTEK does not have the capability to support the Linux applications. JYTEK completely relies upon Microsoft to maintain the cross-platform compatibility between Windows and Linux using MonoDevelop.

# 5. Operating PCIe/PXIe-5710

This chapter provides the operation guides for PCIe/PXIe-5710, including AO, DI, DO, etc.

JYTEK provides extensive examples, on-line help and documentation to assist you to operate the PCIe/PXIe-5710 board. JYTEK strongly recommends you go through these examples before writing your own application. In many cases, an example can also be a good starting point for a user application.

#### 5.1 Quick Start

After you have installed the driver software and the SeeSharpTools, you are ready to use Microsoft Visual Studio C# to operate the PCle/PXle-5710 products.

If you are already familiar with Microsoft Visual Studio C#, the quickest way to use PCle/PXle-5710 boards is to go through our extensive examples. We provide source code of our examples. In many cases, you can modify the source code and start to write your applications.

We also provide **Learn by Example** in the following sections. These examples will help you navigate and learn how to use this PCIe/PXIe-5710.

# 5.2 AO Operations

The PCIe/PXIe-5710 AO provides 16-bit simultaneous outputs. The analog output has three modes of operation: Finite, ContinuousWrapping, and ContinuousNoWrapping.

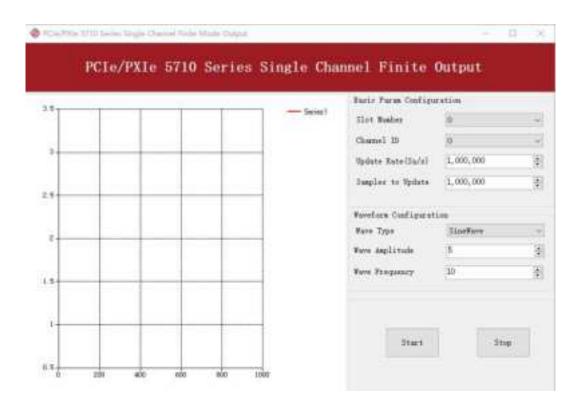

## 5.2.1 Finite Output

The finite output requires the user to write a piece of data. After starting the AO, it starts to output the written data until the output is completed.

#### Learn by Example 5.2.1

- Connect the PCIe/PXIe-5710 AO Ch0 (AO\_0, Pin #3) to the probe tip of the oscilloscope, and AO ground (AO\_GND, Pin #37) is connected to the grounding clip of the oscilloscope.

- PCle/PXle-5710 sends an analog signal through (AO\_0, AO\_GND) and reads the signal on an oscilloscope.

- Open **Analog Output-->Winform AO Finite**, set the following numbers as shown:

Figure 5 Finite Output for Single Channel Setting

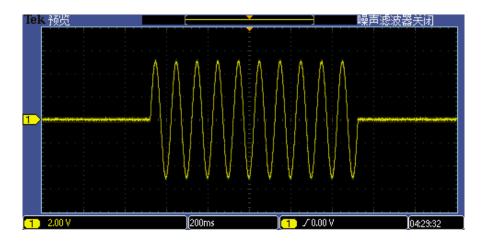

Click **Start** to generate a **SineWave**. The generated signal is shown below:

Figure 6 Finite Output for Single Channel

The image on the oscilloscope is shown in the figure:

Figure 7 Finite Output Signal Image on the Oscilloscope

The analog signal is successfully generated by PCIe/PXIe-5710.

## **5.2.2 Continuous NoWrappping Output**

The continuous acyclic output needs to write a piece of data before starting the AO. After the AO starts, user needs to continuously write new data to ensure the continuous output of the AO.

## Learn by Example 5.2.1

- Connect the PCIe/PXIe-5710 AO Ch0 (AO\_0, Pin #3) to the probe tip of the oscilloscope, and AO ground (AO\_GND, Pin #37) is connected to the grounding clip of the oscilloscope.

- PCIe/PXIe-5710 sends an analog signal through (AO\_0, AO\_GND) and reads the signal on an oscilloscope.

- Open Analog Output-->Winform AO Continuous NoWrapping, set the following numbers as shown:

Figure 8 Continuous NoWrapping Output for Single Channel Setting

- In no wrapping analog output you can change the parameter of the signal whenever you want in Waveform Configuration when generating the wave. After the configuration you should click **Update** to apply the changes.

- Click **Start** to generate a sinewave first. The result is shown below.

Figure 9 Continuous NoWrapping Output for Single Channel

The image on the oscilloscope is shown in the figure:

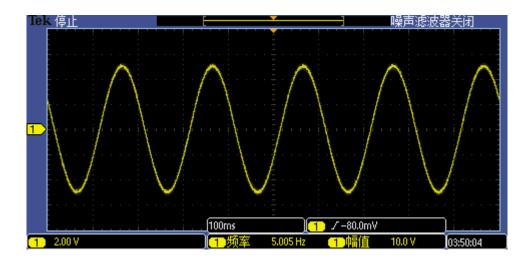

Figure 10 Continuous NoWrapping Signal Image on the Oscilloscope

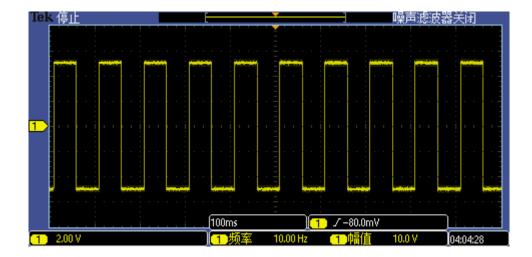

Now change the Wave Type to Squarewave and click Update to generate it. The result is shown below.

Figure 11 Continuous NoWrapping Output for Single Channel Squarewave Setting

The image on the oscilloscope is shown in the figure:

Figure 12 Continuous NoWrapping Signal Image on the Oscilloscope

The analog signal is successfully generated by PCIe/PXIe-5710.

## **5.2.3 Continuous Wrapping Output**

The continuous loop output first writes a piece of data before starting the AO. After the AO starts, the board will repeatedly output this data until user sends a stop command.

## Learn by Example 5.2.1

- Connect the PCIe/PXIe-5710 AO Ch0 (AO 0, Pin #3) to the probe tip of the oscilloscope, and AO ground (AO\_GND, Pin #37) is connected to the grounding clip of the oscilloscope.

- PCIe/PXIe-5710 sends an analog signal through (AO\_0, AO\_GND) and reads the signal on an oscilloscope.

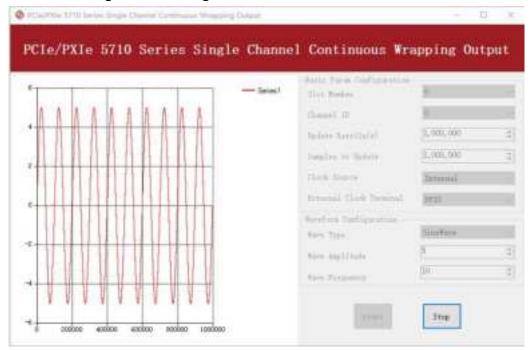

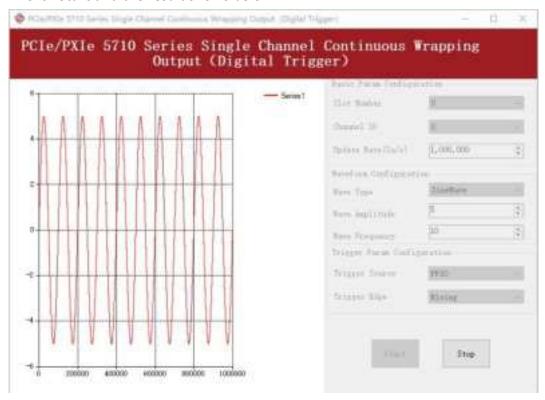

- Open Analog Output-->Winform AO Continuous Wrapping, set the following numbers as shown:

Figure 13 Continuous Wrapping Output for Single Channel Setting

Click **Start** to generate the signal. The result is shown below.

Figure 14 Continuous Wrapping Output for Single Channel

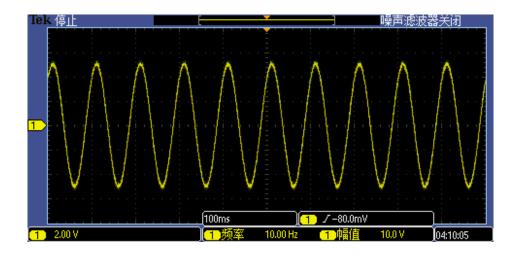

The image on the oscilloscope is shown in the figure:

Figure 15 Continuous Wrapping Signal Image on the Oscilloscope

The analog signal is successfully generated by PCIe/PXIe-5710.

# **5.3** Trigger Source

There are 3 trigger types: Immediate trigger, Software trigger, and Digital trigger. The trigger type is a property and set by driver software.

## 5.3.1 Immediate trigger

This trigger mode does not require configuration and is triggered immediately when an operation starts. The operation can be AO, DI, DO etc.

### Learn by Example 5.2.1

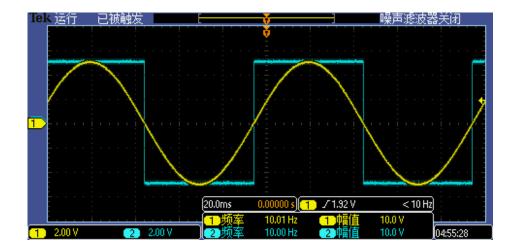

- PCIe/PXIe-5710 AO Ch0 (AO\_0, pin # 3) and AO Ch1 (AO\_1, pin # 4) are connected to the probe tips of channel 1 and channel 2 of oscilloscope respectively. Connect AO ground (AO GND, pin #37) to the ground clips of oscilloscope channels 1 and

- PCIe/PXIe-5710 sends an analog signal through (AO\_0,AO\_GND)、 (AO\_1, AO\_GND) and reads the signal on an oscilloscope.

- Open Analog Output-->Winform AO Continuous Wrapping Multichannel, set the following numbers as shown:

Figure 16 Continuous Wrapping Output for Multichannel Setting

Click Start, the result is shown below.

Figure 17 Continuous Wrapping Output for Multichannel

The image on the oscilloscope is shown in the figure:

Figure 18 Continuous Wrapping Multichannel Signal Image on the Oscilloscope

PCIe/PXIe-5710 multi-channel analog signal was successfully generated.

## 5.3.2 Software Trigger

A software trigger must be configured by the driver software. The trigger starts when a trigger software routine is called.

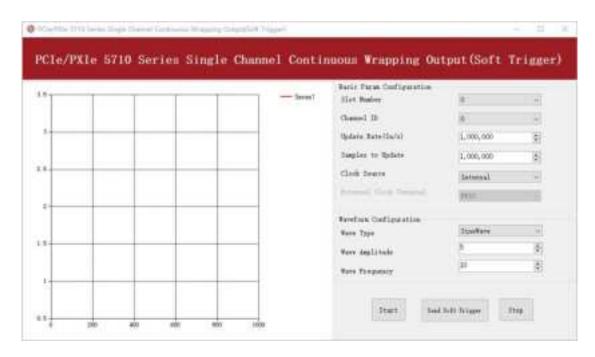

### **Learn by Example 5.3.2**

- Connect the PCIe/PXIe-5710 AO Ch0 (AO 0, Pin #3) to the probe tip of the oscilloscope, and AO ground (AO GND, Pin #37) is connected to the grounding clip of the oscilloscope.

- PCIe/PXIe-5710 sends an analog signal through (AO\_0, AO\_GND) and reads the signal on an oscilloscope.

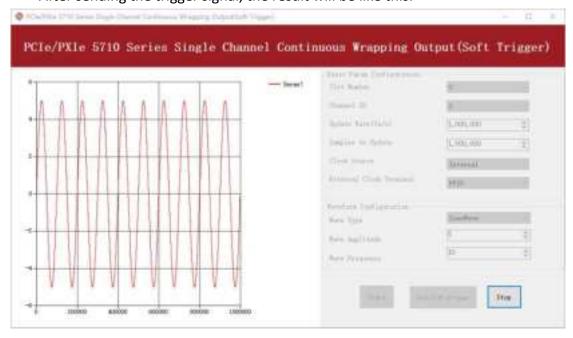

- Open Analog Output-->Winform AO Continuous Wrapping Soft Trigger, set the following numbers as shown:

Figure 19 Continuous Wrapping Output Soft Trigger for Single Channel Setting

- Click **Start** to run the task.

- Data will not be acquired until there is a positive signal from Software Trigger when **Send Soft Trigger** is clicked.

- After sending the trigger signal, the result will be like this:

Figure 20 Continuous Wrapping Output Soft Trigger for Single Channel

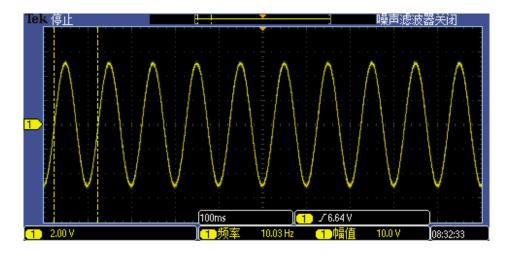

The image on the oscilloscope is shown in the figure:

Figure 21 Continuous Wrapping Output Soft Trigger Signal Image on the Oscilloscope

### 5.3.3 External Digital Trigger

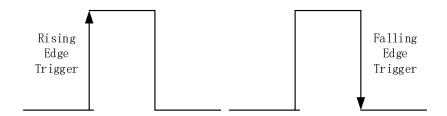

PCIe/PXIe-5710 supports different external digital trigger sources from PXI Trigger bus (PXI\_TRIG<0..7>), and PFI. The high pulse width of digital trigger signal must be longer than 20 ns for effective trigger. The module will monitor the signal on digital trigger source and wait for the rising edge or falling edge of digital signal which depending on the set trigger condition, then cause the module to acquire the data as shown in Figure 22.

Figure 22 External Digital Trigger

### Learn by Example 5.2.1

- Connect the PCIe/PXIe-5710 AO Ch0 (AO\_0, Pin #3) to the probe tip of the oscilloscope, and AO ground (AO GND, Pin #37) is connected to the grounding clip of the oscilloscope.

- The positive connector of function generator is connected to the digital trigger source(PFIO, Pin #1)of PCIe/PXIe-5710, and the negative connector is connected to the digital ground(DGND, Pin #35). Set up a squarewave signal (f=4Hz, Vpp=5v).

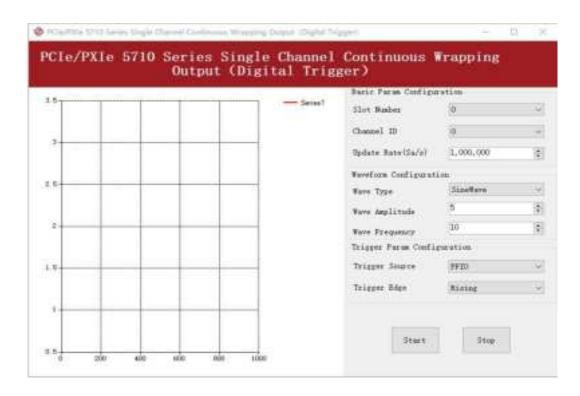

- Open Analog Output-->Winform AO Continuous Wrapping Digital Trigger, set the following numbers as shown:

Figure 23 Continuous Wrapping Output Digital Trigger for Single Channel Setting

- > Trigger Source must match the pin on 5710.

- There are two Trigger Edge: Rising and Falling.

- Click Start and the result shows below:

Figure 24 Continuous Wrapping Output Digital Trigger for Single Channel

PCIe/PXIe-5710 Series | jytek.com | 25

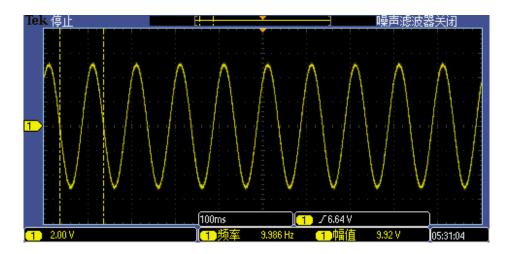

The image on the oscilloscope is shown in the figure:

Figure 25 Continuous Wrapping Output Digital Trigger Signal Image on the Oscilloscope

> Since the squarewave is used for the digital trigger source, when a rising edge of the squarewave occurs, the digital trigger will be activated, and the data generation will start.

# 5.4 Digital I/O Operations

The PCIe/PXIe-5710 provides powerful programmable digital I/O functions.

## 5.4.1 Static DI/DO

Programmable I/O supports static TTL, 3 lines(0,1,2). User can acess these I/O information through software polling.

### Learn by Example 5.4.1

- In this example PCIe/PXIe-5710 outputs a digital signal by its DO function and reads it back by its DI function.

- Connect the PCIe/PXIe-5710 DIO\_0/PFI0(pin #1) and DIO\_1/PFI1(pin #2);

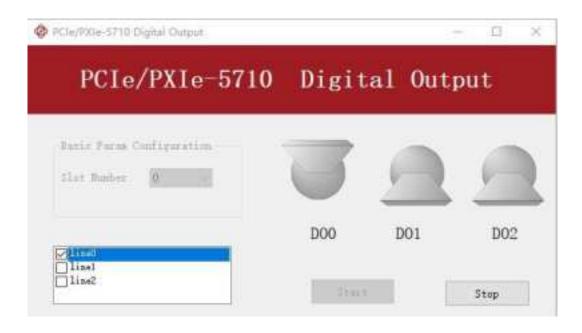

- Open the first program **Digital Output-->Winform DO SinglePoint.**

- Select line 0 for Digital Output, Set DO0 in High-Level positions, make sure all other lines are in Low-Level positions. Click Start to generate the High-Levels as shown.

Figure 26 Digital Output SinglePoint Setting

- Open the second program **Digital Input-->Winform DI SinglePoint**.

- Select **line 1** for **Digital Input** as shown, and click **Start**. The result is shown below.

Figure 27 Digital Output SinglePoint

The result matches the high and low levels set before.

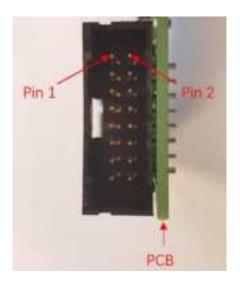

# **5.5** System Synchronization Interface (SSI) for PCle Modules

The synchronization between PCIe modules are handled differently from the PXIe synchronization, it is implemented by the system synchronization interface (SSI). SSI is designed as a bidirectional bus and it can synchronize up to four PCIe modules. One PCIe module is designated as the master module and the other PCIe modules are designated as the slave modules.

Figure 28 SSI Connector in PCle-5710

| Pin | n Signal Name Signal Name |     | Pin |

|-----|---------------------------|-----|-----|

| 1   | PXI_TRIG0                 | GND | 2   |

| 3   | PXI_TRIG1                 | GND | 4   |

| 5   | PXI_TRIG2                 | GND | 6   |

| 7   | PXI_TRIG3                 | GND | 8   |

| 9   | PXI_TRIG4                 | GND | 10  |

| 11  | PXI_TRIG5                 | GND | 12  |

| 13  | PXI_TRIG6                 | GND | 14  |

| 15  | PXI_TRIG7                 | GND | 16  |

Table 13 SSI Connector Pin Assignment for PCIe-5710

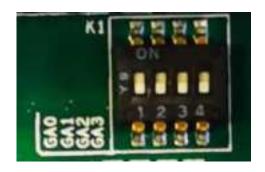

### 5.6 DIP Switch in PCIe-5710

PCIe-5710 series modules have a DIP switch. The card number can be adjusted manually by changing the DIP switch setting, which is used to identify the boards with different slot positions.

For example, if you want to set the card number to 3, you could turn the position 2 and 1 of the DIP switch to the ON position and the orthers to OFF. See below for details.

Figure 29 DIP Switch in PCIe-5710

|                   | Position 4<br>(GA3) | Position 3<br>(GA2) | Position 2<br>(GA1) | Position 1<br>(GA0) |

|-------------------|---------------------|---------------------|---------------------|---------------------|

| Slot 0            | (0/3)               | ( <b>GAZ</b> )      | (GAI)               | (070)               |

| Slot 1            | 0                   | 0                   | 0                   | 1                   |

|                   |                     |                     | 1                   |                     |

| Slot 2            | 0                   | 0                   | 1                   | 0                   |

| Slot 3            | 0                   | 0                   | 1                   | 1                   |

| Slot 4            | 0                   | 1                   | 0                   | 0                   |

| Slot 5            | 0                   | 1                   | 0                   | 1                   |

| Slot 6            | 0                   | 1                   | 1                   | 0                   |

| Slot 7            | 0                   | 1                   | 1                   | 1                   |

| Slot 8            | 1                   | 0                   | 0                   | 0                   |

| Slot 9            | 1                   | 0                   | 0                   | 1                   |

| Slot 10           | 1                   | 0                   | 1                   | 0                   |

| Slot 11           | 1                   | 0                   | 1                   | 1                   |

| Slot 12           | 1                   | 1                   | 0                   | 0                   |

| Slot 13           | 1                   | 1                   | 0                   | 1                   |

| Slot 14           | 1                   | 1                   | 1                   | 0                   |

| Slot 15           | 1                   | 1                   | 1                   | 1                   |

| Note: OFF=0/ ON=1 |                     |                     |                     |                     |

Table 14 Relationship between switch position and slot number

# 6. Calibration

PCIe/PXIe-5710 Series boards are precalibrated before the shipment. We recommend you recalibrate PCIe/PXIe-5710 board periodically to ensure the measurement accuracy. A commonly accepted practice is one year. If for any reason, you need to recalibrate your board, please contact JYTEK.

# 7. Using PCIe/PXIe-5710 in Other Software

While JYTEK's default application platform is Visual Studio, the programming language is C#, we recognize there are other platforms that are either becoming very popular or have been widely used in the data acquisition applications. Among them are Python, C++ and LabVIEW. This chapter explains how you can use PCIe/PXIe-5710 DAQ card using one of this software.

# 7.1 Python

JYTEK provides and supports a native Python driver for PCIe/PXIe-5710 boards. There are many different versions of Python. JYTEK has only tested in CPython version 3.5.4. There is no guarantee that JYTEK python drivers will work correctly with other versions of Python.

If you want to be our partner to support different Python platforms, please contact us.

### 7.2 C++

JYTEK internally uses our C++ drivers to design the C# drivers. We recommend our customers to use C# drivers because C# platform deliver much better efficiency and performance in most situations. We also make our C++ drivers available. However, due to the limit of our resources, we do not actively support C++ drivers. If you want to be our partner to support C++ drivers, please contact us.

#### 7 3 LabVIEW

LabVIEW is a software product from National Instruments. JYTEK provides LabVIEW interface to PCIe/PXIe-5710 boards. You can download the LabVIEW drivers from our website. While JYTEK does not support LabVIEW applications, we may recommend you to a third party who can assist you to interface your LabVIEW with our PCIe/PXIe-5710 boards. We can also recommend you if you want to convert your LabVIEW applications to C# based applications.

### 8. About JYTEK

#### **8.1 JYTEK China**

Founded in June, 2016, JYTEK China is a leading Chinese test & measurement company, providing complete software and hardware products for the test and measurement industry. The company is a joint venture between Adlink Technologies and a group of experienced professionals form the industry. JYTEK independently develop the software and hardware products and is entirely focused on the Chinese market. Our Shanghai headquarters and production service center have regular stocks to ensure timely supply; we have R&D centers in Xi'an and Chongqing to develop new products; we also have highly trained direct technical sales representatives in Shanghai, Beijing, Tianjin, Xi'an, Chengdu, Nanjing, Wuhan, Haerbin, and Changchun. We also have many partners who provide system level support in various cities.

#### **8.2 JYTEK Hardware Products**

According to JYTEK's agreement with our equity partner Adlink Technologies, JYTEK's hardware is manufactured by the state-of-art manufacturing facility located in Shanghai Zhangjiang Hi-Tech Park. Adlink has over 20 years of the world-class low-volume and high-mix manufacturing expertise with ISO9001-2008, China 3C, UL, ROHS, TL9000, ISO-14001, ISO-13485 certifications. Its 30,000 square meters facilities and three high-speed Panasonic SMT production lines can produce 60,000 pieces boards/month; it also has full supply chain management - planning, sweeping, purchasing, warehousing and distribution. Adlink's manufacturing excellence ensures JYTEK's hardware has word-class manufacturing quality.

One core technical advantage is JYTEK's pursue for the basic and fundamental technology excellence. JYTEK China has developed a unique PCIe, PXIe, USB hardware driver architecture, FirmDrive, upon which many our future hardware will be based.

In addition to our own developed hardware, JYTEK also rebrands Adlink's PXI product lines. In addition, JYTEK has other rebranding agreements to increase our hardware coverage. It is our goal to provide the complete product coverage in PXI and PCI modular instrumentation and data acquisition.

#### **8.3 JYTEK Software Platform**

JYTEK has developed a complete software platform, SeeSharp Platform, for the test and measurement applications. We leverage the open sources communities to provide the software tools. Our platform software is also open sourced and is free, thus lowering the cost of tests for our customers. We are the only domestic vendor to offer complete commercial software and hardware tools.

# **8.4** JYTEK Warranty and Support Services

With our complete software and hardware products, JYTEK is able to provide technical and sales services to wide range of applications and customers. In most cases, our products are backed by a 1-year warranty. For technical consultation, pre-sale and after-sales support, please contact JYTEK of your country.

9. Statement

The hardware and software products described in this manual are provided by JYTEK China, or JYTEK

in short.

This manual provides the product review, quick start, some driver interface explanation for JYTEK

PCIe/PXIe-5710 Series family of multi-function data acquisition boards. The manual is copyrighted by

JYTEK.

No warranty is given as to any implied warranties, express or implied, including any purpose or non-

infringement of intellectual property rights, unless such disclaimer is legally invalid. JYTEK is not

responsible for any incidental or consequential damages related to performance or use of this

manual. The information contained in this manual is subject to change without notice.

While we try to keep this manual up to date, there are factors beyond our control that may affect the

accuracy of the manual. Please check the latest manual and product information from our website.

Shanghai Jianyi Technology Co., Ltd.

Address: Room 201, Building 3, NO.300 Fangchun Road, Shanghai.

Post Code: 201203

Tel: 021-5047 5899

Website: www.jytek.com

PCIe/PXIe-5710 Series | jytek.com | 34