User manual

# EVAL-L5965 Evaluation board

#### Introduction

This document provides information concerning features and usage of the EVAL-L5965 that is the complete name for the device evaluation board.

### 1 Preface

The L5965 is a multichannel voltage regulator specifically designed to support applications that need to fulfill functional safety requirements as defined by automotive safety integrity level (ASIL).

It is available in the VQFPN-48 package.

This document describes how to use the L5965 application board in order to check device's performance (please refer to the datasheet for more information).

UM3229 - Rev 1 page 2/17

# 2 Hardware description and setup

This section provides a description of the main components of this evaluation kit, giving instruction for a quick setup of the system.

#### 2.1 **EVAL-L5965** board

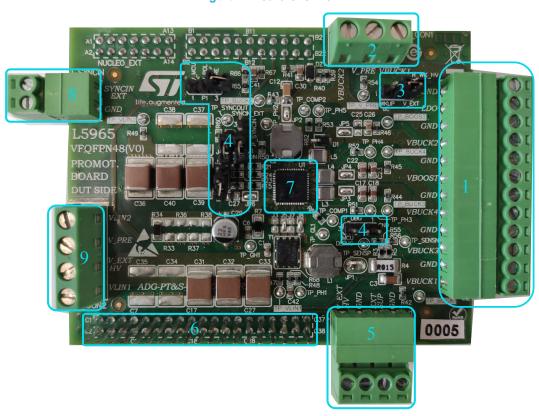

Figure 1. Board overview

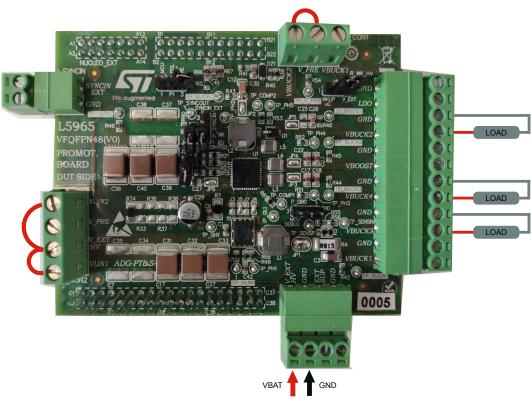

The motherboard is equipped with the following features (refer to the Figure 1, where the main parts are highlighted):

Table 1. Main parts description

| Part # | Description                                                          |

|--------|----------------------------------------------------------------------|

| 1      | Output screw connectors for BUCK's, BOOST and LDO                    |

| 2      | V_PRE selection connector                                            |

| 3      | WKUP jumper selection                                                |

| 4      | Main jumpers of control signals                                      |

| 5      | Screw connectors for main and auxiliary power supply (VBAT1, EXTSUP) |

| 6      | Connectors for SPI and auxiliary signals                             |

| 7      | Device area                                                          |

| 8      | Screw connector for SYNCIN                                           |

| 9      | VLIN1 and VLIN2 selection connector                                  |

UM3229 - Rev 1 page 3/17

#### 2.1.1 Power supply section

The board provides two main power supply inputs V\_EXT\_HV and EXTSUP:

- EXTSUP is intended to supply the VREG internal regulator to improve efficiency (optional)

- V EXT HV is intended to supply the VBAT1 pin of the device, the pre-BUCK1 and external HS MOS

The VREG is normally supplied directly from VBAT1 pin, in case is needed in can be supplied by EXTSUP. To make this transition happened is enough to provide a voltage higher than a threshold (typically 4.6 V) on EXTSUP pin.

The Figure 2 shows the schematic diagram of V\_EXT\_HV and EXTSUP connectors. The main component is the screw connector J1 necessary to provide voltages to the circuit. They are also equipped with a separated GND terminal for each supply. Capacitors C5 and C6 reduce the voltage fluctuations. V\_EXT\_HV is also present in other sections of the board to provide it as an alternative input for each regulator. This option is necessary to test a regulator independently without the influence of the previous one. The R7 resistor works as a jumper to connect or disconnect the EXTSUP supplies from the device. Anyway, the default option is to keep it connected through the resistor.

V EXT HV VBAT1 2 2 3 **EXTSUP** 3 EXSUP 4 0R R7 C6 C5 J1100nF 100nF

Figure 2. VBAT schematic circuit section

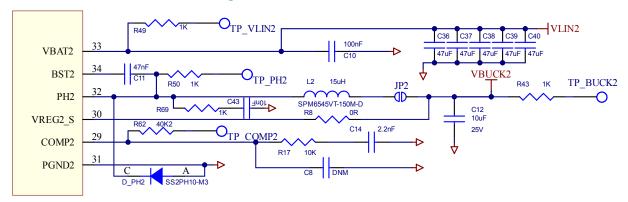

The board provide all the necessary external components and compensation network for the whole power supplies. In the Figure 3 it is reported the schematic view for BUCK2 in which are reported the external components and the external network. For other regulators like BUCK3 or BUCK4 the compensation network is not required because is internally implemented.

Figure 3. BUCK2 schematic circuit

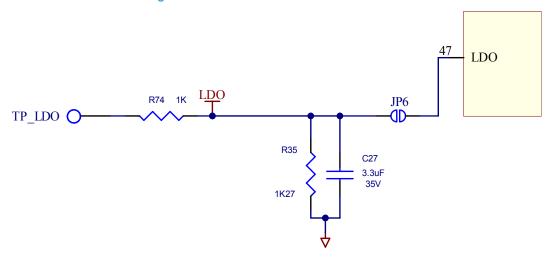

The Figure 4 shows the minimum load required by the linear regulator LDO, similar idea is applied to both linear regulators present in the device VREF and LDO. The minimum load is related to the spec requirement of a minimum current mainly for stability purposes.

UM3229 - Rev 1 page 4/17

Figure 4. LDO schematic circuit section detail

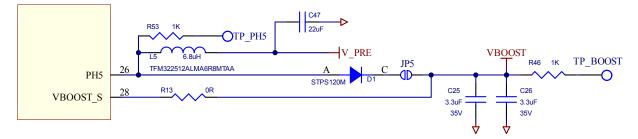

The Figure 5 shows the schematic section of BOOST converter. The main external components required are the inductor L5 that have to be chosen coherently with the maximum current required, the diode D1 and the output capacitor  $C_{out}$  obtained with two equal capacitors in parallel C25 and C26.

Figure 5. BOOST schematic circuit section

UM3229 - Rev 1 page 5/17

#### 2.1.2 VLINE connectors

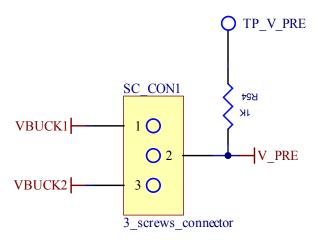

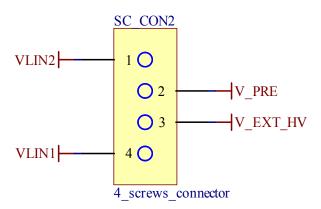

The Figure 6 and Figure 7 show the schematic section for the two connectors, SC\_CON1 and SC\_CON2, that select the input voltages for the different regulators.

Figure 6. SC\_CON1 schematic circuit section

To select the BUCK1 as pre-regulator is needed to insert an external cable shorting the SC\_CON1 connector terminal 1 and 2. Instead, shorting terminal 2 and 3 selects the BUCK2 as pre-regulator. V\_PRE is the input voltage for all the post-regulators BUCK3, BUCK4 and BOOST.

Figure 7. SC\_CON2 schematic circuit section

The SC\_CON2 allows to define the input voltage for the BUCK1 and BUCK2. To have both connected to battery (V\_EXT\_HV), is necessary to use an external cable that shorts terminals 1, 3, and 4 together. Instead, if only one is the pre-regulator, for example the BUCK1, terminal 3 and 4 shall be connected. To provide the input voltage to BUCK2, configured as post-regulator, terminal 1 and 2 shall be connected.

UM3229 - Rev 1 page 6/17

#### 2.1.3 Jumpers configuration

The Table 2 summarize functionality and configurations for the jumpers available on the board.

The V\_POL is the voltage used as supply for the digital pin pull-up, V\_MCU is a supply coming from micro board, VPRE is the supply voltage for post-regulators selected by SC\_CON1 between BUCK1 and BUCK2 output.

Table 2. Jumpers configuration

| Jumper   | Configuration setup                     |                                            |  |

|----------|-----------------------------------------|--------------------------------------------|--|

|          | Position 1-2                            | Position 2-3                               |  |

| P1       | V_POL shorted with V_MCU                | V_POL shorted with VPRE                    |  |

| P2       | WKUP pin shorted with a micro signal    | WKUP pin shorted with V_EXT_HV             |  |

| P_DBG    | DEBUG pin shorted with GND              | DEBUG pin shorted with a micro signal      |  |

| P_SYNCIN | SYNCIN pin shorted with a micro signal  | SYNCIN pin shorted with J_SYNCIN connector |  |

|          | Close                                   | Open                                       |  |

| J4       | SYNCOUT pin shorted with a micro signal | SYNCOUT not connected with micro pin       |  |

| J24      | FAULT pin pull-up to V_POL present      | FAULT pin pull-up to V_POL not present     |  |

UM3229 - Rev 1 page 7/17

### 2.2 Typical application

The Figure 8 shows an example of board standard usage. In details are highlighted the power supply connections VBAT and GND.

The demonstration board is already set to allow the evaluation of the PMIC features. To run the device properly is needed to connect a compatible voltage to the connector J1 (V\_EXT\_HV), to short terminal 2 (V\_PRE) with terminal 3 (BUCK2) for connector SC\_CON1 and to short terminal 3 (V\_EXT\_HV), 1 (VLIN2) and 4 (VLIN1) together for connector SC\_CON2.

BUCK2, BUCK3, BUCK4, BOOST and VREF are switched on automatically.

In the example are connected just 3 loads but in real context application can be used more loads, also more than one load for each regulator.

Figure 8. Board application

UM3229 - Rev 1 page 8/17

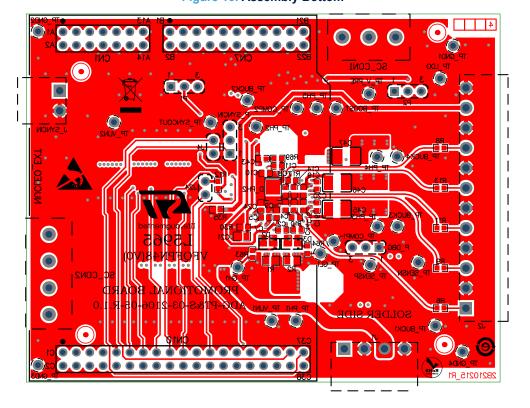

#### 2.3 Layout

Figure 9. Assembly Top

UM3229 - Rev 1 page 9/17

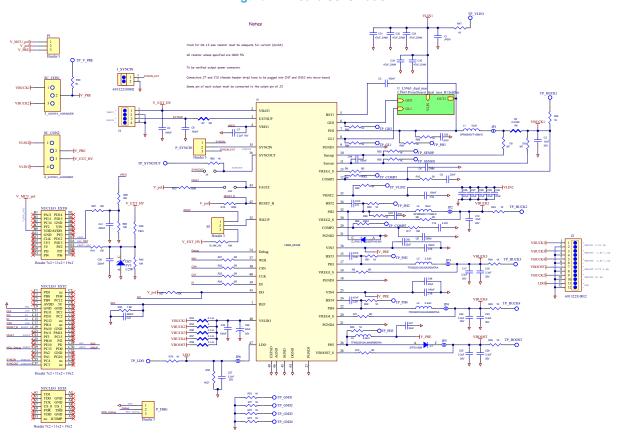

### 2.4 Schematic

Figure 11. Board schematic

UM3229 - Rev 1 page 10/17

### 3 Programming option

The L5965 mounted on this demonstration board is programmed as follows (refer to product datasheet for more information).

2 1 0 15 14 13 12 11 10 Reset activation = 000 Device identification = 000000 OTP\_WD\_REC\_en = 0 BUCK1 CFG = 000 CRC 8 EnBUCK4 = 1 Prim Id = 110 Non Prim Seald = 111 BUCK2 CFG =01010 EnBUCK3 = 1 CRC SeqId BUCK4 = 010 Seqld BUCK3 = 001 BUCK4 CFG = 001 OvRst EN = 1 BUCK3 CFG = 000 CRC 11 Seqld LDO = 111 SeqId BOOST = 011 EnLDO =1 EnBOOST = LDO CFG = 1101 CRC WDG CFG = 10 12 USR Area Protection = 111 Seqld VREF = 100 PowrOn Delay = 01 EnVREF = 1 VREF CFG = 10 CRC

Figure 12. OTP bit mapping

BUCK2 is the main regulator and provides 3.3 V at 2.6 A and 0.4 MHz. This is the pre-regulator that supplies the others. BUCK3 is the second regulator to switch on, and provides 2 V. BUCK4 is the third regulator, supplying 1.8 V. The fourth regulator to start is the BOOST providing 5 V and the latest one is the VREF providing 3.3 V.

The reset is released after the power-good of the main regulator (BUCK2). In case of failures, the RESET\_B signal does not affect the state machine, then the regulator can still be evaluated in this condition. Also an overvoltage cannot assert a reset. All these regulators turn on with a delay of 2 ms among them.

BUCK1 and LDO should be enabled by SPI. Once enabled, BUCK1 provides 5 V and the LDO supplies 1.3 V at 600 mA.

A watchdog is not required to operate the PMIC and rewriting OTP programming is forbidden.

UM3229 - Rev 1 page 11/17

### 4 Information on board use

This evaluation board is intended for the following uses:

- Engineering development

- Demonstrations

- Evaluation purposes only

It is not considered by STMicroelectronics to be a finished end-product fit for general consumer use. The people who handle one or more products must have electronics training and must observe good engineering standard practices.

For this reason, the goods being provided are not intended to be complete in terms of required design, marketing, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the purpose of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives or other related directives.

UM3229 - Rev 1 page 12/17

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 11-Aug-2023 | 1       | Initial release. |

UM3229 - Rev 1 page 13/17

## **Contents**

| 1  | Pref   | ce2                               |  |

|----|--------|-----------------------------------|--|

| 2  | Hard   | ware description and setup3       |  |

|    | 2.1    | EVAL-L5965 board                  |  |

|    |        | <b>2.1.1</b> Power supply section |  |

|    |        | <b>2.1.2</b> VLINE connectors     |  |

|    |        | 2.1.3 Jumpers configuration       |  |

|    | 2.2    | Typical application8              |  |

|    | 2.3    | Layout9                           |  |

|    | 2.4    | Schematic                         |  |

| 3  | Prog   | ramming option11                  |  |

| 4  | Info   | nation on board use               |  |

| Re | vision | nistory                           |  |

## **List of tables**

| Table 1. | Main parts description    |

|----------|---------------------------|

| Table 2. | Jumpers configuration     |

| Гable 3. | Document revision history |

UM3229 - Rev 1 page 15/17

# **List of figures**

| Board overview                       |

|--------------------------------------|

| VBAT schematic circuit section       |

| BUCK2 schematic circuit              |

| LDO schematic circuit section detail |

| BOOST schematic circuit section      |

| SC_CON1 schematic circuit section    |

| SC_CON2 schematic circuit section    |

| Board application                    |

| Assembly Top                         |

| Assembly Bottom                      |

| Board schematic                      |

| OTP bit mapping                      |

|                                      |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

UM3229 - Rev 1 page 17/17