WUXI SIMINUO TECHNOLOGY CO.,LTD

# SER1.54-C

#### **OLED MODULE USER MANUAL**

Address: No.7 Yanqiao Road, Yanqiao Street, huishan District,

Wuxi City, Jiangsu Province

Zipcode:214171

Tel: 0510-68065297/18662277330

Fax: 0510-68065297

Http://www.simair-lcd.com

E-mail: 308183018@qq.com, simair\_lcd@163.com

地址:江苏省无锡市惠山区堰桥街道堰桥路7号

邮编:214171

电话:0510-68065297/18662277330

传真:0510-68065297

网址:www.simair-lcd.com

WUXI SIMINUO TECHNOLOGY CO.,LTD

### 1. FUNCTIONS & FEATURES

#### **Features**

- 128X64 dots

- Font Color: YELLOW/WHITE/GREEN

- Driver IC:SSD1309

- 4-wire SPI,I2C

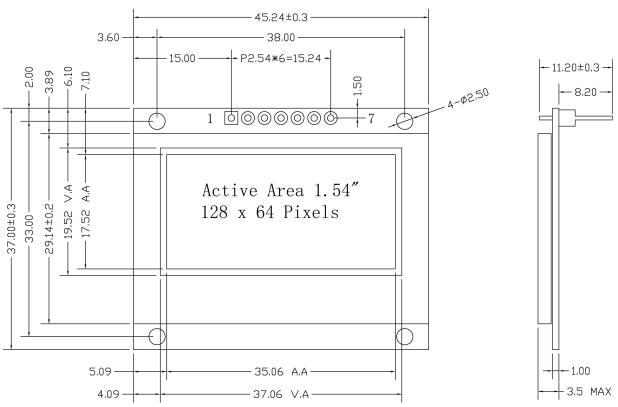

### 2. MECHANICAL SPECIFICATIONS

| ITEM           | SPECIFICATIONS           | UNIT |

|----------------|--------------------------|------|

| Module Size    | 45.24L×37.0W×3.5 (max) H | mm   |

| View Area      | 37.06×19.52              | mm   |

| Effective Area | 128×64                   | dots |

| Dot Size       | 0.274×0.274              | mm   |

| Dot Pitch      | 0.258×0.258              | mm   |

#### 3. EXTERNAL DIMENSIONS

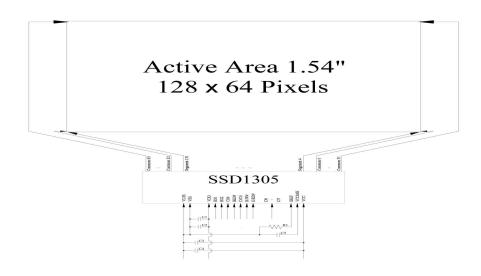

### 4. BLOCK DIAGRAM

WUXI SIMINUO TECHNOLOGY CO.,LTD

### 5. POWER SUPPLY

### 6. PIN DESCRIPTION

### 6.1 CN1 PIN DESCRIPTION

4-SPI: (R2:USE; R1,R3:NO USE)

| ITEM | SYMBOL | LEVEL | FUNCTION                 |  |  |  |  |  |

|------|--------|-------|--------------------------|--|--|--|--|--|

| 1    | GND    | 0V    | Power Ground             |  |  |  |  |  |

| 2    | VDD    | +3.3V | Power Supply For Logic   |  |  |  |  |  |

| 3    | SCLK   | H/L   | Serial Clock signal      |  |  |  |  |  |

| 4    | SDIN   | H/L   | Serial Data Input signal |  |  |  |  |  |

| 5    | /RES   | H/L   | Active LOW Reset signal. |  |  |  |  |  |

| 6    | D/C    | H/L   | H: Data L: Command       |  |  |  |  |  |

| 7    | /CS    | L     | Chip Select              |  |  |  |  |  |

**I2C Interface:** (R1,R3:USE; R2:NO USE)

### WUXI SIMINUO TECHNOLOGY CO.,LTD

| ITEM | SYMBOL   | LEVEL | FUNCTION                       |  |  |  |  |

|------|----------|-------|--------------------------------|--|--|--|--|

| 1    | GND      | 0V    | Power Ground                   |  |  |  |  |

| 2    | VDD      | +3.3V | Power Supply For Logic         |  |  |  |  |

| 3    | SCL      | H/L   | Serial Clock signal.           |  |  |  |  |

| 4    | SDA      | H/L   | Serial Data input signal       |  |  |  |  |

| 5    | /RST     | H/L   | Active LOW Reset signal.       |  |  |  |  |

| 6    | SA0(D/C) | H/L   | Slave Address Selection signal |  |  |  |  |

| 7    | /CS      | L     | Chip Select                    |  |  |  |  |

#### **Absolute Maximum Ratings**

| Parameter                  | Symbol | Min | Max | Unit                   | Notes |

|----------------------------|--------|-----|-----|------------------------|-------|

| Supply Voltage for Logic   | Vdd    | 2.4 | 3.6 | V                      | 1, 2  |

| Supply Voltage for Display | Vcc    | 0   | 15  | V                      | 1, 2  |

| Operating Temperature      | Тор    | -30 | 85  | $^{\circ}\!\mathbb{C}$ | -     |

| Storage Temperature        | Tst    | -40 | 90  | $^{\circ}\!\mathbb{C}$ | -     |

Note 1: All the above voltages are on the basis of "VSS = 0V".

Note 2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur. Also, for normal operations, it is desirable to use this module under the conditions according to Section 3. "Optics & Electrical Characteristics". If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate.

### 9. ELECTRICAL CHARACTERISTICS

| Items                       | Symbol   | Condition         | Min     | TYP | Max     | Unit |

|-----------------------------|----------|-------------------|---------|-----|---------|------|

| Operating Temperature Range | Тор      | Absolute Max      | -40     | _   | +85     | °C   |

| Storage Temperature Range   | Tst      | Absolute Max      | -40     | _   | +90     | °C   |

|                             |          |                   |         |     |         |      |

| Supply Voltage              | Vdd      |                   | 3.0     | 3.3 | 3.6     | V    |

| Supply Current (logic)      | Idd      | Ta=25°C, VDD=3.3V | _       | 180 | 300     | μΑ   |

| Supply Current (display)    | ICC      | 50% ON, VDD=3.3V  | _       | 62  | 70      | mA   |

|                             | icc      | 100% ON, VDD=3.3V | _       | 113 | 120     | mA   |

| Sleep Mode Current          | IDD+ICCS |                   |         | 3   | 15      |      |

|                             | LEEP     |                   | _       | 3   | 15      | μΑ   |

| "H" Level input             | Vih      |                   | 0.8*VDD |     | VDD     | V    |

| "L" Level input             | Vil      |                   | VSS     | _   | 0.2*VDD | V    |

| "H" Level output            | Voh      |                   | 0.9*VDD | _   | VDD     | V    |

| "L" Level output            | Vol      |                   | VSS     | _   | 0.1*VDD | V    |

#### WUXI SIMINUO TECHNOLOGY CO.,LTD

#### **Optical Characteristics**

| Item                   | Symbol | Condition        | Min.   | Тур. | Max. | Unit  |

|------------------------|--------|------------------|--------|------|------|-------|

| Viewing Angle – Top    | AV     |                  | _      | 80   | _    | 0     |

| Viewing Angle – Bottom | AV     |                  | _      | 80   |      | 0     |

| Viewing Angle – Left   | AH     |                  | _      | 80   | _    | 0     |

| Viewing Angle – Right  | AH     |                  | _      | 80   |      | 0     |

| Contrast Ratio         | Cr     |                  | 2000:1 | _    | _    | _     |

| Response Time (rise)   | Tr     | <u> </u>         | _      | 10   |      | us    |

| Response Time (fall)   | Tf     | <u> </u>         | _      | 10   | _    | us    |

| Brightness             |        | 50% checkerboard | 100    | 120  |      | cd/m2 |

| Lifetime               |        | Ta=25°C, 50%     | 10,000 |      |      | Hrs   |

| Effetime               |        | checkerboard     | 10,000 |      |      | 1113  |

Note: Lifetime at typical temperature is based on accelerated high-temperature operation. Lifetime is tested at average 50% pixels on and is rated as Hours until Half-Brightness. The Display OFF command can be used to extend the lifetime of the display.

Luminance of active pixels will degrade faster than inactive pixels. Residual (burn-in) images may occur. To avoid this, every pixel should be illuminated uniformly.

#### Built-in SSD1305 controller.

#### **Instruction Table**

|                   |     |                 |     |    | Coc                                     | le |    |    | Description |    |                                                                                                                                     |              |

|-------------------|-----|-----------------|-----|----|-----------------------------------------|----|----|----|-------------|----|-------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Instruction       | D/C | D/C HEX DB7 DB6 |     |    | DB6   DB5   DB4   DB3   DB2   DB1   DB0 |    |    |    |             |    | Description                                                                                                                         | value        |

| Set Lower Column  | 0   | 00~ 0F          | 0   | 0  | 0                                       | 0  | хз | X2 | X1          | хо | Set the lower nibble of the column start address register for Page                                                                  | 0            |

| Start Address     |     |                 |     |    |                                         |    |    |    |             |    | Addressing Mode.                                                                                                                    |              |

| Set Higher        | 0   | 10~1F           | 0   | 0  | 0                                       | 1  | ХЗ | X2 | X1          | XO | Set the higher nibble of the column start address register for Page                                                                 | 0            |

| Column Start      |     |                 |     |    |                                         |    |    |    |             |    | Addressing Mode.                                                                                                                    |              |

| Address           |     |                 |     |    |                                         |    |    |    |             |    |                                                                                                                                     |              |

| Set Memory        | 0   | 20              | 0   | 0  | 1                                       | 0  | 0  | 0  | 0           | 0  | A[1:0] = 00b, Horizontal Addressing Mode                                                                                            |              |

| Addressing Mode   |     | A[1:0]          | *   | *  | *                                       | *  | *  | *  | A1          | A0 | A[1:0] = 01b, Vertical Addressing Mode                                                                                              | 10b          |

|                   |     |                 |     |    |                                         |    |    |    |             |    | A[1:0] = 10b, Page Addressing Mode                                                                                                  |              |

|                   | -   |                 |     | _  |                                         |    |    |    | _           |    | A[1:0] = 11b, Invalid                                                                                                               |              |

| Set Column        | 0   | 21              | 0   | 0  | 1                                       | 0  | 0  | 0  | 0           | 1  | Setup column start and end address<br>A[7:0]: Column start address. Range: 0-131d                                                   | 0            |

| Address           |     | A[7:0]          | A7  | A6 | A5                                      | A4 | A3 | A2 | A1          | A0 | B[7:0]: Column start address. Range: 0-131d                                                                                         | 131d         |

|                   |     | B[7:0]          | B7  | В6 | B5                                      | B4 | В3 | B2 | B1          | B0 |                                                                                                                                     | 1310         |

| Set Page Address  | 0   | 22              | 0   | 0  | 1                                       | 0  | 0  | 0  | 1           | 0  | Setup page start and end address                                                                                                    |              |

|                   |     | A[2:0]          | *   |    | *                                       | *  | *  | A2 | A1          | A0 | A[2:0]: Page start address. Range: 0-7d B[2:0]: Page end address. Range: 0-7d                                                       | 0<br>7d      |

|                   |     | B[2:0]          | *   | *  | *                                       | *  | *  | B2 | B1          | В0 |                                                                                                                                     |              |

| Set Display Start | 0   | 40~7F           | 0   | 1  | X5                                      | X4 | ХЗ | X2 | X1          | хо | Set display RAM display start line register from 0-63d.                                                                             | 0            |

| Line              |     |                 |     |    |                                         |    |    |    |             |    |                                                                                                                                     |              |

| Set Contrast      | 0   | 81              | 1   | 0  | 0                                       | 0  | 0  | 0  | 0           | 1  | Double byte command to select 1 out of 256 contrast steps. Contrast                                                                 |              |

| Control           |     | A[7:0]          | A7  | A6 | A5                                      | A4 | A3 | A2 | A1          | A0 | increases as the value increases.                                                                                                   | 0x80         |

| Set Brightness    | 0   | 82              | 1   | 0  | 0                                       | 0  | 0  | 0  | 1           | 0  | Double byte command to select 1 out of 256 brightness steps.                                                                        |              |

|                   |     | A[7:0]          | A7  | A6 | A5                                      | A4 | A3 | A2 | A1          | A0 | Brightness increases as the value increases.                                                                                        | 0x80         |

| Set Look-Up Table | 0   | 91              | 1   | 0  | 0                                       | 1  | 0  | 0  | 0           | 1  | Set current drive pulse width of Bank 0, Color A, B and C.                                                                          |              |

|                   |     | X[5:0]          | *   | *  | X5                                      | X4 | Х3 | X2 | X1          | XO | Bank 0: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.                                                                      | 0x31         |

|                   |     | A[5:0]          | *   | *  | A5                                      | A4 | A3 | A2 | A1          | A0 | Color A: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.                                                                     | 0x3F         |

|                   |     | B[5:0]          | *   | *  | B5                                      | B4 | В3 | B2 | B1          | В0 | Color B: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.<br>Color C: X[5:0] = 31 to 63. Pulse width set to 32 to 64 clocks.  | 0x3F<br>0x3F |

|                   |     | C[5:0]          | *   | *  | C5                                      | C4 | C3 | C2 | C1          | CO | Note: Color D pulse width is fixed at 64 clocks.                                                                                    | UXSI         |

| Set Bank Color of | 0   | 92              | 1   | 0  | 0                                       | 1  | 0  | 0  | 1           | 0  | Sets the bank color of Bank1~Bank16 to any one of the 4 colors A.B.C.                                                               |              |

| Bank1 to Bank16   | "   | A[7:0]          | A7  | A6 | A5                                      | A4 | A3 | A2 | A1          | AO | and D.                                                                                                                              |              |

| (Page 0)          |     | B[7:0]          | B7  | В6 | B5                                      | В4 | B3 | B2 | B1          | BO | A[1:0]: 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK1.                                                                   |              |

| (i age o)         |     | C[7:0]          | C7  | C6 | C5                                      | C4 | C3 | C2 | C1          | CO | A[3:2]: 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK2.                                                                   |              |

|                   |     | D[7:0]          | D7  | D6 | D5                                      | D4 | D3 | D2 | D1          | DO |                                                                                                                                     |              |

|                   |     | 5[7.0]          | ",  | 50 | 55                                      | 54 | 53 | 02 | "           | 50 |                                                                                                                                     |              |

|                   |     |                 |     |    |                                         |    |    |    |             |    |                                                                                                                                     |              |

|                   |     |                 |     |    |                                         |    |    |    |             |    | D[5:4] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK15.                                                                 |              |

| Set Bank Color of | 0   | 93              | 1   | 0  | 0                                       | 1  | 0  | 0  | 1           | 1  | D[7:6]: 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK16.  Sets the bank color of Bank17~Bank32 to any one of the 4 colors |              |

| Ser gauk colot of | l u | 93              | _ 1 | U  | U                                       | 1  | U  | U  |             | 1  | Sets the bank color of bank17 bank32 to any one of the 4 colors                                                                     | 1            |

### WUXI SIMINUO TECHNOLOGY CO.,LTD

| Bank17 to Bank32   | Ι | A[7.0] | A7 | A6   | A5    | A4 | А3  | 4.2      | A1 | A0  | A,B,C, and D.                                                                                                                 |       |

|--------------------|---|--------|----|------|-------|----|-----|----------|----|-----|-------------------------------------------------------------------------------------------------------------------------------|-------|

|                    |   | A[7:0] | B7 | B6   | B5    | B4 | B3  | A2<br>B2 | B1 | BO  | A(1:0): 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK17.                                                            |       |

| (Page 1)           |   | B[7:0] |    |      |       |    |     |          |    |     | A[3:2] : 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK17.                                                           |       |

|                    |   | C[7:0] | C7 | C6   | C5    | C4 | C3  | C2       | C1 | CO  | A[3.2] . 000, 010, 100, 01 110 101 Color - A, b, C, 01 0 01 DANKED.                                                           |       |

|                    |   | D[7:0] | D7 | D6   | D5    | D4 | D3  | D2       | D1 | D0  |                                                                                                                               |       |

|                    |   |        |    |      |       |    |     |          |    |     | ,                                                                                                                             |       |

|                    |   |        |    |      |       |    |     |          |    |     | D[5:4]: 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK31.                                                            |       |

|                    |   |        |    |      |       |    |     |          |    |     | D[7:6]: 00b, 01b, 10b, or 11b for Color = A, B, C, or D of BANK32.                                                            |       |

| Set Segment        | 0 | A0/A1  | 1  | 0    | 1     | 0  | 0   | 0        | 0  | X0  | X[0] = 0; Column address 0 is mapped to SEG0                                                                                  | 0     |

| Remap              |   |        |    |      |       |    |     |          |    |     | X[0] = 1; Column address 131 is mapped to SEG0                                                                                |       |

| Entire Display ON  | 0 | A4/A5  | 1  | 0    | 1     | 0  | 0   | 1        | 0  | хо  | X[0] = 0; Resume RAM content display. Output follows RAM content.<br>X[0] = 1; Entire display ON. Output ignores RAM content. | 0     |

| Set Normal/        | 0 | A6/A7  | 1  | 0    | 1     | 0  | 0   | 1        | 1  | XO  | X[0] = 0; Normal display.                                                                                                     | 0     |

| Inverse Display    |   |        |    |      |       |    |     |          |    |     | X[0] = 1; Inverse display.                                                                                                    |       |

| Set Multiplex      | 0 | A8     | 1  | 0    | 1     | 0  | 1   | 0        | 0  | 0   | Set MUX ratio to N+1 MUX                                                                                                      | 64    |

| Ratio              |   | A[5:0] | *  | *    | A5    | A4 | А3  | A2       | A1 | A0  | N=A[5:0]; from 16MUX to 64MUX (0 to 14 are invalid)                                                                           |       |

| Dim mode setting   | 0 | AB     | 1  | 0    | 1     | 0  | 1   | 0        | 1  | 1   | A[3:0] = reserved. Set as 0000b                                                                                               |       |

| Dill mode setting  | " | A[3:0] | *  | *    | *     | *  | A3  | A2       | A1 | A0  | B[7:0] = Set contrast for BANKO. Range 0-255d. Refer to command                                                               |       |

|                    |   | B[7:0] | В7 | В6   | B5    | В4 | B3  | B2       | B1 | BO  | 81h.                                                                                                                          |       |

|                    |   | C[7:0] | C7 | C6   | C5    | C4 | C3  | C2       | C1 | CO  | C[7:0] = Set brightness for color bank. Range 0-255d. Refer to                                                                |       |

|                    |   | C[7.0] | ۲, | _ C6 | L C S | C4 | CS  | L CZ     | CI | CU  | command 82h.                                                                                                                  |       |

| Master             | 0 | AD     | 1  | 0    | 1     | 0  | 1   | 1        | 0  | 1   | Selects external VCC supply                                                                                                   |       |

| configuration      |   | AE     | 1  | 0    | 0     | 0  | 1   | 1        | 1  | 0   |                                                                                                                               | AEh   |

| Set Display ON/    | 0 | AC/    | 1  | 0    | 1     | 0  | 1   | 1        | A1 | A0  | ACh = Display ON in dim mode                                                                                                  | AEh   |

| OFF                |   | AE/    |    |      |       |    |     |          |    |     | AEh = Display OFF (sleep mode)                                                                                                |       |

|                    |   | AF     |    |      |       |    |     |          |    |     | AFh = Display ON in normal mode                                                                                               |       |

| Set Page Start     | 0 | B0~B7  | 1  | 0    | 1     | 1  | 0   | X2       | X1 | xo  | Set GDRAM Page Start Address for Page Addressing Mode using X[2:0].                                                           |       |

| Address            | " | 50 57  | -  | •    | -     | _  | •   | /        |    | 1.0 | PAGE0~PAGE7                                                                                                                   |       |

| Set COM Output     | 0 | C0/C8  | 1  | 1    | 0     | 0  | хз  | 0        | 0  | 0   | X[3] = 0; Normal mode. Scan from COM0 to COM[N-1]                                                                             | 0     |

| Scan Direction     | " | 00,00  | 1  | 1    | •     | •  | Α.σ | "        | "  | "   | X[3] = 1; Remapped mode. Scan from COM[N-1] to COM0                                                                           | _     |

| Set Display Offset | 0 | D3     | 1  | 1    | 0     | 1  | 0   | 0        | 1  | 1   | Set vertical shift by COM from 0~63.                                                                                          | 0     |

| Set Display Offset | " | A[5:0] | *  | *    | A5    | A4 | A3  | A2       | A1 | A0  | Set vertical shift by colvinoin o os.                                                                                         |       |

| Set Display Clock  | 0 | D5     | 1  | 1    | 0     | 1  | 0   | 1        | 0  | 1   | A(3:0) = Define the divide ratio of the display clocks.                                                                       | 0000b |

| Divide Ratio /     | " | A[7:0] | A7 | A6   | A5    | A4 | A3  | A2       | A1 | A0  | Divide ratio = A[3:0] +1                                                                                                      | 00000 |

| Oscillator         |   | A[7:0] | Α/ | Ab   | AS    | A4 | AS  | AZ       | A1 | AU  | A[7:4] = Set the Oscillator Frequency. Frequency increases with the                                                           | 0111b |

|                    |   |        |    |      |       |    |     |          |    |     | value of A[7:4]. Range 0000b~1111b.                                                                                           | 01110 |

| Frequency          | - |        | -  | _    | _     | _  | _   | -        | -  | -   |                                                                                                                               | 00    |

| Set Area Color     | 0 | D8     | 1  | 1    | 0     | 1  | 1   | 0        | 0  | 0   | X[5:4] = 00b; Monochrome mode<br>X[5:4] = 11b; Area Color mode                                                                | 00    |

| Mode ON/OFF &      |   | X[5:0] | 0  | 0    | X5    | Х4 | 0   | X2       | 0  | XO  | X[2] = 0 and X[0] = 0; Normal power mode                                                                                      | 00    |

| Low Power          |   |        |    |      |       |    |     |          |    |     | X[2] = 0 and $X[0] = 0$ , Normal power mode<br>X[2] = 1 and $X[0] = 1$ ; Set low power display mode                           | 00    |

| Display Mode       |   |        |    |      |       |    |     |          |    |     |                                                                                                                               |       |

| Set Pre-charge     | 0 | D9     | 1  | 1    | 0     | 1  | 1   | 0        | 0  | 1   | A[3:0] = Phase 1 period of up to 15 DCLK clocks. 0 is invalid.                                                                | 2h    |

|                    |   |        |    |      |       |    |     |          |    |     | A[7:4] = Phase 2 period of up to 15 DCLK clocks. 0 is invalid.                                                                | 2h    |

|                    |   |        |    |      |       |    |     |          |    |     |                                                                                                                               |       |

| Period             |   | A[7:0] | A7 | A6   | A5    | A4 | А3  | A2       | A1 | A0  |                                                                                                                               |       |

| Set COM pins       | 0 | DA     | 1  | 1    | 0     | 1  | 1   | 0        | 1  | 0   | X[4] = 0; Sequential COM pin configuration                                                                                    |       |

| Hardware           |   | X[5:4] | 0  | 0    | X5    | X4 | 0   | 0        | 1  | 0   | X[4] = 1; Alternative COM pin configuration                                                                                   | 1     |

| configuration      |   |        |    |      |       |    |     |          |    |     | X[5] = 0; Disable COM Left/Right remap                                                                                        |       |

| -                  |   |        |    |      |       |    |     |          | _  | 1   | X[5] = 1; Enable COM Left/Right remap                                                                                         | 1     |

| Set VCOMH          | 0 | DB     | 1  | 1    | 0     | 1  | 1   | 0        | 1  | 1   | A[5:2] = 0000b; VCOMH = ~0.43*VCC                                                                                             |       |

| Deselect Level     |   | A[5:2] | 0  | 0    | A5    | A4 | А3  | A2       | 0  | 0   | A[5:2] = 1101b; VCOMH = ~0.77*VCC                                                                                             | 1101  |

|                    |   |        |    | -    |       |    |     |          | -  | -   | A[5:2] = 1111b; VCOMH = ~0.83*VCC                                                                                             | -     |

| Enter Read         | 0 | E0     | 1  | 1    | 1     | 0  | 0   | 0        | 0  | 0   | Enter the Read/Modify/Write mode.                                                                                             |       |

| Modify Write       |   |        |    |      |       |    |     |          |    |     |                                                                                                                               |       |

Command for No Operation

For detailed instruction information, see SSD1305 datasheet.

#### MPU Interface

Exit Read Modify

mode NOP

#### Serial Interface

The serial interface consists of serial clock SCLK, serial data SDIN, D/C, and /CS.

D0 acts as SCLK and D1 acts as SDIN. D2 should be left open. D3~D7, E, and R/W should be connected to GND.

| Function      | /RD | /WR | /CS | D/C | D0 |

|---------------|-----|-----|-----|-----|----|

| Write Command | 0   | 0   | 0   | 0   | 1  |

| Write Data    | 0   | 0   | 0   | 1   | 1  |

SDIN is shifted into an 8-bit shift register on every rising edge of SCLK in the order of D7, D6,...D0. D/C is sampled on every eighth clock and the data byte in the shift register is written to the GDRAM or command register in the same clock.

Note: Read is not available in serial mode.

WUXI SIMINUO TECHNOLOGY CO.,LTD

#### **I2C** Interface

The I2C interface consists of a slave address bit SA0, I2C-bus data signal SDA, and I2C-bus clock signal SCL.

D1 and D2 can be tied together, and act as SDA. D0 acts as SCL. Both the data and clock signals must be connected to pull-up resistors. /RES is used to initialize the device.

Note: SA0 bit allows the device to have a slave address of either "0111100" or "0111101".

**Note:** Data and acknowledgement are sent through the SDA. The ITO track resistance and the pull-up resistance at SDA becomes a voltage potential divider. As a result, it may not be possible to attain a valid logic "0" level on SDA for the ACK signal. SDAIN must be connected, but SDAOUT may be disconnected and the ACK signal will be ignored on the I2C bus.

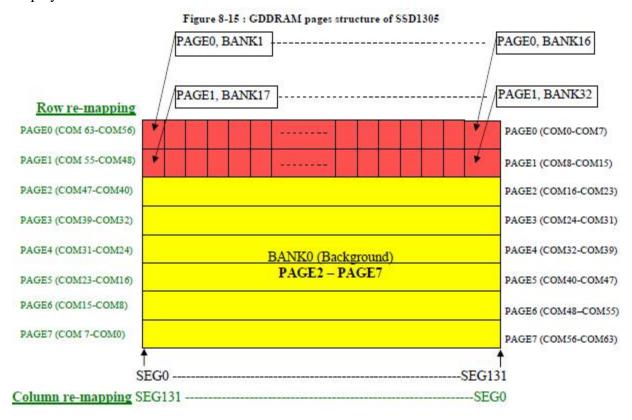

#### 12. Display Control Instructions

The GDDRAM is a bit mapped static RAM holding the bit pattern to be displayed. The size of the RAM is 132 x 64 bits and the RAM is divided into eight pages, from PAGE0 to PAGE7, as shown in Figure 8-15. In GDDRAM, PAGE0 and PAGE1 are belonged to area color section with resolution 132x16. PAGE2 to PAGE7 are used for monochrome 132x48 dot matrix display.

WUXI SIMINUO TECHNOLOGY CO.,LTD

When one data byte is written into GDDRAM, all the rows image data of the same page of the current column are filled (i.e. the whole column (8 bits) pointed by the column address pointer is filled.). Data bit D0 is written into the top row, while data bit D7 is written into bottom row as shown in Figure 8-16.

PAGE2

LSB D0

COM16

COM17

Each lattice represents one bit of image data

Figure 8-16: Enlargement of GDDRAM (No row re-mapping and column-remapping)

#### 14. DESIGN AND HANDING PRECAUTION

- 14.1 The LCD panel is made by glass. Any mechanical shock (eg. Dropping form high place) will damage the LCD module. Do not add excessive force on the surface of the display, which may cause the Display color change abnormally.

- 14.2 The polarizer on the LCD is easily get scratched. If possible, do not remove the LCD protective film until the last step of installation.

- 14.3 Never attempt to disassemble or rework the LCD module.

- 14.4 Only Clean the LCD with Isopropyl Alcohol or Ethyl Alcohol. Other solvents (eg. water) may damage the LCD.

- 14.5 When mounting the LCD module, make sure that it is free form twisting, warping and distortion.

- 14.6 Ensure to provide enough space(with cushion) between case and LCD panel to prevent external force adding on it, or it may cause damage to the LCD or degrade the display result

- 14.7 Only hold the LCD module by its side. Never hold LCD module by add force on the heat seal or TAB.

- 14.8 Never add force to component of the LCD module. It may cause invisible damage or degrade of the reliability.

- 14.9 LCD module could be easily damaged by static electricity. Be careful to maintain an optimum anti-static work environment to protect the LCD module.

- 14.10 When peeling of the protective film form LCD, static charge may cause abnormal display pattern. It is normal and will resume to normal in a short while.

#### WUXI SIMINUO TECHNOLOGY CO.,LTD

- 14.11 Take care and prevent get hurt by the LCD panel edge.

- 14.12 Never operate the LCD module exceed the absolute maximum ratings.

- 14.13 Keep the signal line as short as possible to prevent noisy signal applying to LCD module.

- 14.14 Never apply signal to the LCD module without power supply.

- 14.15 IC chip (eg. TAB or COG) is sensitive to the light. Strong lighting environment could possibly cause malfunction. Light sealing structure casing is recommend.

- 14.16 LCD module reliability may be reduced by temperature shock.

- 14.17 When storing the LCD module, avoid exposure to the direct sunlight, high humidity, high temperature or low temperature. They may damage or degrade the LCD module