# intel Migration Guidelines from Arria 10 to Stratix 10 for 10G **Ethernet Subsystem User Guide**

Home » Intel » intel Migration Guidelines from Arria 10 to Stratix 10 for 10G Ethernet Subsystem User Guide 🖺

### **Contents**

- 1 intel Migration Guidelines from Arria 10 to Stratix 10 for 10G Ethernet Subsystem

- 2 Migration Guidelines from Intel® Arria® 10 to Intel® Stratix® 10 for 10G Ethernet Subsystem

- 3 Supported Configurations for Intel Stratix 10 and Intel Arria 10 LL 10GbE MAC Designs

- **4 Clocking and Reset Infrastructure**

- 4.1 Intel Stratix 10 LL 10GbE MAC and Intel Stratix 10 1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel **FPGA IP Cores**

- **5 IP Register Mapping**

- 6 Signal Connectivity Differences between Intel Stratix 10 and Intel Arria 10 Ethernet Design Examples

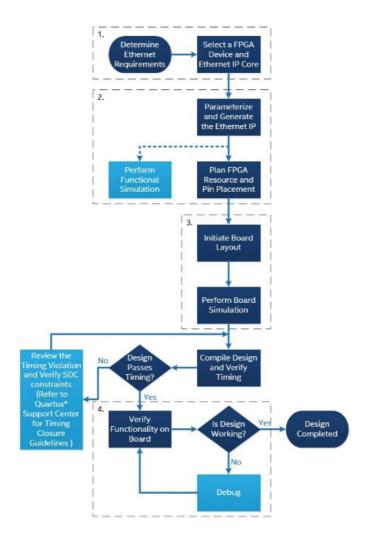

- 7 Migration Flow

- 8 Document Revision History for AN 808

- 9 Documents / Resources

- 10 Related Posts

intel Migration Guidelines from Arria 10 to Stratix 10 for 10G Ethernet Subsystem

# Migration Guidelines from Intel® Arria® 10 to Intel® Stratix® 10 for 10G Ethernet Subsystem

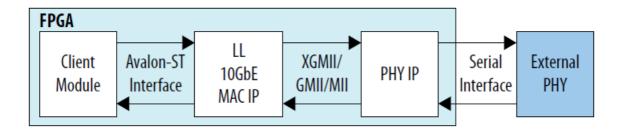

The Low Latency (LL) Ethernet 10G (10GbE) Media Access Controller (MAC) Intel® FPGA IP core includes Intel Stratix® 10 and Intel Arria® 10 design examples that are compliant with IEEE 802.3-2008 specifications. The interfaces between Intel Stratix 10 LL 10GbE MAC Intel FPGA IP core and physical interface (PHY) IP core are different compared to Intel Arria 10 LL 10GbE MAC Intel FPGA IP core with PHY IP core.

These migration guidelines are meant for those are familiar with Intel Arria 10 LL 10GbE MAC Intel FPGA IP core. Use these migration guidelines if you want to migrate your Intel Arria 10 LL 10GbE MAC design to use Intel Stratix 10 devices.

# Intel Stratix 10 LL 10GbE MAC System

Comparison between Intel Stratix 10 and Intel Arria 10 Design Examples for LL 10GbE MAC Intel FPGA IP Core

| Design Exampl<br>e                     | MAC Variant | PHY                                                                       | Development K it                                                            | Intel Arria 10 | Intel Stratix 10 |

|----------------------------------------|-------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------|------------------|

| 10GBASE-R<br>Ethernet                  | 10G         | Native PHY (Su<br>pport L/H-tile Na<br>tive PHY for Inte<br>I Stratix 10) | Intel Arria 10/ Int<br>el Stratix 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Yes              |

| 1G/2.5G Ethern<br>et with 1588         | 1G/2.5G     | 1G/2.5G/5G/10<br>G<br>Multi-rate<br>Ethernet PHY                          | Intel Arria 10/ Int<br>el Stratix 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Yes              |

| 1G/2.5G/10G<br>Ethernet                | 1G/2.5G/10G | 1G/2.5G/5G/10<br>G<br>Multi-rate<br>Ethernet PHY                          | Intel Arria 10/ Int<br>el Stratix 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Yes              |

| 10GBASE-R<br>Register Mode<br>Ethernet | 10G         | Native PHY                                                                | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity                       | Yes            | Not available    |

| XAUI Ethernet                          | 10G         | XAUI PHY                                                                  | Intel Arria 10 GX<br>FPGA                                                   | Yes            | Not available    |

| 1G/10G Etherne t                       | 1G/10G      | 1G/10GbE and<br>10GBASE-KR P<br>HY                                        | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity                       | Yes            | Not available    |

| continued.                             |             |                                                                           |                                                                             |                |                  |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants the performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Other names and brands may be claimed as the property of others.

| Design Exampl<br>e                            | MAC Variant                  | РНҮ                                              | Development K                                         | Intel Arria 10 | Intel Stratix 10 |

|-----------------------------------------------|------------------------------|--------------------------------------------------|-------------------------------------------------------|----------------|------------------|

| 1G/10G Etherne<br>t with 1588                 | 1G/10G                       | 1G/10GbE and<br>10GBASE-KR P<br>HY               | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Not available    |

| 10M/<br>100M/1G/10G<br>Ethernet               | 10M/<br>100M/1G/10G          | 1G/10GbE and<br>10GBASE-KR P<br>HY               | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Not available    |

| 10M/<br>100M/1G/10G<br>Ethernet with 15<br>88 | 10M/<br>100M/1G/10G          | 1G/10GbE and<br>10GBASE-KR P<br>HY               | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Not available    |

| 1G/2.5G Ethern<br>et                          | 1G/2.5G                      | 1G/2.5G/5G/10<br>G<br>Multi-rate<br>Ethernet PHY | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Not available    |

| 10G USXGMII<br>Ethernet                       | 1G/2.5G/5G/10<br>G (USXGMII) | 1G/2.5G/5G/10<br>G<br>Multi-rate<br>Ethernet PHY | Intel Arria 10 GX<br>Transceiver Sign<br>al Integrity | Yes            | Not available    |

## Note:

You can access the listed design examples through the LL 10GbE MAC parameter editor in the Intel Quartus® Prime Pro Edition software.

## **Related Information**

- Low Latency Ethernet 10G MAC User Guide

- Intel Stratix 10 Low Latency Ethernet 10G MAC Design Example User Guide

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

# Supported Configurations for Intel Stratix 10 and Intel Arria 10 LL 10GbE MAC Designs

The following table lists all the possible Intel Stratix 10 and Intel Arria 10 Ethernet IP configurations.

Supported Configurations for Intel Arria 10 and Intel Stratix 10 Ethernet IP Configuration

| IP Core      |                     | Intel Arria 10        | Intel Stratix 10  |

|--------------|---------------------|-----------------------|-------------------|

| LL 10GbE MAC | Speed               | • 10G                 |                   |

|              |                     | • 1G/10G              |                   |

|              |                     | • 10M/100M/1G/10G     |                   |

|              |                     | • 1G/2.5G             |                   |

|              |                     | • 1G/2.5G/10G         |                   |

|              |                     | • 1G/2.5G/5G/10G (US) | (GMII interface)  |

|              |                     | • 10M/100M/1G/2.5G    |                   |

|              |                     | • 10M/100M/1G/2.5G/10 | OG .              |

|              | IEEE 1588v2 feature | • 10G                 | • 10G             |

|              |                     | • 1G/10G              | • 1G/10G          |

|              |                     | • 10M/100M/1G/10G     | • 10M/100M/1G/10G |

|              |                     | • 1G/2.5G             | • 1G/2.5G         |

|              |                     |                       | • 1G/2.5G/10G     |

| continued.   | '                   | ,                     |                   |

| IP Core                                               |                     | Intel Arria 10                                                                                                                        | Intel Stratix 10                                                                                              |

|-------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                                       | Speed               | <ul> <li>2.5G</li> <li>1G/2.5G</li> <li>1G/2.5G/10G (MGBASE-T PHY)</li> <li>1G/2.5G/5G/10G (USXGMII interface/NBASE-T FHY)</li> </ul> |                                                                                                               |

| 1G/2.5G/5G/10G Multi-rat<br>e Ethernet PHY            | IEEE 1588v2 feature | <ul><li>2.5G</li><li>1G/2.5G</li></ul>                                                                                                | <ul> <li>2.5G</li> <li>1G/2.5G</li> <li>1G/2.5G/10G</li> <li>Not supported for enabled SGMII mode.</li> </ul> |

|                                                       | SGMII Mode          | Not available                                                                                                                         | <ul><li>1G/2.5G</li><li>1G/2.5G/10G</li></ul>                                                                 |

| XAUI PHY                                              |                     | Available                                                                                                                             | Not available                                                                                                 |

| Intel Stratix 10 L-tile/H-tile Transceiver Native PHY |                     | Not available                                                                                                                         | Supported presets:  • 10GBASE-R  • 10GBASE-R 1588  • 10GBASE-R Low Late ncy  • 10GBASE-R with KR FEC          |

| Intel Arria 10 Transceiver Native PHY                 |                     | Supported presets:  • 10GBASE-R  • 10GBASE-R Register Mode  • 10GBASE-R Low Late ncy  • 10GBASE-R with KR FEC                         | Not available                                                                                                 |

| Intel Arria 10 1G/10GbE and 10GBASE-KR PHY            |                     | Available                                                                                                                             | Not available                                                                                                 |

| Intel Stratix 10 10GBASE-h                            | (R PHY              | Not available                                                                                                                         | Available                                                                                                     |

# **Clocking and Reset Infrastructure**

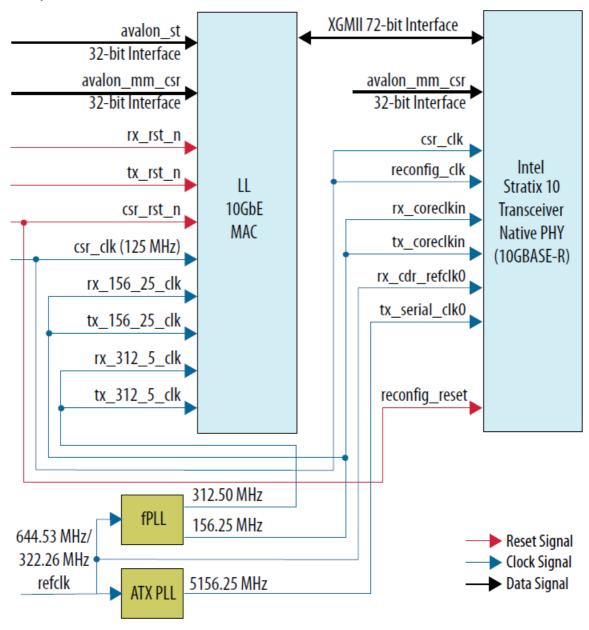

You can configure the Intel Stratix 10 Transceiver Native PHY IP core to implement 10GBASE-R PHY with the Ethernet-specific physical layer running at 10.3125 Gbps data rate as defined in Clause 49 of IEEE 802.3-2008 specification. This configuration provides an XGMII to LL 10GbE MAC Intel FPGA IP core and implements a single-channel 10.3125Gbps PHY for a direct connection to a small form-factor pluggable plus (SFP+) optical module using the small form-factor interface (SFI) electrical specification.

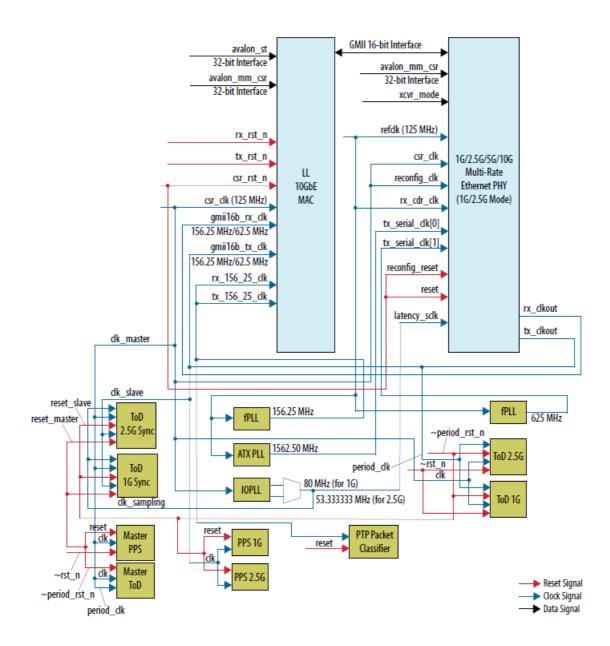

The following figure illustrates the migration from an Intel Arria 10 design to an Intel Stratix 10 design.

# Clocking and Reset Scheme for LL 10GbE MAC and Intel Stratix 10 Transceiver Native PHY in 10GBASE-R Design Example Interface

#### **Related Information**

AN795: Implementing Guidelines for 10G Ethernet Subsystem Using Low Latency 10G MAC IP Core in Arria 10 Devices

# Intel Stratix 10 LL 10GbE MAC and Intel Stratix 10 1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel FPGA IP Cores

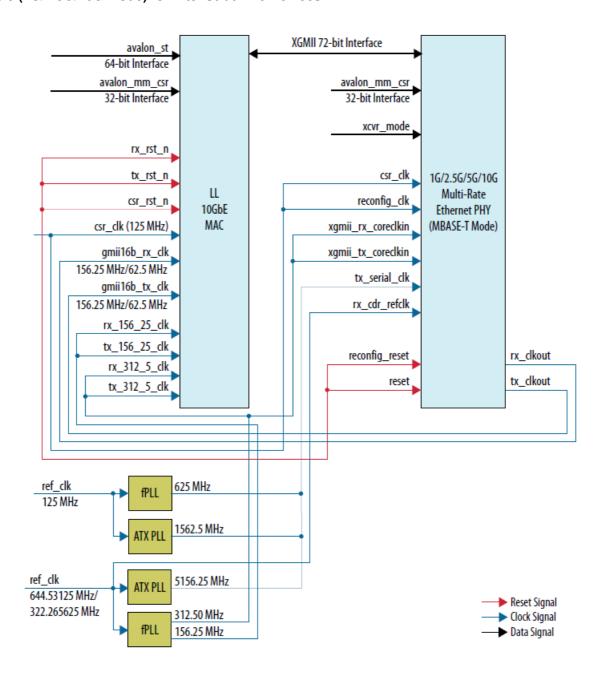

1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel FPGA IP core for Intel Stratix 10 devices provides GMII and XGMII to the LL 10GbE MAC Intel FPGA IP core. The 1G/2.5G/5G/10G Multi-rate Ethernet PHY IP core implements a single channel 1G/2.5G/5G/10Gbps serial PHY. The design provides a direct connection to 1G/2.5GbE dual speed SFP+ pluggable modules, MGBASE-T copper external PHY devices, or chip-to-chip interfaces. These IP cores support reconfigurable data rates.

The following figure illustrates then migration from an Intel Arria 10 design to a Intel Stratix 10 design.

# Clocking and Reset Scheme for LL 10GbE MAC and 1G/2.5G/5G/10G Multi-rate Ethernet PHY Design Example (1G/2.5G/10G Mode) for Intel Stratix 10 Deviecs

The following figure illustrates the latest clocking and reset scheme of the 1G/2.5G Ethernet with IEEE 1588v2 feature design example targeted on Intel Stratix 10 devices. There are differences between this solution and the version that was introduced in the Intel Arria 10 devices. Modification is needed when migrating design from the Intel Arria 10 devices to the Intel Stratix 10 devices.

Clocking and Reset Scheme for LL 10GbE MAC and 1G/2.5G/5G/10G Multi-rate Ethernet PHY Design Example (1G/2.5G Mode with IEEE 1588v2 Feature) for Intel Stratix 10 Devices

A new input clock port latency\_sclk is available in Intel Stratix 10 devices. This port is available when you turn on the Enable latency measurement ports parameter in the Intel Stratix 10 L/H-Tile Transceiver Native PHY IP core or the Enable IEEE 1588 Precision Time Protocol parameter in the 1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel FPGA IP core. This port is required for the deterministic latency measurement model for Intel Stratix 10 devices. For more information, refer to the Deterministic Latency Use Model chapter in Intel Stratix 10 L/H-Tile Transceiver PHY User Guide.

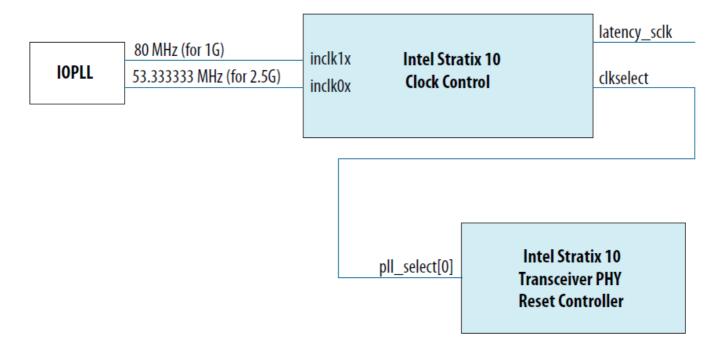

To connect an I/O phase-locked loop (IOPLL), add an Intel Stratix 10 Clock Control (stratix10\_clkctrl) IP from the IP Catalog. The IOPLL provides two sampling clocks in this design: 53.33 MHz for 2.5G mode and 80 MHz for 1G mode.

The following figure illustrates the connectivity details based on the 1G/2.5G Ethernet design.

Connectivity Diagram for 1G/2.5G Ethernet with 1588 Design for Intel Stratix 10 Devices

You must ensure that the inclk0x port connects to 2.5G sampling clock and the inclk1x port connects to 1G sampling clock. The output clock port of clock control becomes the latency\_sclk port. For design migration from the Intel Arria 10 devices to the Intel Stratix 10 devices, you can reuse the similar connectivity between the 1G/2.5G reconfiguration block and transceiver reset controller.

#### **Related Information**

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

- AN795: Implementing Guidelines for 10G Ethernet Subsystem Using Low Latency 10G MAC IP Core in Arria

10 Devices

- Intel Stratix 10 Clocking and PLL User Guide

## **IP Register Mapping**

The LL 10GbE MAC Intel FPGA IP core for Intel Stratix 10 devices uses the same register map as LL 10GbE MAC Intel FPGA IP core for Intel Arria 10 devices. The Multi-rate Ethernet PHY and 10GBASE-R PHY presets also use the same register map for both Intel Stratix 10 and Intel Arria 10 designs. The LL 10GbE MAC Intel FPGA IP core for Intel Stratix 10 devices still supports backward compatibility with 10GbE IP with 64-bit Avalon Memory-Mapped (MM) adapter.

#### **Related Information**

Low Latency Ethernet 10G MAC User Guide.

# Signal Connectivity Differences between Intel Stratix 10 and Intel Arria 10 Ethernet Design Examples

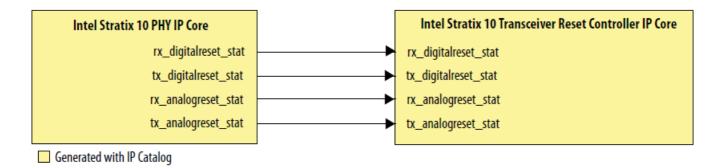

For LL 10GbE MAC Intel FPGA IP core, there are no new signals introduced for Intel Stratix 10 devices. There are new asynchronous reset status signals introduced in Intel Stratix 10 L/H-Tile Transceiver Native PHY IP Core. The differences apply to all Ethernet PHY IP cores, which include all variants of 1G/2.5G/5G/10G Multi-rate Ethernet PHY Intel FPGA IP cores and 10GBASE-R PHY Intel FPGA IP core.

Interface Signal Differences Between Intel Stratix 10 L/H-Tile Transceiver Native PHY/Multi-rate Ethernet PHY and Intel Arria 10 Transceiver Native PHY/Multi-rate Ethernet PHY

**Note:** < n > = The number of lanes.

| Intel Stratix 10 Interface Sig nals                   | Intel Arria 10 Interface Sign als                    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_analogreset_stat[ <n>-1 :0]</n>                    | Not available                                        | These reset status ports are newly introduced in Intel Stratix 10 devices only.                                                                                                                                                                                                                                                                                                                                          |

| rx_analogreset_stat[ <n>-1 :0]</n>                    | Not available                                        | Connect to the corresponding signal in the Tra nsceiver PHY Reset Controller IP core, which i mplements the appropriate reset sequence for the device.                                                                                                                                                                                                                                                                   |

| tx_digitalreset_stat[ <n>- 1:0]</n>                   | Not available                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| rx_digitalreset_stat[ <n>- 1:0]</n>                   | Not available                                        |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| latency_sclk                                          | Not available                                        | Latency measurement input reference clock. S ampling clock for measuring the latency of the transceiver application interface block (AIB) d atapath.  This port is available when the latency measur ement ports option in the Intel Stratix 10 L/H-T ile Transceiver Native PHY IP core or the IEEE 1588 Precision Time Protocol option in the 1G / 2.5G/5G/10G Multi-rate Ethernet PHY Intel F PGA IP core is enabled. |

| reconfig_address [log <sub>2</sub> <n><br/>+10:0]</n> | reconfig_address [log <sub>2</sub> <n>+9:<br/>0]</n> | Reconfiguration address signal connected to the reconfiguration block. Address bus that used to specify address to be accessed for both read and write operations.                                                                                                                                                                                                                                                       |

Interface Signal Differences Between Intel Stratix 10 Transceiver Reset Controller IP and Intel Arria 10 Transceiver Reset Controller IP

**Note:** <n> = The number of lanes.

| Intel Stratix 10 Interface Sig<br>nals | Intel Arria 10 Interface Sign als | Comments                                                                                                                                                                                                                  |

|----------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_analogreset_stat[ <n>-1 :0]</n>     | Not available                     | This is reset status signal from the Transceiver Native PHY IP Core. There is one tx_analogre set_stat per channel.  When asserted, reset sequence for TX PMA b egins. When deasserted, reset sequence for T X PMA ends.  |

| rx_analogreset_stat[ <n>-1 :0]</n>     | Not available                     | This is reset status signal from the Transceiver Native PHY IP Core. There is one rx_analogre set_stat per channel.  When asserted, reset sequence for RX PMA b egins.  When deasserted, reset sequence for RX PM A ends. |

| tx_digitalreset_stat[ <n>- 1:0]</n>    | Not available                     | This is reset status signal from the Transceiver Native PHY IP Core. There is one tx_digitalres et_stat per channel. When asserted, reset seq uence for TX PCS begins.                                                    |

| continued.                             |                                   |                                                                                                                                                                                                                           |

| Intel Stratix 10 Interface Sig      | Intel Arria 10 Interface Sign als | Comments                                                                                                             |

|-------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                     |                                   | When deasserted, reset sequence for TX PCS ends.                                                                     |

|                                     |                                   | This is reset status signal from the Transceiver Native PHY IP Core. There is one rx_digitalres et_stat per channel. |

| rx_digitalreset_stat[ <n>- 1:0]</n> | Not available                     | When asserted, reset sequence for RX PCS b egins. When deasserted, reset sequence for R X PCS ends.                  |

The following figure illustrates the connectivity of reset status signals for the Intel Stratix 10 Ethernet 10G subsystem design. This is applicable if you use either the Intel Stratix 10 L-tile/H-tile Native PHY IP core or the 1G/2.5G/5G/10G Multi-rate PHY Intel FPGA IP core.

## Reset Status Signals Connectivity Diagram for Intel Stratix 10 PHY IP Core and Reset Controller IP Core

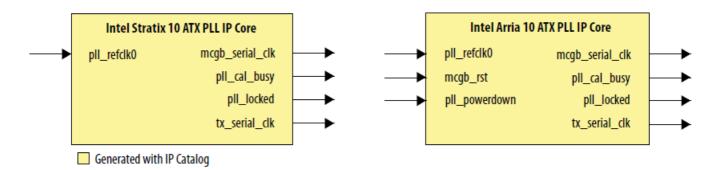

There are some changes to the ATX PLL and fPLL interface signals for the Intel Stratix 10 devices compared to the Intel Arria 10 devices. If you are migrating Ethernet designs from a Intel Arria 10 device to a Intel Stratix 10 device, remove the mcgb\_rst and pll\_powerdown reset signals because they are not available in Intel Stratix 10.

The following figure illustrates the difference between Intel Stratix 10 L-Tile/H-Tile ATX PLL and Intel Arria 10 ATX PLL.

Comparison between Interface Signals for Intel Stratix 10 L-Tile/H-Tile Transceiver ATX PLL and Intel Arria 10 Transceiver ATX PLL

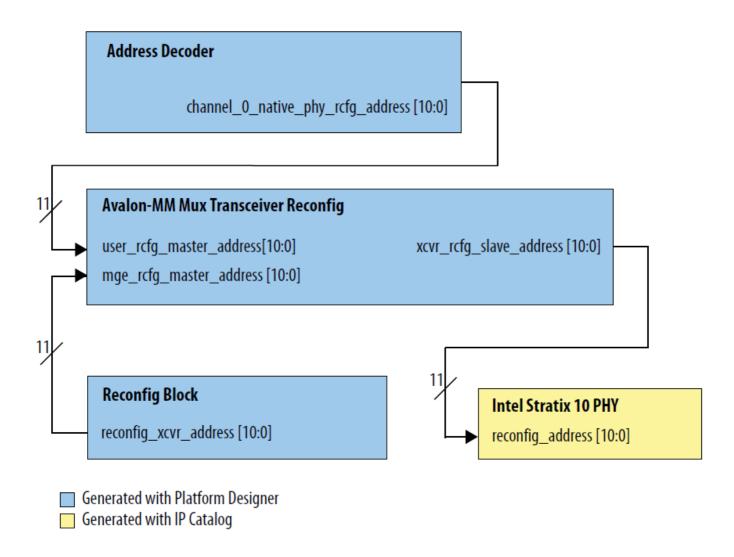

Another change on Intel Stratix 10 L-Tile/H-Tile Transceiver PHY is the additional 1 bit added to the reconfig\_address bus, compared to the Intel Arria 10 Transceiver PHY version. The same change is required for the Multi-rate PHY as it is created by using the Native PHY as the baseline.

The following figure illustrates how to connect the reconfig\_address.

**Block Diagram on Reconfiguration Address Connectivity for Intel Stratix 10 Ethernet Subsystem Design**The example shown is based on the Ethernet design example model. For the blocks that are generated by Platform Designer, you can obtain the modules from the design example files.

# **Related Information**

- Intel Stratix 10 Low Latency Ethernet 10G MAC Design Example User Guide

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

- Intel Stratix 10 Clocking and PLL User Guide

## Migration Flow

Only Intel Quartus Prime Pro Edition software offers Intel Stratix 10 designs. If you are using an Intel Arria 10 Ethernet design from the Intel Quartus Prime Standard Edition, you need to migrate to Intel Quartus Prime Pro Edition version for any Intel Stratix 10 design.

## **Related Information**

Intel Quartus Prime Pro Edition Handbook Volume 1: Design and Compilation

Provides more information about upgrading IP cores and Qsys Pro systems to Quartus Prime Pro Edition software.

# **Document Revision History for AN 808**

Migration Guidelines from Intel Arria 10 to Intel Stratix 10 for 10G Ethernet Subsystem

| Document Ver sion | Changes                                                                                                                                                                                                                                                                                                |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019.11.20        | <ul> <li>Rebranded as Intel.</li> <li>Updated Figure: Clocking and Reset Scheme for LL 10GbE MAC and 1G/2.5G/5G/10G M ulti-rate Ethernet PHY Design Example (1G/2.5G Mode with IEEE 1588v2 Feature) for Intel St ratix 10 Devices.</li> <li>Made editorial updates throughout the document.</li> </ul> |

| Date      | Version    | Changes          |

|-----------|------------|------------------|

| June 2017 | 2017.06.19 | Initial release. |

AN 808: Migration Guidelines from Intel® Arria® 10 to Intel® Stratix® 10 for 10G Ethernet Subsystem.

# **Documents / Resources**

Manuals+,