## intel Mailbox Client with Avalon Streaming Interface FPGA IP **User Guide**

Home » Intel » intel Mailbox Client with Avalon Streaming Interface FPGA IP User Guide

#### intel Mailbox Client with Avalon Streaming Interface FPGA IP User Guide

#### **Contents**

- 1 Mailbox Client with Avalon® Streaming Interface Intel FPGA IP **Overview**

- 1.1 Device Family Support

- 2 Documents / Resources

- **3 Related Posts**

#### Mailbox Client with Avalon® Streaming Interface Intel FPGA IP Overview

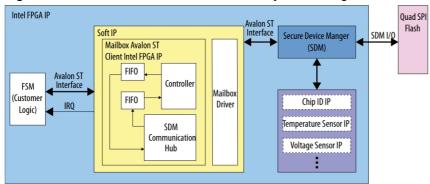

The Mailbox Client with Avalon® streaming interface Intel® FPGA IP (Mailbox Client with Avalon ST Client IP) provides a communication channel between your custom logic and the secure device manager (SDM). You can use the Mailbox Client with Avalon ST IP to send command packets and receive response packets from SDM peripheral modules. The Mailbox Client with Avalon ST IP defines functions that the SDM runs.

Your custom logic can use this communication channel to receive information and access flash memory from the following peripheral modules:

- The Temperature Sensor

- · The Voltage Sensor

- Quad serial peripheral interface (SPI) flash memory

Note: Throughout this user guide, the term Avalon ST abbreviates the Avalon streaming interface or IP.

Figure 1. Mailbox Client with Avalon ST IP System Design

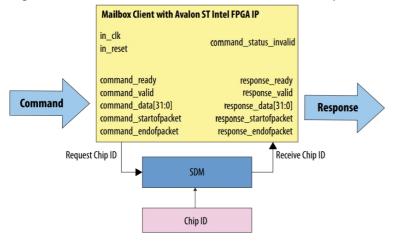

The following figure shows an application in which the Mailbox Client with Avalon ST IP reads the Chip ID.

Figure 2. Mailbox Client with Avalon ST IP Reads Chip ID

#### **Device Family Support**

The following lists the device support level definitions for Intel FPGA IPs:

- Advance support The IP is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP for system architecture and resource utilization studies, simulation, pin out, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards trade offs).

- **Preliminary support** The IP is verified with preliminary timing models for this device family. The IP meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support** The IP is verified with final timing models for this device family. The IP meets all functional and timing requirements for the device family and can be used in production designs.

Table 1. Device Family Support

| Device Family | Support |

|---------------|---------|

| Intel Agilex™ | Advance |

**Note:** You cannot simulate the Mailbox Client with Avalon Streaming Interface Intel FPGA IP because the IP receives the responses from the SDM. To validate this IP, Intel recommends that you perform hardware evaluation.

#### **Related Information**

Mailbox Client with Avalon Streaming Interface Intel FPGA IP Release Notes

#### **Parameters**

| Parameter Name          | Value  | Description                                                                                                                                                                                               |  |  |

|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Enable status interface | On Off | When you enable this interface, the Mailbox Client with Avalon strea ming interface Intel FPGA IP includes the command_status_invalid signal. When command_status_invalid asserts, you must reset the IP. |  |  |

#### Interfaces

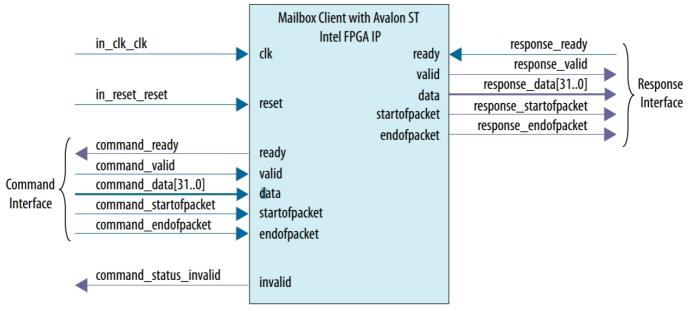

The following figure illustrates the Mailbox Client with Avalon Streaming Interface Intel FPGA IP interfaces:

Figure 3. Mailbox Client with Avalon Streaming Interface Intel FPGA IP Interfaces

For more information about Avalon streaming interfaces, refer to the Avalon Interface Specifications.

#### **Related Information**

**Avalon Interface Specifications**

#### **Clock and Reset Interfaces**

Table 2. Clock and Reset Interfaces

| Signal<br>Name | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| in_clk         | Input     | This is the clock for the Avalon streaming interfaces. The maximum frequency in 250 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| in_rese<br>t   | Input     | This is an active high reset. Assert in_reset to reset the Mailb ox Client with Avalon streaming interface Intel FPGA IP (Mail box Client with Avalon ST IP). When the in_reset signal asserts, the SDM must flush any pending activity from the Mai lbox Client with Avalon ST IP. The SDM continues to process commands from other clients.  To ensure the Mailbox Client with Avalon ST IP functions correctly when the device enters user mode, your design must include the Reset Release Intel FPGA IP to hold the reset until the FPGA fabric entered user mode. Intel recommends using a reset synchronizer when connecting the user reset or output of the Reset Release IP to |  |  |  |

|                |           | the reset port of the Mailbox Client with Avalon ST IP. To imple ment the reset synchronizer, use the Reset Bridge Intel FPGA IP available in the Platform Designer.  Note: For IP instantiation and connection guidelines in the Platform Designer, refer to the Required Communication and Host Components for the Remote System Update Design Example figure in the Intel Agilex Configuration User Guide.                                                                                                                                                                                                                                                                           |  |  |  |

## **Command Interface**

Use the Avalon Streaming (Avalon ST) interface to send commands to the SDM.

**Table 3. Command Interface**

| Signal Name           | Direction | Description                                                                                                                                                                                                                                                                      |

|-----------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| command_ready         | Output    | The Mailbox Client with Avalon ST Intel FPGA IP asserts comm and_ready when it is ready to receive commands from the appli cation. The ready_latency is 0 cycles. The Mailbox Client with Avalon ST can accept command_data[31:0] in the same cycle t hat command_ready asserts. |

| command_valid         | Input     | The command_valid signal asserts to indicate that command_d ata is valid.                                                                                                                                                                                                        |

| command_data[31:0]    | Input     | The command_data bus drives commands to the SDM. Refer t o Command List and Description for definitions of the commands.                                                                                                                                                         |

| command_startofpacket | Input     | The command_startofpacket asserts in the first cycle of a command packet.                                                                                                                                                                                                        |

| command_endofpacket   | Input     | The command_endofpacket asserts in the last cycle of comma nd a packet.                                                                                                                                                                                                          |

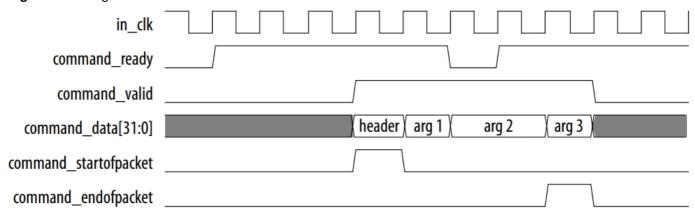

Figure 4. Timing for Avalon ST Command Packet

#### **Response Interface**

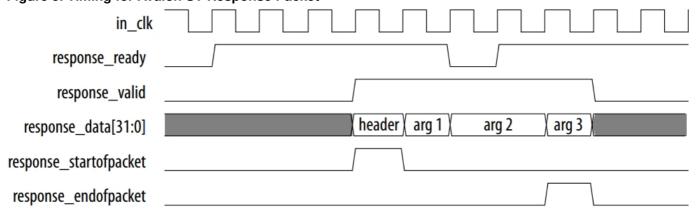

The SDM Avalon ST Client IP sends responses to your application using the response interface.

**Table 4. Response Interface**

| Signal 5               | Direction | Description                                                                                                                                                                                                                                          |

|------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| response_ready         | Input     | Application logic can assert the response_ready signal whenev er it is able to receive a response.                                                                                                                                                   |

| response_valid         | Output    | The SDM asserts response_valid to indicate that response_dat a is valid.                                                                                                                                                                             |

| response_data[31:0]    | Output    | The SDM drives response_data to provide the requested infor mation. The first word of the response is a header that identifies the command that the SDM is providing. Refer to <i>Command Lis t and Description</i> for definitions of the commands. |

| response_startofpacket | Output    | The response_startofpacket asserts in the first cycle of a response packet.                                                                                                                                                                          |

| response_endofpacket   | Output    | The response_endofpacket asserts in the last cycle of a respon se packet.                                                                                                                                                                            |

Figure 5. Timing for Avalon ST Response Packet

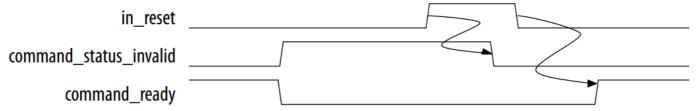

## **Command Status Interface**

Table 5. Command Status Interface

| Signal Name Direction  |        | Description                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| command_status_invalid | Output | The command_status_invalid asserts to indicate an error. This signal typically asserts to indicate that the length of the command specified in the command header does not match the length of the command sent. When command_status_invalid asserts, your application logic must assert in_reset to restart the Mailbox Client with Avalon streaming interface Intel FPGA IP. |  |  |

Figure 6. Reset After command\_status\_invalid Asserts

#### **Commands and Responses**

The host controller communicates with the SDM using command and response packets via the Mailbox Client Intel FPGA IP.

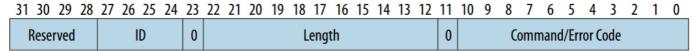

The first word of the command and response packets is a header that provides basic information about the command or response.

Figure 7. Command and Response Header Format

**Note:** The LENGTH field in the command header must match the command length of corresponding command. The following table describes the fields of the header command.

**Table 6. Command and Response Header Description**

| Header                      | Bit     | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reserved                    | [31:28] | Reserved.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| ID                          | [27:24] | The command ID. The response header returns the ID specified in the command header. Refer to Operation Commands for command descriptions.                                                                                                                                                                                                                                              |  |  |

| 0                           | [23]    | Reserved.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LENGTH                      | [22:12] | Number of words of arguments following the header. The IP responds with an error if a wrong number of words of arguments is entered for a given command.  If there is a mismatch between the command length specified in the command header and the number of words sent. The IP raises bit 3 of the Interrupt Status Register (COMMAND_INVALID) and the Mailbox Client must be reset. |  |  |

| Reserved                    | [11]    | Reserved. Must be set to 0.                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Command Code/Error Cod<br>e | [10:0]  | Command Code specifies the command. The Error Code indicates whether the command succeeded or failed. In the command header, these bits represent command code. In the response header, these bits represent error code. If the command succeeds, the Error Code is 0. If the command fails, refer to the error codes defined in the <i>Error Code Responses</i> .                     |  |  |

## **Operation Commands**

## **Resetting Quad SPI Flash**

**Important:** For Intel Agilex devices, you must connect the serial flash or quad SPI flash reset pin to the AS\_nRST pin. The SDM must fully control the QSPI reset. Do not connect the quad SPI reset pin to any external host.

**Table 7. Command List and Description**

| Command | Code<br>(Hex) | Comman d Length | Respons<br>e Length<br>(1) | Description                  |

|---------|---------------|-----------------|----------------------------|------------------------------|

| NOOP    | 0             | 0               | 0                          | Sends an OK status response. |

| GET_IDCOD<br>E   | 10 | 0 | 1    | The response contains one argument which is the JTAG IDCO DE for the device                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|----|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GET_CHIPID       | 12 | 0 | 2    | The response contains 64-bit CHIPID value with the least signi ficant word first.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GET_USERC<br>ODE | 13 | 0 | 1    | The response contains one argument which is the 32-bit JTAG USERCODE that the configuration bitstream writes to the device.                                                                                                                                                                                                                                                                                                                                                                           |

| GET_VOLTAG<br>E  | 18 | 1 | n(2) | The GET_VOLTAGE command has a single argument which is a bitmask specifying the channels to read. Bit 0 specifies channel 0, bit 1 specifies channel 1, and so on.  The response includes a one-word argument for each bit set in the bitmask. The voltage returned is an unsigned fixed-point number with 16 bits below the binary point. For example, a voltage of 0.75V returns 0x0000C000. (3)  Intel Agilex devices have a single voltage sensor. Consequently, the response is always one word. |

| GET_ TEMPE<br>RATURE | 19 | 1 | n( <u>4</u> ) | The GET_TEMPERATURE command returns the temperature or temperatures of the core fabric or transceiver channel locations you specify.  For Intel Agilex devices, use the sensor_req argument to specify the locations. The sensor_req includes the following fields:  Bits[31:28]: Reserved.  Bits[27:16]: Sensor Location. Specifies the TSD location.  Bits[15:0]: Sensor mask. Specifies the sensors to read for the esensor location specified. The response contains one word for each temperature requested. If omitted, the command reads channel 0. The least significant bit (lsb) corresponds to sensor 0. The most significant bit (msb) corresponds to channel 15.  The temperature returned is a signed fixed value with 8 bits below the binary point. For example, a temperature of 10°C returns 0x00000A00. A of temperature -1.5°C returns 0xFFFFFE80. If the bitmask specifies an invalid Location, the command returns an error code which is any value in the range 0x80000000 - 0x800000FF.  For Intel Agilex devices, refer to the Intel Agilex Power Management User Guide for more information about local build-in temperature sensors. |

|----------------------|----|---|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSU_IMAGE_<br>UPDATE | 5C | 2 | 0             | Triggers reconfiguration from the data source that can be either the factory or an application image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| continued            |    | , |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

- 1. This number does not include the command or response header.

- 2. For Intel Agilex devices that support reading multiple devices, index n matches the number of channels you enable on your device.

- 3. Refer to the *Intel Agilex Power Management User Guide* for more information about temperature sensor channels and locations.

- 4. Index n depends on the number of sensor masks.

| Command   | Code<br>(Hex) | Comman<br>d Length<br>(1) | Respons<br>e Length<br>(1) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                 |  |  |

|-----------|---------------|---------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------|--|--|

|           |               |                           |                            | This command takes an optional 64-bit argument that specifies the reconfiguration data address in the flash. When sending the argument to the IP, you first send bits [31:0] followed by bits 63:32]. If you do not provide this argument its value is assumed to be 0.  • Bit [31:0]: The start address of an application image.  • Bit [63:32]: Reserved (write as 0).  Once the device processes this command, it returns the response header to response FIFO before it proceeds to reconfigure the device. Ensure the host PC or host controller stops servicing other interrupts and focuses on reading the response header data to indicate the command completed successfully. Otherw se, the host PC or host controller may not be able to receive the response once the reconfiguration process started. Once the device proceeds with reconfiguration, the link between the external host and FPGA is lost. If you use PCIe in your design, you need to re-enumerate the PCIe link.  Important: When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9. |             |                                 |  |  |

|           |               |                           |                            | RSU_GET_SPT retrieves the quad SPI flash location for the tw o sub- partition tables that the RSU uses: SPT0 and SPT1. The 4-word response contains the following information:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                 |  |  |

|           |               |                           |                            | Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Name        | Description                     |  |  |

| RSU_GET_S |               |                           |                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPT0[63:32] |                                 |  |  |

| PT        | 5A            | 0                         | 4                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | SPT0 address in quad SPI flash. |  |  |

|                   |   |   |   | 1       | SPT0[31:0]     |                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---|---|---|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |   |   |   | 2       | SPT1[63:32]    |                                                                                                                                                                                                                                                                                                                                                                  |

|                   |   |   |   | 3       | SPT1[31:0]     | SPT1 address in quad SPI flash.                                                                                                                                                                                                                                                                                                                                  |

|                   |   |   |   | command | to check the c | last reconfiguration. You can use this onfiguration status during and after coe contains the following information:                                                                                                                                                                                                                                              |

|                   |   |   |   | Word    | Summary        | Description                                                                                                                                                                                                                                                                                                                                                      |

| CONFIG_ST<br>ATUS | 4 | 0 | 6 | 0       | State          | Describes the most recent configurat ion related error. Returns 0 when the re are no configuration errors. The error field has 2 fields:  • Upper 16 bits: Major error code.  • Lower 16 bits: Minor error code.  Refer to Appendix: CONFIG_STATU S and RSU_STATUS Error Code De scriptions in the Mailbox Client Intel FPGA IP User Guide for more information. |

|                   |   |   |   |         |                |                                                                                                                                                                                                                                                                                                                                                                  |

|  | 1 | Quartus Ver sion | Available in Intel Quartus® Prime so ftware versions between 19.4 and 2 1.2, the field displays:  • Bit [31:28]: Index of the firmware or decision firmware copy that was used the most recently.  Possible values are 0, 1, 2, and 3  • Bit [27:24]: Reserved  • Bit [23:16]: Value is '0'                                                                                                                                                                                                                                                                                                                                                                      |

|--|---|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  |   |                  | Available in Intel Quartus Prime soft ware version 21.3 or later, the Quart us version displays:  • Bit [31:28]: Index of the firmware or decision firmware copy that wa s used the most recently.  Possible values are 0, 1, 2, and 3  .  • Bit [27:24]: Reserved  • Bit [23:16]: Major Quartus release number  • Bit [15:8]: Minor Quartus release number  • Bit [7:0]: Quartus update number  For example, in Intel Quartus Prime software version 21.3.1, the followin g values represent the major and mi nor Quartus release numbers, and the Quartus update number:  • Bit [23:16] = 8'd21 = 8'h15  • Bit [15:8] = 8'd3 = 8'h3  • Bit [7:0] = 8'd1 = 8'h1 |

|                |    |   |   | 2                       | Pin status           | <ul> <li>Bit [31]: Current nSTATUS outp value (active low)</li> <li>Bit [30]: Detected nCONFIG inp value (active low)</li> <li>Bit [29:8]: Reserved</li> <li>Bit [7:6]: Configuration clock so ce <ul> <li>01 = Internal oscillator</li> <li>10 = OSC_CLK_1</li> </ul> </li> <li>Bit [5:3]: Reserved</li> <li>Bit [2:0]: The MSEL value at poer up</li> </ul> |

|----------------|----|---|---|-------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |    |   |   | 3                       | Soft function status | Contains the value of each of the st functions, even if you have not as gned the function to an SDM pin.  Bit [31:6]: Reserved Bit [5]: HPS_WARMRESET Bit [4]: HPS_COLDRESET Bit [3]: SEU_ERROR Bit [2]: CVP_DONE Bit [1]: INIT_DONE Bit [0]: CONF_DONE                                                                                                       |

|                |    |   |   | 4                       | Error locatio        | Contains the error location. Return 0 if there are no errors.                                                                                                                                                                                                                                                                                                 |

|                |    |   |   | 5                       | Error details        | Contains the error details. Returns if there are no errors.                                                                                                                                                                                                                                                                                                   |

|                |    |   |   | e this cor<br>uration a | mmand to check       | ote system upgrade status. You can<br>the configuration status during con<br>ompleted. This command returns th                                                                                                                                                                                                                                                |

| RSU_STATU<br>S | 5B | 0 | 9 |                         |                      |                                                                                                                                                                                                                                                                                                                                                               |

|  | Word | Summary | Description (Continue) |

|--|------|---------|------------------------|

|--|------|---------|------------------------|

1. This number does not include the command or response header

|  |  | 0-1 | Current imag<br>e | Flash offset of the currently running application image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--|--|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  |  | 2-3 | Failing imag<br>e | Flash offset of the highest priority fail ing application image. If multiple ima ges are available in flash memory, st ores the value of the first image that failed. A value of all 0s indicates no failing images. If there are no failing i mages, the remainder of the remaining words of the status information do not store valid information.  Note: A rising edge on nCONFIG to reconfigure from ASx4, does not clear this field. Information about failing i mage only updates when the Mailbox Client receives a new RSU_IMAGE_UPDATE command and successfully configures from the update image. |

|  |  | 4   | State             | Failure code of the failing image. The error field has two parts:  • Bit [31:16]: Major error code  • Bit [15:0]: Minor error code Returns 0 for no failures. Refer to  Appendix: CONFIG_STATUS and R SU_STATUS Error Code Descriptions in the Mailbox Client Intel FPGA IP User Guide for more information.                                                                                                                                                                                                                                                                                               |

|  |  | 5   | Version           | RSU interface version and error source. For more information, refer to RSU S tatus and Error Codes section in the Hard Processor System Remote System Update User Guide.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|  |  |     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           | 6 | 6 | Error locatio                       | Stores the error location of the failin g image. Returns 0 for no errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---|---|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 7 | 7 | Error details                       | Stores the error details for the failing image. Returns 0 if there are no erro rs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 8 | 8 | Current imag<br>e retry count<br>er | Count of the number of retries that h ave been attempted for the current i mage. The counter is 0 initially. The counter is set to 1 after the first retry, then 2 after a second retry.  Specify the maximum number of retr ies in your Intel Quartus Prime Settin gs File (.qsf). The command is: set_global_assignment -name RSU_MA X_RETRY_COUNT 3. Valid values f or the MAX_RETRY counter are 1-3. The actual number of available retrie s is MAX_RETRY -1 This field was added in version 19.3 of the Intel Quartus Prime Pro Editio n software. |

| continued |   |   |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

1. This number does not include the command or response header.

| RSU_NOTIFY | 5D | 1 | 0 | Clears all error information in the RSU_STATUS response and resets the retry counter. The one-word argument has the follo wing fields:  • 0x00050000: Clear current reset retry counter. Resetting the current retry counter sets the counter back to zero, as if the current image was successfully loaded for the first time.  • 0x00060000: Clear error status information. |

|------------|----|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSU_NOTIFY | 5D | 1 | 0 | e current retry counter sets the counter back to zero, as if th e current image was successfully loaded for the first time.                                                                                                                                                                                                                                                    |

|            |    |   |   | Quartus i illile i io Euition sollware.                                                                                                                                                                                                                                                                                                                                        |

| QSPI_OPEN  | 32 | 0 | 0 | Requests exclusive access to the quad SPI. You issue this request before any other QSPI requests. The SDM accepts the request if the quad SPI is not in use and the SDM is not configuring the device.  Returns OK if the SDM grants access.  The SDM grants exclusive access to the client using this mailb ox. Other clients cannot access the quad SPI until the active client relinquishes access using the QSPI_CLOSE command. Access to the quad SPI flash memory devices via any mailbox client IP is not available by default in designs that include the HPS, unless you disable the QSPI in HPS software configuration.  Important: When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9. |

|------------|----|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSPI_CLOSE | 33 | 0 | 0 | Closes the exclusive access to the quad SPI interface.  Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| QSPI_SET_C<br>S | 34 | 1 | 0 | Specifies one of the attached quad SPI devices via the chip sel ect lines. Takes a one-word argument as described below  • Bits[31:28]: Flash device to select. Refer to information belo w for the value that corresponds to the nCSO[0:3] pins  • Value 4'h0000 selects the flash that corresponds to n CSO[0].  • Value 4'h0001 selects the flash that corresponds to n CSO[1].  • Value 4'h0002 selects the flash that corresponds to n CSO[2].  • Value 4'h0003 selects the flash that corresponds to n CSO[3].  • Bits[27:0]: Reserved (write as 0).  Note: Intel Agilex or Intel Stratix® 10 devices support one AS x 4 flash memory device for AS configuration from quad SPI device connected to nCSO[0]. Once the device entered user mode, you can use up to four AS x4 flash memories for use wit h Mailbox Client IP or HPS as data storage. TheMailbox Client IP or HPS can use nCSO[3:0] to access quad SPI devices. This command is optional for the AS x4 configuration scheme, the chip select line follows the last executed QSPI_SET_CS command or defaults to nCSO[0] after the AS x4 configuration. The JTAG configuration scheme requires executing this command to access the QSPI flash memory devices using SDM_IO pins. Access to the QSPI flash memory devices using SDM_IO pins is only available for the AS x4 configuration scheme, JTAG con figuration, and a design compiled for AS x4 configuration. For the Avalon streaming interface (Avalon ST) configuration scheme, you must connect QSPI flash memories to GPIO pins. |

|-----------------|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| continued       |    |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

1. This number does not include the command or response header

|            |    |     |   | Important: When resetting quad SPI, you must follow instructio ns specified in Resetting Quad SPI Flash on page 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSPI_READ  | ЗА | 2   | N | Reads the attached quad SPI device. The maximum transfer si ze is 4 kilobytes (KB) or 1024 words. Takes two arguments:  • The quad SPI flash address (one word). The address must be word aligned. The device returns the 0x1 error code for n on- aligned addresses.  • Number of words to read (one word).  When successful, returns OK followed by the read data from the quad SPI device. A failure response returns an error code. For a partially successful read, QSPI_READ may erroneously return the OK status.  Note: You cannot run the QSPI_READ command while device configuration is in progress.  Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9. |

| QSPI_WRITE | 39 | 2+N | 0 | <ul> <li>Writes data to the quad SPI device. The maximum transfer siz e is 4 kilobytes (KB) or 1024 words.</li> <li>Takes three arguments:</li> <li>The flash address offset (one word). The write address mus t be word aligned.</li> <li>The number of words to write (one word).</li> <li>The data to be written (one or more words). A successful wr ite returns the OK response code.</li> <li>To prepare memory for writes, use the QSPI_ERASE comman d before issuing this command.</li> <li>Note: You cannot run the QSPI_WRITE command while devic e configuration is in progress.</li> <li>Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9.</li> </ul>  |

| QSPI_ERASE               | 38 | 2 | 0 | Erases a 4/32/64 KB sector of the quad SPI device. Takes two arguments:  • The flash address offset to start the erase (one word). Depending on the number of words to erase, the start address must be:  • 4 KB aligned if number words to erase is 0x400  • 32 KB aligned if number words to erase is 0x2000  • 64 KB aligned if number words to erase is 0x4000 Returns an error for non-4/32/64 KB aligned addresses.  • The number of words to erase is specified in multiples of:  • 0x400 to erase 4 KB (100 words) of data. This option is the minimum erase size.  • 0x2000 to erase 32 KB (500 words) of data  • 0x4000 to erase 64 KB (1000 words) of data A successful erase returns the OK response code.  Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9. |

|--------------------------|----|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSPI_READ_<br>DEVICE_REG | 35 | 2 | N | Reads registers from the quad SPI device. The maximum read is 8 bytes. Takes two arguments:  • The opcode for the read command.  • The number of bytes to read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| continued                |    |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

1. This number does not include the command or response header.

|                                |    |     |   | A successful read returns the OK response code followed by the data read from the device. The read data return is in multiple of 4 bytes. If the bytes to read is not an exact multiple of 4 bytes, it is padded with multiple of 4 bytes until the next word boun dary and the padded bit value is zero.  Important: When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|----|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSPI_WRITE<br>_ DEVICE_R<br>EG | 36 | 2+N | 0 | Writes to registers of the quad SPI. The maximum write is 8 by tes. Takes three arguments:  • The opcode for the write command.  • The number of bytes to write.  • The data to write.  To perform a sector erase or sub-sector erase, you must specify the serial flash address in most significant byte (MSB) to least significant byte (LSB) order as the following example ill ustrates.  To erase a sector of a Micron 2 gigabit (Gb) flash at address 0x04FF0000 using the QSPI_WRITE_DEVICE_REG command, write the flash address in MSB to LSB order as shown here:  Header: 0x00003036 Opcode: 0x000000DC  Number of bytes to write: 0x00000004 Flash address: 0x000 0FF04  A successful write returns the OK response code. This command pads data that is not a multiple of 4 bytes to the next word boundary. The command pads the data with zero.  Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9. |

| QSPI_SEND_<br>DEVICE_OP        | 37 | 1   | 0 | Sends a command opcode to the quad SPI. Takes one argume nt:  • The opcode to send the quad SPI device.  A successful command returns the OK response code.  Important:When resetting quad SPI, you must follow instructions specified in Resetting Quad SPI Flash on page 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- Mailbox Client Intel FPGA IP User Guide: CONFIG\_STATUS and RSU\_STATUS Error Code Descriptions

For more information about the CONFIG\_STATUS and RSU\_STATUS error codes.

- Intel Agilex Power Management User Guide

For more information about the temperature sensor channel numbers and temperature sensing diodes (TSDs).

- Intel Agilex Hard Processor System Technical Reference Manual

- Intel Agilex Hard Processor System Remote System Update User Guide

## **Error Code Responses**

#### **Table 8. Error Codes**

| Valu<br>e (He<br>x) | Error Code Res<br>ponse             | Description                                                                                                                                                                                          |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | ОК                                  | Indicates that the command completed successfully. A command may erroneously return the OK status if a command, such as QSPI_READ is partially successful.                                           |

| 1                   | INVALID_COM<br>MAND                 | Indicates that the currently loaded boot ROM cannot decode or recognize the comm and code.                                                                                                           |

| 3                   | UNKNOWN_CO<br>MMAND                 | Indicates that the currently loaded firmware cannot decode the command code.                                                                                                                         |

| 4                   | INVALID_COM<br>MAND_ PARAM<br>ETERS | Indicates that the command is incorrectly formatted. For example, the length field set ting in header is not valid.                                                                                  |

| 6                   | COMMAND_IN<br>VALID_ON_ SO<br>URCE  | Indicates that the command is from a source for which it is not enabled.                                                                                                                             |

| 8                   | CLIENT_ID_NO<br>_MATCH              | Indicates that the Client ID cannot complete the request to close the exclusive acces s to quad SPI. The Client ID does not match the existing client with the current exclusive access to quad SPI. |

|   | 9          | INVALID_ADDR<br>ESS            | The address is invalid. This error indicates one of the following conditions:  • An unaligned address  • An address range problem  • A read permission problem  • An invalid chip select value, displaying value of more than 3  • An invalid address in RSU case  • An invalid bitmask value for GET_VOLTAGE command  • An invalid page selection for GET_TEMPERATURE command |                           |                    |                                                      |

|---|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|------------------------------------------------------|

| • | Α          | AUTHENTICATI<br>ON_FAIL        | Indicates the configuration bitstream signature authentication failure.                                                                                                                                                                                                                                                                                                        |                           |                    |                                                      |

|   | В          | TIMEOUT                        | This error indicates time out due to the following conditions:  Command  Waiting for QSPI_READ operation to complete  Waiting for the requested temperature reading from one of the temperature sensors. May indicate a potential hardware error in the temperature sensor.                                                                                                    |                           |                    |                                                      |

|   | С          | HW_NOT_REA<br>DY               | <ul> <li>Indicates one of the following conditions:</li> <li>The hardware is not ready. Can indicate either an initialization or configuration pro blem. The hardware may refer to quad SPI.</li> <li>RSU image is not used to configure the FPGA.</li> </ul>                                                                                                                  |                           |                    |                                                      |

|   | D          | HW_ERROR                       | Indicates that the command completed unsuccessfully due to unrecoverable hardware error.                                                                                                                                                                                                                                                                                       |                           |                    |                                                      |

| , |            |                                | Indicates a command specific error due to an SDM command you used.                                                                                                                                                                                                                                                                                                             |                           |                    | d you used.                                          |

|   |            |                                | SDM<br>Command                                                                                                                                                                                                                                                                                                                                                                 | Error Name                | Err<br>or c<br>ode | Description                                          |

|   | 80 –<br>8F | COMMAND_SP<br>ECIFIC_ERRO<br>R | GET_CHIPID                                                                                                                                                                                                                                                                                                                                                                     | EFUSE_SYSTEM_ FAIL<br>URE | 0x8<br>2           | Indicates that the eFus e cache pointer is inval id. |

|   |            |                                |                                                                                                                                                                                                                                                                                                                                                                                |                           |                    |                                                      |

|     |                                                       | QSPI_OPEN/ QSPI_CLO<br>SE/ QSPI_SET_CS/<br>QSPI_READ_D EVICE_R<br>EG/                                                                                                                                                             | QSPI_HW_E                 | RROR | 0x8<br>0                                                                                                                                                                                              | Indicates QSPI flash m<br>emory error. This error<br>indicates one of the foll<br>owing conditions: |

|-----|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|     |                                                       | QSPI_WRITE_ DEVICE_R<br>QSPI_SEND_D EVICE_OF<br>QSPI_READ                                                                                                                                                                         |                           |      | <ul> <li>A QSPI flash chi p select setting p roblem</li> <li>A QSPI flash initi alization problem</li> <li>A QSPI flash res etting problem</li> <li>A QSPI flash sett ings update probl em</li> </ul> |                                                                                                     |