# intel FPGA Programmable Acceleration Card N3000 Board Management Controller User Guide

Home » Intel » intel FPGA Programmable Acceleration Card N3000 Board Management Controller User Guide

# **Contents**

- 1 intel FPGA Programmable Acceleration Card N3000 Board Management Controller

- 2 Intel FPGA Programmable Acceleration Card N3000 BMC Introduction

- 3 Board Monitoring through PLDM over MCTP SMBus

- **4 SMBus Interface Speed**

- **4.1 MCTP Packetization Support**

- **4.2 MCTP Packet Fields**

- 4.3 Supported Command Sets

- 4.4 PLDM Topology and Hierarchy

- 5 Board Monitoring through I2C SMBus

- **6 EEPROM Data Format**

- **7 Revision History**

- 8 Documents / Resources

- 8.1 References

- 9 Related Posts

intel FPGA Programmable Acceleration Card N3000 Board Management Controller

# Intel FPGA Programmable Acceleration Card N3000 BMC Introduction

#### **About this Document**

Reference the Intel FPGA Programmable Acceleration Card N3000 Board Management User Guide to learn more about the functions and features of the Intel® MAX® 10 BMC and to understand how to read telemetry data on the Intel FPGA PAC N3000 using PLDM over MCTP SMBus and I2C SMBus. An introduction to Intel MAX 10 root of trust (RoT) and secure remote system update is included.

# Overview

The Intel MAX 10 BMC is responsible for controlling, monitoring and granting access to board features. The Intel MAX 10 BMC interfaces with on-board sensors, the FPGA and the flash, and manages power-on/power-off sequences, FPGA configuration and telemetry data polling. You can communicate with the BMC using the Platform Level Data Model (PLDM) version 1.1.1 protocol. The BMC firmware is field upgradeable over PCIe using the remote system update feature.

# **Features of BMC**

- Acts as a Root of Trust (RoT) and enables the secure update features of the Intel FPGA PAC N3000.

- Controls firmware and FPGA flash updates over PCle.

- Manages FPGA configuration.

- Configures the network settings for the C827 Ethernet re-timer device.

- Controls Power up and power down sequencing and fault detection with automatic shut-down protection.

- Controls power and resets on the board.

- · Interfaces with sensors, FPGA flash and QSFPs.

- Monitors telemetry data (board temperature, voltage and current) and provides protective action when readings are outside of critical threshold.

- Reports telemetry data to host BMC via Platform Level Data Model (PLDM) over MCTP SMBus or I2C.

- Supports PLDM over MCTP SMBus via PCIe SMBus. 0xCE is a 8-bit slave address.

- Supports I2C SMBus. 0xBC is the 8-bit slave address.

- Accesses the Ethernet MAC addresses in EEPROM and field replaceable unit identificiation (FRUID)

EEPROM.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

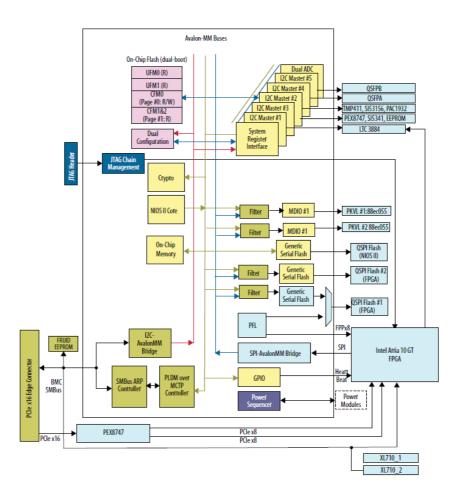

# **BMC High-Level Block Diagram**

# **Root of Trust (RoT)**

The Intel MAX 10 BMC acts as a Root of Trust (RoT) and enables the secure remote system update feature of the Intel FPGA PAC N3000. The RoT includes features that may help prevent the following:

- Loading or executing of unauthorized code or designs

- Disruptive operations attempted by unprivileged software, privileged software, or the host BMC

- Unintended execution of older code or designs with known bugs or vulnerabilities by enabling the BMC to revoke authorization

Intel® FPGA Programmable Acceleration Card N3000 Board Management Controller User Guide

The Intel FPGA PAC N3000 BMC also enforces several other security policies relating to access through various interfaces, as well as protecting the on-board flash through write rate limitation. Please refer to the Intel FPGA Programmable Acceleration Card N3000 Security User Guide for information on RoT and security features of the Intel FPGA PAC N3000.

# **Related Information**

# **Secure Remote System Update**

The BMC supports Secure RSU for the Intel MAX 10 BMC Nios® firmware and RTL image and Intel Arria® 10 FPGA image updates with authentication and integrity checks. The Nios firmware is in charge of authenticating the image during the update process. The updates are pushed over the PCIe interface to the Intel Arria 10 GT FPGA, which in turn writes it over the Intel Arria 10 FPGA SPI master to Intel MAX 10 FPGA SPI slave. A temporary flash area called staging area stores any type of authentication bitstream through SPI interface. The BMC RoT design contains the cryptographic module which implements SHA2 256 bit hash verification function and ECDSA 256 P 256 signature verification function to authenticate the keys and user image. Nios firmware uses the cryptographic module to authenticate the user signed image in the staging area. If authentication passes, the Nios firmware copies the user image to user flash area. If the authentication fails, the Nios firmware reports an error. Please refer to the Intel FPGA Programmable Acceleration Card N3000 Security User Guide for information on RoT and security features of the Intel FPGA PAC N3000.

#### **Related Information**

Intel FPGA Programmable Acceleration Card N3000 Security User Guide

# **Power Sequence Management**

The BMC Power sequencer state machine manages Intel FPGA PAC N3000 power-on and power-off sequences for corner cases during the power-on process or normal operation. The Intel MAX 10 power-up flow covers the entire process including Intel MAX 10 boot-up, Nios boot-up, and power sequence management for FPGA configuration. The host must check the build versions of both the Intel MAX 10 and FPGA, as well as the Nios status after every power-cycle, and take corresponding actions in case the Intel FPGA PAC N3000 runs into corner cases such as a Intel MAX 10 or FPGA factory build load failure or Nios boot up failure. The BMC protects the Intel FPGA PAC N3000 by shutting down power to the card under the following conditions:

- 12 V Auxiliary or PCIe edge supply voltage is below 10.46 V

- FPGA core temperature reaches 100°C

- Board temperature reaches 85 °C

# **Board Monitoring Through Sensors**

The Intel MAX 10 BMC monitors voltage, current and temperature of various components on the Intel FPGA PAC N3000. Host BMC can access the telemetry data through PCle SMBus. The PCle SMBus between host BMC and Intel FPGA PAC N3000 Intel MAX 10 BMC is shared by both the PLDM over MCTP SMBus endpoint and Standard I2C slave to Avalon-MM interface (read-only).

# **Board Monitoring through PLDM over MCTP SMBus**

The BMC on the Intel FPGA PAC N3000 communicates with a server BMC over the PCIe\* SMBus. The MCTP controller supports Platform Level Data Model (PLDM) over Management Component Transport Protocol (MCTP) stack. MCTP endpoint slave address is 0xCE by default. It can be reprogrammed into corresponding section of external FPGA Quad SPI flash via in-band way if necessary. The Intel FPGA PAC N3000 BMC supports a subset of the PLDM and MCTP commands to enable a server BMC to obtain sensor data such as voltage, current and temperature.

#### Note:

Platform Level Data Model (PLDM) over MCTP SMBus endpoint is supported. PLDM over MCTP via native PCIe is not supported. SMBus device category: "Fixed not Discoverable" device is supported by default, but all four device categories are supported and are field-reconfigurable. ACK-Poll is supported

- Supported with SMBus default slave address 0xCE.

- Supported with a fixed or assigned slave address.

The BMC supports version 1.3.0 of the Management Component Transport Protocol (MCTP) Base Specification (DTMF specification DSP0236), version 1.1.1 of the PLDM for Platform Monitoring and Control standard (DTMF specification DSP0248), and version 1.0.0 of the PLDM for Message Control and Discovery (DTMF specification DSP0240).

#### **Related Information**

Distributed Management Task Force (DMTF) Specifications For link to specific DMTF specifications

# **SMBus Interface Speed**

The Intel FPGA PAC N3000 implementation supports SMBus transactions at 100 KHz by default.

# **MCTP Packetization Support**

# **MCTP Definitions**

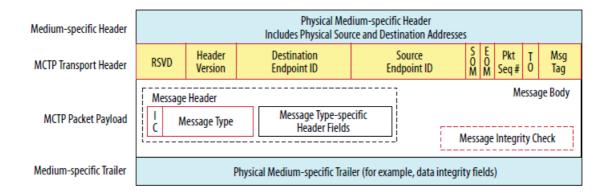

- The message body represents the payload of an MCTP message. The message body can span multiple MCTP packets.

- MCTP packet payload refers to the portion of the message body of an MCTP message that is carried in a single MCTP packet.

- Transmission Unit refers to the size of the portion of the MCTP packet payload.

# **Transmission Unit Size**

- The baseline transmission unit (minimum transmission unit) size for MCTP is 64 bytes.

- All MCTP control messages are required to have a packet payload that is no larger than the baseline transmission unit without negotiation. (The negotiation mechanism for larger transmission units between endpoints is message type-specific and is not addressed in MCTP Base specification)

- Any MCTP message whose message body size is bigger than 64 bytes shall be split into multiple packets for a single message transmission.

#### **MCTP Packet Fields**

# Generic Packet/Message Fields

#### **Supported Command Sets**

# **Supported MCTP Commands**

- · Get MCTP Version Support

- Base Spec Version Info

- Control Protocol Version Info

- PLDM over MCTP Version

- Set Endpoint ID

- · Get Endpoint ID

- Get Endpoint UUID

- Get Message Type Support

- · Get Vendor Defined Message Support

#### Note:

For Get Vendor Defined Message Support command, the BMC responds with the completion code ERROR\_INVALID\_DATA(0x02).

# **Supported PLDM Base Specification Commands**

- SetTID

- GetTID

- GetPLDMVersion

- GetPLDMTypes

- GetPLDMCommands

# Supported PLDM for Platform Monitoring and Control Specification Commands

- SetTID

- GetTID

- · GetSensorReading

- GetSensorThresholds

- SetSensorThresholds

- · GetPDRRepositoryInfo

- GetPDR

#### Note:

The BMC Nios II core polls for different telemetry data every 1 millisecond, and the polling duration takes about 500~800 milliseconds, hence the response message versus a corresponding request message of the command GetSensorReading or GetSensorThresholds accordingly updates every 500~800 milliseconds.

#### Note:

GetStateSensorReadings is not supported.

# **PLDM Topology and Hierarchy**

# **Defined Platform Descriptor Records**

The Intel FPGA PAC N3000 uses 20 Platform Descriptor Records (PDRs). Intel MAX 10 BMC only supports consolidated PDRs where the PDRs will not be added or removed dynamically when QSFP is plugged and unplugged. When unplugged the sensor operational status will simply be reported as unavailable.

# **Sensor Names and Record Handle**

All PDRs are assigned an opaque numeric value called the Record Handle. This value is used for accessing individual PDRs within the PDR Repository via GetPDR (DTMF specification DSP0248). The following table is a consolidated list of sensors monitored on Intel FPGA PAC N3000.

# **PDRs Sensor Names and Record Handle**

|                                      |                           | Sensor Information                                  | PLDM                    |                                                                                                |                                               |  |

|--------------------------------------|---------------------------|-----------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Function                             | Sensor Name               | Sensor Reading So urce (Component)                  | PDR<br>Record<br>Handle | Thresholds in P<br>DR                                                                          | Threshold c<br>hanges allo<br>wed via<br>PLDM |  |

| Total Intel FPGA PA<br>C input power | Board Power               | Calculate from PCIe fingers 12V Current and Voltage | 1                       | 0                                                                                              | No                                            |  |

| PCIe fingers 12 V C urrent           | 12 V Backplane C urrent   | PAC1932 SENSE1                                      | 2                       | 0                                                                                              | No                                            |  |

| PCIe fingers 12 V V oltage           | 12 V Backplane V oltage   | PAC1932 SENSE1                                      | 3                       | 0                                                                                              | No                                            |  |

| 1.2 V Rail Voltage                   | 1.2 V Voltage             | MAX10 ADC                                           | 4                       | 0                                                                                              | No                                            |  |

| 1.8 V Rail Voltage                   | 1.8 V Voltage             | MAX 10 ADC                                          | 6                       | 0                                                                                              | No                                            |  |

| 3.3 V Rail Voltage                   | 3.3 V Voltage             | MAX 10 ADC                                          | 8                       | 0                                                                                              | No                                            |  |

| FPGA Core Voltage                    | FPGA Core Voltag<br>e     | LTC3884 (U44)                                       | 10                      | 0                                                                                              | No                                            |  |

| FPGA Core Current                    | FPGA Core Curre           | LTC3884 (U44)                                       | 11                      | 0                                                                                              | No                                            |  |

| FPGA Core Temper ature               | FPGA Core Temp<br>erature | FPGA temp diode vi<br>a TMP411                      | 12                      | Upper Warning:<br>90<br>Upper Fatal: 100                                                       | Yes                                           |  |

| Board Temperature                    | Board Temperatur<br>e     | TMP411 (U65)                                        | 13                      | Upper Warning:<br>75<br>Upper Fatal: 85                                                        | Yes                                           |  |

| QSFP0 Voltage                        | QSFP0 Voltage             | External QSFP mod ule (J4)                          | 14                      | 0                                                                                              | No                                            |  |

| QSFP0 Temperatur<br>e                | QSFP0 Temperatu<br>re     | External QSFP mod ule (J4)                          | 15                      | Upper Warning:<br>Value set by<br>QSFP Vendor<br>Upper Fatal: Valu<br>e set by QSFP V<br>endor | No                                            |  |

| PCIe Auxiliary 12V<br>Current | 12 V AUX                 | PAC1932 SENSE2                 | 24 | 0                                                                                              | No |  |

|-------------------------------|--------------------------|--------------------------------|----|------------------------------------------------------------------------------------------------|----|--|

| PCIe Auxiliary 12V<br>Voltage | 12 V AUX Voltage         | PAC1932 SENSE2                 | 25 | 0                                                                                              | No |  |

| QSFP1 Voltage                 | QSFP1 Voltage            | External QSFP mod ule (J5)     | 37 | 0                                                                                              | No |  |

| QSFP1 Temperatur<br>e         | QSFP1 Temperatu<br>re    | External QSFP mod ule (J5)     | 38 | Upper Warning:<br>Value set by<br>QSFP Vendor<br>Upper Fatal: Valu<br>e set by QSFP V<br>endor | No |  |

| PKVL A Core Temp erature      | PKVL A Core Tem perature | PKVL chip (88EC05<br>5) (U18A) | 44 | 0                                                                                              | No |  |

| continued                     |                          |                                |    |                                                                                                |    |  |

|                            |                            | Sensor Information                 | PLDM                    |                       |                                               |

|----------------------------|----------------------------|------------------------------------|-------------------------|-----------------------|-----------------------------------------------|

| Function                   | Sensor Name                | Sensor Reading So urce (Component) | PDR<br>Record<br>Handle | Thresholds in P<br>DR | Threshold c<br>hanges allo<br>wed via<br>PLDM |

| PKVL A Serdes Te mperature | PKVL A Serdes Te mperature | PKVL chip (88EC05<br>5) (U18A)     | 45                      | 0                     | No                                            |

| PKVL B Core Temp erature   | PKVL B Core Tem perature   | PKVL chip (88EC05<br>5) (U23A)     | 46                      | 0                     | No                                            |

| PKVL B Serdes Te mperature | PKVL B Serdes Te mperature | PKVL chip (88EC05<br>5) (U23A)     | 47                      | 0                     | No                                            |

#### Note:

The Upper Warning and Upper Fatal values for QSFP are set by the QSFP vendor. Refer to vendor datasheet for the values. The BMC will read these threshold values and report them out. fpgad is a service that can help you protect the server from crashing when the hardware reaches an upper non-recoverable or lower non-recoverable sensor threshold (also called as fatal threshold). fpgad is capable of monitoring each of the 20 sensors reported by the Board Management Controller. Please refer to the Graceful Shutdown topic from Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000 for more information.

#### Note:

Qualified OEM server systems should provide the required cooling for your workloads. You can obtain the values of the sensors by running the following OPAE command as root or sudo: \$ sudo fpgainfo bmc

# **Related Information**

Intel Acceleration Stack User Guide: Intel FPGA Programmable Acceleration Card N3000

# **Board Monitoring through I2C SMBus**

The standard I2C slave to Avalon-MM interface (read-only) shares the PCIe SMBus between the host BMC and

the Intel MAX 10 RoT. The Intel FPGA PAC N3000 supports standard I2C slave interface and the slave address is 0xBC by default only for out-of-band access. Byte addressing mode is 2-byte offset address mode. Here is the telemetry data register memory map that you can use to access information through the I2C commands. The description column describes how the returned register values may be further processed to get the actual values. The units can be Celsius (°C), mA, mV, mW depending on what sensor you read.

# **Telemetry Data Register Memory Map**

| Register                             | Offset | Width | Access | Field  | Default Valu<br>e | Description                                                                        |

|--------------------------------------|--------|-------|--------|--------|-------------------|------------------------------------------------------------------------------------|

| Board Tempe rature                   | 0x100  | 32    | RO     | [31:0] | 32'h00000000      | TMP411(U65) Register valu e is signed int eger Tempera ture = register value * 0.5 |

| Board Tempe<br>rature High W<br>arn  | 0x104  | 32    | RW     | [31:0] | 32'h00000000      | TMP411(U65) Register valu e is signed int eger                                     |

|                                      |        |       |        |        |                   | High Limit = r<br>egister value<br>* 0.5                                           |

| Board Tempe<br>rature High F<br>atal | 0x108  | 32    | RW     | [31:0] | 32'h00000000      | TMP411(U65)  Register valu e is signed int eger                                    |

|                                      |        |       |        |        |                   | High Critical = register value  * 0.5                                              |

| FPGA Core T<br>emperature            | 0x110  | 32    | RO     | [31:0] | 32'h00000000      | TMP411(U65) Register valu e is signed int eger                                     |

|                                      |        |       |        |        |                   | Temperature = register val ue * 0.5                                                |

| FPGA Die Temperature High Warn | 0x114 | 32 | RW | [31:0] | 32'h00000000 | TMP411(U65)  Register valu e is signed int eger |

|--------------------------------|-------|----|----|--------|--------------|-------------------------------------------------|

|                                |       |    |    |        |              | High Limit = r<br>egister value<br>* 0.5        |

| continued                      |       |    |    |        |              |                                                 |

| Register                  | Offset | Width | Access | Field  | Default Valu<br>e | Description                                             |

|---------------------------|--------|-------|--------|--------|-------------------|---------------------------------------------------------|

| FPGA Core V<br>oltage     | 0x13C  | 32    | RO     | [31:0] | 32'h00000000      | LTC3884(U44<br>)<br>Voltage(mV)<br>= register val<br>ue |

| FPGA Core C<br>urrent     | 0x140  | 32    | RO     | [31:0] | 32'h00000000      | LTC3884(U44 )  Current(mA) = register val ue            |

| 12v Backplan<br>e Voltage | 0x144  | 32    | RO     | [31:0] | 32'h00000000      | Voltage(mV)<br>= register val<br>ue                     |

| 12v Backplan<br>e Current | 0x148  | 32    | RO     | [31:0] | 32'h00000000      | Current(mA)<br>= register val<br>ue                     |

| 1.2v Voltage              | 0x14C  | 32    | RO     | [31:0] | 32'h00000000      | Voltage(mV)<br>= register val<br>ue                     |

| 12v Aux Volta<br>ge       | 0x150  | 32    | RO     | [31:0] | 32'h00000000      | Voltage(mV)<br>= register val<br>ue                     |

| 12v Aux Curr<br>ent       | 0x154  | 32    | RO     | [31:0] | 32'h00000000      | Current(mA)<br>= register val<br>ue                     |

| 1.8v Voltage              | 0x158  | 32    | RO     | [31:0] | 32'h00000000      | Voltage(mV)<br>= register val<br>ue                     |

| 3.3v Voltage              | 0x15C  | 32    | RO     | [31:0] | 32'h00000000      | Voltage(mV)<br>= register val<br>ue                     |

| Board Power                       | 0x160 | 32 | RO | [31:0] | 32'h00000000 | Power(mW) = register value                                                            |

|-----------------------------------|-------|----|----|--------|--------------|---------------------------------------------------------------------------------------|

| PKVL A Core<br>Temperature        | 0x168 | 32 | RO | [31:0] | 32'h00000000 | PKVL1(U18A)  Register valu e is signed int eger  Temperature = register val ue  * 0.5 |

| PKVL A Serd<br>es Temperatu<br>re | 0x16C | 32 | RO | [31:0] | 32'h00000000 | PKVL1(U18A)  Register valu e is signed int eger  Temperature = register val ue  * 0.5 |

| PKVL B Core<br>Temperature        | 0x170 | 32 | RO | [31:0] | 32'h00000000 | PKVL2(U23A)  Register value is signed integer  Temperature = register value  * 0.5    |

| PKVL B Serd<br>es Temperatu<br>re | 0x174 | 32 | RO | [31:0] | 32'h00000000 | PKVL2(U23A)  Register valu e is signed int eger  Temperature = register val ue  * 0.5 |

QSFP values are obtained by reading the QSFP module and reporting the read values in the appropriate register. If the QSFP module does not support Digital Diagnostics Monitoring or if the QSFP module is not installed, then ignore values read from QSFP registers. Use the Intelligent Platform Management Interface (IPMI) tool to read the telemetry data through the I2C bus.

# I2C command to read the board temperatures at address 0x100:

In the command below:

- 0x20 is the I2C master bus address of your server that can access PCIe slots directly. This address varies with the server. Please refer to your server datasheet for the correct I2C address of your server.

- 0xBC is the I2C slave address of the Intel MAX 10 BMC.

- 4 is the number of read data bytes

- 0x01 0x00 is the register address of the board temperature which is presented in the table.

#### Command:

ipmitool i2c bus=0x20 0xBC 4 0x01 0x00

# **Output:**

01110010 00000000 00000000 00000000

The output value in hexidecimal is:  $0x72000000 \ 0x72$  is 114 in decimal. To calculate the temperature in Celsius multiply by 0.5:  $114 \times 0.5 = 57$  °C

# Note:

Not all servers support I2C bus directly access to PCle slots. Please check your server datasheet for support information and I2C bus address.

# **EEPROM Data Format**

This section defines the data format of both the MAC Address EEPROM and the FRUID EEPROM and that can be accessed by the host and FPGA respectively.

#### **MAC EEPROM**

At the time of manufacturing, Intel programs the MAC address EEPROM with the Intel Ethernet Controller XL710-BM2 MAC addresses. The Intel MAX 10 accesses the addresses in the MAC address EEPROM through the I2C bus. Discover the MAC address using the following command: \$ sudo fpga mac

The MAC Address EEPROM only contains the starting 6-byte MAC address at address 0x00h followed by the MAC address count of 08. The starting MAC address is also printed on the label sticker on the back side of the Printed Circuit Board (PCB). The OPAE driver provides sysfs nodes to obtain the starting MAC address from the following location: /sys/class/fpga/intel-fpga-dev.\*/intel-fpga-fme.\*/spi altera.\*.auto/spi\_master/ spi\*/spi\*/mac\_address Starting MAC Address Example: 644C360F4430 The OPAE driver obtain the count from the following location: /sys/class/fpga/ intel-fpga-dev.\*/intel-fpga-fme.\*/spi-altera.\*.auto/spi\_master/ spi\*/spi\*/mac\_count MAC count Example: 08 From the starting MAC address, the remaining seven MAC addresses are obtained by sequentially incrementing the Least Significant Byte (LSB) of the starting MAC Address by a count of one for each subsequent MAC address. Subsequent MAC address example:

- 644C360F4431

- 644C360F4432

- 644C360F4433

- 644C360F4434

- 644C360F4435

- 644C360F4436

- 644C360F4437

**Note**: If you are using an ES Intel FPGA PAC N3000, the MAC EEPROM may not be programmed. If the MAC EEPROM is not programmed then the first MAC address read returns as FFFFFFFFFF.

# Field Replaceable Unit Identification (FRUID) EEPROM Access

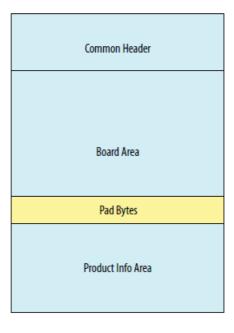

You can only read the field replaceable unit identification (FRUID) EEPROM (0xA0) from the host BMC through SMBus. The structure in the FRUID EEPROM is based on the IPMI specification, Platform Management FRU Information Storage Definition, v1.3, March 24, 2015, from which a board information structure is derived. The FRUID EEPROM follows the common header format with Board Area and Product Info Area. Refer to the table below for what fields in the common header apply to the FRUID EEPROM.

# **Common Header of FRUID EEPROM**

All the fields in the common header are mandatory.

| Field Length in Bytes | Field Description                                                                                                              | FRUID EEPROM Value     |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1                     | Common Header Format Version 7:<br>4 – reserved, write as 0000b<br>3:0 – format version number = 1h fo<br>r this specification | 01h (Set as 00000001b) |

| 1                     | Internal Use Area Starting Offset (in multiples of 8 bytes).  00h indicates that this area is not present.                     | 00h (not present)      |

| 1                     | Chassis Info Area Starting Offset (in multiples of 8 bytes).  Oth indicates that this area is not present.                     | 00h (not present)      |

| 1                     | Board Area Starting Offset (in multiples of 8 bytes).  00h indicates that this area is not present.                            | 01h                    |

| 1 | Product Info Area Starting Offset (in multiples of 8 bytes).  00h indicates that this area is not present. | 0Ch               |

|---|------------------------------------------------------------------------------------------------------------|-------------------|

| 1 | MultiRecord Area Starting Offset (in multiples of 8 bytes).  00h indicates that this area is not present.  | 00h (not present) |

| 1 | PAD, write as 00h                                                                                          | 00h               |

| 1 | Common Header Checksum (zero checksum)                                                                     | F2h               |

The common header bytes are placed from the first address of the EEPROM. The layout looks like the figure below.

# FRUID EEPROM Memory Layout Block Diagram

# **FRUID EEPROM Board Area**

| Field Length in<br>Bytes | Field Description                                                                                                                                 | Field Values                                 | Field Encoding                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1                        | Board Area Format Version 7:4 – re served, write as 0000b 3:0 – format version number                                                             | 0x01                                         | Set to 1h (0000 0001b)                                                                                                      |

| 1                        | Board Area Length (in multiples of 8 bytes)                                                                                                       | 0x0B                                         | 88 bytes (includes 2 pad 0 0 bytes)                                                                                         |

| 1                        | Language Code                                                                                                                                     | 0x00                                         | Set to 0 for English  Note: No other languages supported at this time                                                       |

| 3                        | Mfg. Date / Time: Number of minute s from 0:00 hrs 1/1/96.  Least Significant byte first (little endian)  00_00_00h = unspecified (Dynamic field) | 0x10<br>0x65<br>0xB7                         | Time difference between 12:00 AM 1/1/96 to 12 PM 11/07/2018 is 12018960 minutes = b76510h - stor ed in little endian format |

| 1                        | Board Manufacturer type/length byt e                                                                                                              | 0xD2                                         | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b<br>5:0 – 010010b (18 bytes o<br>f data)                                             |

| Р                        | Board Manufacturer bytes                                                                                                                          | 0x49<br>0x6E<br>0x74<br>0x65<br>0x6C<br>0xAE | 8-bit ASCII + LATIN1 coded Intel® Corporation                                                                               |

| continued                |                                                                                                                                                   |                                              | ,                                                                                                                           |

| Field Length in<br>Bytes | Field Description | Field Values | Field Encoding |

|--------------------------|-------------------|--------------|----------------|

|--------------------------|-------------------|--------------|----------------|

|   |                                      | 0x20<br>0x43<br>0x6F<br>0x72<br>0x70 |                                                                                 |

|---|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------|

|   |                                      | 0x6F<br>0x72                         |                                                                                 |

|   |                                      | 0x61                                 |                                                                                 |

|   |                                      | 0x74<br>0x69                         |                                                                                 |

|   |                                      | 0x6F                                 |                                                                                 |

|   |                                      | 0x6E                                 |                                                                                 |

| 1 | Board Product Name type/length by te | 0xD5                                 | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b<br>5:0 – 010101b (21 bytes o<br>f data) |

|   |                                       | 21/12 |                                              |

|---|---------------------------------------|-------|----------------------------------------------|

|   |                                       | 0X49  |                                              |

|   |                                       | 0X6E  |                                              |

|   |                                       | 0X74  |                                              |

|   |                                       | 0X65  |                                              |

|   |                                       | 0X6C  |                                              |

|   |                                       | 0XAE  |                                              |

|   |                                       | 0X20  |                                              |

|   |                                       | 0X46  |                                              |

|   |                                       | 0X50  |                                              |

|   |                                       | 0X47  |                                              |

| Q | Board Product Name bytes              | 0X41  | 8-bit ASCII + LATIN1 coded Intel FPGA PAC N3 |

|   |                                       | 0X20  | 000                                          |

|   |                                       | 0X50  |                                              |

|   |                                       | 0X41  |                                              |

|   |                                       | 0X43  |                                              |

|   |                                       | 0X20  |                                              |

|   |                                       | 0X4E  |                                              |

|   |                                       | 0X33  |                                              |

|   |                                       | 0X30  |                                              |

|   |                                       | 0X30  |                                              |

|   |                                       | 0X30  |                                              |

|   |                                       |       |                                              |

| 1 |                                       | 0xCC  | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b      |

|   | Board Serial Number type/length by te |       | 5:0 – 001100b (12 bytes o                    |

|   |                                       |       | f data)                                      |

|   |                                       |       |                                              |

|           |                                              | 0x30 |                                          |  |

|-----------|----------------------------------------------|------|------------------------------------------|--|

|           | Board Serial Number bytes<br>(Dynamic field) | 0x30 |                                          |  |

|           |                                              | 0x30 | 8-bit ASCII + LATIN1 coded               |  |

|           |                                              | 0x30 | 1st 6 hex digits are OUI: 0 00000        |  |

| N         |                                              | 0x30 |                                          |  |

|           |                                              | 0x30 | 2nd 6 hex digits are MAC address: 000000 |  |

|           |                                              | 0x30 |                                          |  |

|           |                                              | 0x30 |                                          |  |

|           |                                              |      |                                          |  |

| continued |                                              |      |                                          |  |

| Field Length in<br>Bytes | Field Description                  | Field Values | Field Encoding                                                               |

|--------------------------|------------------------------------|--------------|------------------------------------------------------------------------------|

|                          |                                    |              | Note: This is coded as an example and needs to be modified in an actual devi |

|                          |                                    | 0x30         | ce                                                                           |

|                          |                                    | 0x30         | 1st 6 hex digits are OUI: 6<br>44C36                                         |

|                          |                                    | 0x30         | 2nd 6 hex digits are MAC                                                     |

|                          |                                    | 0x30         | address: 00AB2E                                                              |

|                          |                                    |              | Note: To identify not                                                        |

|                          |                                    |              | programmed FRUID, set<br>OUI and MAC address to<br>"0000".                   |

|                          |                                    |              | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b                                      |

| 1                        | Board Part Number type/length byte | 0xCE         | 5:0 – 001110b (14 bytes o f data)                                            |

|           |                              | 0x4B<br>0x38 | 8-bit ASCII + LATIN1                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                              | 0x32         | coded with BOM ID.                                                                                                                                                                                                                                                                                            |

|           |                              | 0x34         | For 14 byte length, the co ded board part number ex                                                                                                                                                                                                                                                           |

|           |                              | 0x31         | ample is K82417-002                                                                                                                                                                                                                                                                                           |

|           |                              | 0x37         | Note: This is coded as an example and needs to be                                                                                                                                                                                                                                                             |

|           |                              | 0x20         | modified in an actual devi                                                                                                                                                                                                                                                                                    |

| M         | Board Part Number bytes      | 0x30         | This field value varies wit                                                                                                                                                                                                                                                                                   |

|           |                              | 0x30         | h different board PBA nu<br>mber.                                                                                                                                                                                                                                                                             |

|           |                              | 0x32         |                                                                                                                                                                                                                                                                                                               |

|           |                              | 0x20         | PBA Revision has been r<br>emoved in FRUID. These                                                                                                                                                                                                                                                             |

|           |                              | 0x20         | last four bytes return blan k and are reserved for futu                                                                                                                                                                                                                                                       |

|           |                              | 0x20         | re use.                                                                                                                                                                                                                                                                                                       |

|           |                              | 0x20         |                                                                                                                                                                                                                                                                                                               |

|           |                              |              | 8-bit ASCII + LATIN1<br>coded 7:6 – 00b                                                                                                                                                                                                                                                                       |

|           |                              |              | 5:0 – 000000b (0 bytes of data)                                                                                                                                                                                                                                                                               |

|           |                              |              | The FRU File ID bytes fiel d that should follow this is not included as the field w ould be 'null'.                                                                                                                                                                                                           |

| 1         | FRU File ID type/length byte | 0x00         | Note: FRU File ID bytes. The FRU File version field is a pre-defined field provi ded as a manufacturing ai d for verifying the file that was used during manufacture or field updat e to load the FRU information. The content is manufacturer-specific. This field is also provided in the Bo ard Info area. |

|           |                              |              | Either or both fields may b e 'null'.                                                                                                                                                                                                                                                                         |

| 1         | MMID type/length byte        | 0xC6         | 8-bit ASCII + LATIN1 coded                                                                                                                                                                                                                                                                                    |

| continued |                              |              |                                                                                                                                                                                                                                                                                                               |

|           |                              |              |                                                                                                                                                                                                                                                                                                               |

| Field Length in<br>Bytes | Field Description                                                | Field Values                                 | Field Encoding                                                                                                                                                                   |

|--------------------------|------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                  |                                              | 7:6 – 11b 5:0 – 000110b (6 bytes of data)  Note: This is coded as an example and needs to be modified in an actual device                                                        |

| M                        | MMID bytes                                                       | 0x39<br>0x39<br>0x39<br>0x44<br>0x58<br>0x46 | Formatted as 6 hex digits. Specific example in cell al ongside Intel FPGA PAC N3000 MMID = 999DXF. This field value varies wit h different SKUs fields lik e MMID, OPN, PBN etc. |

| 1                        | C1h (type/length byte encoded to in dicate no more info fields). | 0xC1                                         |                                                                                                                                                                                  |

| Υ                        | 00h – any remaining unused space                                 | 0x00                                         |                                                                                                                                                                                  |

| 1                        | Board Area Checksum (zero checksum)                              | 0xB9                                         | Note: The checksum in the is table is a zero checksum computed for the value sused in the table. It must be recomputed for the actual values of a Intel FPGA PAC N3000.          |

| Field Length in Bytes | Field Description                                                                                                    | Field Values                                 | Field Encoding                                                                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|

| 1                     | Product Area Format Version 7:4 – r eserved, write as 0000b  3:0 – format version number = 1h for this specification | 0x01                                         | Set to 1h (0000 0001b)                                                          |

| 1                     | Product Area Length (in multiples of 8 bytes)                                                                        | 0x0A                                         | Total of 80 bytes                                                               |

| 1                     | Language Code                                                                                                        | 0x00                                         | Set to 0 for English  Note: No other languages supported at this time           |

| 1                     | Manufacturer Name type/length byte                                                                                   | 0xD2                                         | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b<br>5:0 – 010010b (18 bytes o<br>f data) |

| N                     | Manufacturer Name bytes                                                                                              | 0x49 0x6E 0x74 0x65 0x6C 0xAE 0x20 0x43 0x6F | 8-bit ASCII + LATIN1 coded Intel Corporation                                    |

| continued             |                                                                                                                      |                                              |                                                                                 |

| Field Length in Bytes | Field Description | Field Values | Field Encoding |

|-----------------------|-------------------|--------------|----------------|

|-----------------------|-------------------|--------------|----------------|

|   |                               | 0x72 |                                         |

|---|-------------------------------|------|-----------------------------------------|

|   |                               | 0x70 |                                         |

|   |                               | 0x6F |                                         |

|   |                               | 0x72 |                                         |

|   |                               | 0x61 |                                         |

|   |                               | 0x74 |                                         |

|   |                               | 0x69 |                                         |

|   |                               | 0x6F |                                         |

|   |                               | 0x6E |                                         |

| 1 | Product Name type/length byte | 0xD5 | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b |

| 1 | Troduct Name typerlength byte | 0,00 | 5:0 – 010101b (21 bytes o f data)       |

|   | I                                           | I    |                                                |

|---|---------------------------------------------|------|------------------------------------------------|

|   |                                             | 0x49 |                                                |

|   |                                             | 0x6E |                                                |

|   |                                             | 0x74 |                                                |

|   |                                             | 0x65 |                                                |

|   |                                             | 0x6C |                                                |

|   |                                             | 0xAE |                                                |

|   |                                             | 0x20 |                                                |

|   |                                             | 0x46 |                                                |

|   |                                             | 0x50 |                                                |

|   |                                             | 0x47 |                                                |

| M | Product Name bytes                          | 0x41 | 8-bit ASCII + LATIN1<br>coded Intel FPGA PAC N |

|   |                                             | 0x20 | 3000                                           |

|   |                                             | 0x50 |                                                |

|   |                                             | 0x41 |                                                |

|   |                                             | 0x43 |                                                |

|   |                                             | 0x20 |                                                |

|   |                                             | 0x4E |                                                |

|   |                                             | 0x33 |                                                |

|   |                                             | 0x30 |                                                |

|   |                                             | 0x30 |                                                |

|   |                                             | 0x30 |                                                |

|   |                                             |      | 0.17.4000                                      |

|   | Droduct Dort/Model Number time - //         |      | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b        |

| 1 | Product Part/Model Number type/len gth byte | 0xCE | 5:0 – 001110b (14 bytes o f data)              |

|   |                                             |      |                                                |

|           |                                 | 0x42 |                                                                                                                    |

|-----------|---------------------------------|------|--------------------------------------------------------------------------------------------------------------------|

|           |                                 | 0x44 |                                                                                                                    |

|           |                                 | 0x2D |                                                                                                                    |

|           |                                 | 0x4E |                                                                                                                    |

|           |                                 | 0x56 | 8-bit ASCII + LATIN1                                                                                               |

|           |                                 | 0x56 | coded                                                                                                              |

|           | Product Part/Model Number bytes | 0x2D | OPN for the board BD-NV<br>V- N3000-1<br>This field value varies wit<br>h different Intel FPGA PA<br>C N3000 OPNs. |

| 0         |                                 | 0x4E |                                                                                                                    |

|           |                                 | 0x33 |                                                                                                                    |

|           |                                 | 0x30 |                                                                                                                    |

|           |                                 | 0x30 |                                                                                                                    |

|           |                                 | 0x30 |                                                                                                                    |

|           |                                 | 0x2D |                                                                                                                    |

|           |                                 | 0x31 |                                                                                                                    |

| continued |                                 |      |                                                                                                                    |

| Field Length in Bytes | Field Description                       | Field Values | Field Encoding                                                                  |

|-----------------------|-----------------------------------------|--------------|---------------------------------------------------------------------------------|

| 1                     | Product Version type/length byte        | 0x01         | 8-bit binary 7:6 – 00b<br>5:0 – 000001b (1 byte of data)                        |

| R                     | Product Version bytes                   | 0x00         | This field is encoded as fa mily member                                         |

| 1                     | Product Serial Number type/length b yte | 0xCC         | 8-bit ASCII + LATIN1<br>coded 7:6 – 11b<br>5:0 – 001100b (12 bytes o<br>f data) |

|           |                                              | 0x30<br>0x30<br>0x30<br>0x30<br>0x30                 | 8-bit ASCII + LATIN1 coded  1st 6 hex digits are OUI: 0 00000  2nd 6 hex digits are MAC address: 000000  Note: This is coded as an                                                                              |  |  |

|-----------|----------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P         | Product Serial Number bytes (Dyna mic field) | 0x30<br>0x30<br>0x30<br>0x30<br>0x30<br>0x30<br>0x30 | example and needs to be modified in an actual devi ce.  1st 6 hex digits are OUI: 6 44C36  2nd 6 hex digits are MAC address: 00AB2E  Note: To identify not programmed FRUID, set OUI and MAC address to "0000". |  |  |

| 1         | Asset Tag type/length byte                   | 0x01                                                 | 8-bit binary 7:6 – 00b<br>5:0 – 000001b (1 byte of data)                                                                                                                                                        |  |  |

| Q         | Asset Tag                                    | 0x00                                                 | Not supported                                                                                                                                                                                                   |  |  |

| 1         | FRU File ID type/length byte                 | 0x00                                                 | 8-bit ASCII + LATIN1 coded 7:6 – 00b  5:0 – 000000b (0 bytes of data)  The FRU File ID bytes fiel d that should follow this is not included as the field w ould be 'null'.                                      |  |  |

| continued | continued                                    |                                                      |                                                                                                                                                                                                                 |  |  |

| Field Length in Bytes | Field Description                                                 | Field Values | Field Encoding                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|-------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                                   |              | Note: FRU file ID bytes.  The FRU File version field is a pre-defined field provi ded as a manufacturing ai d for verifying the file that was used during manufacture or field update to load the FRU in formation. The content is manufacturer- specific. Th is field is also provided in the Board Info area.  Either or both fields may be 'null'. |

| 1                     | C1h (type/length byte encoded to ind icate no more info fields).  | 0xC1         |                                                                                                                                                                                                                                                                                                                                                       |

| Υ                     | 00h – any remaining unused space                                  | 0x00         |                                                                                                                                                                                                                                                                                                                                                       |

| 1                     | Product Info Area Checksum (zero c<br>hecksum)<br>(Dynamic Field) | 0x9D         | Note: the checksum in thi s table is a zero checksum computed for t he values used in the tabl e. It must be recomputed f or the actual values of a I ntel FPGA PAC.                                                                                                                                                                                  |

Intel® FPGA Programmable Acceleration Card N3000 Board Management Controller User Guide

# **Revision History**

# Revision History for the Intel FPGA Programmable Acceleration Card N3000 Board Management Controller User Guide

| Document Ver sion | Changes                     |

|-------------------|-----------------------------|

| 2019.11.25        | Initial Production Release. |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Documents / Resources**

<sup>\*</sup>Other names and brands may be claimed as the property of others.

intel.

Izatel\* PPAA Programmable

Acceleration Card NIDOO Board

Management Controller User Guida

# intel FPGA Programmable Acceleration Card N3000 Board Management Controller [pdf]

User Guide

FPGA Programmable Acceleration Card N3000 Board, Management Controller, FPGA, Programmable Acceleration Card N3000 Board, Management Controller, N3000 Board Management Controller, Management Controller

Charleston name name

# References

- All DMTF Standard Publications | DMTF

- intel 1. Intel FPGA Programmable Acceleration Card N3000 BMC Introduction

- intel 1. Overview

- intel 1. About this Document

- intel ISO 9001:2015 Registrations

Manuals+,