# eCPRI Intel FPGA IP User Manual

Home » Intel » eCPRI Intel FPGA IP User Manual

# eCPRI Intel FPGA IP

The Intel® FPGA IP version (X.Y.Z) number can change with each Intel Quartus® Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

## **Related Information**

- Introduction to Intel FPGA IP Cores

- eCPRI Intel FPGA IP User Guide

- eCPRI Intel FPGA IP Design Example User Guide

## eCPRI Intel FPGA IP v2.0.1

Table 1. v2.0.1 2022.11.15

| Intel Quartus Pri<br>me Version | Description                                                                             | Impact |

|---------------------------------|-----------------------------------------------------------------------------------------|--------|

|                                 | Added support for the following Intel Agilex <sup>™</sup> device grade and speed grade: |        |

| 22.3                            | <ul><li>Device grade: Industrial</li><li>Speed grade: -3</li></ul>                      | _      |

## eCPRI Intel FPGA IP v2.0.0

Table 2. v2.0.0 2022.08.26

| Intel Quartus Pri<br>me Version | Description                                                                                                                                                                                          | Impact |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                 | Added support for L2 CoS priority packet arbitration scheme based on the O-RAN Control, User and Synchronization Pl ane Specification 7.01 (ORAN-WG4.CUS.0-v07.01), Section 5.3 Quality of Service.  | _      |

| 22.2                            | Added support for Data Flow Identification mechanism base d on the O-RAN Control, User and Synchronization Plane S pecification  7.01 (ORAN-WG4.CUS.0-v07.01), Section 5.4 Data Flow Identification. | _      |

|                                 | Added new signal:                                                                                                                                                                                    | _      |

| Intel Quartus Prime Version  | Description                       | Impact |

|------------------------------|-----------------------------------|--------|

|                              | tx_queue_ <n>_fifo_full</n>       |        |

|                              | ext_source_pkt_type               |        |

|                              | ext_tx_ingress_timestamp_96b_data |        |

|                              | ptp_tx_ingress_timestamp_96b_data |        |

|                              | Added new IP parameters:          |        |

|                              | Default VLAN ID                   |        |

|                              | Data Flow Maching Mechanism       |        |

|                              | Packets Arbitration Scheme        |        |

|                              | TX Packets Default Priority       |        |

|                              | TX Arbitration Queue 0 Depth      |        |

|                              | TX Arbitration Queue 1 Depth      | _      |

|                              | TX Arbitration Queue 2 Depth      |        |

|                              | TX Arbitration Queue 3 Depth      |        |

|                              | TX Arbitration Queue 4 Depth      |        |

|                              | TX Arbitration Queue 5 Depth      |        |

|                              | TX Arbitration Queue 6 Depth      |        |

| TX Arbitration Queue 7 Depth |                                   |        |

# eCPRI Intel FPGA IP v1.4.1

Table 3. v1.4.1 2022.07.01

| Intel Quartus Pri<br>me Version | Description                                                                                                                                       | Impact                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                 | Added the hardware design example support for Intel Agilex F-tile device variations. The design example support s the following development kits: |                              |

|                                 | <ul> <li>Intel Agilex I-Series FPGA Development Kit</li> <li>Intel Agilex I-Series Transceiver-SoC Development Kit</li> </ul>                     |                              |

| 22.1                            | Added support for QuestaSim* simulator.                                                                                                           | _                            |

|                                 | Removed support for ModelSim* SE simulator.                                                                                                       | _                            |

|                                 | Added IP-XACT support.                                                                                                                            | _                            |

| 21.3                            | Issue fixed: Unable to detect list of tiles for a device.                                                                                         | No incorrect tile selection. |

# eCPRI Intel FPGA IP v1.4.0

Table 4. v1.4.0 2021.10.01

| Intel Quartus Pri<br>me Version | Description                                                                                                                            | Impact                                                                                       |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                 | Added support for Intel Agilex F-tile devices.                                                                                         | _                                                                                            |

|                                 | Added support for multi-channel designs.                                                                                               | _                                                                                            |

|                                 | Removed support for NCSim* simulator.                                                                                                  | _                                                                                            |

| 21.2                            | Issue fixed: The <b>Streaming</b> option was unavailable when y ou enable the <b>Pair with ORAN</b> option in the IP Parameter Editor. | You can enable or disable the Streaming option when the Pair with ORAN parameter is enabled. |

# eCPRI Intel FPGA IP v1.3.0

Table 5. v1.3.0 2021.02.26

| Intel Quartus Pri<br>me Version | Description                                                                  | Impact                                                       |

|---------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                 | Added support for Intel Agilex E-tile devices.                               | _                                                            |

| 20.4                            | Added support for 1588 PTP Fingerprint (8-bit width) as a st andard feature. | No backward compatibility w ith 4-bit PTP Fingerprint Wid th |

# eCPRI Intel FPGA IP v1.2.0

Table 6. v1.2.0 2021.01.08

| Intel Quartus Pri<br>me Version | Description                                                                                                                                                    | Impact                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|                                 | Added support for interworking function (IWF) type 0.                                                                                                          | You can connect eCPRI nod e with one CPRI node.                             |

|                                 | Supports pairing of eCPRI Intel FPGA IP with O-RAN Intel FPGA IP.                                                                                              | _                                                                           |

|                                 | Added following new IWF related parameters:  Interworking Function (IWF) Support  Interworking Function (IWF) Type  Interworking Function (IWF) Number of CPRI | Using these parameters, you can enable your eCPRI IP for IWF functionality. |

|                                 |                                                                                                                                                                |                                                                             |

|      | Added following IWF related interfaces:                                                                        |   |

|------|----------------------------------------------------------------------------------------------------------------|---|

|      | IWF Type 0 eCPRI Source Interface                                                                              |   |

|      | IWF Type 0 eCPRI Sink Interface                                                                                |   |

|      | IWF Type 0 CPRI MAC Interface                                                                                  |   |

|      | Note: Refer to eCPRI Intel FPGA IP User Guide for detailed information on signals related to these interfaces. | _ |

|      | Added following clock signals:                                                                                 |   |

|      | iwf_gmii_rxclk[N]                                                                                              |   |

|      | iwf_gmii_txclk[N]                                                                                              |   |

|      | gmii_rxclk[N]                                                                                                  | _ |

|      | gmii_txclk[N]                                                                                                  |   |

|      | Added following reset signals:                                                                                 |   |

| 20.3 | iwf_rst_tx_n                                                                                                   |   |

|      | iwf_rst_rx_n                                                                                                   |   |

|      | rst_tx_n_sync                                                                                                  |   |

|      | rst_rx_n_sync                                                                                                  |   |

|      | iwf_gmii_rxreset_n[N]                                                                                          |   |

|      | iwf_gmii_txreset_n[N]                                                                                          | _ |

|      | gmii_rxreset_n[N]                                                                                              |   |

|      | gmii_txreset_n[N]                                                                                              |   |

|      | The eCPRI IP design example for Intel Arria® 10 device is n ow available.                                      | _ |

# eCPRI Intel FPGA IP v1.1.0

Table 7. v1.1.0 2020.05.18

| Intel Quartus Pri<br>me Version | Description                                                                     | Impact |

|---------------------------------|---------------------------------------------------------------------------------|--------|

|                                 | Added support for Intel Arria 10 devices.                                       | _      |

|                                 | The IP supports 10G data rate for Intel Stratix® 10 and Intel Arria 10 devices. | _      |

|                                 | Added following new parameters:                                                 |        |

|                                 | Streaming                                                                       |        |

|                                 | Pair with ORAN                                                                  |        |

| 20.1                            | One-way Delay Measurement Timer Bitwidth                                        | _      |

|                                 | Remote Memory Access Timer Bit-width                                            |        |

|                                 | Remote Reset Timer Bit-width                                                    |        |

## eCPRI Intel FPGA IP v1.0.0

Table 8. v1.0.0 2020.04.13

| Intel Quartus Pri<br>me Version | Description      | Impact |

|---------------------------------|------------------|--------|

| 19.4                            | Initial release. | _      |

## **eCPRI Intel FPGA IP User Guide Archives**

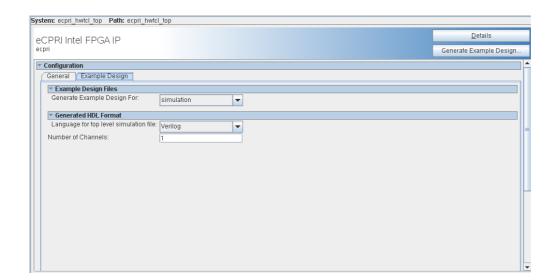

For the latest and previous versions of this user guide, refer to the eCPRI Intel FPGA IP User Guide HTML version. Select the version and click Download. If an IP or software version is not listed, the user guide for the previous IP or software version applies.

## eCPRI Intel FPGA IP Design Example User Guide Archives

For the latest and previous versions of this user guide, refer to the eCPRI Intel FPGA IP Design Example User Guide HTML version. Select the version and click Download. If an IP or software version is not listed, the user guide for the previous IP or software version applies.

#### Intel Corporation.

All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Other names and brands may be claimed as the property of others.

# **Documents / Resources**

intel.

# intel eCPRI Intel FPGA IP [pdf] User Manual eCPRI Intel FPGA IP, eCPRI Intel, FPGA IP

Control of the contro

# References

- intel 1. Introduction to Intel® FPGA IP Cores

- intel 1. eCPRI Intel® FPGA IP Release Notes

- intel 1. Introduction

- intel\_1. Quick Start Guide

- intel 1. Quick Start Guide

- intel 1. Introduction

- intel ISO 9001:2015 Registrations

Manuals+,