# intel Cyclone 10 Native FloatingPoint DSP FPGA IP User Guide

Home » Intel » intel Cyclone 10 Native FloatingPoint DSP FPGA IP User Guide 1

#### **Contents**

- 1 intel Cyclone 10 Native FloatingPoint DSP FPGA IP

- 2 Intel® Cyclone® 10 GX Native Floating-Point DSP Intel® FPGA IP User Guide

- 2.1 Parameterizing the Intel® Cyclone® 10 GX Native Floating-Point DSP Intel® FPGA IP

- 2.2 Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP Signals

- **3 Document Revision History**

- 4 Documents / Resources

- 4.1 References

- **5 Related Posts**

intel Cyclone 10 Native FloatingPoint DSP FPGA IP

## Intel® Cyclone® 10 GX Native Floating-Point DSP Intel® FPGA IP User Guide

#### Parameterizing the Intel® Cyclone® 10 GX Native Floating-Point DSP Intel® FPGA IP

Select different parameters to create an IP core suitable for your design.

- 1. In Intel® Quartus® Prime Pro Edition,create a new project that targets a Intel Cyclone® 10 GX device.

- 2. In IP Catalog, click on Library ➤ DSP ➤ Primitive DSP ➤ Intel Cyclone 10 GX Native Floating Point DSP.

The Intel Cyclone 10 GX Native Floating-Point DSP IP Core IP parameter editor opens.

- 3. In the New IP Variation dialog box, enter an Entity Name and click OK.

- 4. Under Parameters, select the DSP Template and the View you want for your IP core

- 5. In the DSP Block View, toggle the clock or reset of each valid register.

- 6. For Multiply Add or Vector Mode 1, click on the Chain In multiplexer in the GUI to select input from chainin port or Ax port.

- 7. Click the Adder symbol in the GUI to select addition or subtraction.

- 8. Click on the Chain Out multiplexer in the GUI to enable chainout port.

- 9. Click Generate HDL.

- 10. Click Finish.

#### Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP Parameters

Table 1. Parameters

| Parameter    | Value                                                                       | Default Value    | Description                                                                                                                               |

|--------------|-----------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| DSP Template | Multiply Add Multiply Add Multi ply Accumulate Ve ctor Mode 1 Vector Mode 2 | Multiply         | Select the desired operational mode for the DSP block.  The selected operation is reflected in the D SP Block View.                       |

| View         | Register Enables<br>Register Clears                                         | Register Enables | Options to select clocking scheme or reset scheme for registers view. The selected op eration is reflected in the <b>DSP Block View</b> . |

| continued    |                                                                             |                  |                                                                                                                                           |

| Parameter        | Value     | Default Value | Description                                                                                                                                                                                 |

|------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |           |               | Select Register Enables for DSP Block V iew to show registers clocking scheme. Yo u can change the clocks for each of the registers in this view.  Select Register Clears for DSP Block Vie |

|                  |           |               | w to show registers reset scheme. Turn on Use Single Clear to change the registers r eset scheme.                                                                                           |

|                  |           |               | Turn on this parameter if you want a single reset to reset all the registers in the DSP bl ock. Turn off this parameter to use different reset ports to reset the registers.                |

|                  |           |               | Turn on for clear 0 on output register; turn o ff for clear 1 on output register.                                                                                                           |

|                  |           |               | Clear 0 for input registers uses aclr[0]                                                                                                                                                    |

| Use Single Clear | On or off | Off           | signal.                                                                                                                                                                                     |

|                  |           |               | Clear 1 for output and pipeline registers us es                                                                                                                                             |

|                  |           |               | aclr[1] signal.                                                                                                                                                                             |

|                  |           |               | All input registers use aclr[0] reset signal. A Il output and pipeline registers use aclr[1] r eset signal.                                                                                 |

|                  |           |               |                                                                                                                                                                                             |

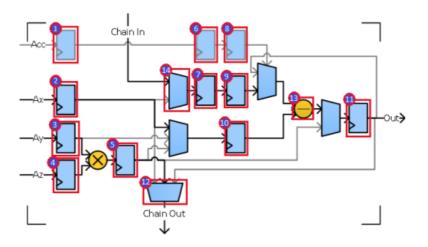

DSP View Block.

| Chain In Multiplexer<br>(14)                                                                                                                                                                                                                                 | Enable Disable                     | Disable | Click on the multiplexer to enable chainin port.                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chain Out Multiplex<br>er (12)                                                                                                                                                                                                                               | Disable Enable                     | Disable | Click on the multiplexer to enable chainout port.                                                                                                                                                                                                                                                                                                                     |

| Adder (13)                                                                                                                                                                                                                                                   | +                                  | +       | Click on the <b>Adder</b> symbol to select addition or subtraction mode.                                                                                                                                                                                                                                                                                              |

| Register Clock  ax_clock (2)  ay_clock (3)  az_clock (4)  mult_pipeline_clock (5)  ax_chainin_pl_cl ock (7)  adder_input_clock ( 9)  adder_input_2_cloc k (10)  output_clock (11)  accum_late_cloc k (1)  accum_pipeline_ cl ock (6)  accum_adder_cl ock (8) | None Clock 0<br>Clock 1<br>Clock 2 | Clock 0 | To bypass any register, toggle the register clock to <b>None</b> .  Toggle the register clock to:  • Clock 0 to use clk[0] signal as the clock source  • Clock 1 to use clk[1] signal as the clock source  • Clock 2 to use clk[2] signal as the clock source  You can only change these settings when y ou select <b>Register Enables</b> in <b>View</b> para meter. |

Figure 1. DSP Block View

**Table 2. DSP Templates**

| DSP Templates | Description                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multiply      | Performs single precision multiplication operation and applies the following equation:  • Out = Ay * Az                                                                                                                                            |

| Add           | Performs single precision addition or subtraction operation and applies the following equations:.  • Out = Ay + Ax  • Out = Ay - Ax                                                                                                                |

| Multiply Add  | This mode performs single precision multiplication, followe d by addition or subtraction operations and applies the following equations.  • Out = (Ay * Az) – chainin  • Out = (Ay * Az) + chainin  • Out = (Ay * Az) – Ax  • Out = (Ay * Az) + Ax |

| Multiply Accumulate | Performs floating-point multiplication followed by floating-p oint addition or subtraction with the previous multiplication result and applies the following equations:  • Out(t) = [Ay(t) * Az(t)] - Out (t-1) when accumulate signal is driven high.  • Out(t) = [Ay(t) * Az(t)] + Out (t-1) when accumulate port is driven high.  • Out(t) = Ay(t) * Az(t) when accumulate port is driven low. |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vector Mode 1       | Performs floating-point multiplication followed by floating-p oint addition or subtraction with the chainin input from the previous variable DSP block and applies the following equ ations:.                                                                                                                                                                                                     |

| continued           |                                                                                                                                                                                                                                                                                                                                                                                                   |

| DSP Templates | Description                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Out = (Ay * Az) - chainin                                                                                                                                                                                                                         |

|               | Out = (Ay * Az) + chainin                                                                                                                                                                                                                         |

|               | Out = (Ay * Az) , chainout = Ax                                                                                                                                                                                                                   |

|               | Performs floating-point multiplication where the IP core fe eds the multiplication result is directly to chainout. The IP core then adds or subtracts the chainin input from the prev ious variable DSP block from input Ax as the output result. |

| Vector Mode 2 | This mode applies the following equations:                                                                                                                                                                                                        |

| vector wode Z | • Out = Ax – chainin , chainout = Ay * Az                                                                                                                                                                                                         |

|               | Out = Ax + chainin , chainout = Ay * Az                                                                                                                                                                                                           |

|               | Out = Ax , chainout = Ay * Az                                                                                                                                                                                                                     |

|               |                                                                                                                                                                                                                                                   |

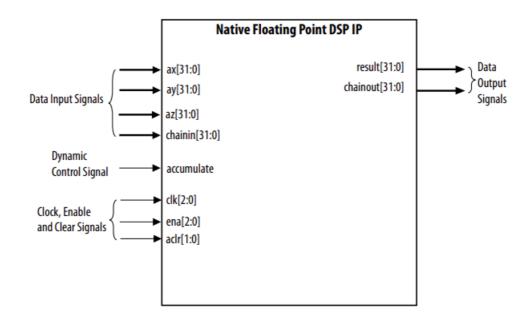

## Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP Signals

Figure 2. Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP Signals The figure shows the input and output signals of the IP core.

Table 3. Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP Input Signals

| Signal Name | Туре  | Width | Default | Description                                                                                                                                               |

|-------------|-------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ax[31:0]    | Input | 32    | Low     | Input data bus to the multiplier. Available in:  • Add mode  • Multiply-Add mode without chainin and chain nout feature  • Vector Mode 1  • Vector Mode 2 |

| ay[31:0]    | Input | 32    | Low     | Input data bus to the multiplier.  Available in all floating-point operational modes .                                                                    |

| az[31:0]    | Input | 32    | Low     | Input data bus to the multiplier. Available in:  • Multiply  • Multiply Add  • Multiply Accumulate  • Vector Mode 1  • Vector Mode 2                      |

| chainin[31:0] | Input | 32 | Low  | Connect these signals to the chainout signals fr om the preceding floating-point DSP IP core.                                                                                              |

|---------------|-------|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk[2:0]      | Input | 3  | Low  | Input clock signals for all registers.  These clock signals are only available if any of the input registers, pipeline registers, or output register is set to Clock0 or Clock1 or Clock2. |

| ena[2:0]      | Input | 3  | High | Clock enable for clk[2:0]. These signals are active-High.  • ena[0] is for Clock0  • ena[1] is for Clock1  • ena[2] is for Clock2                                                          |

| aclr[1:0]     | Input | 2  | Low  | Asynchronous clear input signals for all register s. These signals are active-high.  Use aclr[0] for all input registers and use aclr[1]  for all pipeline and output registers.           |

| accumulate     | Input  | 1  | Low | Input signal to enable or disable the accumulator feature.  • Assert this signal to enable feedback the ad der's output.  • De-assert this signal to disable the feedback mechanism.  You can assert or de-assert this signal during r un- time.  Available in Multiply Accumulate mode. |

|----------------|--------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| chainout[31:0] | Output | 32 | _   | Connect these signals to the chainin signals of the next floating-point DSP IP core.                                                                                                                                                                                                     |

| result[31:0]   | Output | 32 | _   | Output data bus from IP core.                                                                                                                                                                                                                                                            |

### **Document Revision History**

Changes to the Intel Cyclone 10 GX Native Floating-Point DSP Intel FPGA IP User Guide

| Date          | Version    | Changes          |

|---------------|------------|------------------|

| November 2017 | 2017.11.06 | Initial release. |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

#### **Documents / Resources**

#### References

- intel 1. Intel® Cyclone® 10 GX Native Floating-Point DSP Intel® FPGA IP...

- intel ISO 9001:2015 Registrations

Manuals+,