#### Skip to content

#### Manuals+

User Manuals Simplified.

# ASMI Parallel II Intel FPGA IP User Guide

Home » Intel » ASMI Parallel II Intel FPGA IP User Guide

**Contents hide**

1 ASMI Parallel II Intel FPGA IP

**2 Release Information**

3 Ports

**4 Parameters**

**5 Register Map**

**6 Operations**

**7 Control Status Register Operations**

**8 Memory Operations**

9 ASMI Parallel II Intel FPGA IP Use Case Examples

10 ASMI Parallel II Intel FPGA IP User Guide Archives

11 Document Revision History for the ASMI Parallel II Intel FPGA IP User Guide

12 Documents / Resources

12.1 References

**13 Related Posts**

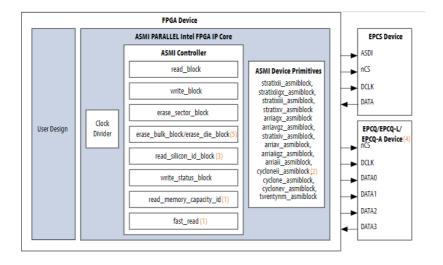

### **ASMI Parallel II Intel FPGA IP**

The ASMI Parallel II Intel® FPGA IP provides access to the Intel FPGA configuration devices, which are the quad-serial configuration (EPCQ), low-voltage quad-serial configuration (EPCQ-L), and EPCQ-A serial configuration. You can use this IP to read and write data to the external flash devices for applications, such as remote system update and SEU Sensitivity Map Header File (.smh) storage.

Other than the features supported by the ASMI Parallel Intel FPGA IP, the ASMI Parallel II Intel FPGA IP additionally supports:

• Direct flash access (write/read) through the Avalon® memory-mapped interface.

- · Control register for other operations through the control status register (CSR) interface in the Avalon memory-mapped interface.

- Translate the generic commands from the Avalon memory-mapped interface into device command codes.

The ASMI Parallel II Intel FPGA IP is available for all Intel FPGA device families including the Intel MAX® 10 devices which are using the GPIO mode.

The ASMI Parallel II Intel FPGA IP only supports the EPCQ, EPCQ-L, and EPCQ-A devices. If you are using third-party flash devices, you must use the Generic Serial Flash Interface Intel FPGA IP.

The ASMI Parallel II Intel FPGA IP is supported in the Intel Quartus® Prime software version 17.0 and onwards.

#### **Related Information**

- Introduction to Intel FPGA IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts

- Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices

- Guidelines for efficient management and portability of your project and IP files.

- · ASMI Parallel Intel FPGA IP Core User Guide

- Generic Serial Flash Interface Intel FPGA IP User Guide

- Provides support for third-party flash devices.

- AN 720: Simulating the ASMI Block in Your Design

#### **Release Information**

IP versions are the same as the Intel Quartus Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

The IP version (X.Y.Z) number may change from one Intel Quartus Prime software version to another. A change in:

- X indicates a major revision of the IP. If you update your Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

### Table 1. ASMI Parallel II Intel FPGA IP Release Information

| Item                                    | Description |

|-----------------------------------------|-------------|

| IP Version                              | 18.0        |

| Intel Quartus Prime Pro Edition Version | 18.0        |

| Release Date                            | 2018.05.07  |

### **Ports**

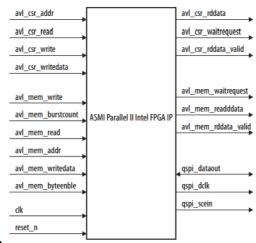

Figure 1. Ports Block Diagram

**Table 2. Ports Description**

| Signal Widt | n Direction | Description |

|-------------|-------------|-------------|

|-------------|-------------|-------------|

### Avalon Memory-Mapped Slave Interface for CSR (avl\_csr)

| avl_csr_addr   | 6  | Input  | Avalon memory-mapped interface address bus. The address bus is in word addressing. |

|----------------|----|--------|------------------------------------------------------------------------------------|

| avl_csr_read   | 1  | Input  | Avalon memory-mapped interface read control to the CSR.                            |

| avl_csr_rddata | 32 | Output | Avalon memory-mapped interface read data bus from the CSR.                         |

| avl_csr_write        | 1  | Input  | Avalon memory-mapped interface write control to the CSR.                                      |

|----------------------|----|--------|-----------------------------------------------------------------------------------------------|

| avl_csr_writedata    | 32 | Input  | Avalon memory-mapped interface write data bus to CSR.                                         |

| avl_csr_waitrequest  | 1  | Output | Avalon memory-mapped interface waitrequest control from the CSR.                              |

| avl_csr_rddata_valid | 1  | Output | Avalon memory-mapped interface read data valid that indicates the CSR read data is available. |

## Avalon Memory-Mapped Slave Interface for Memory Access (avl\_mem)

| avl_mem_write       | 1  | Input  | Avalon memory-mapped interface write control to the memory                                                                                             |

|---------------------|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| avl_mem_burstcount  | 7  | Input  | Avalon memory-mapped interface burst count for the memory. The value range from 1 to 64 (maximum page size).                                           |

| avl_mem_waitrequest | 1  | Output | Avalon memory-mapped interface waitrequest control from the memory.                                                                                    |

| avl_mem_read        | 1  | Input  | Avalon memory-mapped interface read control to the memory                                                                                              |

| avl_mem_addr        | N  | Input  | Avalon memory-mapped interface address bus. The address bus is in word addressing.  The width of the address depends on the flash memory density used. |

| avl_mem_writedata   | 32 | Input  | Avalon memory-mapped interface write data bus to the memory                                                                                            |

| avl_mem_readddata   | 32 | Output | Avalon memory-mapped interface read data bus from the memory.                                                                                          |

| avl_mem_rddata_valid | 1 | Output | Avalon memory-mapped interface read data valid that indicates the memory read data is available.                                  |

|----------------------|---|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| avl_mem_byteenble    | 4 | Input  | Avalon memory-mapped interface write data enable bus to memory. During bursting mode, byteenable bus will be logic high, 4'b1111. |

| Clock and Reset      |   |        |                                                                                                                                   |

| clk                  | 1 | Input  | Input clock to clock the IP. (1)                                                                                                  |

| reset_n              | 1 | Input  | Asynchronous reset to reset the IP.(2)                                                                                            |

| Conduit Interface(3) |   |        |                                                                                                                                   |

Input or output port to feed data from the flash device.

## continued...

fqspi\_dataout

| Signal     | Width | Direction | Description                                                   |

|------------|-------|-----------|---------------------------------------------------------------|

| qspi_dclk  | 1     | Output    | Provides clock signal to the flash device.                    |

|            |       |           | Provides the ncs signal to the flash device.                  |

| qspi_scein | 1     | Output    | Supports Stratix® V, Arria® V, Cyclone® V, and older devices. |

| deb-assem  |       |           | Provides the ncs signal to the flash device.                  |

|            | 3     | Output    | Supports Intel Arria 10 and Intel Cyclone 10 GX devices.      |

- You can set the clock frequency to lower or equal to 50 MHz.

- Hold the signal for at least one clock cycle to reset the IP.

4

• Available when you enable the Disable dedicated Active Serial interface parameter.

Bidirectional

## **Related Information**

- Quad-Serial Configuration (EPCQ) Devices Datasheet

- EPCQ-L Serial Configuration Devices Datasheet

- EPCQ-A Serial Configuration Device Datasheet

### **Parameters**

## **Table 3. Parameter Settings**

| Parameter                                    | Legal Values                                                                                                                                                                  | Descriptions                                                                                                                                                                                                                                         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration device type                    | EPCQ16,<br>EPCQ32,<br>EPCQ64,<br>EPCQ128,<br>EPCQ256,<br>EPCQ512, EPCQ-L256, EPCQ-L512,<br>EPCQ-L1024,<br>EPCQ4A,<br>EPCQ16A,<br>EPCQ32A,<br>EPCQ32A,<br>EPCQ64A,<br>EPCQ128A | Specifies the EPCQ, EPCQ-L, or EPCQ-A device type you want to use.                                                                                                                                                                                   |

| Choose I/O mode                              | NORMAL<br>STANDARD DUAL<br>QUAD                                                                                                                                               | Selects extended data width when you enable the Fast Read operation.                                                                                                                                                                                 |

| Disable dedicated Active<br>Serial interface | _                                                                                                                                                                             | Routes the ASMIBLOCK signals to the top level of your design.                                                                                                                                                                                        |

| Enable SPI pins interface                    | _                                                                                                                                                                             | Translates the ASMIBLOCK signals to the SPI pin interface.                                                                                                                                                                                           |

| Enable flash simulation model                | _                                                                                                                                                                             | Uses the default EPCQ 1024 simulation model for simulation. If you are using a third-party flash device, refer to <i>AN 720:</i> Simulating the <i>ASMI Block in Your Design</i> to create a wrapper to connect the flash model with the ASMI Block. |

| Number of Chip Select used                   | 1<br>2( <u>4</u> )<br>3( <u>4</u> )                                                                                                                                           | Selects the number of chip select connected to the flash.                                                                                                                                                                                            |

• Only supported in Intel Arria 10 devices, Intel Cyclone 10 GX devices, and other devices with Enable SPI pins interface enabled.

## **Related Information**

- Quad-Serial Configuration (EPCQ) Devices Datasheet

- EPCQ-L Serial Configuration Devices Datasheet

- EPCQ-A Serial Configuration Device Datasheet

- AN 720: Simulating the ASMI Block in Your Design

## Table 4. Register Map

- Each address offset in the following table represents 1 word of memory address space.

- All registers have a default value of 0x0.

| Offset | Register Name   | R/W | Field Name      | Bit             | Width       | Description                                                                                                                                                                  |

|--------|-----------------|-----|-----------------|-----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | WR_ENABLE       | W   | WR_ENABLE       | 0               | 1           | Write 1 to perform write enable.                                                                                                                                             |

| 1      | WR_DISABLE      | w   | WR_DISABLE      | 0               | 1           | Write 1 to perform write disable.                                                                                                                                            |

| 2      | WR_STATUS       | W   | WR_STATUS       | 7:0             | 8           | Contains the information to write to the status register.                                                                                                                    |

| 3      | RD_STATUS       | R   | RD_STATUS       | 7:0             | 8           | Contains the information from read status register operation.                                                                                                                |

| 4      | SECTOR_ERASE    | W   | Sector Value    | 23:0<br>or 31:0 | 24 or<br>32 | Contain the sector address to be erased depending on device density.(5)                                                                                                      |

| 5      | SUBSECTOR_ERASE | W   | Subsector Value | 23:0<br>or 31:0 | 24 or<br>32 | Contains the subsector address to be erased depending on device density.(6)                                                                                                  |

| 6 – 7  | Reserved        |     |                 |                 |             |                                                                                                                                                                              |

|        |                 | W/R | CHIP SELECT     | 7:4             | 4           | Selects flash device. The default value is 0, which targets first flash device. To select second device, set the value to 1, to select the third device, set the value to 2. |

W/R DISABLE

0 1

Set this to 1 to disable the SPI signals of the IP by putting all output signal to high-Z state.

## continued...

| Offset | Register Name            | R/W | Field Name           | Bit  | Width | Description                                                 |

|--------|--------------------------|-----|----------------------|------|-------|-------------------------------------------------------------|

|        |                          |     |                      |      |       | This can be used to share bus with other devices.           |

| 9 – 12 | Reserved                 |     |                      |      |       |                                                             |

| 13     | WR_NON_VOLATILE_CONF_REG | W   | NVCR value           | 15:0 | 16    | Writes value to non-<br>volatile configuration<br>register. |

| 14     | RD_NON_VOLATILE_CONF_REG | R   | NVCR value           | 15:0 | 16    | Reads value from non-<br>volatile configuration<br>register |

| 15     | RD_FLAG_STATUS_REG       | R   | RD_FLAG_STATUS_REG   | ì 8  | 8     | Reads flag status register                                  |

| 16     | CLR_FLAG_ STATUS REG     | W   | CLR_FLAG_ STATUS REG | à 8  | 8     | Clears flag status register                                 |

| 17     | BULK_ERASE               | W   | BULK_ERASE           | 0    | 1     | Write 1 to erase entire chip (for single-die device).(7)    |

| 18         | DIE_ERASE             | W | DIE_ERASE             | 0   | 1 | Write 1 to erase entire die (for stack-die device).(7)     |

|------------|-----------------------|---|-----------------------|-----|---|------------------------------------------------------------|

| 19         | 4BYTES_ADDR_EN        | W | 4BYTES_ADDR_EN        | 0   | 1 | Write 1 to enter 4 bytes address mode                      |

| 20         | 4BYTES_ADDR_EX        | W | 4BYTES_ADDR_EX        | 0   | 1 | Write 1 to exit 4 bytes address mode                       |

| 21         | SECTOR_PROTECT        | W | Sector protect value  | 7:0 | 8 | Value to write to status register to protect a sector. (8) |

| 22         | RD_MEMORY_CAPACITY_ID | R | Memory capacity value | 7:0 | 8 | Contains the information of memory capacity ID.            |

| 23 –<br>32 | Reserved              |   |                       |     |   |                                                            |

You only need to specify any address within the sector and the IP will erase that particular sector. You only need to specify any address within the subsector and the IP will erase that particular subsector.

## **Related Information**

- Quad-Serial Configuration (EPCQ) Devices Datasheet

- EPCQ-L Serial Configuration Devices Datasheet

- EPCQ-A Serial Configuration Device Datasheet

- · Avalon Interface Specifications

## **Operations**

The ASMI Parallel II Intel FPGA IP interfaces are Avalon memory-mapped interface compliant. For more details, refer to the Avalon specifications.

- You only need to specify any address within the die and the IP will erase that particular die.

- For EPCQ and EPCQ-L devices, the block protect bit are bit [2:4] and [6] and the top/bottom (TB) bit is bit 5 of the status register. For EPCQ-A devices, the block protect bit are bit [2:4] and the TB bit is bit 5 of the status register.

## **Related Information**

· Avalon Interface Specifications

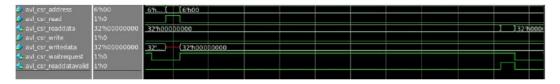

## **Control Status Register Operations**

You can perform a read or write to a specific address offset using the Control Status Register (CSR). To execute the read or write operation for the control status register, follow these steps:

- 1. Assert the avl\_csr\_write or avl\_csr\_read signal while the avl\_csr\_waitrequest signal is low (if the waitrequest signal is high, the avl\_csr\_write or avl\_csr\_read signal must to be kept high until the waitrequest signal goes low).

- 2. At the same time, set the address value on the avl\_csr\_address bus. If it is a write operation, set the value data on the avl\_csr\_writedata bus together with the address.

- 3. If it is a read transaction, wait until the avl\_csr\_readdatavalid signal is asserted high to retrieve the read data.

- · For operations that require write value to flash, you must perform the write enable operation first.

- · You must read the flag status register every time you issue a write or erase command.

- If multiple flash devices are used, you must write to the chip select register to select the correct chip select before performing any operation to the specific flash device.

Figure 2. Read Memory Capacity Register Waveform Example

Figure 3. Write Enable Register Waveform Example

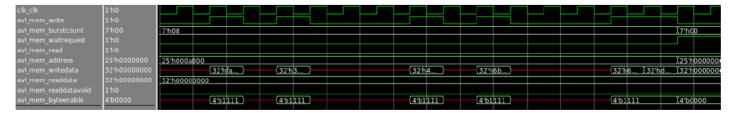

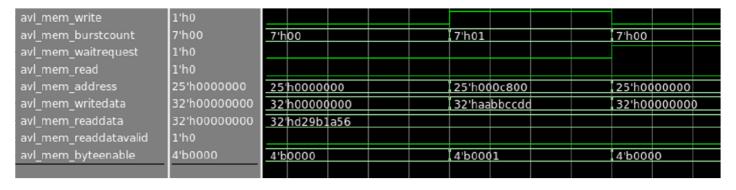

## **Memory Operations**

The ASMI Parallel II Intel FPGA IP memory interface supports bursting and direct flash memory access. During the direct flash memory access, the IP performs the following steps to allow you to perform any direct read or write operation:

- · Write enable for the write operation

- · Check flag status register to make sure the operation has been completed at the flash

- Release the waitrequest signal when the operation is completed

Memory operations are similar to the Avalon memory-mapped interface operations. You must set the correct value at the address bus, write data if it is a write transaction, drive the burst count value to 1 for single transaction or your desired burst count value, and trigger the write or read signal.

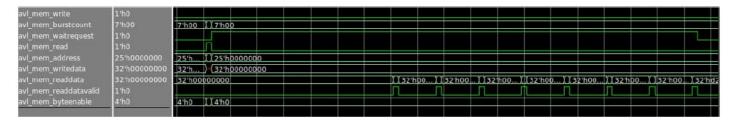

Figure 4. 8-Word Write Burst Waveform Example

Figure 5. 8-Word Reading Burst Waveform Example

Figure 6. 1-Byte Write byteenable = 4'b0001 Waveform Example

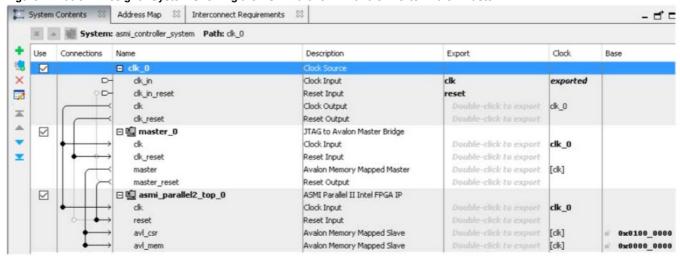

The use case examples use the ASMI Parallel II IP and JTAG-to-Avalon Master to perform flash access operations, such as read silicon ID, read memory, write memory, sector erase, sector protect, clear flag status register, and write nvcr.

To run the examples, you must configure the FPGA. Follow these steps:

1. Configure the FPGA based on Platform Designer system as shown in the following figure.

Figure 7. Platform Designer System Showing the ASMI Parallel II IP and JTAG-to-Avalon Master

2. Save the following TCL script in the same directory as your project. Name the script as epcq128 access.tcl for example.

```

#invoked by Tcl code that wishes to use a particular version of a

#particular package

package require Tcl 8.5

#set base address according to Platform Designer system

set base 0x01000000

#set the variables to their respective offset

set wr_enable

set wr_disable

{$base +

[expr

[expr

$base +

0x4

set wr_status

set rd status

[expr

$base +

0x8

[expr

$base +

0xc}]

$base +

set sector erase

[expr

0x10

set subsector_erase

[expr

$base +

0x14

set control

[expr

$base +

0x20

set wr_non_volatile_conf_reg

set rd_non_volatile_conf_reg

[expr

$base +

0x34

[expr

$base +

0x38

set rd flag status reg

$base +

0x3c

[expr

set clr_flag_status_reg

$base +

0x40

[expr

set bulk_erase

[expr

$base +

0x44

set die_erase

set 4bytes_addr_en

$base +

0x48

[expr

[expr

$base +

0x4c

set 4bytes_addr_ex

[expr

$base +

0x50

[expr

set sector_protect

$base +

0x54

[expr {$base + 0x58}]

set rd_memory_capacity_id

#assign variable mp to the string that is the 0th element in the list

#returned by get_service_paths master

set mp [lindex [get_service_paths master] 0]

#procedure to open the connection to the master module

proc start_service_master { } {

global mp

open_service master $mp

#procedure to close the connection to the master module

proc stop_service_master {} {

global mp

close_service master $mp

#read silicon id from RD MEMORY CAPACITY ID register

proc read_silicon_id {} {

global mp rd_memory_capacity_id

set id [master_read_32 $mp $rd_memory_capacity_id 1]

puts $id

```

```

#read status register from RD_STATUS register

proc read status register {} {

global mp rd status

set status [master_read_32 $mp $rd_status 1]

puts $status

#write 1 to WR_ENABLE register to perform write enable

proc write_enable {}

global mp wr_enable

master_write_32 $mp $wr_enable 1

#applicable for EPCQ256 or EPCQ512/A only

proc enable_4byte_addressing {} {

global mp 4bytes_addr_en

master_write_32 $4bytes_addr_en 1

}

#applicable for EPCQ256 or EPCQ512/A only

proc exit 4byte addressing {} {

global mp 4bytes_addr_ex

master_write_32 $4bytes_addr_ex 1

#memory read

proc read memory {addr bytes_size} {

global mp

master_read_32 $mp $addr $bytes_size}

#wait until WIP bit in status register is ready after issue write_memory

proc write_memory {addr data} {

global mp

master_write_32 $mp $addr $data

}

#wait until WIP in status register is ready after issue erase_sector

proc erase_sector {sector_addr} {

global mp sector_erase

master_write_32 $mp $sector_erase $sector_addr

proc erase_bulk {} {

global mp bulk_erase

master_write_32 $mp $bulk_erase 1

#modify Block Protect Bit and Top/Bottom Bit in Status Register to perform

#block protect

#wait until WIP bit in status register is ready after issue sector_protect

proc sector_protect {block_protect} {

global mp sector_protect

write enable

master write 32 $mp $sector protect $block protect

proc read_nvcr {} {

global mp rd_non_volatile_conf_reg

master_read_32 %mp %rd_non_volatile_conf_reg 1

#not applicable for EPCQA

#not applicable for secon

proc read_flag_status_reg {} {

global mp rd_flag_status_reg

master_read_32 %mp %rd_flag_status_reg 1

}

#not applicable for EPCQA

proc clear_flag_status_reg {value} {

global mp clr_flag_status_reg

write_enable

master_write_32 $mp $clr_flag_status_reg $value

}

#write NVCR[15:0]

#wait until WIP bit in status register is ready after issue write_nvcr

proc write_nvcr {value} {

global mp wr_non_volatile_conf_reg

write_enable

master_write_32 $mp $wr_non_volatile_conf_reg $value

}

#calling the start_service_master procedure

start_service_master

```

3. Launch system console. In the console, source the script by using "source epcq128\_access.tcl".

## Example 1: Read the Silicon ID of the Configuration Devices

```

#system console prints silicon id

read_silicon_id

```

### Example 2: Read and Write One Word of Data at Address H'40000000

```

#ensure system console prints 0xffffffff to indicate the address is empty of

#data

read memory 0x40000000 1

#write 0xabcd1234 into address H'40000000

write_memory 0x40000000 0xabcd1234

#read back data to ensure it is successful written into the address

read_memory 0x40000000 1

```

## Example 3: Erase Sector 64

```

#Issue any addresses within sector 64 to erase the sector

erase_sector 0x40000000

#read back data at address H'40000000 to ensure it is successful erased

read_memory 0x40000000 1

```

#### Example 4: Perform Sector Protect at Sectors (0 to 127)

```

#If the sector is not protected with TB bit set to 0, system console prints #0x00000000 read_status_register #Execute sectors (0 to 127) protection. Refer to datasheet for block #protection bit. sector_protect 0x000000000 #read back status register to check whether sectors(0 to 127) are protected, #system console prints 0x000000000 read_status_register

```

### **Example 5: Read and Clear Flag Status Register**

```

#If there is no errors, system console prints 0x000000000

read_flag_status_reg

#Attempt to write data on protected sector

write_memory 0x40000000 0xabcd1234

#Bit 0 and Bit 4 of flag status register will set to 1 indicates program

#operation has failed and program operation has attempted to modify the

#protected array respectively

read_flag_status_reg

#set bit 0 and bit 4 to 0 to clear the error bit

clear_flag_status_reg 0x000000000

#read back flag status register to confirm the error bits are cleared

read_flag_status_reg

```

### **Example 6: Read and Write nvcr**

```

#Bit 15:12 indicates number of dummy clock cycles

read_nvcr

#Change dummy cycles to 8

write_nvcr 0x8fff

#Read back non-volatile configuration register to confirm the dummy cycles is

#changed

read_nvcr

```

### **ASMI Parallel II Intel FPGA IP User Guide Archives**

IP versions are the same as the Intel Quartus Prime Design Suite software versions up to v19.1. From Intel Quartus Prime Design Suite software version 19.2 or later, IP cores have a new IP versioning scheme.

If an IP core version is not listed, the user guide for the previous IP core version applies.

| Intel Quartus Prime<br>Version | IP Core Version | User Guide                                 |

|--------------------------------|-----------------|--------------------------------------------|

| 17 0                           | 17.0            | Altera ASMI Parallel II IP Core User Guide |

Document Revision History for the ASMI Parallel II Intel FPGA IP User Guide

| Document Version | Intel Quartus<br>Prime Version | IP Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020.07.29       | 18.0                           | 18.0       | <ul> <li>Updated the document title to ASMI Parallel II Intel FPGA IP User Guide.</li> <li>Updated Table 2: Parameter Settings in section Parameters.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2018.09.24       | 18.0                           | 18.0       | <ul> <li>Added information on the applications and support for the ASMI Parallel II Intel FPGA IP core.</li> <li>Added a note to refer to the <i>Generic Serial Flash Interface Intel FPGA IP Core User Guide.</i></li> <li>Added the <i>ASMI Parallel II Intel FPGA IP Core Use Case Examples</i> section.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

| 2018.05.07       | 18.0                           | 18.0       | <ul> <li>Renamed Altera ASMI Parallel II IP core to ASMI Parallel II Intel FPGA IP core per Intel rebranding.</li> <li>Added support for EPCQ-A devices.</li> <li>Added a note to the clk signal in the <i>Ports Description</i> table.</li> <li>Updated the description for the qspi_scein signal in the <i>Ports Description</i> table.</li> <li>Added a note to the SECTOR_PROTECT register in the <i>Register Map</i> table.</li> <li>Updated the bit and width for SECTOR_ERASE and SUBSECTOR_ERASE registers in the <i>Register Map</i> table.</li> <li>Updated the bit and width for SECTOR_PROTECT register in the <i>Register Map</i> table.</li> </ul> |

continued...

**Document Version**

Intel Quartus

Prime Version

**IP Version**

### Changes

- Updated the description for the CHIP SELECT option of the CONTROL register in the Register Map table.

- Updated the footnotes for the SECTOR\_ERASE, SUBSECTOR\_ERASE, BULK\_ERASE, and DIE\_ERASE registers in the Register Map table.

- · Updated the description for the vl\_mem\_addr

signal in the Ports Description table.

· Minor editorial edits.

DateVersionChangesMay 20172017.05.08Initial release.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

#### **Documents / Resources**

intel ASMI Parallel II Intel FPGA IP [pdf] User Guide

ASMI Parallel II Intel FPGA IP, ASMI, Parallel II Intel FPGA IP, II Intel FPGA IP, FPGA IP

Controller some

### References

- intel 1. Quad-Serial Configuration (EPCQ) Devices Datasheet

- intel 1. Simulating the ASMI Block in Your Design

- intel Intel® Quartus® Prime Software User Guides

- intel 1. Introduction to Intel® FPGA IP Cores

- intel 1. Introduction to Intel® FPGA IP Cores

- intel 1. Introduction to the Avalon® Interface Specifications

- intel 1. ASMI Parallel Intel® FPGA IP Core User Guide

- intel\_1. EPCQ-A Serial Configuration Device Datasheet

- intel 1. Generic Serial Flash Interface Intel® FPGA IP User Guide

- intel EPCQ-L Serial Configuration Devices Datasheet

- intel ISO 9001:2015 Registrations

#### Manuals+,

- home

- privacy