# intel Accelerator Functional Unit Simulation Environment Software User Guide

Home » Intel » intel Accelerator Functional Unit Simulation Environment Software User Guide 12

#### **Contents**

- 1 About this Document

- 2 System Requirements

- 3 Setting Up the Environment

- 4 Simulating hello\_afu in Client-Server Mode

- **5 AFU Examples**

- 6 Troubleshooting

- 7 ASE Quick Start User Guide Archives

- 8 Document Revision History for ASE Quick Start User Guide

- 9 Documents / Resources

- 9.1 References

- **10 Related Posts**

## **About this Document**

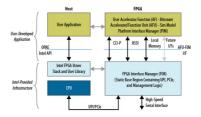

This document describes how to simulate a sample Accelerator Functional Unit (AFU) using the Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) environment. Refer to the Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide for comprehensive details on ASE capabilities and internal architecture.

The Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) is a hardware and software cosimulation environment for any Intel FPGA Programmable® Acceleration Card (Intel FPGA PAC). This software co-simulation environment currently supports the following Intel FPGA PACs: 10 GX FPGA

- Intel FPGA Programmable Acceleration Card D5005

- Intel Programmable Acceleration Card with Intel Arria®

The ASE provides a transactional model for the Core Cache Interface (CCI-P) protocol and a memory model for the FPGA-attached local memory.

The ASE also validates Accelerator Functional Unit (AFU) compliance to the following protocols and APIs:

- The CCI-P protocol specification

- · The Avalon

Memory Mapped (Avalon-MM) Interface Specification

• The Open Programmable Acceleration Engine (OPAE)®

Table 1. Acceleration Stack for Intel Xeon® CPU with FPGAs Glossary

| Term                                                        | Abbreviation       | Description                                                                                                                                                  |

|-------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Acceleration Stack for Intel Xeon® CPU with FPGAs     | Acceleration Stack | A collection of software, firmware and tools that provi<br>des performance-optimized connectivity between an I<br>ntel FPGA and an Intel Xeon processor.     |

| Intel FPGA Programmable Accel eration Card (Intel FPGA PAC) | Intel FPGA PAC     | PCIe* FPGA accelerator card. Contains an FPGA Interface Manager (FIM) that pair s with an Intel Xeon processor over a PCIe bus.                              |

| Intel Xeon Scalable Platform with Integrated FPGA Pl atform |                    | Intel Xeon plus FPGA platform with the Intel Xeon and an FPGA in a single package and sharing a cohere nt cache of memory via Ultra Path Interconnect (UPI). |

## **Related Information**

Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants the performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

# **System Requirements**

Here are the system requirements for Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE)::

- A 64-bit Linux operating system. This release validated the following operating systems:

- For Intel FPGA PAC D5005:

- RHEL 7.6 with Kernel 3.10.0-957

- For Intel PAC with Intel Arria 10 GX FPGA:

- RHEL 7.6 with Kernel 3.10.0-957

- Ubuntu 18.04 with Kernel 4.15

- One of the following simulators:

- 64-bit Synopsys\* VCS-MX-2016.06-SP2-1 RTL Simulator

- 64-bit Mentor Graphics\* Modelsim SE Simulator (Version 10.5c)

- 64-bit Mentor Graphics QuestaSim Simulator (Version 10.5c)

- C compiler: GCC 4.7.0 or above

- CMake: version 2.8.12 or above

- GNU C Library: version 2.17 or above

- Python: version 2.7

- Intel Quartus® Prime Pro Edition software version 19.2 (1)

# **Setting Up the Environment**

You must set up your simulation environment and install the OPAE software before running the ASE.

- 1. Set the following environment variables for your simulation software:

- · For VCS:

```

$ export VCS_HOME=<path to VCS installation directory>

```

```

$ export PATH=$VCS HOME/bin:$PATH

```

The VCS installation directory structure is as follows:

```

suse32

admin

bin

etc

gnu

include

linux

vcfca

vgcommon

install.log

suse64

flexlm gui

linux64

doc

packages

verific

```

Make sure your system has a valid VCS license.

## • For Modelsim SE/QuestaSim:

\$ export MTI\_HOME=<path to Modelsim installation directory>

\$ export PATH=\$MTI\_HOME/linux\_x86\_64/:\$MTI\_HOME/bin/:\$PATH

The Modelsim/Questa installation directory structure is as follows:

```

LICENSE

mpich2

vhdlopt lib

sv std

uvm-1.1d

ieee

src

gcc-4.3.3-linux

ieee env

linux

msidata

RELEASE_NOTES

uvm-1.2

synopsys

cov src

gcc-4.3.3-linux x86 64

ieeepure

linux x86 64

osver

RELEASE NOTES.html

uvmc-2.3.1

vital1995

tcl.fs

upf_lib

upf_src

gcc-4.5.0-linux

gcc-4.5.0-linux_x86_64

docs

include

mc2_lib

OSVVM

RELEASE NOTES.txt

uvm_reg-1.1

vital2000

drill src

ovm-2.1.1

infact

vital2.2b

mac ams

VCO

4-linux

modelsim.ini

ovm-2.1.2

verilog

keyring

floatfixlib gcc-4.7.4-linux x86 64

modelsim lib pa lib

std developerskit

verilog src

```

Make sure your system has a valid Modelsim SE/QuestaSim license.

#### • For Intel Quartus Prime Pro Edition:

\$ export QUARTUS\_HOME=<path to Intel Quartus Prime Pro Edition installation directory

The Intel Quartus Prime installation directory structure is as follows:

```

adm common drivers dsp_builder extlibs32 linux64 qdesigns sopc_builder bin cusp dspba eda libraries lmf readme.txt version.txt

```

Add the environment variable to check the Modelsim license:

\$ export MGLS\_LICENSE\_FILE=<Modelsim License>

2. Export:

\$ export LM LICENSE FILE=<Quartus Prime License>

Extract the runtime archive file, and install OPAE libraries, binaries, include files, and ASE libraries as

described in the section: Installing the OPAE Software Package in the appropriate Intel Acceleration Stack

Quick Start User Guide for your Intel FPGA PAC.

Your environment must be set up correctly to configure and build an AFU. In particular, you must install the OPAE Software Development Kit (SDK) properly. OPAE SDK scripts must be on PATH and include files and libraries that must be available to the C compiler. In addition, you must ensure that the OPAE\_PLATFORM\_ROOT environment variable is set. Refer to Installing the OPAE Software Package for more information.

To ensure that the OPAE SDK and ASE are properly installed, in a shell, confirm that your PATH includes

afu\_sim\_setup. The afu\_sim\_setup should be in the /usr/bin directory or in <opae install path> if you built the OPAE from source files.

#### **Related Information**

- Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

- Installing the OPAE Software Package

For Intel PAC with Intel Arria 10 GX FPGA.

- Installing the OPAE Software Package For Intel FPGA PAC D5005.

## Simulating hello\_afu in Client-Server Mode

The hello\_afu example is a simple AFU template that demonstrates the primary CCI-P interface. The RTL satisfies the minimum requirements of an AFU, responding to memory-mapped I/O reads to return the device feature header and the AFU's UUID.

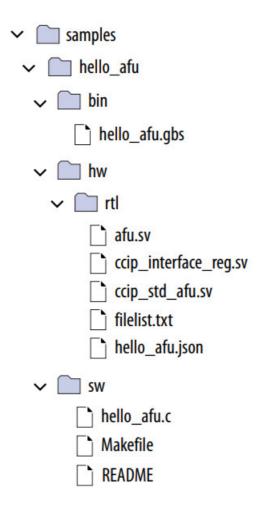

Figure 1. hello\_afu Directory Tree

#### Note:

This document uses <AFU example> to refer to an example design directory, such as hello\_afu in the figure above.

The software demonstrates the minimum requirements to attach to an FPGA using the OPAE. The RTL demonstrates the minimum requirements to satisfy the OPAE driver and the hello\_afu example software. filelist.txt specifies the files for RTL simulation and synthesis.

To successfully configure and build the AFU samples, your environment must be set up correctly, as described in Setting Up the Environment.

#### **Related Information**

- Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

- Setting Up the Environment on page 5

## **Developing AFUs with the OPAE SDK**

In the Accelerator Functional Unit (AFU) Developer's Guide

#### 4.1. Simulation in Client-Server Mode

The following example flow introduces the basic ASE scripts. You can simulate all examples with the ASE, except eth e2e e10 and eth e2e e40.

The simulation requires two software processes: one process for RTL simulation and a second process to run the connected software. To construct an RTL simulation environment, run the following in \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu:

\$ afu\_sim\_setup -source hw/rtl/filelist.txt build\_sim

This command constructs an ASE environment in the build\_sim subdirectory.

To build and run the simulator:

\$ cd build sim

\$ make

\$ make sim

The simulator prints a message that it is ready for simulation. It also prints a message prompting you to set the ASE WORKDIR environment variable.

Open another shell for software simulation. You must ensure to set the OPAE\_PLATFORM\_ROOT environment variable.

To build and run the software in the new shell:

\$ cd \$OPAE PLATFORM ROOT

\$ export ASE WORKDIR=\$OPAE PLATFORM ROOT/hw/samples/hello afu/build sim/work

\$ cd \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/sw

\$ make clean

\$ make USE ASE=1

\$./hello afu

#### Note:

The specific pathname for ASE\_WORKDIR may vary. Use the pathname provided by the simulator prompt. The software and simulator run, log transactions, and exit.

## 4.1.1. Simulation Log Files

The simulation work directory stores the waveform, CCI-P transactions, and simulation log files. Complete the following steps to view the waveform database:

- 1. Change to the directory in which you executed the make sim command.

- 2. Type:

\$ make wave

The make wave command invokes the waveform viewer.

# 4.1.2. Design Declarations

The following file and directories define the AFU simulation:

- \$OPAE PLATFORM ROOT/hw/samples/<AFU example>/hw/rtl/filelist.txt specifies RTL sources.

- <AFU example> is the example directory as shown in the hello afu Directory Tree figure.

- filelist.txt lists SystemVerilog, VHDL, and the AFU JavaScript Object Notation (.json) file.

- The AFU .json describes the interfaces the AFU requires. It also includes a UUID to identify the AFU once downloaded to an FPGA.

- hw/rtl/hello\_afu.json defines ccip\_std\_afu as the top-level interface by setting afu-top-interface to ccip\_std\_afu.

ccip\_std\_afu is the base CCI-P interface including clocks, reset, and CCI-P TX and RX structures. More advanced examples define other interface options.

- The .json file declares the AFU UUID. An OPAE script generates the UUID. The RTL loads the UUID from afu json info.vh.

- sw/Makefile generates afu json info.h. The software loads the UUID from afu json info.h.

# 4.1.3. Troubleshooting Client-Server Simulation

If the afu\_sim\_setup command fails, confirm that:

- afu\_sim\_setup is on your PATH. afu\_sim\_setup should be in /usr/bin or in <opae install path> if you built OPAE from source files.

- You have Python version 2.7 or higher installed.

If you are unable to build and execute the simulator, it is likely that you did not install your RTL simulation tool properly.

When you try to build and run the software, if you see an "Error enumerating AFCs" message, you omitted setting USE\_ASE=1 on the make command line. The software is searching for a physical FPGA device. To recover, repeat the steps from the make clean command.

## **AFU Examples**

#### Table 2.

#### **AFU Examples**

Each AFU example includes a detailed README file, providing an operational description and notes on how to simulate the design. For a full understanding of the simulation process, review the README file in each AFU example.

| AFU               | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| hello_mem_afu     | hello_mem_afu demonstrates an AFU that builds a simple state machine to access m emory. The state machine is capable of several access patterns to local memory directly attached to FPGA pins, such as DDR4 DIMMs. This memory is distinct from the host memory accessed over CCI-P. The host manages the hello_mem_afu controller state machine using memory-mapped I/O (MMIO) requests to control and status register s (CSRs). |  |  |

| hello_intr_afu    | hello_intr_afu demonstrates the application interrupt feature in the ASE.                                                                                                                                                                                                                                                                                                                                                          |  |  |

| DMA an f1.1 (2) _ | dma_afu demonstrates a DMA Basic Building Block for host to FPGA, FPGA to host, and FPGA to FPGA memory transfers. When simulating this AFU, the buffer size use d for DMA transfer is small to keep the simulation time reasonable. For more informati on, refer to the DMA Accelerator Functional Unit (AFU) User Guide.                                                                                                         |  |  |

| nlb_mode_O        | nlb_mode_O is a CCI-P system demonstrating the memory copy test. \$0PAE_PLA TFORM_ROOT/ sw/opae—cre/ease number>/sample/hello_fpga . c includes nlb_mode_0.                                                                                                                                                                                                                                                                        |  |  |

|                   | \$ sh regress.sh -a <afu dir=""> -r rtl_sim -s &lt; vcslmodelsimlquesta &gt; [-i <opae install="" path="">) -b <path dir="" opae="" source="" to=""></path></opae></afu>                                                                                                                                                                                                                                                           |  |  |

| streaming_dma     | streaming_dma demonstrates how to transfer data between host memory and an FP GA streaming port. For more information, refer to the Streaming DMA Accelerator Fur ctional Unit (AFU) User Guide.                                                                                                                                                                                                                                   |  |  |

| hello_afu         | hel lo_a fu is a simple AFU that demonstrates the primary CCI-P interface. The RTL s atisfies the bare minimum requirements of an AFU, responding to MMIO reads to return the device feature header and the AFU's UUID.                                                                                                                                                                                                            |  |  |

## **Related Information**

- DMA Accelerator Functional Unit (AFU) User Guide

For information on how to compile and execute the dma\_afu on your Intel PAC with Intel Arria 10 GX FPGA.

- Streaming DMA Accelerator Functional Unit (AFU) User Guide

For information on how to compile and execute the streaming\_dma\_afu on your Intel PAC with Intel Arria 10 GX FPGA.

- DMA Accelerator Functional Unit User Guide: Intel FPGA Programmable Acceleration Card D5005 For information on how to compile and execute the dma\_afu on your Intel FPGA PAC D5005.

- Streaming DMA Accelerator Functional Unit User Guide: Intel FPGA Programmable Acceleration Card D5005 For information on how to compile and execute the dma\_afu on your Intel FPGA PAC D5005.

# **Troubleshooting**

If the following error appears during the simulation, correct it by following the steps below. Error Message

- # [SIM] An ASE instance is probably still running in the current directory!

- # [SIM] Check for PID 28816

- # [SIM] Simulation will exit... you may use a SIGKILL to kill the simulation process.

- # [SIM] Also check if .ase\_ready.pid file is removed before proceeding. Solution

- 1. Type kill ase\_simv to kill zombie simulation processes and remove any temporary files left behind by failed simulation processes or lock ups.

- 2. Delete the .ase\_ready.pid file, found in the \$ASE\_WORKDIR directory.

# **ASE Quick Start User Guide Archives**

| Intel Acceleration<br>Stack Version | User Guide                                                                                  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| 2.0                                 | Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) Quick Start User Guide |  |  |

| 1.                                  | Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) Quick Start User Guide |  |  |

| 1.                                  | Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) Quick Start User Guide |  |  |

| 1.0                                 | Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) Quick Start User Guide |  |  |

# **Document Revision History for ASE Quick Start User Guide**

| Document Ver sion | Intel Acceleration Stack<br>Version | Changes                                                                                                                                                                                                                                                                            |

|-------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020.03.06        | 1.2.1 and 2.0.1                     | Updated the following: • System Requirements                                                                                                                                                                                                                                       |

| 2019.08.05        | 2.0                                 | <ul> <li>Updated the Intel Quartus Prime Pro Edition version in System Requirements.</li> <li>Added the hello_afu in AFU Examples.</li> <li>Removed information about simulating in regression mode.</li> <li>Added a new section: ASE Quick Start User Guide Archives.</li> </ul> |

| 2018.12.04        | 1.                                  | Added Ubuntu support.                                                                                                                                                                                                                                                              |

| 2018.08.06        | 1.                                  | Updated the system requirements, directory structure, and corres ponding filenames.                                                                                                                                                                                                |

| 2018.04.10        | 1.0                                 | Initial release.                                                                                                                                                                                                                                                                   |

683200 | 2020.03.06

**Documents / Resources**

<u>intel Accelerator Functional Unit Simulation Environment Software</u> [pdf] User Guide Accelerator Functional Unit, Simulation Environment Software, Accelerator Functional Unit Simulation Environment, Software, Accelerator Functional Unit Simulation Environment Software

# References

- Ontel® Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide OPAE

- intel 1. About this Document

- intel ISO 9001:2015 Registrations

Manuals+,