# **GOWIN GW1NRF Series Bluetooth FPGA User Guide**

Home » GOWIN » GOWIN GW1NRF Series Bluetooth FPGA User Guide 🖫

#### **Contents**

- 1 GOWIN GW1NRF Series Bluetooth FPGA

- 2 Disclaimer

- 3 Purpose

- **4 Related Documents**

- **5 Terminology and Abbreviations**

- 6 Support and Feedback

- **7 Overview**

- 7.1 Package, Max. User I/O Information, and LVDS Paris

- 7.2 Power Pin

- **8 Pin Quantity**

- 8.1 Quantity of GW1NRF-4B Pins

- 9 Pin Definitions

- 9.1 I/O BANK Introduction

- 10 View of Pin Distribution

- 10.1 View of GW1NRF-4B Pins Distribution

- 11 Package Diagrams

- 12 Documents / Resources

- 12.1 References

- **13 Related Posts**

#### **GOWIN GW1NRF Series Bluetooth FPGA**

Copyright © 2019 Guangdong Gowin Semiconductor Corporation. All Rights Reserved., LittleBee, and GOWIN are trademarks of Guangdong Gowin Semiconductor Corporation and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

### **Disclaimer**

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date       | Version | Description                |

|------------|---------|----------------------------|

| 11/12/2019 | 1.0E    | Initial version published. |

### **Purpose**

This manual contains an introduction to the GW1NRF series of Bluetooth FPGA products together with a definition of the pins, list of pin numbers, distribution of pins, and package diagrams.

#### **Related Documents**

The latest user guides are available on the GOWINSEMI Website. You can find the related documents at <a href="https://www.gowinsemi.com">www.gowinsemi.com</a>:

- 1. DS891, GW1NRF series of Bluetooth FPGA products Data Sheet

- 2. UG290, Gowin FPGA Products Programming and Configuration User Guide

- 3. UG893, GW1NRF series of Bluetooth FPGA products Package and Pinout

- 4. UG892, GW1NRF-4B Pinout

### **Terminology and Abbreviations**

The terminology and abbreviations used in this manual are as shown in Table 1-1 below. Table 1-1 Abbreviation and Terminology

| Terminology and Abbreviations | Full Name                     |

|-------------------------------|-------------------------------|

| FPGA                          | Field Programmable Gate Array |

| SIP                           | System in Package             |

| GPIO                          | Gowin Programmable IO         |

| QN48                          | QFN48                         |

| QN48E                         | QFN48E                        |

### Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: <a href="mailto:www.gowinsemi.com.cn">www.gowinsemi.com.cn</a></a><a href="mailto:com.cn">cn</a><a href="mailto:com.cn">com.cn</a><a href="mailto:com.cn">com.cn</a><a

#### Overview

The GW1NRF series of FPGA products are the first generation products in the LittleBee® family and represent one form of SoC FPGA. The GW1NRF series of FPGA products integrate 32 bits hardcore processor and support Bluetooth 5.0 Low Energy radio. They have abundant logic units, IOs, built-in B-SRAM and DSP resources, power management module, and security module. The GW1NRF series provides low power consumption, instant on, low cost, non-volatile, high security, various packages, and flexible usage.

#### **PB-Free Package**

The GW1NRF series of Bluetooth FPGA products are PB free in line with the EU ROHS environmental directives. The substances used in the GW1NRF series of Bluetooth FPGA products are in full compliance with the IPC-1752 standards.

#### Package, Max. User I/O Information, and LVDS Paris

Table 2-1 Package, Max. User I/O Information, and LVDS Paris

| Package | Pitch (mm) | Size (mm) | GW1NRF-4B |

|---------|------------|-----------|-----------|

| QN48    | 0.4        | 6 x 6     | 25(4)     |

| QN48E   | 0.4        | 6 x 6     | 25(4)     |

#### Note!

- In this manual, abbreviations are employed to refer to the package types. See 1.3Terminology and Abbreviations.

- See GW1NRF series of Bluetooth FPGA Products Data Sheet for more details.

- The JTAGSEL\_N and JTAG pins cannot be used as I/O simultaneously. The data in this table is when the loaded four JTAG pins (TCK, TDI, TDO, and TMS) are used as I/O;

#### **Power Pin**

#### Table 2-2 Other Pins in the GW1NRF Series

| VCC   | VCCO0 | VCCO1 | VCCO2 |

|-------|-------|-------|-------|

| VCCO3 | VCCX  | VSS   |       |

## **Pin Quantity**

**Quantity of GW1NRF-4B Pins**

Table 2-3 Quantity of GW1NRF-4BPins

| Pin Type                               |                  | GW1NRF-4B |       |

|----------------------------------------|------------------|-----------|-------|

|                                        |                  | QN48      | QN48E |

|                                        | BANK0            | 9/4/0     | 9/4/0 |

| I/O Single end / Differential pair / L | BANK1            | 4/1/1     | 4/1/1 |

| VDS1                                   | BANK2            | 8/4/3     | 8/4/3 |

|                                        | BANK3            | 4/1/0     | 4/1/0 |

| Max. User I/O 2                        |                  | 25        | 25    |

| Differential Pair                      |                  | 10        | 10    |

| True LVDS output                       | True LVDS output |           | 4     |

| VCC                                    | vcc              |           | 2     |

| VCCX                                   |                  | 1         | 1     |

| VCCO0/VCCO33                           |                  | 1         | 1     |

| VCCO1/VCCO23                           |                  | 1         | 1     |

| VSS                                    |                  | 2         | 1     |

| MODE0                                  |                  | 0         | 0     |

| MODE1                                  |                  | 0         | 0     |

| MODE2                                  |                  | 0         | 0     |

| JTAGSEL_N                              |                  | 1         | 1     |

#### Note!

- 1. The number of single end/ differential/LVDS I/O includes CLK pins and download pins;

- 2. The JTAGSEL\_N and JTAG pins cannot be used as I/O simultaneously. The data in this table is when the loaded four JTAG pins (TCK, TDI, TDO, and TMS) are used as I/O; When mode [2:0] = 001, JTAGSEL\_N and the four JTAG pins (TCK, TDI, TDO, and TMS) can be used as GPIO simultaneously, and the Max. user I/O plus one.

- 3. Pin multiplexing.

### **Pin Definitions**

The location of the pins in the GW1NRF series of Bluetooth FPGA products varies according to the different packages. Table 2-4 provides a detailed overview of user I/O, multi-function pins, dedicated pins, and other pins.

Table 2-4 Definition of the Pins in the GW1NRF series of Bluetooth FPGA products

| Pin Name      | I/O | Description |

|---------------|-----|-------------|

| Max. User I/O |     |             |

|                                     |                  | [End] indicates the pin location, including L(left) R(right) B(b ottom), and T(top)                                                                                                                                                                                                                         |  |

|-------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IO[End][Row/Column<br>Number][A/B]  | I/O              | [Row/Column Number] indicates the pin Row/Column numb er.If [End] is T(top) or B(bottom), the pin indicates the colum n number of the corresponding CFU. If [End] is L(left) or R(right), the pin indicates the Row number of the corresponding CFU.  [A/B] indicates differential signal pair information. |  |

| Multi-Function Pins                 |                  |                                                                                                                                                                                                                                                                                                             |  |

| IO[End][Row/Column Number][A/B]/MMM |                  | /MMM represents one or more of the other functions in addition to being general purpose user I/O. These pins can be used as user I/O when the functions are not used.                                                                                                                                       |  |

| RECONFIG_N                          | I, internal weak | Start new GowinCONFIG mode when low pulse                                                                                                                                                                                                                                                                   |  |

| READY                               | I/O              | High level indicates the device can be programmed and configured currently  Low level indicates the device cannot be programmed and configured currently                                                                                                                                                    |  |

| DONE                                | I/O              | High level indicates successful program and configure  Low level indicates incomplete or failed to program and configure                                                                                                                                                                                    |  |

| FASTRD_N /D3                        | I/O              | In MSPI mode, FASTRD_N is used as Flash access speed port. Low indicates high-speed Flash access mode; high indicates regular Flash access mode.  Data port D3 in CPU mode                                                                                                                                  |  |

| MCLK /D4                            | I/O              | Clock output MCLK in MSPI mode Data port D4 in CPU mode                                                                                                                                                                                                                                                     |  |

| MCS_N /D5                           | I/O              | Enable signal MCS_N in MSPI mode, active-low  Data port D5 in CPU mode                                                                                                                                                                                                                                      |  |

| MI /D7                              | I/O              | MISO in MSPI mode: Master data input/Slave data output  Data port D7 in CPU mode                                                                                                                                                                                                                            |  |

| MO /D6                              | I/O              | MISO in MSPI mode: Master data output/Slave data input  Data port D6 in CPU mode                                                                                                                                                                                                                            |  |

| SSPI_CS_N/D0 | I/O | Enable signal SSPI_CS_N in SSPI mod, active-low, Internal Weak Pull Up  Data port D0 in CPU mode |

|--------------|-----|--------------------------------------------------------------------------------------------------|

| SO/D1        | I/O | MISO in MSPI mode: Master data input/Slave data                                                  |

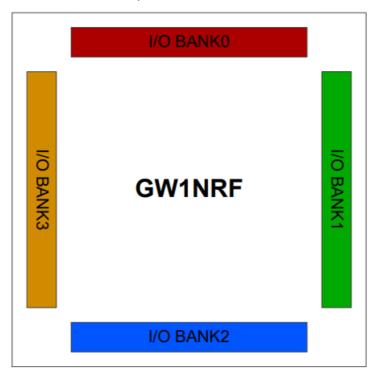

#### I/O BANK Introduction

There are four I/O Banks in the GW1NRF series of FPGA products. The I/O BANK Distribution of the GW1NRF series of Bluetooth FPGA products is as shown in Figure 2-1.

Figure 2-1GW1NRF series of Bluetooth FPGA products I/O Bank Distribution

This manual provides an overview of the distribution view of the pins in the GW1NRF series of Bluetooth FPGA products. The four I/O Banks that form the GW1NRF series of Bluetooth FPGA products are marked with four different colors.

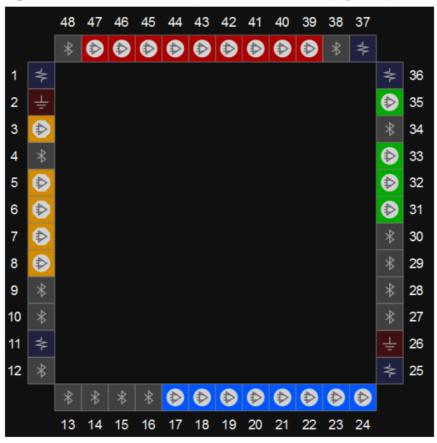

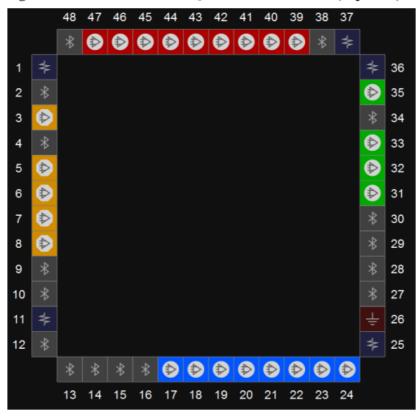

Various symbols are used for the user I/O, power, and ground. The various symbols and colors used for the various pins are defined as follows:

- " denotes the I/O in BANK0. The filling color changes with the BANK;

- denotes the I/O in BANK1. The filling color changes with the BANK;

- " **🔁** "

- "denotes the I/O in BANK2. The filling color changes with the BANK;

- "denotes the I/O in BANK3. The filling color changes with the BANK;

- "denotes VCC, VCCX, and VCCO. The filling color does not change;

- " denotes VSS, the filling color does not change;

- denotes NC;

- " denotes BLE, the filling color does not change.

### **View of Pin Distribution**

View of GW1NRF-4B Pins Distribution

### **View of QN48 Pins Distribution**

Figure 3-1 View of GW1NRF-4B QN48 Pins Distribution (Top View)

Table 3-1 Other pins in GW1NRF-4B QN48

| VCC         | 11,37 |

|-------------|-------|

| VCCX        | 36    |

| VCCO0/VCCO3 | 1     |

| VCCO1/VCCO2 | 25    |

| VSS         | 26,2  |

**View of QN48E Pins Distribution**

Figure 3-2 View of GW1NRF-4B QN48E Pins Distribution (Top View)

Table 3-2 Other pins in GW1NRF-4B QN48

| VCC         | 11,37 |

|-------------|-------|

| VCCX        | 36    |

| VCCO0/VCCO3 | 1     |

| VCCO1/VCCO2 | 25    |

| VSS         | 26    |

### **Package Diagrams**

### QN48 Package Outline (6mm x 6mm)

|        | MILLIMETER |      |      |

|--------|------------|------|------|

| SYMBOL | MIN        | NOM  | MAX  |

| Α      | 0.75       | 0.85 | 0.85 |

| A1     |            | 0.02 | 0.05 |

| b      | 0.15       | 0.20 | 0.25 |

| С      | 0.18       | 0.20 | 0.23 |

| D      | 5.90       | 6.00 | 6.10 |

| D2     | 4.10       | 4.20 | 4.30 |

| е      | 0.40 BSC   |      |      |

| Ne     | 4.40BSC    |      |      |

| Nd     | 4.40BSC    |      |      |

| E      | 5.90       | 6.00 | 6.10 |

| E2     | 4.10       | 4.20 | 4.30 |

| L      | 0.35       | 0.40 | 0.45 |

| h      | 0.30       | 0.35 | 0.40 |

| L/F    |            | •    |      |

| MIL    | 177*177    |      |      |

### **Documents / Resources**

### References

- \* Home GOWIN Semiconductor

- ③\_\_\_\_\_

- \* Home|GOWIN Semiconductor