FUTEK QIA128 SPI Communication Power Digital Controller

General Description

The QIA128 is a single channel ultra-low power digital controller with UART and SPI outputs. The QIA128 (slave device) can be used to communicate with any master devices through an SPI bus.

Pin Configurations and Function Descriptions for QIA128

Table 1

| # | Pin | Description | J1 # |

| ? | RESET | Active low reset pin. | – |

| 2 | TMS | JTAG TMS (Test Mode Select). Input pin used for debug and download. | – |

| 3 | TX | Transmit Asynchronous Data output. | 7 |

| 4 | RX | Receive Asynchronous Data input. | 6 |

| 5 | GND | Ground pins are connected to each other internally. | 1 |

QIA128 SPI Communication Guide

| 6 | -Excitation | Sensor excitation return (connected to Ground). | 2 |

| 7 | -Signal | Sensor negative Input. | 5 |

| 8 | +Excitation | Sensor excitation. | 3 |

| 9 | +Signal | Sensor positive Input. | 4 |

| 10 | VIN | Voltage input 3 − 5?????? | 9 |

| 11 | cs | Active low chip-select. Do not drive the CS line low until the device has booted up completely. Also ensure that the CS line is not driven low unless the DRDY is low. | 14 |

| 12 | SCLK | Serial clock generated by master. | 13 |

| 13 | MISO | Master-In-Slave-Out. | 12 |

| 14 | MOSI | Master-Out-Slave-In. | 11 |

| 15 | DRDY – | Active low DRDY pin is used to keep all communication synchronized . It notifies the master device when new data from the sampling system is ready. This ensures that the master is always collecting the latest data. When the DRDY pin goes low, it indicates that the data is ready to be clocked out. This pin can be used to externally interrupt the master. The pin returns high when the system is in a conversion state and returns low once new data is ready. *Note: The pin does not return high once data is read-it will only return high once the system enters a conversion state. |

– |

| 16 | VDD | Digital rail (2.5V). | – |

| 17 | NTRST | JTAG NTRST/BM Reset/Boot Mode. Input pin used for debug and download only and boot mode (BM). |

– |

| 18 | TDO | JTAG TDO (Data Out). Input pin used for debug and download. | – |

| 19 | TDI | JTAG TDI (Data In). Input pin used for debug and download. | – |

| 20 | TCK | JTAG TCK (Clock Pin). Input pin used for debug and download. | – |

QIA128 SPI Configuration

Table 2.

| Serial Word Length | 8-Bit | |||

| SPI Mode | Mode 0 (CPOL = 0, CPHA = 0) | |||

| SCLK Frequency | Min | 1 MHz | Max | 2 MHz |

| Internal Clock Frequency of MCU | 10.24 MHz | |||

| Operation Mode | Slave | |||

| Voltage Level | 1.8 VDC (compatible with 3.3 VDC) | |||

QIA128 Internal Design Algorithm

When the DRDY pin goes high, it means the device is in the process of A/D conversion, calculating the CRCB (See CRC

Calculations and References) and generating the packet that needs to be sent per the master device’s request. DRDY goes

low as soon as it fills out the SP/ TX buffer. The following algorithm is being executed while DRDY is high:

- Receives the latest ADC data from the highest interrupt priority

- Slave Service Function

- Keeps reading the RX FIFO until it is empty

- Saves all the bytes in a software buffer

- If the buffer is empty, creates a mock-up GADC command to go to the default state

- Checks the CRCB byte and CMD byte

- If either the CRCB or the CMD are incorrect

- Goes to the default state

-

- Else

-

- Replies with the corresponding packet (See Table 5.)

-

- Default State:

-

- Restarts the SP/ module

- Calculates the CRCB

- Loads 4 bytes of data (including the latest ADC data and the CRCB byte) into the TX FIFO

buffer - DRDY goes low

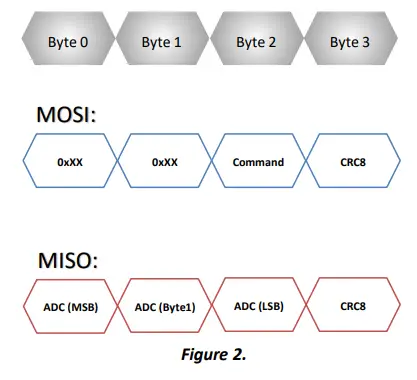

SPI Packet Structure

The packet structure stays consistent during all transactions and always includes four bytes of data for both receiving and transmitting.

“Continuous Read” Mode

GADC Command may be sent for each DRDY period to continuously get the ADC data.

*Note: If the CRC or the CMD bytes are incorrect, the device still fills out the buffer with the ADC data followed by the CRCB.

Timing Diagrams

Packet Structure (Get ADC Data):

Note: Each clack in Figure 3. represents 8-bits.

*Note: Each word (8-bits) can be clocked out with or without delay, but the entire transaction must be completed within a single DRDY period.

DRDY Period:

Table 3.

| T1(us) | T2(ms) | T3(us) | Descripti |

| 0to…* | 240 | 125 | 4 SPS |

| 55 | 20 SPS | ||

| 19 | 50 SPS | ||

| 9 | 100 SPS | ||

| 4.5 | 200 SPS | ||

| 1.5 | 500 SPS | ||

| 1.1 | 850 SPS | ||

| 0.6 | 1300SPS |

*Note: No delay or any delay as long as a/14 bytes are clocked out prior to DRDY going high. (See t 2 )

System Behavior

Start-up

When the system powers ON, it starts reading data from the internal flash and the solid green LED lights up; this represents normal operation mode.

*Note: Do not drive the CS line low until the device has booted up completely. Also ensure that the CS line is not driven low unless the DRDY is low. The DRDY line goes low as soon as the first data is ready to be clocked out.

Sampling Rate Change

When a sampling rate change is requested, it will take certain amount of time (depends on the requested sampling rate) to

see the change in the DRDY period. (See Table 4. )

| Maximum Approximate data rate change timing (ms) | SR Code | Sampling Rate I |

| =250 | OxOO | 4SPS |

| OxOl | 20SPS | |

| Ox02 | 50SPS | |

| Ox03 | 100 SPS | |

| Ox04 | 200 SPS | |

| Ox05 | 500 SPS | |

| Ox06 | 850 SPS | |

| Ox07 | 1300 SPS |

Command-Set List

Table 5.

| Type | Name | Description | MOSI Line Packet Structure (Master to QIA128) | MISO Line Packet Structure (QIA128 to Master) | ||||||

| CMD | CRC | Payload | Payload | Payload | CRC | |||||

| Byte0 | Byte 1 | Byte2 | Byte3 | Byte0 | Byte 1 | Byte2 | Byte3 | |||

| Get | GADC | Get ADC Data | OxXX | OxXX | OxOO | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCPO | Get Calibration Point Zero | OxXX | OxXX | OxOl | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCPl | Get Calibration Point One | OxXX | OxXX | Ox02 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP2 | Get Calibration Point Two | OxXX | OxXX | Ox03 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP3 | Get Calibration Point Three | OxXX | OxXX | Ox04 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP4 | Get Calibration Point Four | OxXX | OxXX | Ox05 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCPS | Get Calibration Point Five | OxXX | OxXX | Ox06 | CRCB | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GCP6 | Get Calibration Point Six | OxXX | OxXX | Ox07 | CRCB | ADCMSB | ADC Byte 1 | ADCLSB | CRCB |

| Get | GCP7 | Get Calibration Point Seven | OxXX | OxXX | Ox08 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCPB | Get Calibration Point Eight | OxXX | OxXX | Ox09 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP9 | Get Calibration Point Nine | OxXX | OxXX | OxOA | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP10 | Get Calibration Point Ten | OxXX | OxXX | OxOB | CRCB | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GCP11 | Get Calibration Point Eleven | OxXX | OxXX | OxOC | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP12 | Get Calibration Point Twelve | OxXX | OxXX | OxOD | CRCB | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GCP13 | Get Calibration Point Thirteen | OxXX | OxXX | OxOE | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP14 | Get Calibration Point Fourteen | OxXX | OxXX | OxOF | CRC8 | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GCP15 | Get Calibration Point Fifteen | OxXX | OxXX | Ox10 | CRC8 | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GCP16 | Get Calibration Point Sixteen | OxXX | OxXX | Ox11 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP17 | Get Calibration Point Seventeen | OxXX | OxXX | Ox12 | CRC8 | ADCMSB | ADC Bytel | ADC LSB | CRC8 |

| Get | GCP18 | Get Calibration Point Eighteen | OxXX | OxXX | Ox13 | CRC8 | ADCMSB | ADC Bytel | ADCLSB | CRC8 |

| Get | GCP19 | Get Calibration Point Nineteen | OxXX | OxXX | Ox14 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRC8 |

| Get | GCP20 | Get Calibration Point Twenty | OxXX | OxXX | Ox15 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP21 | Get Calibration Point Twenty-One | OxXX | OxXX | Ox16 | CRCB | ADCMSB | ADC Bytel | ADCLSB | CRCB |

| Get | GCP22 | Get Calibration Point Twenty-Two | OxXX | OxXX | Ox17 | CRCB | ADCMSB | ADC Bytel | ADC LSB | CRCB |

| Get | GSSN | Get Sensor Serial Number | OxXX | OxXX | Ox18 | CRCB | SSN MSB | SSN Bytel | SSN LSB | CRCB |

| Get | GISN | Get Instrument Serial Number | OxXX | OxXX | Ox19 | CRCB | /SN MSB | /SN Bytel | /SN LSB | CRCB |

| Get | GFRN | Get Firmware Revision Number | OxXX | OxXX | OxlA | CRCB | Major | Minor | Patch | CRCB |

| Get | GOR | Get Data Rate | OxXX | OxXX | OxlB | CRCB | OxOO | OxOO | SR Code (See

Tab /e 4.} |

CRCB |

| Set | S4SPS | Set 4 Sample Per Second | OxXX | OxXX | OxlC | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | S20SPS | Set 20 Sample Per Second | OxXX | OxXX | OxlD | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | SSOSPS | Set 50 Sample Per Second | OxXX | OxXX | OxlE | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | SlOOSPS | Set 100 Sample Per Second | OxXX | OxXX | OxlF | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | S200SPS | Set 200 Sample Per Second | OxXX | OxXX | Ox20 | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | SSOOSPS | Set 500 Sample Per Second | OxXX | OxXX | Ox21 | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | SBSOSPS | Set 850 Sample Per Second | OxXX | OxXX | Ox22 | CRCB | OxOO | OxOO | OxOO | CRCB |

| Set | S1300SPS | Set 1300 Sample Per Second | OxXX | OxXX | Ox23 | CRCB | OxOO | OxOO | OxOO | CRCB |

| Get | GNO | Get Number of Directions | OxXX | OxXX | Ox27 | CRCB | OxOO | OxOO | GNO | CRCB |

| Get | GNLP | Get Number of Loading Points | OxXX | OxXX | Ox28 | CRCB | OxOO | OxOO | GNLP | CRCB |

Packet and CRC Examples

The following transaction is the response to the GSSN command (Get Sensor Serial Number) that is being clocked out with the GADC command (Get ADC Data

us crc8(u8 *p, u8 len); function (See CRC Calculations and References) has been used as a reference to calculate the CRC for the

example above:

I I CRC calculation for the MISO transaction, MSB = 0x0l and LSB = 0x40

u8 BUFFER[] = {MSB, … ,LSB} » » » u8 BUFFER[] = {0x01, 0xE2, 0x40};

u8 crc8(BUFFER, 3);

then function returns 0xCS

ADC Data Conversion

The following formula could be used to convert the raw ADC data:

Calculated Reading

Here are the variables:[Devalue – Offset Value]————- x FullScaleLoad

[FullScaleValue – Offset Value]

Here are the variables:

ADCValue = the most recent analog-to-digital conversion value.

0 ff set Value= the analog-to-digital conversion value stored during calibration that corresponds to the offset (zero

physical load).

FullScaleValue = the analog-to-digital conversion value stored during calibration that corresponds to the full scale

(maximum physical load).

FullScaleLoad = the numeric value stored during calibration for the maximum physical load.

ADC Data Conversion Example

Calibration Data:

Offset Value = Get Calibration Point Zero {GCP0): 8000000 (0x7A1200)

FullScaleValue = Get Calibration Point Five {GCPS): 12000000 (0xB71B00)

Flu Scale Load = 20 I b

ADCValue. Get ADC Data {GADC): 10552731 (0xA1059B)

. [10552731 – 8000000]

CalculatedReadmg = [l2000000 _ 8000000 ] x 20 lb = 12.763 lb

Firmware Revision

| Applacation | |

| Revision | 6.1.0 |

| Release Date | 11/15/2022 |

| Hardware Compatibility | REV00l |

| Notes | New Features

|

Changes

commands |

|

| Fixes

• N/A |

CRC Calculations and References

crc8.h example:

extern uint8_t const crc_table[256];

uint8_t crc8(uint8_t *p, uint8_t len);

crc8.c example:

uint8_t canst crc_table[256] = {

OxOO, Ox07, Ox0e,Ox09,0xlc,Oxlb,Ox12,0x15,0x38,0x3~ Ox36,0x31, Ox24, Ox23, Ox2a, Ox2d,Ox70, Ox77, Ox7e,Ox79,0x6c,Ox6b,Ox62,0x65, Ox48, Ox4f,Ox46,0x41,0x54,0x53,0x5a,Ox5d,Oxe0, Oxe7, Oxee,Oxe9, Oxfc, Oxfb, Oxf2, OxfS, Oxd8, Oxdf, Oxd6, Oxdl, Oxc4, Oxc3, Oxca, Oxcd, Ox90, Ox97, Ox9e,Ox99,0x8c,Ox8b,Ox82,0x85,0xa8,0xa~ Oxa6, Oxal, Oxb4,0xb3,0xba, Oxbd,Oxc7,0xc0,0xc9,0xce, Oxdb,Oxdc, Oxd5,0xd2, Oxff, Oxf8, Oxfl, Oxf6, Oxe3, Oxe4, Oxed, Oxea, Oxb7, OxbO, Oxb9, Oxbe, Oxab,Oxac,Oxa5,0xa2,0x8~ Ox88, Ox81, Ox86, Ox93,0x94,0x9d, Ox9a, Ox27, Ox20, Ox29, Ox2e,Ox3b,Ox3c,Ox35,0x32,0xl~ Oxl8, Oxll,Oxl6, Ox03, Ox04, Ox0d,Ox0a,Ox57, OxSO, Ox59, Ox5e,Ox4b,Ox4c,Ox45,0x42, Ox6f,Ox68,0x61,0x66,0x73,0x74,0x7d,Ox7a,Ox89,0x8e,Ox87,0x80, Ox95, Ox92, Ox9b,Ox9c,Oxbl,Oxb6, Oxbf,Oxb8, Oxad, Oxaa, Oxa3, Oxa4, Oxf9, Oxfe, Oxf7, OxfO, Oxes, Oxe2, Oxeb, Oxec, Oxcl, Oxc6, Oxcf, Oxc8, Oxdd, Oxda, Oxd3,0xd4,0x69,0x6e,Ox67,0x60,0x75,0x72,0x7b,Ox7c,

Drawing Number EM1052 REV F 2023-06-02 Page 13 of 14

QIA128 SPI Communication Guide

0x51, 0x56, 0x5f, 0x58, 0x4d, 0x4a, 0x43, 0x44, 0x19, 0x1e, 0x17, 0x10, 0x05, 0x02, 0x0b, 0x0c, 0x21, 0x26, 0x2f, 0x28, 0x3d, 0x3a, 0x33, 0x34, 0x4e, 0x49, 0x40, 0x47, 0x52, 0x55, 0x5c, 0x5b, 0x76, 0x71, 0x78, 0x7f, 0x6a, 0x6d, 0x64, 0x63, 0x3e, 0x39, 0x30, 0x37, 0x22, 0x25, 0x2c, 0x2b, 0x06, 0x01, 0x08, 0x0f, 0x1a, 0x1d, 0x14, 0x13, 0xae, 0xa9, 0xa0, 0xa7, 0xb2, 0xb5, 0xbc, 0xbb, 0x96, 0x91, 0x98, 0x9f, 0x8a, 0x8d, 0x84, 0x83, 0xde, 0xd9, 0xd0, 0xd7, 0xc2, 0xc5, 0xcc, 0xcb, 0xe6, 0xe1, 0xe8, 0xef,

0xfa, 0xfd, 0xf4, 0xf3

};

// ————————————————————————————————-

uint8_t crc8(uint8_t *p, uint8_t len){

uint16_t i;

uint16_t crc = 0x0;

while (len–) {

i = (crc ^ *p++) & 0xFF;

crc = (crc_table[i] ^ (crc << 8)) & 0xFF;

}

return crc & 0xFF;

}//end crc8()

Documents / Resources

|

FUTEK QIA128 SPI Communication Power Digital Controller [pdf] User Guide QIA128 SPI Communication Power Digital Controller, QIA128 SPI, Communication Power Digital Controller, Power Digital Controller, Digital Controller, Controller |