# **FUTEK QIA123 UART Digital Low Power Controller Installation** Guide

Home » FUTEK » FUTEK QIA123 UART Digital Low Power Controller Installation Guide 🖺

#### **Contents**

- 1 FUTEK QIA123 UART Digital Low Power

- Controller

- **2 Product Information**

- **3 Product Usage Instructions**

- **4 General Description**

- **5 QIA123 UART Configuration**

- **6 DRDY Pin Functionality**

- 7 Command-Set List

- 8 Payload Example

- 9 Documents / Resources

- **10 Related Posts**

**FUTEK QIA123 UART Digital Low Power Controller**

#### **Product Information**

# **General Description**

The QIA123 is a low power digital controller with UART, SPI and analog outputs. It offers power management capability, allowing the master device to control the power consumption of the system by enabling and disabling the sampling system if required by the application.

# **PIN Configurations and Function Descriptions**

| Pin   | Description |

|-------|-------------|

| 1     | GND         |

| 2     | TRIG        |

| 3     | GND         |

| 4     | CS          |

| 5     | SCLK        |

| 6     | MOSI        |

| 7     | MISO        |

| 8     | TX          |

| 9     | RX          |

| 10-13 | GND         |

# **QIA123 UART Configuration**

| Data Operation | Baud Rate    | Parity | Stop bits | Flow Control |

|----------------|--------------|--------|-----------|--------------|

| 8-Bit          | 1,000,000bps | None   | 1-Bit     | None         |

#### **Stream Mode**

The Set System Stream State (SSSS) [with payload of 1] command can be sent to activate the stream mode. The device will stop streaming as soon as the Set System Stream State command [with payload of 0], or any other command is sent to QIA123.

#### **UART Packet Structure**

The packet structure and length for every command may vary due to their type (GET and SET) and functionalities; refer to the Command Set Table for further information.

#### **System Behavior**

**Start-up and Self-Calibration Mode:** When the system powers ON, it starts reading the data from EEPROM and goes to the internal calibration mode. The LED indicator starts blinking until it receives the first sample from the ADC.

**Sleep-Mode:** When power is applied to the system, it enters Sleep-Mode and stays high until the Set System Power Save State (SSPSS) is sent with a payload of 1.

### **Product Usage Instructions**

### **Sampling Rate Change**

When a sampling rate change is requested, it will take no more than 1 second (depending on the selected sampling rate) to see the change in the period.

#### **Sampling Rates**

The following table shows the available sampling rates:

| Sampling Rate | Period |

|---------------|--------|

| 10 SPS        | 912    |

| 60 SPS        | 130    |

| 100 SPS       | 26     |

| 1000 SPS      | ?      |

| 4800 SPS      | ?      |

| 9600 SPS      | ?      |

#### **General Description**

The QIA123 is a low power digital controller with UART, SPI and analog outputs. The QIA123 offers power management capability which allows the master device to control the power consumption of the system by enabling and disabling the sampling system if required by the application.

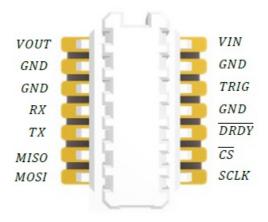

#### **PIN Configurations and Function Descriptions**

Figure 1.

| # | Pin    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | ?????? | Voltage Input 5V±4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2 | GND    | Ground pins are connected to each other internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3 | TRIG   | Trigger is an input pin (slave) and output pin (master) dedicated for special applications such as programing for future development                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4 | GND    | Ground pins are connected to each other internally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | ?????? | Active low ??????? pin is used to keep all communication synchronized. It notifies the mast er device when new data from the sampling system is ready to ensure that the master is alw ays collecting the latest data. When the ???????pin goes low, it indicates that the data is re ady. This pin can be used to externally interrupt the master. The pin returns high when the sy stem is in a conversion state and returns low once new data is ready. The pin does not return high once data is read—it will only return high once the system enters a conversion state. |

| 6  | ???                                                    | Active low Chip Select. Do not drive the ???? line low until the device has booted up complet ely. The <i>LED</i> turns off once the board has booted and is ready to communicate. This process takes <i>3 seconds</i> . Also ensure that the ???? line is not driven low unless the ???????? is also low. |  |

|----|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7  | SCLK                                                   | Serial Clock generated by master                                                                                                                                                                                                                                                                           |  |

| 8  | MOSI                                                   | OSI Master-Out-Slave-In                                                                                                                                                                                                                                                                                    |  |

| 9  | MISO                                                   | Master-In-Slave-Out                                                                                                                                                                                                                                                                                        |  |

| 10 | TX                                                     | UART Transmit of QIA123                                                                                                                                                                                                                                                                                    |  |

| 11 | RX UART Receive of QIA123                              |                                                                                                                                                                                                                                                                                                            |  |

| 12 | GND Ground pins are connected to each other internally |                                                                                                                                                                                                                                                                                                            |  |

| 13 | GND Ground pins are connected to each other internally |                                                                                                                                                                                                                                                                                                            |  |

| 14 | VOUT                                                   | Analog voltage output calibrated between 0.2V - 2.8V                                                                                                                                                                                                                                                       |  |

# **QIA123 UART Configuration**

Table 2.

| Data                 | 8-Bit        |

|----------------------|--------------|

| Operation Baud Rate: | 1,000,000bps |

| Parity               | None         |

| Stop bits            | 1-Bit        |

| Flow Control:        | None         |

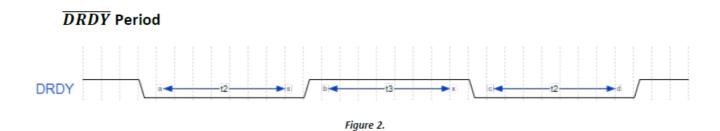

# **DRDY Pin Functionality**

When the DRDY pin goes high, it means the device is in the process of A/D conversion. DRDYgoes low as soon as the conversion is complete.

The following table shows the period of the pin for all sampling rates.

| ?? <sub>??</sub> (µ??) | ?? <sub>??</sub> (µ??) | ?? <sub>??</sub> (µ??) | Description |

|------------------------|------------------------|------------------------|-------------|

|                        | 99600                  |                        | 10 SPS      |

|                        | 16600                  |                        | 60 SPS      |

| 0.4-                   | 9926                   |                        | 100 SPS     |

| 0 to*                  | 912                    | 80                     | 1000 SPS    |

|                        | 130                    |                        | 4800 SPS    |

|                        | 26                     |                        | 9600 SPS    |

#### "Stream" Mode

The Set System Stream State (SSSS) [with payload of 1] command may be sent to activate the stream mode. The device will stop streaming as soon as the Set System Stream State command [with payload of 0], or any other command is sent to QIA123.

\*Note: There may be no response from the QIA123 if an incorrect command is sent.

#### **UART Packet Structure**

The packet structure and length for every command may vary due to their type (GET and SET) and functionalities; refer to the Command Set Table for further information.

#### **System Behavior**

#### **Start-up and Self-Calibration Mode**

When the system powers ON, it starts reading the data from EEPROM and goes to the internal calibration mode. The LED indicator starts blinking until it receives the first sample from the ADC.

\*Note: The White LED turns off once the board has booted and is ready to communicate. This process takes ~3 seconds.

\*Note: When power is applied to the system, it enters Sleep-Mode and stays high until the Set System Power Save State (SSPSS) is sent with a payload of 1.

#### **Sampling Rate Change**

When a sampling rate change is requested it will take no more than 1 second (depending on the selected sampling rate) to see the change in the period.

### **Sampling Rates**

| SPS Code (Payload) | Sampling Rate |

|--------------------|---------------|

| 0x04               | 10 SPS        |

| 0x05               | 60 SPS        |

| 0x06               | 100 SPS       |

| 0x07               | 1000 SPS      |

| 0x08               | 4800 SPS      |

| 0x09               | 9600 SPS      |

#### **Shunt Switch Feature**

#### **GDCSSW (Get Device Channel Shunt Switch)**

GDCSSW command returns the current state of the shunt switch.

| Shunt Switch (Payload) | State |

|------------------------|-------|

| 0x00                   | OFF   |

| 0x01                   | ON    |

SDCSSW (Set Device Channel Shunt Switch)

SDCSSW command enables or disables the shunt switch.

#### **Power Management**

SSPSS command has been implemented to turn OFF/ON the sampling system to manage power consumption.

### SSPSS [Payload 1] (Disable Sampling; Sleep-Mode)

SSPSS command with a payload of 1 makes the system go to Sleep-Mode. The device shuts down the sampling system after replying to the master device.

\*Note: When the system is in the Sleep-Mode, stays high and the current draw (instrument only) drops down to ~12mA.

### SSPSS [Payload 0] (Enable Sampling; Wake-Mode)

SSPSS command with a payload of 0 puts the system in Wake-Mode. The sampling system is enabled after replying the master device.

- \* **Note:** The SSPSS command with a payload of 0 must be sent to enable the sampling system. Do not use any other command to wake up the system other than SSPSS. The current draw in this state (instrument only) is ~19mA.

- \* **Note:** In order to receive a response from the QIA123 the SSPSS with a payload of 0 needs to be sent twice in a row.

#### **Command-Set List**

Table 6.

| Тур  | Name | Description                                              | TX Packet Struct ure  | RX Packet Structure            | Bytes in Payload |

|------|------|----------------------------------------------------------|-----------------------|--------------------------------|------------------|

| Get  | GSAI | Get slave activity inquiry (use d to test communication) | 00 05 00 01 0E        | 00 05 00 01 0E                 | N/A              |

| *Get | GCCR | Get channel current reading                              | 00 06 00 05 00 20     | See Payload Example            | 4                |

| Set  | SSSS | Set system stream state OFF                              | 00 06 00 0C 00 3<br>C | 00 05 00 0C 3A                 | N/A              |

| *Set | SSSS | Set system stream state ON                               | 00 06 00 0C 01 41     | 00 05 00 0C 3A [Stream B ytes] | N/A [4]          |

| Set       | SSPS<br>S | Set system power save state sleep       | 00 06 00 0D 01 45       | 00 05 00 0D 3E      | N/A |

|-----------|-----------|-----------------------------------------|-------------------------|---------------------|-----|

| **Se<br>t | SSPS<br>S | Set system power save state wake        | 00 06 00 0D 00 40       | 00 05 00 0D 3E      | N/A |

| *Get      | GDSN      | Get device serial number                | 00 05 01 00 0D          | See Payload Example | 4   |

| *Get      | GDM<br>N  | Get device model number                 | 00 05 01 01 11          | See Payload Example | 10  |

| *Get      | GDHV      | Get device hardware version             | 00 05 01 03 19          | See Payload Example | 1   |

| *Get      | GDFV      | Get device firmware version             | 00 05 01 04 1D          | See Payload Example | 2   |

| *Get      | GDFD      | Get device firmware date                | 00 05 01 05 21          | See Payload Example | 3   |

| *Get      | GDCS<br>W | Get device channel shunt swit ch        | 00 06 01 0B 00 3B       | See Payload Example | 1   |

| Set       | SDCS<br>W | Set device channel shunt swit<br>ch OFF | 00 07 02 0B 00 00<br>40 | 00 05 02 0B 3C      | N/A |

| Set       | SDCS<br>W | Set device channel shunt swit ch ON     | 00 07 02 0B 00 01<br>46 | 00 05 02 0B 3C      | N/A |

| *Get      | GPSS<br>N | Get profile sensor serial numb er       | 00 06 03 00 00 15       | See Payload Example | 4   |

| *Get      | GPSP<br>R | Get profile sampling rate               | 00 06 03 1E 00 8<br>D   | See Payload Example | 1   |

| Set       | SPSP<br>R | Set profile sampling rate 10S<br>PS     | 00 07 04 1E 00 04<br>AA | 00 05 04 1E 8E      | N/A |

| Set       | SPSP<br>R | Set profile sampling rate 60S PS        | 00 07 04 1E 00 05<br>B0 | 00 05 04 1E 8E      | N/A |

| Set       | SPSP<br>R | Set profile sampling rate 100SPS        | 00 07 04 1E 00 06<br>B6 | 00 05 04 1E 8E      | N/A |

| Set       | SPSP<br>R | Set profile sampling rate 1000 SPS      | 00 07 04 1E 00 07<br>BC | 00 05 04 1E 8E      | N/A |

| Set       | SPSP<br>R | Set profile sampling rate 4800 SPS      | 00 07 04 1E 00 08<br>C2 | 00 05 04 1E 8E      | N/A |

| Set  | SPSP<br>R | Set profile sampling rate 9600 SPS                              | 00 07 04 1E 00 09<br>C8 | 00 05 04 1E 8E      | N/A |

|------|-----------|-----------------------------------------------------------------|-------------------------|---------------------|-----|

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 0 (Direction 1) | 00 07 03 19 00 00<br>7B | See Payload Example | 4   |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 1 (Direction 1) | 00 07 03 19 00 01<br>81 | See Payload Example | 4   |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 2 (Direction 1)  | 00 07 03 19 00 02<br>87 | See Payload Example | 4 |

|------|-----------|------------------------------------------------------------------|-------------------------|---------------------|---|

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 3 (Direction 1)  | 00 07 03 19 00 03<br>8D | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 4 (Direction 1)  | 00 07 03 19 00 04<br>93 | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 5 (Direction 1)  | 00 07 03 19 00 05<br>99 | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 6 (Direction 2)  | 00 07 03 19 00 06<br>9F | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 7 (Direction 2)  | 00 07 03 19 00 07<br>A5 | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 8 (Direction 2)  | 00 07 03 19 00 08<br>AB | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 9 (Direction 2)  | 00 07 03 19 00 09<br>B1 | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 10 (Direction 2) | 00 07 03 19 00 0A<br>B7 | See Payload Example | 4 |

| *Get | GPAD<br>P | Get profile analog-to-digital calibration value 11 (Direction 2) | 00 07 03 19 00 0B<br>BD | See Payload Example | 4 |

**Note:** The Payload bytes are located directly before the last byte of the packet which is the Checksum. **Note:** In order to receive a response from the QIA123 the SSPSS with a payload of 0 needs to be sent twice in a row.

### **Payload Example**

The following transaction is the response to the GDSN command (Get device serial number). This command has a payload of 4 bytes.

TX: 00 05 01 00 0D

RX: 00 09 01 00 00 01 E2 40 49

Hex to decimal: 0x0001E240 -> 123456

**ADC Data Conversion**

The following formula could be used to convert the raw ADC data:

$$CalculatedReading = \frac{[ADCValue - OffsetValue]}{[FullScaleValue - OffsetValue]} \times FullScaleLoad$$

Here are the variables:

ADValue = the most recent analog-to-digital conversion value.

Offsetvalue = the analog-to-digital conversion value stored during calibration that corresponds to the offset (zero physical load. FullScaleValue = the analog-to-digital conversion value stored during calibration that corresponds to the full scale (maximum physical load.

FullScaleLoad = the numeric value stored during calibration for the maximum physical load.

#### ADC Data Conversion Examples (Direction 1, 2-point Calibration)

Calibration Data

Get profile analog-to-digital calibration value 0 (Direction 1) [GPADP]:

Hex to decimal: 0x81B320 -> 8,500,000

Get profile analog-to-digital calibration value 5 (Direction 1) [GPADP]:

Hex to decimal: 0xB71B00 -> 12,000,000 Get channel current reading (GCCR): Hex to decimal: 0x989680 -> 000

#### Calculation

OffsetValue = 8,500,000 FullScaleValue = 12,000,000

FullScaleLoad = 20g (Available on the calibration certificate)

$$CalculatedReading = \frac{[10000000 - 8500000]}{[12000000 - 8500000]} \times 20g = 8.5714g$$

#### **Firmware Revision**

Revision 1.6 Firmware Notes

#### **New Features**

N/A

Changes

N/A

**Fixes**

N/A

Drawing Number EM1058 • Revision A • 2022-03-09

Sensor Solution Source Load • Torque • Pressure • Multi Axis • Calibration • Instruments • Software www.futek.com

#### **Documents / Resources**

**FUTEK QIA123 UART Digital Low Power Controller** [pdf] Installation Guide QIA123 UART Digital Low Power Controller, QIA123, UART Digital Low Power Controller, Digit al Low Power Controller, Low Power Controller, Power Controller, Controller

Manuals+,