# ESPRESSIF ESP32 Wroom-32D ESP32D WiFi Development **Board User Guide**

Home » ESPRESSIF » ESPRESSIF ESP32 Wroom-32D ESP32D WiFi Development Board User Guide 🖫

#### **Contents**

- 1 ESPRESSIF ESP32 Wroom-32D ESP32D WiFi Development **Board**

- 2 Release Notes

- **3 Documentation Change Notification**

- **4 Certification**

- 5 Design Changes in Chip

- **6 Impact on Customer Projects**

- 7 Label Specification

- **8 Ordering Information**

- 9 Documents / Resources

- 9.1 References

- 10 Related Posts

ESPRESSIF ESP32 Wroom-32D ESP32D WiFi Development Board

This document describes differences between chip revision v3.0 and previous ESP32 chip revisions.

### **Release Notes**

| Date    | Version | Release notes                                                  |

|---------|---------|----------------------------------------------------------------|

| 2020.01 | V1.0    | Initial release.                                               |

| 2020.07 | V1.1    | Added item 6 to Chapter 1 Design Changes in ECO V3.            |

| 2022.10 | v1.2    | Replaced "ECO" with "Chip Revision"                            |

|         |         | Renamed this document as "ESP32 Chip Revision v3.0 User Guide" |

| 2022.11 | v1.3    | Added item 1 to Chapter 1 Design Changes in ECO V3.            |

# **Documentation Change Notification**

Espressif provides email notifications to keep customers updated on changes to technical documentation. Please subscribe at <a href="https://www.espressif.com/en/subscribe">https://www.espressif.com/en/subscribe</a>.

# Certification

Download certificates for Espressif products from <a href="https://www.espressif.com/en/certificates">https://www.espressif.com/en/certificates</a>.

# **Design Changes in Chip**

Espressif has released ESP32 chip revision v3.0 that features wafer-level changes basing on previous ESP32

chip revisions. The design changes introduced on the ESP32 chip revision v3.0 are:

- 1. Fixed "Due to the flash start-up time, a spurious watchdog reset occurs when ESP32 is powered up or wakes up from Deep-sleep". Details of the issue can be found in item 3.8 in ESP32 Series SoC Errata.

- 2. PSRAM Cache Bug Fix: Fixed "When the CPU accesses the external SRAM in a certain sequence, read & write errors can occur". Details of the issue can be found in item 3.9 in ESP32 Series SoC Errata.

- 3. Fixed "When each CPU reads certain different address spaces simultaneously, a read error can occur". Details of the issue can be found in item 3.10 in ESP32 Series SoC Errata.

- 4. Optimized 32.768 KHz crystal oscillator stability. The issue was reported by client that there is a low probability that on chip revision v1.0 hardware, the 32.768 KHz crystal oscillator couldn't start properly.

- 5. Fixed Fault injection issues regarding secure boot and flash encryption are fixed. Reference: Security Advisory concerning fault injection and eFuse protections (CVE-2019-17391) & Espressif Security Advisory Concerning Fault Injection and Secure Boot (CVE-2019-15894)

- 6. Improvement: Changed the minimum baud rate supported by the TWAI module from 25 kHz to 12.5 kHz.

- 7. Allowed Download Boot mode to be permanently disabled by programming new eFuse bit UART\_DOWNLOAD\_DIS. When this bit is programmed to 1, Download Boot mode cannot be used and booting will fail if the strapping pins are set for this mode. Software programs this bit by writing to bit 27 of EFUSE\_BLK0\_WDATA0\_REG, and reads this bit by reading bit 27 of EFUSE\_BLK0\_RDATA0\_REG. Write disable for this bit is shared with write disable for the flash\_crypt\_cnt eFuse field.

### **Impact on Customer Projects**

This section is intended to help our customers to understand the impact of using chip revision v3.0 in a new design or replacing older version SoC with chip revision v3.0 in existing design.

### Use Case 1: Hardware and Software Upgrade

This is the use-case where the new project is being initiated or upgrade for hardware and software in an existing project is a possible option. In such a case, the project can benefit from protection against fault injection attack and can also take advantage of newer secure boot mechanism and PSRAM cache bug fix with slightly enhanced PSRAM performance.

#### 1. Hardware Design Changes:

Please follow the latest ESP32 Hardware Design Guidelines. For 32.768 KHz crystal oscillator stability issue optimization, please refer to Section Crystal Oscillator for more information.

# 2. Software Design Changes:

- 1. Select Minimum configuration to Rev3: Go to menuconfig > Conponent config > ESP32-specific, and set the Minimum Supported ESP32 Revision option to "Rev 3".

- 2. Software version: Recommend to use RSA-based secure boot from ESP-IDF v4.1 and later. ESP-IDF v3.X Release version can also work with application with original secure boot V1.

#### **Use Case 2: Hardware Upgrade Only**

This is the use-case where customers have existing project which can allow hardware upgrade but software needs to remain the same across hardware revisions. In this case the project gets benefit of security to fault injection attacks, PSRAM cache bug fix and 32.768KHz crystal oscillator stability issue. The PSRAM performance continues to remain the same though.

### 1. Hardware Design Changes:

Please follow latest ESP32 Hardware Design Guidelines.

2. Software Design Changes:

Client can continue to use the same software and binary for deployed product. The same application binary will work on both chip revision v1.0 and chip revision v3.0.

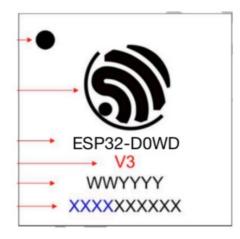

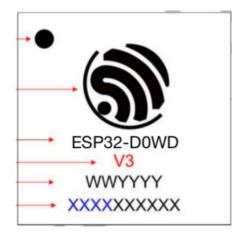

# **Label Specification**

• The label of ESP32-D0WD-V3 is shown below:

• The label of ESP32-D0WDQ6-V3 is shown below:

## **Ordering Information**

For product ordering, please refer to: ESP Product Selector.

Disclaimer and Copyright Notice

- Information in this document, including URL references, is subject to change without notice.

- THIS DOCUMENT IS PROVIDED AS IS WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY

WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE,

OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

- All liability, including liability for infringement of any proprietary rights, relating to use of information in this document is disclaimed. No licenses express or implied, by estoppel or otherwise, to any intellectual property rights are granted herein.

- The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth logo is a registered

trademark of Bluetooth SIG.

- All trade names, trademarks and registered trademarks mentioned in this document are property of their respective owners, and are hereby acknowledged.

- Copyright © 2022 Espressif Inc. All rights reserved.

#### **Documents / Resources**

### References

- Mi-Fi & Bluetooth MCUs and AloT Solutions I Espressif Systems

- Wi-Fi & Bluetooth MCUs and AloT Solutions I Espressif Systems

- Documentation Feedback | Espressif Systems

- Sepressif Security Advisory Concerning Fault Injection and Secure Boot (CVE-2019-15894) |

Espressif Systems

- Security Advisory concerning fault injection and eFuse protections (CVE-2019-17391) | Espressif

Systems

- <u>Subscribe | Espressif Systems</u>

Manuals+,