AN5827

Nodyn cais

Canllawiau ar gyfer mynd i mewn i gyflwr RMA ar MPUs Cyfres STM32MP1

Rhagymadrodd

Mae microbroseswyr Cyfres STM32MP1 yn cynnwys dyfeisiau STM32MP15xx a STM32MP13xx.. Mae'r nodyn cais hwn yn darparu gwybodaeth i gefnogi'r broses o fynd i mewn i gyflwr dadansoddi deunydd dychwelyd, y cyfeirir ato fel RMA yn y ddogfen hon.

Gwybodaeth gyffredinol

Mae'r ddogfen hon yn berthnasol i ficrobroseswyr Cyfres STM32MP1 sy'n seiliedig ar greiddiau Arm® Cortex®

Nodyn: Mae Arm yn nod masnach cofrestredig Arm Limited (neu ei is-gwmnïau) yn yr UD a / neu rywle arall.

Dogfennau cyfeirio

| Cyfeiriad | Teitl y ddogfen |

| STM32MP13xx | |

| AN5474 | Dechrau arni gyda datblygu caledwedd llinellau STM32MP13x |

| DS13878 | Arm® Cortex®-A7 hyd at 1 GI-ft, 1xETH, 1 xADC, 24 amserydd, sain |

| DS13877 | Arm® Cortex®-A7 hyd at 1 GHz, 1xETH, 1 xADC, 24 amserydd, sain, crypto ac adv. diogelwch |

| DS13876 | Arm® Cortex®-A7 hyd at 1 GI-ft, 2xETH, 2xCAN FD, 2xADC. 24 amserydd, sain |

| DS13875 | Arm® Cortex®-A7 hyd at 1 GHz, 2xETH, 2xCAN FD, 2xADC, 24 amserydd, sain, crypto ac adv. diogelwch |

| DS13874 | Arm® Cortex®-A7 hyd at 1 GHz, LCD-TFT, rhyngwyneb camera, 2xETH, 2xCAN FD, 2xADC, 24 amserydd, sain |

| DS13483 | Arm® Cortex®-A7 hyd at 1 GHz, LCD-TFT, rhyngwyneb camera, 2xETH, 2xCAN FD, 2xADC, 24 amserydd, sain, crypto ac adv. diogelwch |

| RM0475 | STM32MP13xx MPUs 0-did datblygedig yn seiliedig ar Arm32 |

| STM32MP15xx | |

| AN5031 | Dechrau arni gyda datblygu caledwedd llinell STM32MP151, STM32MP153 a STM32MP157 |

| DS12500 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. rhyngwynebau, 25 amserydd, adv. analog |

| DS12501 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. rhyngwynebau, 25 amserydd, adv. analog, crypto |

| DS12502 | Arm® deuol Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. rhyngwynebau, 29 amserydd, adv. analog |

| DS12503 | Arm® deuol Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. rhyngwynebau, 29 amserydd, adv. analog, crypto |

| DS12504 | Arm® deuol Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 comm. rhyngwynebau, 29 amserydd, adv. analog |

| DS12505 | Arm® deuol Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 comm. rhyngwynebau, 29 amserydd, adv. analog, crypto |

| RM0441 | STM32MP151 datblygedig MPUs 32-did yn seiliedig ar Arm® |

| RM0442 | STM32MP153 uwch MPUs 32-did yn seiliedig ar Arnie |

| RM0436 | STM32MP157 uwch MPUs 0-did seiliedig ar Arm32 |

Termau ac acronymau

Tabl 2. Diffiniad o acronymau

| Tymor | Diffiniad |

| PELL | Cais dadansoddi methiant: llif a ddefnyddir i ddychwelyd dyfais amheus i'w dadansoddi i STMicroelectronics. Er mwyn gwella'r llawn prawfadwyedd y ddyfais yn ystod dadansoddiad o'r fath, rhaid i'r ddyfais fod mewn cyflwr RMA. |

| JTAG | Grŵp gweithredu prawf ar y cyd (rhyngwyneb dadfygio) |

| PMIC | Cylched rheoli pŵer allanol sy'n darparu cyflenwadau pŵer platfform amrywiol, gyda gallu rheoli mawr drwyddo signalau a rhyngwyneb cyfresol. |

| RMA | Dadansoddiad deunydd dychwelyd: cyflwr dyfais benodol yn y cylch bywyd sy'n caniatáu actifadu modd prawf llawn yn ôl yr angen STMicroelectroneg at ddiben dadansoddi methiant. |

1. Yn y ddogfen hon, nid yw'r acronym RMA yn cyfeirio yn unrhyw le at "dderbyn deunydd dychwelyd" sef y llif a ddefnyddir i ddychwelyd rhannau nas defnyddir (stoc cwsmeriaid ar gyfer example).

Cyflwr RMA o fewn y llif PELL

Mae'r llif FAR yn cynnwys dychwelyd dyfais i STMicroelectronics ar gyfer dadansoddiad methiant dyfnach rhag ofn bod amheuaeth o broblem ansawdd. Rhaid dychwelyd y rhan y gellir ei phrofi i ST fel y gellir perfformio'r dadansoddiad.

- Rhaid i'r rhan fod mewn cyflwr RMA

- Rhaid i'r rhan fod yn gydnaws yn gorfforol â'r ddyfais wreiddiol (maint pêl, traw, ac ati)

Cylch bywyd cynnyrch STM32MP13xx

Ar ddyfeisiau STM32MP13xx, cyn dychwelyd y ddyfais, rhaid i'r cwsmer fynd i mewn i gyflwr RMA gyda chyfrinair 32-did wedi'i ddiffinio ymlaen llaw gan y cwsmer wedi'i nodi trwy'r JTAG (gweler Adran 3). Ar ôl ei nodi yn nhalaith RMA, nid yw'r ddyfais bellach yn ddefnyddiadwy i'w chynhyrchu (gweler Ffigur 1) ac mae'r modd prawf llawn yn cael ei actifadu i STMicroelectronics barhau i ymchwilio tra bod holl gyfrinachau cwsmeriaid (OTP uchaf fel y disgrifir yn y llawlyfr cyfeirio) yn anhygyrch. gan y caledwedd.

Mae'r ffigur isod yn dangos cylch bywyd cynnyrch dyfeisiau STM32MP13xx. Mae'n dangos, unwaith y bydd y cyflwr RMA wedi'i nodi, ni all y ddyfais fynd yn ôl i foddau eraill.

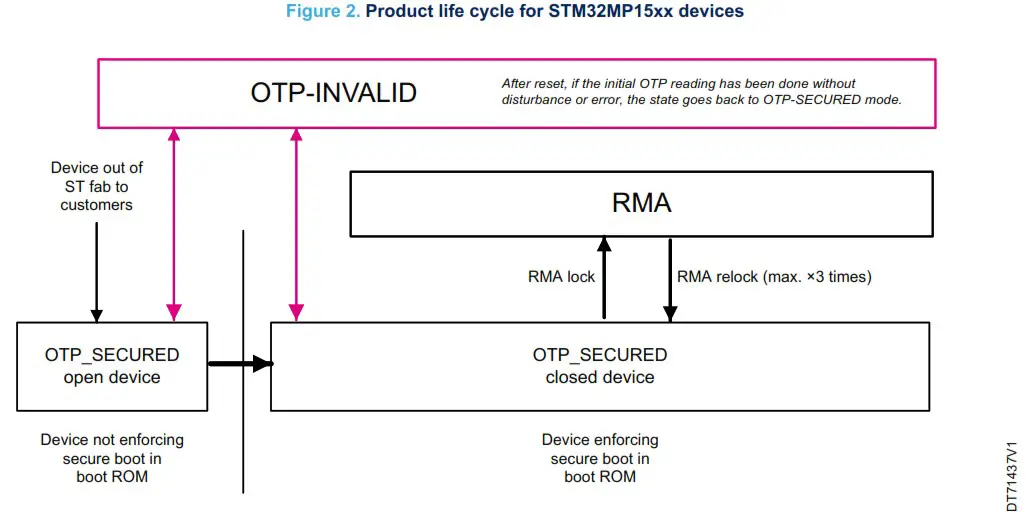

Cylch bywyd cynnyrch STM32MP15xx

Ar ddyfeisiau STM32MP15xx, cyn dychwelyd y ddyfais, rhaid i'r cwsmer fynd i mewn i gyflwr RMA gyda chyfrinair 15-did wedi'i ddiffinio ymlaen llaw gan y cwsmer wedi'i nodi trwy'r JTAG (gweler Adran 3). Ar ôl ei nodi yn nhalaith RMA, gall y ddyfais fynd yn ôl i gyflwr SECURE_CLOSED trwy nodi cyfrinair “RMA_RELOCK” wedi'i ddiffinio ymlaen llaw gan y cwsmer. Dim ond 3 o dreialon cyflwr trawsnewid RMA i RMA_RELOCKED a ganiateir (gweler Ffigur 2). Yn nhalaith RMA, mae'r modd prawf llawn yn cael ei actifadu i STMicroelectronics barhau i ymchwilio tra bod yr holl gyfrinachau cwsmeriaid (OTP uchaf fel y disgrifir yn y llawlyfr cyfeirio) yn cael eu cadw'n anhygyrch gan y caledwedd.

Mae'r ffigur isod yn dangos cylch bywyd cynnyrch dyfeisiau STM32MP15x.

Cyfyngiadau bwrdd gwladwriaeth RMA

Er mwyn actifadu cyflwr RMA, mae angen y cyfyngiadau canlynol.

Mae'r J.TAG dylai mynediad fod ar gael

Rhaid i'r signalau NJTRST a JTDI, JTCK, JTMS, JTDO (pin PH4, PH5, PF14, PF15 ar ddyfeisiau STM32MP13xx) fod yn hygyrch. Ar rai offer, nid yw'r JTDO yn angenrheidiol (ar gyfer cynample, Trace32) ar eraill fel OpenOCD mae'r offeryn yn gwirio'r ddyfais JTAG ID trwy JTDO cyn gweithredu'r JTAG dilyniant.

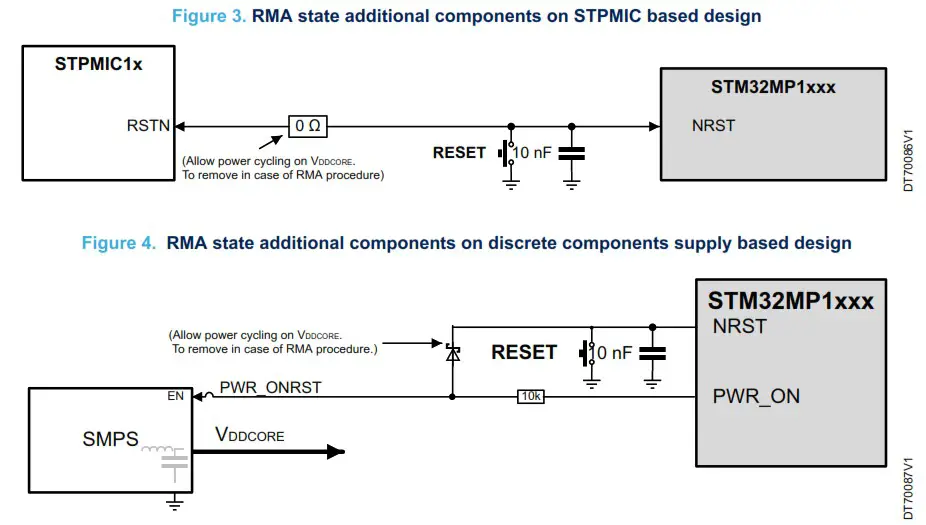

Ni ddylid diffodd y cyflenwad pŵer VDDCORE a VDD pan fydd y pin NRST yn cael ei actifadu

Ar ddyluniad cyfeirio ST, mae'r NRST yn actifadu cylch pŵer o'r rheolyddion pŵer cydrannau arwahanol STPMIC1x neu allanol. Dangosir gweithrediad posibl yn y dyluniad cyfeirio exampdarperir yn y nodyn cais Dechrau arni gyda datblygu caledwedd llinellau STM32MP13x (AN5474) . Mae Ffigur 3 a Ffigur 4 yn fersiynau symlach sy'n dangos y cydrannau sy'n gysylltiedig â chyflwr RMA yn unig. Mae'r un peth yn wir am ddyfeisiau STM32MP15xx.

Bwrdd syml gyda dim ond y JTAG gellir defnyddio pin a soced priodol at ddibenion cyfrinair RMA yn unig (rhag ofn nad yw'n bosibl cyrchu JTAG ar y bwrdd cynhyrchu). Mewn achos o'r fath rhaid i'r cwsmer yn gyntaf ddadsoddi'r ddyfais o'r bwrdd cynhyrchu ac ailboblogi'r peli pecyn.

Rhaid i'r bwrdd fod â'r pinnau STM32MP1xxx a restrir yn Nhabl 3 wedi'u cysylltu fel y nodir . Gellir gadael pinnau eraill yn arnofio.

Tabl 3 . Cysylltiad pin ar gyfer bwrdd syml a ddefnyddir ar gyfer mynediad cyfrinair RMA

| Enw pin (signal) | Wedi'i gysylltu â | Sylw | |

| STM32MP13xx | STM32MP15xx | ||

| JTAG ac ailosod | |||

| NJTRST | CGCGC | JTAG cysylltydd | |

| PH4 (JTDI) | JTDI | ||

| PH5 (JTDO) | JTDO | Nid oes ei angen ar ryw offeryn dadfygio fel Trace32 | |

| PF14 (JTCK) | JTCK | ||

| PF15 (JTMS) | JTMS | ||

| NRST | NRST | Botwm ailosod | Gyda chynhwysydd 10 nF i VSS |

| Cyflenwadau pŵer | |||

| VDDCORE. VDDCPU | VDDCORE | Cyflenwad allanol | Cyfeiriwch at daflen ddata cynnyrch ar gyfer nodweddiadol gwerth |

| VDD. VDDSD1. VDDSD2. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON |

VDD. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON. PDR_ON_CORE |

3.3 V allanol cyflenwad |

Dylai fod ar gael yn gyntaf a'i ddileu olaf (gall fod ynghyd ag eraill cyflenwadau) |

| VDDA, VREF+, VDD3V3_USBHS. VDDO_DDR |

VDDA. VREF+. VDD3V3_USBHS. VDDO_DDR. VDD_DSI. VDD1V2_DSI_REG. VDD3V3_USBFS |

0 | ADC. VREFBUF, USB, DDR heb eu defnyddio |

| VSS. VSS_PLL. VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_US131-IS |

VSS. VSS_PLL, VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_USBHS. VSS_DSI |

0 | |

| VDDA1V8_REG. VDDA1V1_REG |

VDDA1V8_REG. VDDA1V1_REG |

arnofio | |

| Arall | |||

| BYPASS_REG1V8 | BYPASS_REG1V8 | 0 | Rheoleiddiwr 1V8 wedi'i alluogi yn ddiofyn (REG 18E = 1) |

| PC15- OSC32_OUT | PC15- OSC32_OUT | arnofio | |

| PC14- OSC32_IN | PC14- OSC32_IN | Osgiliaduron allanol heb eu defnyddio (boot ROM i ddefnyddio osgiliadur mewnol HSI) |

|

| PHO-OSC_IN | PHO-OSC_IN | ||

| PH1-0SC_OUT | PH1-0SC_OUT | ||

| USB_RREF | USB_RREF | arnofio | USB heb ei ddefnyddio |

| P16 (BOOT2) | BOOT2 | X | Mae mynd i mewn i gyflwr RMA yn gweithio beth bynnag yw'r gwerthoedd cychwyn (2:0). |

| DP5 (BOOT1) | 60011 | X | |

| DP4 (BOOTO) | BOOTO | X | |

| NRST_CORE | 10 nF i VSS | Tynnu i fyny mewnol ar NRST_CORE | |

| PA13 (BOOTFAILN) | PA13 (BOOTFAILN) | LED | Dewisol |

Gofynion blaenorol i ganiatáu i dalaith RMA ddod i mewn yn y dyfodol

Rhaid i'r cwsmer sefydlu'r posibilrwydd i fynd i mewn i gyflwr RMA trwy nodi cyfrinair yn ystod cynhyrchiad cwsmer ar ôl darparu cyfrinachol

- Mae'r ddyfais wrth ei chludo o STMicroelectronics mewn cyflwr agored OTP_SECURED.

- Mae'r ddyfais yn cynnwys cyfrinachau ST sy'n cael eu diogelu gan ROM cychwyn, a dim cyfrinach cwsmer.

- Wrth ailosod neu ar ôl gweithredu ROM cychwyn, gellir ailagor mynediad DAP gan Linux neu drwy ddull “cist datblygu” cychwyn ROM (OTP_SECURED agored + boot pins BOOT[2:0]=1b100 + ailosod).

- Tra yn OTP_SECURED agored, rhaid i'r cwsmer ddarparu ei gyfrinachau yn OTP:

- yn uniongyrchol gan gwsmer ar ei risg ei hun neu

- yn ddiogel trwy'r sianel wedi'i hamgryptio gan ddefnyddio'r “nodwedd SSP” o ROM cychwyn ynghyd ag offer STM32.

- Ar ddiwedd darparu cyfrinachau, gall y cwsmer asio:

- Ar STM32MP13xx cyfrinair RMA 32 did yn OTP_CFG56 (dylai cyfrinair fod yn 0).

- Ar STM32MP15xx cyfrinair RMA 15 did yn OTP_CFG56[14:0], cyfrinair RMA_RELOCK yn OTP_CFG56[29:15].

Dylai'r cyfrinair fod yn wahanol i 0.

- Gosodwch yr OTP_CFG56 fel “clo rhaglennu parhaol” i osgoi rhaglennu diweddarach yn 0xFFFFFF a chaniatáu mynd i mewn i'r cyflwr RMA heb wybodaeth am y cyfrinair cychwynnol.

- Gwiriwch raglennu cywir yr OTP_CFG56 trwy wirio'r gofrestr BSEC_OTP_STATUS.

- Yn olaf, mae'r ddyfais yn cael ei newid i OTP_SECURED ar gau:

- Ar STM32MP13xx trwy asio OTP_CFG0[3] = 1 ac OTP_CFG0[5] = 1.

- Ar STM32MP15xx trwy asio OTP_CFG0[6] = 1.

Gellir ailagor y ddyfais yn nhalaith RMA i'w harchwilio gan STMicroelectronics

- Pan fydd y ddyfais mewn cyflwr caeedig OTP_SECURED, nid yw "cist datblygu" yn bosibl mwyach.

RMA nodi manylion cofnodi

Fel y soniwyd yn flaenorol, defnyddir y dalaith RMA i ailagor y modd prawf llawn yn ddiogel heb unrhyw ddatguddiad o gyfrinachau a ddarperir gan gwsmeriaid. Gwneir hyn diolch i swyddogaethol JTAG mewnbynnau tra bod holl gyfrinachau cwsmeriaid yn cael eu cadw'n anhygyrch gan y caledwedd.

Rhag ofn y bydd angen dadansoddi methiant aample mae angen mynd i gyflwr RMA (gweler Ffigur 5. Newid i OTP_SECURED ar gau ), sy'n sicrhau cyfrinachau cwsmeriaid ac yn ailagor dadfygio yn ddiogel ac nad yw'n ddiogel yn DAP.

- Mae'r cwsmer yn symud yn BSEC_JTAGWRTH gofrestru'r cyfrinair RMA gan ddefnyddio JTAG (dim ond gwerthoedd gwahanol i 0 sy'n cael eu derbyn).

- Mae'r cwsmer yn ailosod y ddyfais (pin NRST).

Nodyn: Yn ystod y cam hwn, mae'r cyfrinair yn BSEC_JTAGNi ddylid dileu cofrestr IN. Felly, rhaid i'r NRST beidio â chau'r VDD na'r cyflenwadau pŵer VDDCORE i lawr. Ni ddylai ychwaith gael ei gysylltu â'r pin NJTRST. Rhag ofn y defnyddir STPMIC1x, efallai y bydd yn orfodol cuddio'r cyflenwadau pŵer yn ystod yr ailosod. Gwneir hyn trwy raglennu'r gofrestr opsiwn mwgwd STPMIC1x (BUCKS_MRST_CR) neu ddileu'r gwrthydd a ychwanegwyd ar gyfer RMA ar y bwrdd rhwng STPMICx RSTn a STM32MP1xxx NRST (gweler Ffigur 3). - Mae'r ROM cychwyn yn cael ei weithredu ac yn gwirio'r cyfrinair RMA a gofnodwyd yn BSEC_JTAGMEWN gyda OTP_CFG56.RMA_PASSWORD:

• Os yw'r cyfrineiriau'n cyfateb, mae'r sample yn dod yn RMA_LOCK sample (am byth ar STM32MP13xx).

• Os nad yw'r cyfrineiriau'n cyfateb, mae'r sample yn aros yn y cyflwr caeedig OTP_SECURED ac mae cownter "ailagor treialon" RMA yn cael ei gynyddu mewn OTP.

Nodyn: Dim ond tri threial ailagor RMA sydd wedi'u hawdurdodi. Ar ôl methu tri threial, nid yw ailagor RMA yn bosibl mwyach. Mae'r ddyfais yn aros yn ei chyflwr cylch bywyd gwirioneddol. - Mae'r cwsmer yn ailosod yr ail waith yr samptrwy pin NRST:

• mae'r LED ar PA13 ymlaen (os yw wedi'i gysylltu)

• mae mynediad dadfygio DAP yn cael ei ailagor. - Gellir anfon y ddyfais i STMicroelectronics.

- Ar ôl ailosod (pin NRST neu ailosod unrhyw system), mae'r ROM cychwyn yn cael ei ddefnyddio:

• Mae'n canfod bod OTP8.RMA_LOCK = 1 (RMA cloi sample).

• Mae'n sicrhau'r holl STMicroelectroneg a chyfrinachau cwsmeriaid.

• Mae'n ailagor mynediad dadfygio DAP yn ddiogel a heb fod yn ddiogel.

Tra mewn cyflwr RMA mae'r rhan yn anwybyddu'r pinnau Boot ac nid yw'n gallu cychwyn o fflach allanol na USB / UART.

Datgloi manylion RMA

Ar STM32MP15xx mae'n bosibl datgloi'r ddyfais o RMA a mynd yn ôl i gyflwr SECURE_CLOSED.

Yn BSEC_JTAGYN y gofrestr, mae'r cwsmer yn symud y cyfrinair datgloi RMA gan ddefnyddio JTAG (dim ond gwerthoedd gwahanol i 0 sy'n cael eu derbyn)

- Mae'r cwsmer yn ailosod y ddyfais (pin NRST).

Nodyn: Dim ond tri threial Datglo RMA sydd wedi'u hawdurdodi. Ar ôl tri threialon a fethwyd, nid yw datgloi RMA yn bosibl mwyach. Mae'r ddyfais yn aros yn ei chyflwr cylch bywyd RMA. - Mae'r cwsmer yn ailosod yr ail waith yr samptrwy pin NRST:

• mae'r LED ar PA13 ymlaen (os yw wedi'i gysylltu),

• mae'r ddyfais mewn cyflwr SECURE_CLOSED (mae mynediad dadfygio DAP ar gau).

Talaith RMA yn mynd i mewn i JTAG sgript examples

STM32MP13xx sgript cynampmae llai i nodi'r cyfrinair a nodi'r cyflwr RMA ar gael mewn sip ar wahân file. Gellir eu defnyddio gyda Trace32, OpenOCD gan ddefnyddio stiliwr STLINK, OpenOCD gan ddefnyddio stiliwr cydnaws CMSIS-DAP (ar gyfer cynampgyda ULink2). Mae gwybodaeth ar gael yn www.st.com. Cyfeiriwch at gynnyrch STM32MP13xx “CAD resources” yn yr adran “manyleb gweithgynhyrchu bwrdd”.

Cyn tebygampgellir deillio les ar gyfer dyfeisiau STM32MP15xx. Mae cynample i fynd i mewn i gyflwr RMA ac i adael cyflwr RMA ar gyfer Trace32 ar gael mewn sip ar wahân file. Mae gwybodaeth ar gael yn www.st.com. Cyfeiriwch at “adnoddau CAD” cynnyrch STM32MP15x yn yr adran “manyleb gweithgynhyrchu bwrdd”.

Hanes adolygu

Tabl 4. Hanes adolygu'r ddogfen

| Dyddiad | Fersiwn | Newidiadau |

| 13-Chwefror-23 | 1 | Rhyddhad cychwynnol. |

HYSBYSIAD PWYSIG DARLLENWCH YN OFALUS

Mae STMicroelectronics NV a'i is-gwmnïau (“ST”) yn cadw'r hawl i wneud newidiadau, cywiriadau, gwelliannau, addasiadau a gwelliannau i gynhyrchion ST a/neu i'r ddogfen hon ar unrhyw adeg heb rybudd. Dylai prynwyr gael y wybodaeth berthnasol ddiweddaraf am gynhyrchion ST cyn gosod archebion. Gwerthir cynhyrchion ST yn unol â thelerau ac amodau gwerthu ST sydd ar waith ar adeg cydnabod yr archeb.

Prynwyr yn unig sy'n gyfrifol am ddewis, dewis a defnyddio cynhyrchion ST ac nid yw ST yn cymryd unrhyw atebolrwydd am gymorth ymgeisio neu ddyluniad cynhyrchion prynwyr.

Ni roddir trwydded, yn benodol nac yn oblygedig, i unrhyw hawl eiddo deallusol gan ST yma.

Bydd ailwerthu cynhyrchion ST gyda darpariaethau gwahanol i'r wybodaeth a nodir yma yn dileu unrhyw warant a roddir gan ST ar gyfer cynnyrch o'r fath.

Mae ST a'r logo ST yn nodau masnach ST. I gael gwybodaeth ychwanegol am nodau masnach ST, cyfeiriwch at www.st.com/trademarks. Mae pob enw cynnyrch neu wasanaeth arall yn eiddo i'w perchnogion priodol.

Mae gwybodaeth yn y ddogfen hon yn disodli ac yn disodli gwybodaeth a ddarparwyd yn flaenorol mewn unrhyw fersiynau blaenorol o'r ddogfen hon.

© 2023 STMicroelectroneg Cedwir pob hawl

AN5827 – Dat 1

AN5827 – Diwygiad 1 – Chwefror 2023

Am wybodaeth bellach cysylltwch â'ch swyddfa werthu STMicroelectroneg leol.

www.st.com

Dogfennau / Adnoddau

|

Microbrosesyddion Cyfres STMicroelectroneg STM32MP1 [pdfCanllaw Defnyddiwr Microbroseswyr Cyfres STM32MP1, Cyfres STM32MP1, Microbroseswyr |