AN5827

Nota di l'applicazione

Linee guida per entra in u statu RMA nantu à i MPU di a serie STM32MP1

Introduzione

I microprocessori di a serie STM32MP1 includenu i dispositi STM32MP15xx è STM32MP13xx.. Questa nota di l'applicazione furnisce infurmazioni per sustene u prucessu d'ingressu di u statu di l'analisi di materiale di ritornu, chjamatu RMA in stu documentu.

infurmazione generale

Stu documentu s'applica à i microprocessori di a serie STM32MP1 basati in core Arm® Cortex®

Nota: Arm hè una marca registrata di Arm Limited (o i so filiali) in i Stati Uniti è / o in altrò.

Documenti di riferimentu

| Riferimentu | Titulu di u documentu |

| STM32MP13xx | |

| AN5474 | Cumincià cù u sviluppu di hardware di linee STM32MP13x |

| DS13878 | Arm® Cortex®-A7 finu à 1 GI-ft, 1xETH, 1 xADC, 24 timers, audio |

| DS13877 | Arm® Cortex®-A7 finu à 1 GHz, 1xETH, 1 xADC, 24 timers, audio, criptu è adv. sicurità |

| DS13876 | Arm® Cortex®-A7 finu à 1 GI-ft, 2xETH, 2xCAN FD, 2xADC. 24 timers, audio |

| DS13875 | Arm® Cortex®-A7 finu à 1 GHz, 2xETH, 2xCAN FD, 2xADC, 24 timers, audio, criptu è adv. sicurità |

| DS13874 | Arm® Cortex®-A7 finu à 1 GHz, LCD-TFT, interfaccia di camera, 2xETH, 2xCAN FD, 2xADC, 24 timers, audio |

| DS13483 | Arm® Cortex®-A7 finu à 1 GHz, LCD-TFT, interfaccia di càmera, 2xETH, 2xCAN FD, 2xADC, 24 timers, audio, criptu è adv. sicurità |

| 0475 RM | STM32MP13xx MPU avanzati basati su Arm0 a 32 bit |

| STM32MP15xx | |

| AN5031 | Cumincià cù u sviluppu di hardware di linea STM32MP151, STM32MP153 è STM32MP157 |

| DS12500 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. interfacce, 25 timers, adv. analogicu |

| DS12501 | Arm® Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 35 comm. interfacce, 25 timers, adv. analogu, criptu |

| DS12502 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. interfacce, 29 timers, adv. analogicu |

| DS12503 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, TFT, 37 comm. interfacce, 29 timers, adv. analogu, criptu |

| DS12504 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 comm. interfacce, 29 timers, adv. analogicu |

| DS12505 | Arm® dual Cortex®-A7 800 MHz + Cortex®-M4 MPU, GPU 3D, TFT/DSI, 37 comm. interfacce, 29 timers, adv. analogu, criptu |

| 0441 RM | STM32MP151 MPU avanzate basate su Arm® a 32 bit |

| 0442 RM | STM32MP153 MPU avanzati basati su Arnie a 32 bit |

| 0436 RM | STM32MP157 MPU avanzati basati su Arm0 a 32 bit |

Termini è acronimi

Table 2. Definizione di acronimi

| Terminu | Definizione |

| FAR | Richiesta di analisi di fallimentu: flussu utilizatu per rinvià u dispositivu suspettu per l'analisi à STMicroelectronics. Per rinfurzà u pienu testability di u dispusitivu durante tali analisi, u dispusitivu deve esse in statu RMA. |

| JTAG | Gruppu d'azzione di prova cumuna (interfaccia di debug) |

| PMIC | Circuitu di gestione di l'energia esterna chì furnisce diverse alimentazione di piattaforma, cù una grande controllabilità attraversu signali è interfaccia seriale. |

| RMA | Analisi di materiale di ritornu: statu specificu di u dispusitivu in u ciculu di vita chì permette l'attivazione di u modu di prova cumpleta cum'è necessariu STMicroelectronics per scopi di analisi di fallimentu. |

1. In questu ducumentu, l'acronimu RMA ùn si riferisce nudda parte à l'"accettazione di u materiale di ritornu" chì hè u flussu utilizatu per rinvià e parti micca utilizzate (stock cliente per ex.ample).

Statu RMA in u flussu FAR

U flussu FAR cunsiste in rinvià un dispositivu à STMicroelectronics per una analisi più profonda di fallimentu in casu di un suspettatu prublema di qualità. A parte deve esse tornata testabile à ST per chì l'analisi pò esse realizatu.

- A parte deve esse in u statu RMA

- A parte deve esse fisicamente cumpatibile cù u dispusitivu originale (dimensione di a bola, pitch, etc.)

U ciclu di vita di u produttu STM32MP13xx

Nantu à i dispositi STM32MP13xx, prima di rinvià u dispusitivu, u cliente deve entre in u statu RMA cù una password di 32-bit predefinita da u cliente inserita da u J.TAG (vede Sezione 3). Una volta intrutu in u statu RMA, u dispusitivu ùn hè più utilizzabile per a produzzione (vede a Figura 1) è u modu di prova cumpleta hè attivatu per STMicroelectronics per cuntinuà l'investigazione mentre chì tutti i sicreti di i clienti (OTP superiore cum'è descrittu in u manuale di riferimentu) sò tenuti inaccessibili. da u hardware.

A figura sottu mostra u ciclu di vita di u produttu di i dispositi STM32MP13xx. Mostra chì una volta chì u statu RMA hè intrutu in u dispusitivu ùn pò micca turnà à altri modi.

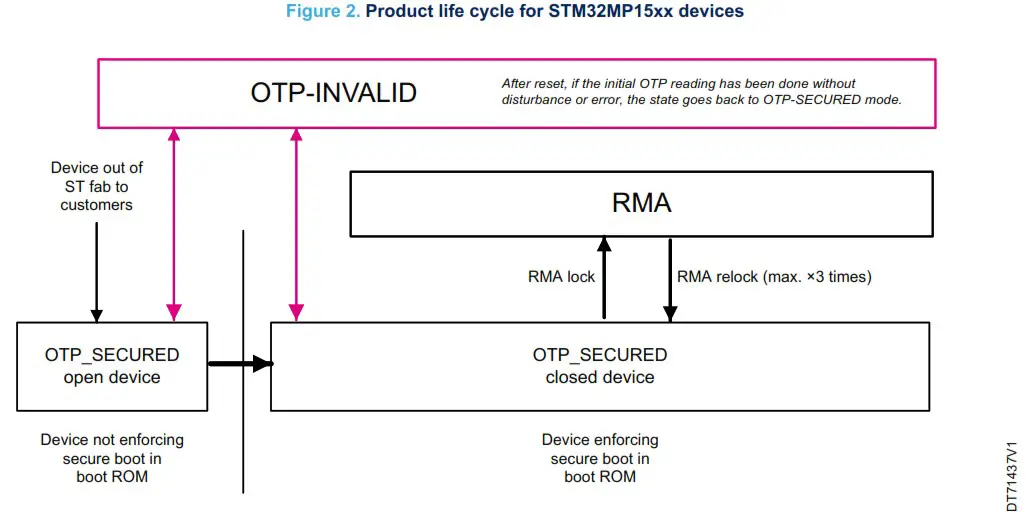

U ciclu di vita di u produttu STM32MP15xx

Nantu à i dispositi STM32MP15xx, prima di rinvià u dispusitivu, u cliente deve entre in u statu RMA cù una password di 15-bit predefinita da u cliente inserita da u J.TAG (vede Sezione 3). Una volta intrutu in u statu RMA, u dispusitivu pò turnà à u statu SECURE_CLOSED inserendu una password "RMA_RELOCK" predefinita da u cliente. Solu 3 prucessi RMA à RMA_RELOCKED stati di transizione sò permessi (vede a Figura 2). In u statu RMA, u modu di prova cumpleta hè attivatu per STMicroelectronics per cuntinuà l'investigazione mentre tutti i sicreti di i clienti (OTP superiore cum'è descrittu in u manuale di riferimentu) sò manteni inaccessibili da u hardware.

A figura sottu mostra u ciclu di vita di u produttu di i dispositi STM32MP15x.

Limitazioni di u cunsigliu statale di RMA

Per attivà u statu RMA, i seguenti limitazioni sò necessarii.

U JTAG l'accessu deve esse dispunibule

I signali NJTRST è JTDI, JTCK, JTMS, JTDO (pin PH4, PH5, PF14, PF15 nantu à i dispositi STM32MP13xx) deve esse accessibile. In certi arnesi, u JTDO ùn hè micca necessariu (per esample, Trace32) nant'à altri cum'è OpenOCD u strumentu cuntrolla u dispusitivu JTAG ID via JTDO prima di eseguisce u JTAG sequenza.

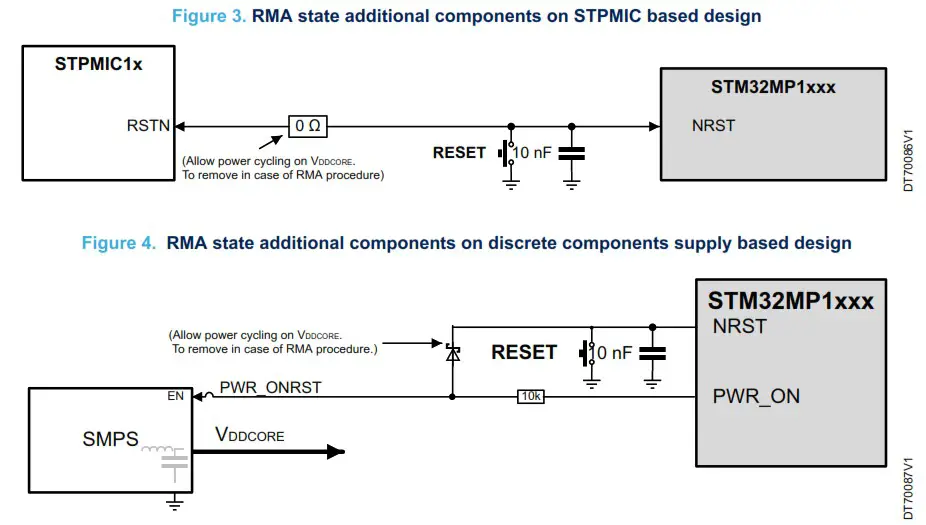

L'alimentazione VDDCORE è VDD ùn deve esse micca spenta quandu u pin NRST hè attivatu

In u disignu di riferimentu ST, u NRST attiva un ciclu di putenza di u STPMIC1x o regulatori di putenza di cumpunenti discreti esterni. Una implementazione pussibule hè mostrata in u disignu di riferimentu example furnitu in a nota di l'applicazione Accuminciamentu cù u sviluppu di hardware di linee STM32MP13x (AN5474). A Figura 3 è a Figura 4 sò versioni simplificate chì mostranu solu i cumpunenti di u statu RMA. U listessu vale per i dispositi STM32MP15xx.

Un pianu simplice cù solu u JTAG pin è socket appropritatu ponu esse usatu solu per scopi di password RMA (in casu ùn hè micca pussibule di accede à JTAG nantu à u bordu di pruduzzione). In questu casu, u cliente deve prima unsolder u dispusitivu da u bordu di pruduzzione è ripopulate e palle di pacchettu.

A scheda deve avè i pin STM32MP1xxx elencati in a Tabella 3 cunnessi cum'è indicatu. Altri pin ponu esse lasciati flottanti.

Tabella 3. Cunnessione Pin per una scheda simplice utilizata per l'ingressu di password RMA

| Pin name (signale) | Cunnessu à | Cumentu | |

| STM32MP13xx | STM32MP15xx | ||

| JTAG è resettate | |||

| NJTRST | NJRST | JTAG cunnessu | |

| PH4 (JTDI) | JTDI | ||

| PH5 (JTDO) | JTDO | Ùn hè micca necessariu in qualchì strumentu di debug cum'è Trace32 | |

| PF14 (JTCK) | JTCK | ||

| PF15 (JTMS) | JTMS | ||

| NRST | NRST | Reset buttone | Cù condensatore 10 nF à VSS |

| Forniture di energia | |||

| VDDCORE. VDDCPU | VDDCORE | Alimentazione esterna | Consultate a scheda di dati di u produttu per u tipicu valore |

| VDD. VDDSD1. VDDSD2. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON |

VDD. VDD_PLL. VDD_PLL2. VBAT. VDD_ANA. PDR_ON. PDR_ON_CORE |

3.3 V esternu supply |

Deve esse dispunibule prima è sguassate ultimu (pò esse inseme cù altri forniture) |

| VDDA, VREF+, VDD3V3_USBHS. VDDO_DDR |

VDDA. VREF+. VDD3V3_USBHS. VDDO_DDR. VDD_DSI. VDD1V2_DSI_REG. VDD3V3_USBFS |

0 | ADC. VREFBUF, USB, DDR micca usatu |

| VSS. VSS_PLL. VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_US131-IS |

VSS. VSS_PLL, VSS_PLL2. VSSA. VSS_ANA. VREF-. VSS_USBHS. VSS_DSI |

0 | |

| VDDA1V8_REG. VDDA1V1_REG |

VDDA1V8_REG. VDDA1V1_REG |

flottante | |

| Altru | |||

| BYPASS_REG1V8 | BYPASS_REG1V8 | 0 | Regulatore 1V8 attivatu per difettu (REG 18E = 1) |

| PC15- OSC32_OUT | PC15- OSC32_OUT | flottante | |

| PC14- OSC32_IN | PC14- OSC32_IN | Oscillatori esterni ùn sò micca usati (boot ROM per utilizà l'oscillatore internu HSI) |

|

| PHO-OSC_IN | PHO-OSC_IN | ||

| PH1-0SC_OUT | PH1-0SC_OUT | ||

| USB_RREF | USB_RREF | flottante | USB micca usatu |

| P16 (BOOT2) | BOTTA 2 | X | Entra in u statu RMA travaglia qualunque sia i valori di boot (2:0). |

| PI5 (BOOT1) | 60011 | X | |

| PI4 (BOOTO) | BOTO | X | |

| NRST_CORE | 10 nF à VSS | Pulsazione interna nantu à NRST_CORE | |

| PA13 (BOOTFAILN) | PA13 (BOOTFAILN) | LED | Opcional |

Requisiti precedenti per permette l'ingressu futuru di u statu RMA

A pussibilità di entre in u statu RMA deve esse stallatu da u cliente inserendu una password durante a produzzione di u cliente dopu a provisioning secreta

- U dispusitivu quandu hè speditu da STMicroelectronics hè in u statu apertu OTP_SECURED.

- U dispusitivu cuntene ST sicreti chì sò prutetti da boot ROM, è ùn sicretu clienti.

- À u resettore o dopu l'esecuzione di a ROM di boot, l'accessu DAP pò esse riaperto da Linux o da u modu di "boot di sviluppu" di a ROM di boot (OTP_SECURED open + boot pins BOOT [2: 0] = 1b100 + reset).

- Mentre in OTP_SECURED apertu, u cliente deve furnisce i so sicreti in OTP:

- direttamente da u cliente à propiu risicu o

- in modu sicuru via u canale criptatu utilizendu a "funzione SSP" di a ROM di boot inseme cù l'arnesi STM32.

- À a fine di l'approvvigionamentu di secreti, u cliente pò fusione:

- In STM32MP13xx una password RMA di 32 bit in OTP_CFG56 (password deve esse 0).

- In STM32MP15xx una password RMA di 15 bit in OTP_CFG56[14:0], una password RMA_RELOCK in OTP_CFG56[29:15].

A password deve esse diversa da 0.

- Stabilite l'OTP_CFG56 cum'è "serratura di prugrammazione permanente" per evità a prugrammazione più tardi à 0xFFFFFF è permette di entre in u statu RMA senza cunniscenza di a password iniziale.

- Verificate a prugrammazione curretta di l'OTP_CFG56 cuntrollandu u registru BSEC_OTP_STATUS.

- Infine, u dispusitivu hè cambiatu à OTP_SECURED chjusu:

- Nantu à STM32MP13xx fusione OTP_CFG0[3] = 1 è OTP_CFG0[5] = 1.

- Nantu à STM32MP15xx fusendu OTP_CFG0[6] = 1.

U dispusitivu pò esse riapertura in u statu RMA per l'investigazione da STMicroelectronics

- Quandu u dispusitivu hè in u statu chjusu OTP_SECURED, "boot di sviluppu" ùn hè più pussibule.

Statu RMA chì entre in dettagli

Cum'è diciatu prima, u statu RMA hè adupratu per riapertura in modu sicuru u modu di prova cumpletu senza alcuna esposizione di i secreti furniti da u cliente. Questu hè fattu grazia à u funziunale JTAG inputs mentri tutti i sicreti di i clienti sò tenuti inaccessibili da u hardware.

In casu ci hè un requisitu per l'analisi nantu à un sample ci hè u bisognu di andà à u statu RMA (vede Figura 5. Cambia à OTP_SECURED chjusu ), chì pruteghja i sicreti di u cliente è riapertura di debug sicuru è micca sicuru in DAP.

- U cliente cambia in BSEC_JTAGIN registrate a password RMA cù JTAG (Solu i valori diffirenti da 0 sò accettati).

- U cliente resetta u dispusitivu (NRST pin).

Nota: Duranti stu passu, a password in BSEC_JTAGU registru IN ùn deve esse sguassatu. Cusì, u NRST ùn deve micca chjude u VDD nè l'alimentazione VDDCORE. Ùn deve ancu esse cunnessu à u pin NJTRST. In casu STPMIC1x hè utilizatu, puderia esse ubligatoriu per maschera l'alimentazione durante u reset. Questu hè fattu da prugrammazione di u registru di l'opzione di maschera STPMIC1x (BUCKS_MRST_CR) o sguassate a resistenza aghjuntu per RMA nantu à u bordu trà STPMICx RSTn è STM32MP1xxx NRST (vede a Figura 3). - A ROM di boot hè invucata è verifica a password RMA inserita in BSEC_JTAGIN cù OTP_CFG56.RMA_PASSWORD:

• Sè i password currispondenu, u sample diventa un RMA_LOCK sample (per sempre nantu à STM32MP13xx).

• Sè i password ùn currispondenu, u sample ferma in u statu chjusu OTP_SECURED è un contatore RMA di "riapertura di prucessi" hè aumentatu in OTP.

Nota: Solu trè prucessi di riapertura di RMA sò autorizati. Dopu trè prucessi falluti, a riapertura di RMA ùn hè più pussibule. U dispusitivu ferma in u so statu di ciclu di vita attuale. - U cliente resetta una seconda volta u sample via NRST pin:

• u LED in PA13 hè accesa (se cunnessu)

• l'accessu di debug DAP hè riapertura. - U dispusitivu pò esse mandatu à STMicroelectronics.

- Dopu à u reset (pin NRST o qualsiasi reset di u sistema), a ROM di boot hè invucata:

• It detects chì OTP8.RMA_LOCK = 1 (RMA locked sample).

• It secures tutti i STMicroelectronics è sicreti clienti.

• It reopens DAP debug accessu in sicuru è micca sicuru.

Mentre in u statu RMA, a parte ignora i pin di Boot è ùn hè micca capaci di boot da u flash esternu nè USB / UART.

Dettagli di sbloccare RMA

In STM32MP15xx hè pussibule di sbloccare u dispusitivu da RMA è torna à u statu SECURE_CLOSED.

In BSEC_JTAGIN u registru, u cliente cambia a password di sbloccare RMA utilizendu JTAG (Solu i valori diversi da 0 sò accettati)

- U cliente resetta u dispusitivu (NRST pin).

Nota: Solu trè prucessi RMA Unlock sò autorizati. Dopu trè prucessi falluti, unlock RMA ùn hè più pussibule. U dispusitivu ferma in u so statu di ciclu di vita RMA. - U cliente resetta una seconda volta u sample via NRST pin:

• u LED in PA13 hè accesa (se cunnessu),

• u dispusitivu hè in statu SECURE_CLOSED (accessu debug DAP hè chjusu).

Statu RMA chì entra in JTAG script examples

STM32MP13xx script examples per entre a password è entre in u statu RMA sò dispunibuli in un zip separatu file. Puderanu esse usatu cù Trace32, OpenOCD cù a sonda STLINK, OpenOCD cù a sonda cumpatibile CMSIS-DAP (per esempiuample ULink2). L'infurmazione pò esse truvata à www.st.com. Fate riferimentu à u produttu STM32MP13xx "Risorse CAD" in a sezione "Specificazioni di fabricazione di bordu".

Simile exampi pò esse derivati per i dispositi STM32MP15xx. Un example per entre in u statu RMA è per esce da u statu RMA per Trace32 hè dispunibule in un zip separatu file. L'infurmazione pò esse truvata à www.st.com. Riferite à u pruduttu STM32MP15x "Risorse CAD" in a sezione "Specificazioni di fabricazione di bordu".

Storia di rivisione

Table 4. Storia di rivisione di documenti

| Data | Versione | Cambiamenti |

| 13-Feb-23 | 1 | Liberazione iniziale. |

AVVISU IMPORTANTE LEGGIU ATTENTAMENTE

STMicroelectronics NV è e so filiali ("ST") si riservanu u dirittu di fà cambiamenti, correzioni, miglioramenti, mudificazioni è migliure à i prudutti ST è / o à stu documentu in ogni mumentu senza avvisu. I cumpratori anu da ottene l'ultime informazioni pertinenti nantu à i prudutti ST prima di fà ordini. I prudutti ST sò venduti in cunfurmità cù i termini è e cundizioni di vendita di ST in vigore à u mumentu di a ricunniscenza di l'ordine.

I cumpratori sò solu rispunsevuli di a scelta, a selezzione è l'usu di i prudutti ST è ST ùn assume micca responsabilità per l'assistenza di l'applicazione o u disignu di i prudutti di l'acquirente.

Nisuna licenza, espressa o implicita, à qualsiasi dirittu di pruprietà intellettuale hè cuncessa da ST quì.

A rivendita di i prudutti ST cù disposizioni diverse da l'infurmazioni stabilite quì annullerà ogni garanzia accordata da ST per tali pruduttu.

ST è u logo ST sò marchi di ST. Per infurmazioni supplementari nantu à i marchi ST, riferite à www.st.com/trademarks. Tutti l'altri prudutti o nomi di serviziu sò a pruprietà di i so rispettivi pruprietarii.

L'infurmazioni in stu documentu rimpiazzanu è rimpiazzanu l'infurmazioni furnite prima in qualsiasi versione precedente di stu documentu.

© 2023 STMicroelectronics Tutti i diritti riservati

AN5827 - Rev 1

AN5827 - Rev 1 - ferraghju 2023

Per più infurmazione cuntattate u vostru uffiziu di vendita STMicroelectronics locale.

www.st.com

Documenti / Risorse

|

Microprocessori STMicroelectronics Serie STM32MP1 [pdfGuida di l'utente Microprocessori STM32MP1 Series, STM32MP1 Series, Microprocessori |