# **BOARDCON CM210-II Embedded Design System on Module** for Data Terminals User Manual

<u>Home</u> » <u>Boardcon</u> » BOARDCON CM210-II Embedded Design System on Module for Data Terminals User Manual <sup>™</sup>

#### **Contents**

- 1 BOARDCON CM210-II Embedded Design System on Module for Data Terminals

- **2 Product Information**

- **3 Product Usage Instructions**

- 4 Introduction

- 5 Block Diagram

- **6 Pin Definition**

- 7 Hardware Design Guide

- **8 Product Electrical Characteristics**

- 9 Documents / Resources

- 9.1 References

- **10 Related Posts**

**BOARDCON CM210-II Embedded Design System on Module for Data Terminals**

## **Product Information**

# **Specifications**

- CPU: Samsung S5PV210AH-A01GHz ARM Cortex A8 Core

- RAM: On-board 512MB DDR2-RAM

- ROM: On-board SLC or MLC 256MB Nand Flash

- Power Input: 5V & 3.3V

- Features: PowerVR SGX540 3D Graphics Engine, HD Mult-Format video codec, HDMI 1.3 output, AC97

AUDIO interface, and more

# **Product Usage Instructions**

## Introduction

This manual provides an overview of the board, its benefits, features specifications, and setup procedures. It also includes important safety information.

# **Hardware Design Guide**

Refer to the Peripheral Circuit Reference and PCB Footprint sections for detailed hardware design guidance.

## **Product Electrical Characteristics**

Understand the dissipation, temperature, and reliability of tests for optimal product performance.

## **FAQ**

- Q: What is the CPU of CM210-II?

- A: The CPU is Samsung S5PV210AH-A01GHz ARM Cortex A8 Core.

- Q: How much RAM does the module have?

#### Introduction

#### **About this Manual**

This manual is intended to provide the user with an overview of the board and benefits, complete features specifications, and set up procedures. It contains important safety information as well.

# Feedback and Update to this Manual

To help our customers make the most of our products, we are continually making additional and updated resources available on the Boardcon website (www.boardcon.com, www.armdesigner.com).

These include manuals, application notes, programming examples, and updated software and hardware. Check in periodically to see what's new!

When we are prioritizing work on these updated resources, feedback from customers is the number one influence, If you have questions, comments, or concerns about your product or project, please no hesitate to contact us at support@armdesigner.com.

#### **Limited Warranty**

Boardcon warrants this product to be free of defects in material and workmanship for a period of one year from date of buy. During this warranty period Boardcon will repair or replace the defective unit in accordance with the following process:

A copy of the original invoice must be included when returning the defective unit to Boardcon. This limited warranty does not cover damages resulting from lighting or other power surges, misuse, abuse, abnormal conditions of operation, or attempts to alter or modify the function of the product. This warranty is limited to the repair or replacement of the defective unit. In no event shall Boardcon be liable or responsible for any loss or damages, including but not limited to any lost profits, incidental or consequential damages, loss of business, or anticipatory profits arising from the use or inability to use this product.

Repairs make after the expiration of the warranty period are subject to a repair charge and the cost of return shipping. Please contact Boardcon to arrange for any repair service and to obtain repair charge information.

#### Summary

CM210-II is System on Module (SOM) based on the Samsung's S5PV210AH-A0 application processor with ARM Cortex-A8 core in small size, powerful 3D accelerator full HD (1080P) and high-performance HW multimedia. The module is perfect combination of minimum size, low cost and high performance.

Stable electrical performance, Successful mass production. applicable to MID, POS, PND, and Terminal controller.

#### **Features**

# • CPU

- Samsung S5PV210AH-A0 1GHz ARM Cortex A8 Core

- 64KB I&D Cache, 512KB L2 Cache

- PowerVR SGX540 3D Graphics Engine

- HD Mult-Format video codec(MPEG2, MPEG4, H.264, Divx, VC-1)

#### RAM

- o On-board 512MB DDR2-RAM

- 64bit data bus

- DDR clock frequency as high as 200MHz

#### ROM

- On-board SLC or MLC 256MB Nand Flash

- Up to 16GB

#### POWER

- high-efficiency DC-DC converter

- 5V & 3.3V Power input

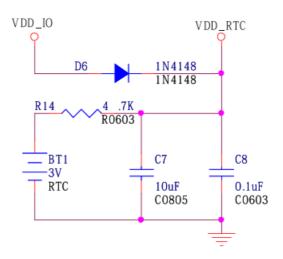

- RTC

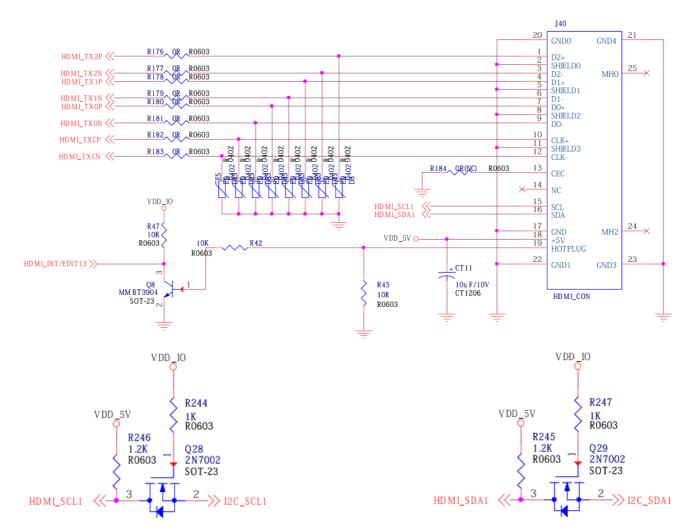

- HDMI 1.3 output (up to 1080P)

- TV output

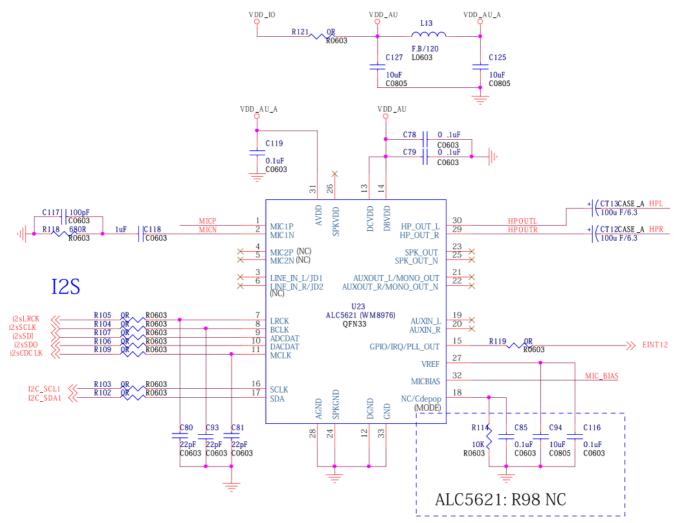

- AC97 AUDIO interface

- Watchdog

- · Boot mode setting

- 4 UART

- 2 Three line and 2 Five line

- Support IrDA

- 1 IIC interface(CH1)

- 1 HS-SPI interface

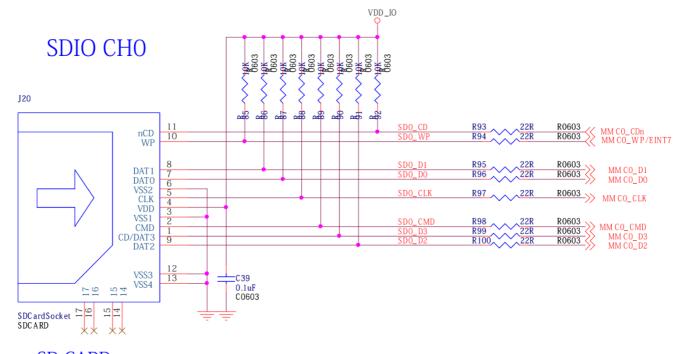

- SDIO interface

- o 2 4bit SDIO or 1 8bit SDIO

- Boot in SDIO CH0

- 6 12bit ADIN or 2 ADIN and 4 wire RES-touch panel interface

- 32 interrupt sources

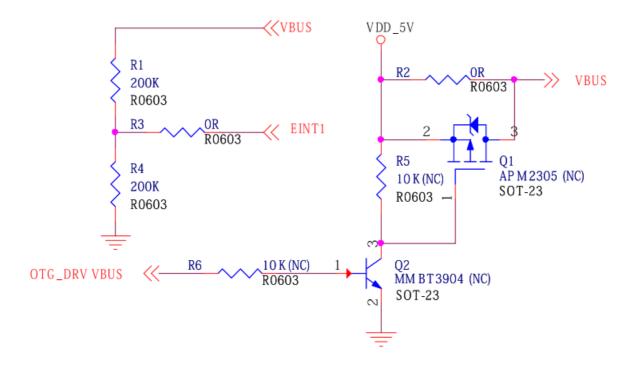

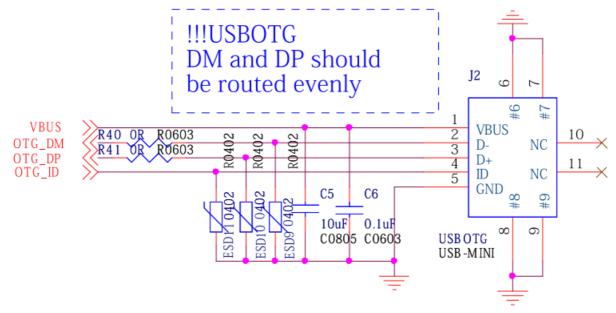

- 2 2.0 USB interface (OTG and HOST)

- 1 32bit PWM Timer out

- 1 Camera interface

- Max 8192 x 8192 pixels input

- ITU601/656 8bit support

- TFT LCD BUS

- 24BPP RGB parallel output

- PIP(OSD) function

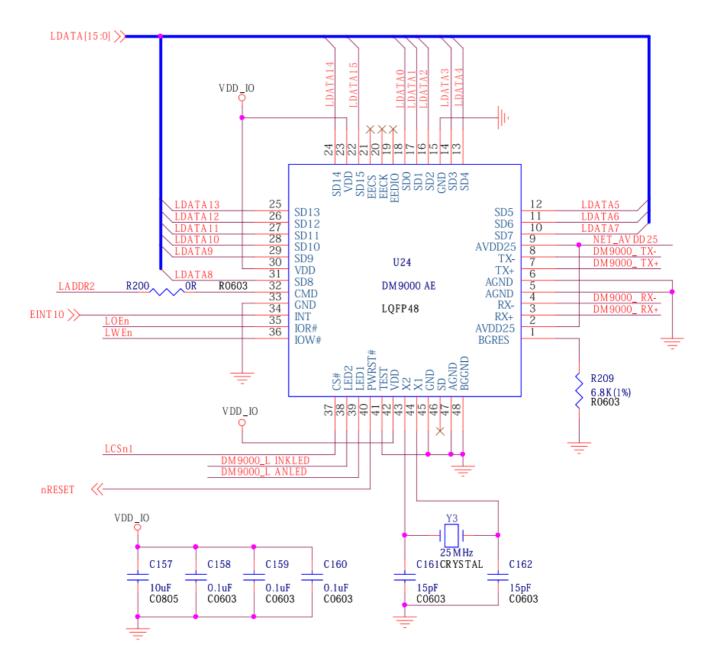

- 16bit system BUS

# **Block Diagram**

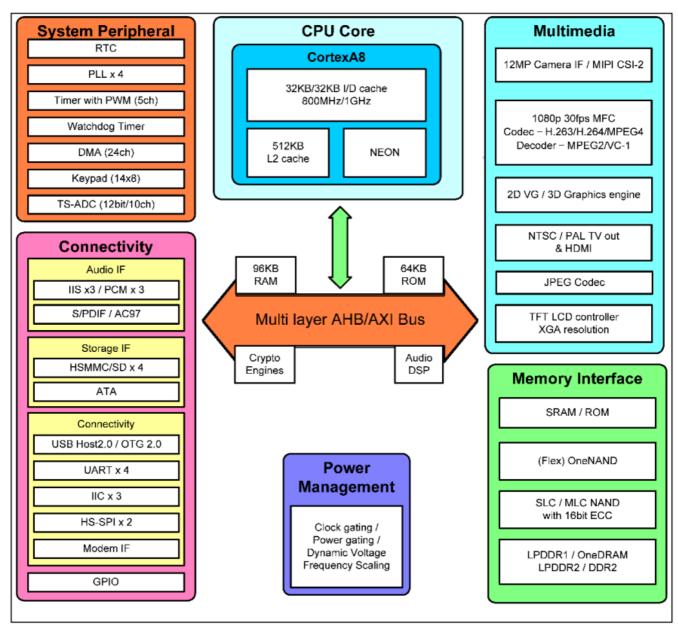

1. S5PV210 Block Diagram

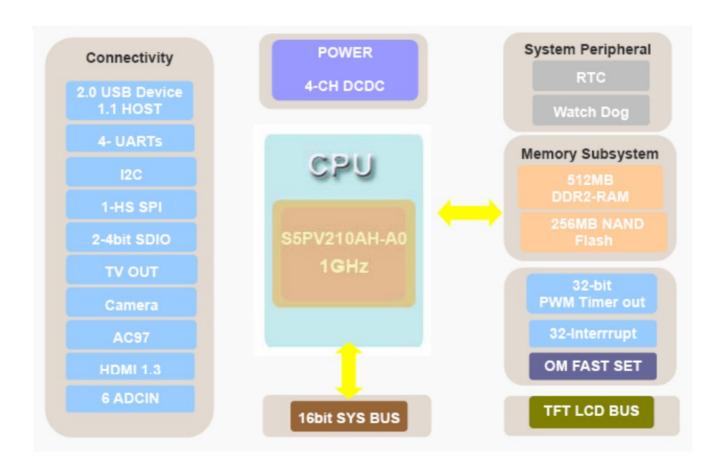

2. CM210-II Block Diagram

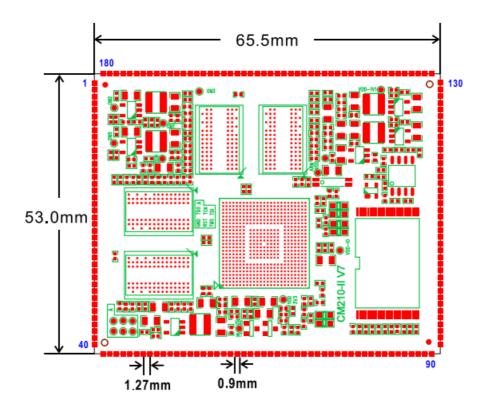

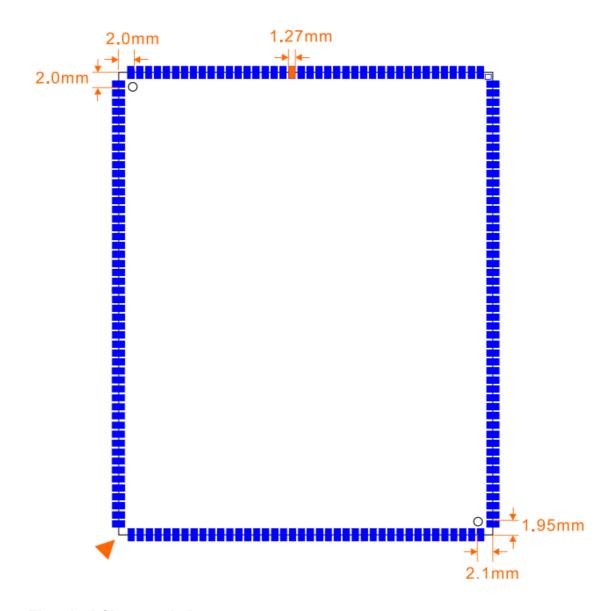

# **PCB Dimension**

# **Pin Definition**

| Pin | Signal name | Function              | Description                        | IO Type |

|-----|-------------|-----------------------|------------------------------------|---------|

| 1   | DCIN        | 5V Power in           | Can connect to 3.7V Li battery     | Р       |

| 2   | DCIN        | 5V Power in           | Can connect to 3.7V Li battery     | Р       |

| Pin | Signal name | Function              | Description                        | IO Type |

| 3   | DCIN        | 5V Power in           | Can connect to 3.7V Li battery     | Р       |

| 4   | VDD_IO      | 3.3V Power in         |                                    | Р       |

| 5   | VDD_IO      | 3.3V Power in         |                                    | Р       |

| 6   | VDD_ARM     | ARM Power test pin    |                                    | Р       |

| 7   | VDD_INT     | INT Power test pin    |                                    | Р       |

| 8   | VDD_MEM     | Memory Power test pin |                                    | Р       |

| 9   | VDD_RTC     | RTC battery in        | Must be connct to Battery or 3.3V  | Р       |

| 10  | GND         | Ground                |                                    | Р       |

| 11  | PWREN       | XPWRRGTON             | Power control                      | 0       |

| 12  | EINT9       | EINT9/GPH1_1          |                                    | I/O     |

| 13  | OTG_ID      | XuoID                 | USB OTG mini-Receptacle Identifier | I/O     |

| 14  | XOTG_DP     | XUOTGDP               | USB OTG Data pin DATA+             | I/O     |

| 15  | XOTG_DM     | XUOTGDM               | USB OTG Data pin DATA-             | I/O     |

| 16  | XVBUS       | XUOTGVBUS             | USB OTG mini-Receptacle Vbus       | I/O     |

| 17  | DRV_VBUS    | XUOTGDRVVUBS          | USB OTG charge pump enable         | 0       |

| 18  | USBH_DP     | XUHOSTDP              | USB HOST Data pin DATA+            | I/O     |

| 19  | USBH_DN     | XUHOSTDM              | USB HOST Data pin DATA-            | I/O     |

| 20  | EINT11      | EINT11/GPH1_3         |                                    | I/O     |

| 21  | HDMI_CEC    | EINT12/GPH1_4         | Defined for HDMI CEC signal        | I/O     |

| 22  | SD0DATA0    | SD0DATA0/GPG0_3       | SD0 interface DATA0                | I/O     |

| 23  | SD0DATA1    | SD0DATA1/GPG0_4       | SD0 interface DATA1                | I/O     |

| 24  | SD0DATA2    | SD0DATA2/GPG0_5       | SD0 interface DATA2                | I/O     |

| 25  | SD0DATA3    | SD0DATA3/GPG0_6       | SD0 interface DATA3                | I/O     |

| 26 | SD0CLK   | SD0CLK/GPG0_0   | SD0 interface Clock         | I/O |

|----|----------|-----------------|-----------------------------|-----|

| 27 | SD0CMD   | SD0CMD/GPG0_1   | SD0 Command/Response        | I/O |

| 28 | SD0CDn   | SD0CDn/GPG0_2   | SD0 Card Detect             | I/O |

| 29 | EINT7    | EINT7/GPH0_7    |                             | I/O |

| 30 | SD1DATA0 | SD1DATA0/GPG1_0 | SD1 interface DATA0         | I/O |

| 31 | SD1DATA1 | SD1DATA1/GPG1_1 | SD1 interface DATA1         | I/O |

| 32 | SD1DATA2 | SD1DATA2/GPG1_2 | SD1 interface DATA2         | I/O |

| 33 | SD1DATA3 | SD1DATA3/GPG1_3 | SD1 interface DATA3         | I/O |

| 34 | SD1CLK   | SD1CLK/GPG1_4   | SD1 interface Clock         | I/O |

| 35 | SD1CMD   | SD1CMD/GPG1_5   | SD1 Command/Response        | I/O |

| 36 | SD1CDn   | SD1CDn/GPG1_6   | SD1 Card Detect             | I/O |

| 37 | EINT8    | EINT8/GPH1_0    |                             | I/O |

| 38 | HDMI_HPD | EINT13/GPH1_5   | Defined for HDMI HPD signal | I/O |

| 39 | EINT14   | EINT14/GPH1_6   |                             | I/O |

| 40 | EINT15   | EINT15/GPH1_7   |                             | I/O |

| 41 | TSXM     | ADCIN8          | Used for TS_XM              | 1   |

| 42 | TSXP     | ADCIN9          | Used for TS_XP              | I   |

| 43 | TSYM     | ADCIN6          | Used for TS_YM              | I   |

| 44 | TSYP     | ADCIN7          | Used for TS_YP              | I   |

|    |          |                 |                             |     |

| 46 E<br>47 E<br>48 E | EINT16 EINT17 EINT18 EINT19 | EINT16/GPH2_0 EINT17/GPH2_1 EINT18/GPH2_2 | OR KP_COL1          | I/O<br>I/O |

|----------------------|-----------------------------|-------------------------------------------|---------------------|------------|

| 47 E                 | EINT18                      | _                                         | _                   | I/O        |

| 48 E                 |                             | EINT18/GPH2_2                             | 00 100 0010         | 1          |

|                      | EINT19                      |                                           | OR KP_COL2          | I/O        |

| 49 E                 |                             | EINT19/GPH2_3                             | OR KP_COL3          | I/O        |

|                      | EINT20                      | EINT20/GPH2_4                             | OR KP_COL4          | I/O        |

| 50 E                 | EINT21                      | EINT21/GPH2_5                             | OR KP_COL5          | I/O        |

| 51 T                 | ΓX2N                        | HDMI_TX2N                                 | HDMI phy TX2 N      | 0          |

| 52 T                 | ГХ2Р                        | HDMI_TX2P                                 | HDMI phy TX2 P      | 0          |

| 53 T                 | ΓX1N                        | HDMI_TX1N                                 | HDMI phy TX1 N      | 0          |

| 54 T                 | ГХ1Р                        | HDMI_TX1P                                 | HDMI phy TX1 P      | 0          |

| 55 T                 | TX0N                        | HDMI_TX0N                                 | HDMI phy TX0 N      | 0          |

| 56 T                 | TX0P                        | HDMI_TX0P                                 | HDMI phy TX0 P      | 0          |

| 57 T                 | TXCN                        | HDMI_TXCN                                 | HDMI phy TX clock N | 0          |

| 58 T                 | ГХСР                        | HDMI_TXCP                                 | HDMI phy TX clock P | 0          |

| <b>59</b> E          | 30                          | RGB_DATA0/GPF0_4                          | OR VEN_DATA0        | I/O        |

| 60 E                 | 31                          | RGB_DATA1/GPF0_5                          | OR VEN_DATA1        | I/O        |

| <b>61</b> E          | 32                          | RGB_DATA2/GPF0_6                          | OR VEN_DATA2        | I/O        |

| 62 E                 | 33                          | RGB_DATA3/GPF0_7                          | OR VEN_DATA3        | I/O        |

| 63 E                 | 34                          | RGB_DATA4/GPF1_0                          | OR VEN_DATA4        | I/O        |

| 64 E                 | 35                          | RGB_DATA5/GPF1_1                          | OR VEN_DATA5        | I/O        |

| 65 E                 | 36                          | RGB_DATA6/GPF1_2                          | OR VEN_DATA6        | I/O        |

| 66 | B7     | RGB_DATA7/GPF1_3  | OR VEN_DATA7                          | I/O |

|----|--------|-------------------|---------------------------------------|-----|

| 67 | G0     | RGB_DATA8/GPF1_4  | OR V656_DATA0                         | I/O |

| 68 | G1     | RGB_DATA9/GPF1_5  | OR V656_DATA1                         | I/O |

| 69 | G2     | RGB_DATA10/GPF1_6 | OR V656_DATA2                         | I/O |

| 70 | G3     | RGB_DATA11/GPF1_7 | OR V656_DATA3                         | I/O |

| 71 | G4     | RGB_DATA12/GPF2_0 | OR V656_DATA4                         | I/O |

| 72 | G5     | RGB_DATA13/GPF2_1 | OR V656_DATA5                         | I/O |

| 73 | G6     | RGB_DATA14/GPF2_2 | OR V656_DATA6                         | I/O |

| 74 | G7     | RGB_DATA15/GPF2_3 | OR V656_DATA7                         | I/O |

| 75 | R0     | RGB_DATA16/GPF2_4 |                                       | I/O |

| 76 | R1     | RGB_DATA17/GPF2_5 |                                       | I/O |

| 77 | R2     | RGB_DATA18/GPF2_6 |                                       | I/O |

| 78 | R3     | RGB_DATA19/GPF2_7 |                                       | I/O |

| 79 | R4     | RGB_DATA20/GPF3_0 |                                       | I/O |

| 80 | R5     | RGB_DATA21/GPF3_1 |                                       | I/O |

| 81 | R6     | RGB_DATA22/GPF3_2 |                                       | I/O |

| 82 | R7     | RGB_DATA23/GPF3_3 |                                       | I/O |

| 83 | VSYNC  | RGB_VS/GPF0_1     | Vertical sync signal for RGB or VEN   | I/O |

| 84 | HSYNC  | RGB_HS/GPF0_0     | Horizontal sync signal for RGB or VEN | I/O |

| 85 | DOTCLK | RGB_CLK/GPF0_3    | Video clock for RGB or V601           | I/O |

| 86 | DE     | RGB_VDEN/GPF0_3   | RGB_DE or VEN_HREF                    | I/O |

| Pin | Signal name | Function          | Description                          | IO Type |

|-----|-------------|-------------------|--------------------------------------|---------|

| 87  | TOUT0       | TOUT0/GPD0_0      | PWM time out                         | I/O     |

| 88  | EINT22      | EINT22/GPH2_6     | OR KP_COL6                           | I/O     |

| 89  | EINT23      | EINT23/GPH2_7     | OR KP_COL7                           | I/O     |

| 90  | TVOUT       | XDACOUT           | Analog output of Video DAC           | 0       |

| 91  | EINT24      | EINT24/GPH3_0     | OR KP_ROW0                           | I/O     |

| 92  | EINT25      | EINT25/GPH3_1     | OR KP_ROW1                           | I/O     |

| 93  | I2S1LRCK    | AC97SYNC/I2S1LRCK | Audio interface CH1                  | I/O     |

| 94  | I2S1SCLK    | AC97BCK/I2S1SCLK  | Audio interface CH1                  | I/O     |

| 95  | I2S1SDI     | AC97SDI/I2S1SDI   | Audio interface CH1                  | I/O     |

| 96  | I2S1SDO     | AC97SDO/I2S1SDO   | Audio interface CH1                  | I/O     |

| 97  | I2S1CDCLK   | AC97RST/I2S1CDCLK | Audio interface CH1                  | I/O     |

| 98  | EINT26      | EINT26/GPH3_2     | OR KP_ROW2                           | I/O     |

| 99  | EINT27      | EINT27/GPH3_3     | OR KP_ROW3                           | I/O     |

| 100 | TXD3        | TXD3/RTSn2/GPA1_3 | Uart 3 transmits data output         | I/O     |

| 101 | RXD3        | RXD3/CTSn2/GPA1_2 | Uart 3 receives data input           | I/O     |

| 102 | TXD2        | TXD2/GPA1_1       | Uart 2 transmits data output         | I/O     |

| 103 | RXD2        | RXD2/GPA1_0       | Uart 2 receives data input           | I/O     |

| 104 | RTSn1       | RTSn1/GPA0_7      | Uart 1 request to send output signal | I/O     |

| 105 | CTSn1       | CTSn1/GPA0_6      | Uart 1 clean to send input signal    | I/O     |

| 106 | TXD1        | TXD1/ GPA0_5      | Uart 1 transmits data output         | I/O     |

| 107 | RXD1        | RXD1/GPA0_4       | Uart 1 receives data input           | I/O     |

| 108 | RTSn0       | RTSn0/GPA0_3      | Uart 0 request to send output signal | I/O     |

| 109 | CTSn0       | CTSn0/GPA0_2      | Uart 0 clean to send input signal    | I/O     |

| 110 | TXD0     | TXD0/ GPA0_1     | Uart 0 transmits data output        | I/O |

|-----|----------|------------------|-------------------------------------|-----|

| 111 | RXD0     | RXD0/GPA0_0      | Uart 0 receives data input          | I/O |

| 112 | SPIMOSI0 | SPI0_MOSI/GPB3   | SPI CH0 master output / slave input | I/O |

| 113 | SPIMISO0 | SPI0_MISO/GPB2   | SPI CH0 master input / slave output | I/O |

| 114 | SPICS0   | SPI0_CS/GPB1     | SPI CH0 chip select                 | I/O |

| 115 | SPICLK0  | SPI0_CLK/GPB0    | SPI CH0 clock                       | I/O |

| 116 | EINT28   | EINT28/GPH3_4    | OR KP_ROW4                          | I/O |

| 117 | EINT29   | EINT29/GPH3_5    | OR KP_ROW5                          | I/O |

| 118 | EINT30   | EINT30/GPH3_6    | OR KP_ROW6                          | I/O |

| 119 | EINT31   | EINT31/GPH3_7    | OR KP_ROW7                          | I/O |

| 120 | EINT0    | EINT0/GPH0_0     |                                     | I/O |

| 121 | EINT1    | EINT1/GPH0_1     |                                     | I/O |

| 122 | YDATA7   | CAM_DATA7/GPE1_2 | Camera A data 7 in                  | I/O |

| 123 | YDATA6   | CAM_DATA6/GPE1_1 | Camera A data 6 in                  | I/O |

| 124 | YDATA5   | CAM_DATA5/GPE1_0 | Camera A data 5 in                  | I/O |

| 125 | YDATA4   | CAM_DATA4/GPE0_7 | Camera A data 4 in                  | I/O |

| 126 | YDATA3   | CAM_DATA3/GPE0_6 | Camera A data 3 in                  | I/O |

| 127 | YDATA2   | CAM_DATA2/GPE0_5 | Camera A data 2 in                  | I/O |

| 128 | YDATA1   | CAM_DATA1/GPE0_4 | Camera A data 1 in                  | I/O |

|     |          |                  |                                     |     |

| Pin | Signal name | Function          | Description                   | IO Type |

|-----|-------------|-------------------|-------------------------------|---------|

| 129 | YDATA0      | CAM_DATA0/GPE0_3  | Camera A data 0 in            | I/O     |

| 130 | YPCLK       | CAM_PCLK/GPPE0_0  | Camera A clock in             | I/O     |

| 131 | YCLKO       | CAM_CLKEN/GPE1_3  | Master clock to dirver Camera | I/O     |

| 132 | YVSYNC      | CAM_VS/GPE0_1     | Camera A VSYNC in             | I/O     |

| 133 | YHREF       | CAM_HREF/GPE0_2   | Camera A HSYNC in             | I/O     |

| 134 | YRST        | CAM_FIELD/GPE1_4  | Reset or Power down Camera    | I/O     |

| 135 | SDA1        | IIC-bus CH1 data  | Defaulted on HDMI DDC SDA     | I/O     |

| 136 | SCL1        | IIC-bus CH1 clock | Defaulted on HDMI DDC SCL     | I/O     |

| 137 | DATA15      | EBI_DATA15/MP07_7 | Memory port0 Data bus         | I/O     |

| 138 | DATA14      | EBI_DATA14/MP07_6 | Memory port0 Data bus         | I/O     |

| 139 | DATA13      | EBI_DATA13/MP07_5 | Memory port0 Data bus         | I/O     |

| 140 | DATA12      | EBI_DATA12/MP07_4 | Memory port0 Data bus         | I/O     |

| 141 | DATA11      | EBI_DATA11MP07_3  | Memory port0 Data bus         | I/O     |

| 142 | DATA10      | EBI_DATA10/MP07_2 | Memory port0 Data bus         | I/O     |

| 143 | DATA9       | EBI_DATA9/MP07_1  | Memory port0 Data bus         | I/O     |

| 144 | DATA8       | EBI_DATA8/MP07_0  | Memory port0 Data bus         | I/O     |

| 145 | DATA7       | EBI_DATA7/MP06_7  | Memory port0 Data bus         | I/O     |

| 146 | DATA6       | EBI_DATA6/MP06_6  | Memory port0 Data bus         | I/O     |

| 147 | DATA5       | EBI_DATA5/MP06_5  | Memory port0 Data bus         | I/O     |

| 148 | DATA4       | EBI_DATA4/MP06_4  | Memory port0 Data bus         | I/O     |

| 149 | DATA3       | EBI_DATA3/MP06_3  | Memory port0 Data bus         | I/O     |

| 150 | DATA2       | EBI_DATA2/MP06_2  | Memory port0 Data bus         | I/O     |

| 151 | DATA1       | EBI_DATA1/MP06_1  | Memory port0 Data bus         | I/O     |

| 152 | DATA0   | EBI_DATA0/MP06_0    | Memory port0 Data bus           | I/O |

|-----|---------|---------------------|---------------------------------|-----|

| 153 | OEn     | EBI_OEn/MP01_6      | Memory port0 SROM Output Enable | I/O |

| 154 | WEn     | EBI_WEn/MP01_7      | Memory port0 SROM Write Enable  | I/O |

| 155 | CSn1    | SROM_CSn1/MP01_1    | Memory port0 SROM Chip Select   | I/O |

| 156 | EINT10  | EINT10/GPH1_2       |                                 | I/O |

| 157 | ADDR2   | EBI_ADDR2/MP04_2    | Memory Port0 Address bus        | 0   |

| 158 | nRESET  | RESET OUT           |                                 | 0   |

| 159 | EINT2   | EINT2/GPH0_2        |                                 | I/O |

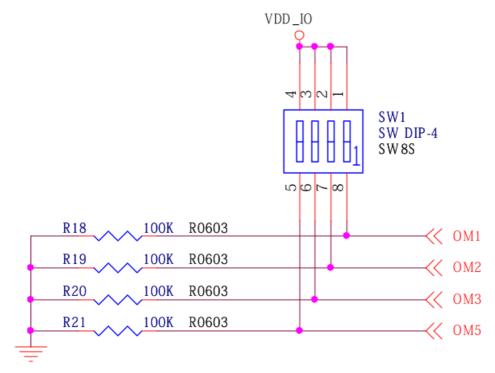

| 160 | OM5     | OM1: 1, Others: 0   |                                 | 1   |

| 161 | OM3     | Boot in Nand Flash  |                                 | 1   |

| 162 | OM2     | OM2/3: 1, Others: 0 |                                 | 1   |

| 163 | OM1     | Boot in SD0         |                                 | 1   |

| 164 | EINT3   | EINT3/GPH0_3        |                                 | I/O |

| 165 | EINT4   | EINT4/GPH0_4        |                                 | I/O |

| 166 | EINT5   | EINT5/GPH0_5        |                                 | I/O |

| 167 | RST_KEY | RESET KEY IN        | Connect to Reset button         | 1   |

| 168 | EINT6   | EINT6/GPH0_6        |                                 | I/O |

| 169 | AIN1    | 12bit ADC CH1 input |                                 | 1   |

| 170 | AIN0    | 12bit ADC CH0 input |                                 | 1   |

| 171 | GND     | Ground              |                                 | Р   |

| 172 | GND     | Ground              |                                 | Р   |

| 173 | GND     | Ground              |                                 | Р   |

| 174 | GND     | Ground              |                                 | Р   |

| 175 | GND     | Ground              |                                 | Р   |

| 176 | GND     | Ground              |                                 | Р   |

| 177 | GND     | Ground              |                                 | Р   |

| 178 | GND     | Ground              |                                 | Р   |

| 179 | GND     | Ground              |                                 | Р   |

| 180 | GND     | Ground              |                                 | Р   |

**Multiplexed GPIO**

| Pin | Signal name | Function 1 | Function 2 | Function 3 |

|-----|-------------|------------|------------|------------|

| 87  | TOUT0       | TOUT0      | GPD0_0     |            |

This pin is 32bit PWM timer output, use for LCD backlight brightness control.

| Pin | Signal name | Function 1 | Function 2 | Function 3 |

|-----|-------------|------------|------------|------------|

| 45  | EINT16      | EINT16     | GPH2_0     | KP_COL0    |

| 46  | EINT17      | EINT17     | GPH2_1     | KP_COL1    |

| 47  | EINT18      | EINT18     | GPH2_2     | KP_COL2    |

| 48  | EINT19      | EINT19     | GPH2_3     | KP_COL3    |

| 49  | EINT20      | EINT20     | GPH2_4     | KP_COL4    |

| 50  | EINT21      | EINT21     | GPH2_5     | KP_COL5    |

| 88  | EINT22      | EINT22     | GPH2_6     | KP_COL6    |

| 89  | EINT23      | EINT23     | GPH2_7     | KP_COL7    |

| 91  | EINT24      | EINT24     | GPH3_0     | KP_ROW0    |

| 92  | EINT25      | EINT25     | GPH3_1     | KP_ROW1    |

| 98  | EINT26      | EINT26     | GPH3_2     | KP_ROW2    |

| 99  | EINT27      | EINT27     | GPH3_3     | KP_ROW3    |

| 116 | EINT28      | EINT28     | GPH3_4     | KP_ROW4    |

| 117 | EINT29      | EINT29     | GPH3_5     | KP_ROW5    |

| 118 | EINT30      | EINT30     | GPH3_6     | KP_ROW6    |

| 119 | EINT31      | EINT31     | GPH3_7     | KP_ROW7    |

These pins are external interrupt and use to wake up. EINT12 default as HDMI\_CEC. EINT13 default as HDMI\_HPD.

| Pin | Signal name | Function 1 | Function 2 | Function 3 |

|-----|-------------|------------|------------|------------|

| 100 | TXD3        | TXD3       | GPA1_3     | RTSn2      |

| 101 | RXD3        | RXD3       | GPA1_2     | CTSn2      |

| 102 | TXD2  | TXD2  | GPA1_1 |  |

|-----|-------|-------|--------|--|

| 103 | RXD2  | RXD2  | GPA1_0 |  |

| 104 | RTSn1 | RTSn1 | GPA0_7 |  |

| 105 | CTSn1 | CTSn1 | GPA0_6 |  |

| 106 | TXD1  | TXD1  | GPA0_5 |  |

| 107 | RXD1  | RXD1  | GPA0_4 |  |

| 108 | RTSn0 | RTSn0 | GPA0_3 |  |

| 109 | CTSn0 | CTSn0 | GPA0_2 |  |

| 110 | TXD0  | TXD0  | GPA0_1 |  |

| 111 | RXD0  | RXD0  | GPA0_0 |  |

UARTs, All CH supports both IR transmission and reception.

| Pin | Signal name | Function 1 | Function 2 | Function 3 |

|-----|-------------|------------|------------|------------|

| 135 | SDA1        | I2C1_SDA   | GPD1_2     |            |

| 136 | SCL1        | I2C1_SCL   | GPD1_3     |            |

I2C CH1 default as HDMI DDC. Other devices can be simulated by GPIOs.

| Pin | Signal name | Function 1 | Function 2 | Function 3 | Function 4 |

|-----|-------------|------------|------------|------------|------------|

| 93  | I2S1LRCK    | AC97SYNC1  | I2S1LRCK   | PCM1FSYNC  | GPC2       |

| 94  | I2S1SCLK    | AC97BCK1   | I2S1SCLK   | PCM1SCLK   | GPC0       |

| 95  | I2S1SDI     | AC97SDI1   | I2S1SDI    | PCM1SIN    | GPC3       |

| 96  | I2S1SDO     | AC97SDO1   | I2S1SDO    | PCM1SOUT   | GPC4       |

| 97  | I2S1CDCLK   | AC97RST1   | I2S1CDCLK  | PCM1EXTCLK | GPC1       |

Audio codec interface.

| Pin | Signal name | Function 1 | Function 2 | Function 3 |

|-----|-------------|------------|------------|------------|

| 112 | SPIDI0      | SPI0_MOSI  | GPB3       |            |

| 113 | SPIDO0      | SPI0_MISO  | GPB2       |            |

| 114 | SPICS0      | SPI0_CS    | GPB1       |            |

| 115 | SPICLK0     | SPI0_CLK   | GPB0       |            |

SPI interface.

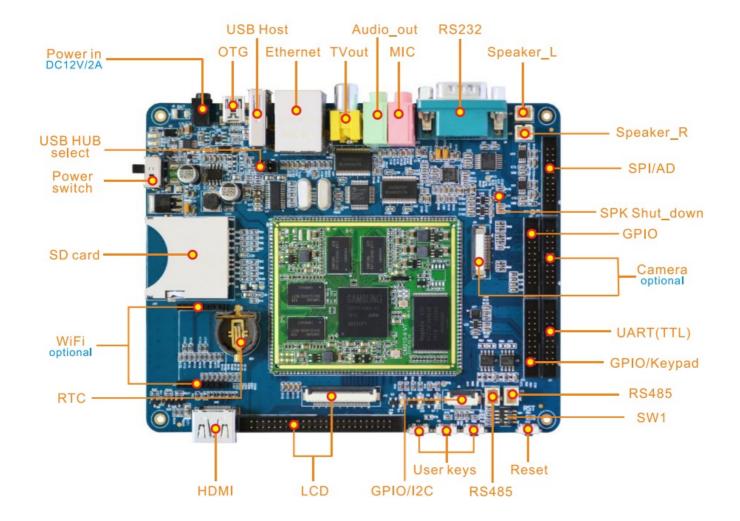

**Development Kit (Android210)**

# **Hardware Design Guide**

# **Peripheral Circuit Reference**

# 1. RTC Battery Circuit

2. HDMI Interface Circuit

## 3. OTG Interface Circuit

# 4. OM Setting Circuit

## 5. SD0 Interface Circuit

# SD CARD

#### 6. Audio Codec Circuit

7. Ethernet Interface Circuit

**PCB Footprint**

# **Product Electrical Characteristics**

# **Dissipation and Temperature**

| Symbol  | Parameter              | Min    | Тур | Max    | Unit |

|---------|------------------------|--------|-----|--------|------|

| DC5V    | Module Supply Voltage  | 3.6    | 5   | 5.5    | V    |

| VDD_IO  | IO Supply Voltage      | 3.3-5% | 3.3 | 3.3+5% | V    |

| Vrvpp   | Max ripple Voltage     |        |     | 0.15   | V    |

| Idmax   | DC5V Max Input Current |        | 310 | 350    | mA   |

| Ipmax   | VDD_IO Max Current     |        | 45  | 55     | mA   |

| VCC_RTC | RTC Battery Voltage    | 1.7    | 3   | 3.6    | V    |

| Irtc    | RTC Input Current      |        |     | 10     | uA   |

| Та      | Operating Temperature  | 0      |     | 70     | °C   |

| Tstg    | Storage Temperature    | -40    |     | 85     | °C   |

# **Reliability of Test**

| High Temperature Operating Test |                                  |          |  |  |

|---------------------------------|----------------------------------|----------|--|--|

| Contents                        | Operating 8h in high temperature | 55°C±2°C |  |  |

| Result                          | Pass                             |          |  |  |

| Operating Life Test |                   |      |  |

|---------------------|-------------------|------|--|

| Contents            | Operating in room | 120h |  |

| Result              | Pass              |      |  |

# www.armdesigner.com

## **Documents / Resources**

BOARDCON CM210-II Embedded Design System on Module for Data Terminals [pdf] User Manual

CM210-II, V7, CM210-II Embedded Design System on Module for Data Terminals, CM210-II, E mbedded Design System on Module for Data Terminals, Design System on Module for Data Terminals, System on Module for Data Terminals, on Module for Data Terminals, Module for Data Terminals, Terminals, Terminals

## References

• User Manual

# Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.